Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 11                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

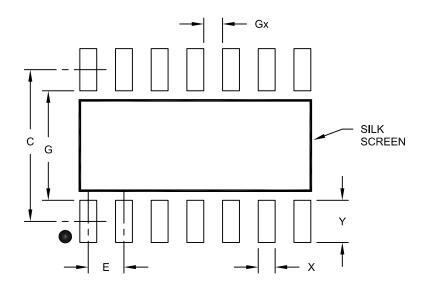

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 14-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1554-i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- · Program Memory

- Configuration Words

- Device ID

- User ID

- Flash Program Memory

- · Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

The following features are associated with access and control of program memory and data memory:

- · PCL and PCLATH

- Stack

- · Indirect Addressing

## 3.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing a 32K x 14 program memory space. Table 3-1 shows the memory sizes implemented. Accessing a location above these boundaries will cause a wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 3-1).

#### TABLE 3-1: DEVICE SIZES AND ADDRESSES

| Device      | Program Memory<br>Space (Words) | Last Program Memory<br>Address | High-Endurance Flash<br>Memory Address Range <sup>(1)</sup> |

|-------------|---------------------------------|--------------------------------|-------------------------------------------------------------|

| PIC16LF1554 | 4,096                           | 0FFFh                          | 0F80h-0FFFh                                                 |

| PIC16LF1559 | 8,192                           | 1FFFh                          | 1F80h-1FFFh                                                 |

Note 1: High-endurance Flash applies to low byte of each address in the range.

TABLE 3-9: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Address | Name                               | Bit 7                                     | Bit 6                                       | Bit 5          | Bit 4            | Bit 3           | Bit 2        | Bit 1          | Bit 0         | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |  |

|---------|------------------------------------|-------------------------------------------|---------------------------------------------|----------------|------------------|-----------------|--------------|----------------|---------------|-----------------------|---------------------------------|--|

| Bank 1  |                                    |                                           |                                             |                |                  |                 |              |                |               |                       |                                 |  |

| 080h    | INDF0 <sup>(1)</sup>               | Addressing t                              | his location us                             | es contents of | FSR0H/FSR0       | L to address    | data memor   | (not a physi   | cal register) | xxxx xxxx             | uuuu uuuu                       |  |

| 081h    | INDF1 <sup>(1)</sup>               | Addressing t                              | his location us                             | es contents of | FSR1H/FSR1       | L to address    | data memor   | y (not a physi | cal register) | xxxx xxxx             | uuuu uuuu                       |  |

| 082h    | PCL <sup>(1)</sup>                 |                                           | Program Counter (PC) Least Significant Byte |                |                  |                 |              |                |               |                       |                                 |  |

| 083h    | STATUS <sup>(1)</sup>              | <del>TO</del> <del>PD</del> z DC C        |                                             |                |                  |                 |              |                |               | 1 1000                | q quuu                          |  |

| 084h    | FSR0L <sup>(1)</sup>               |                                           |                                             | Indirect Da    | ita Memory Ad    | Idress 0 Low    | Pointer      |                |               | 0000 0000             | uuuu uuuu                       |  |

| 085h    | FSR0H <sup>(1)</sup>               |                                           |                                             | Indirect Da    | ta Memory Ad     | dress 0 High    | Pointer      |                |               | 0000 0000             | 0000 0000                       |  |

| 086h    | FSR1L <sup>(1)</sup>               |                                           |                                             | Indirect Da    | ita Memory Ad    | Idress 1 Low    | Pointer      |                |               | 0000 0000             | uuuu uuuu                       |  |

| 087h    | FSR1H <sup>(1)</sup>               |                                           |                                             | Indirect Da    | ta Memory Ad     | dress 1 High    | Pointer      |                |               | 0000 0000             | 0000 0000                       |  |

| 088h    | BSR <sup>(1)</sup>                 | _                                         | _                                           | _              |                  |                 | BSR<4:0>     |                |               | 0 0000                | 0 0000                          |  |

| 089h    | WREG <sup>(1)</sup>                |                                           |                                             |                | Working R        | egister         |              |                |               | 0000 0000             | uuuu uuuu                       |  |

| 08Ah    | PCLATH <sup>(1)</sup>              | _                                         |                                             | Write But      | ffer for the upp | er 7 bits of th | ne Program C | ounter         |               | -000 0000             | -000 0000                       |  |

| 08Bh    | INTCON <sup>(1)</sup>              | GIE                                       | PEIE                                        | TMR0IE         | INTE             | IOCIE           | TMR0IF       | INTF           | IOCIF         | 0000 0000             | 0000 0000                       |  |

| 08Ch    | TRISA                              | _                                         | _                                           | TRISA5         | TRISA4           | _               | TRISA2       | TRISA1         | TRISA0        | 11 1111               | 11 1111                         |  |

| 08Dh    | TRISB <sup>(2)</sup>               |                                           | Unimplemented                               |                |                  |                 |              |                |               |                       | _                               |  |

| וועסטו  | TRISB <sup>(3)</sup>               | TRISB7                                    | TRISB6                                      | TRISB5         | TRISB4           | _               | _            | _              | _             | 1111                  | 1111                            |  |

| 08Eh    | TRISC <sup>(2)</sup>               | _                                         | ı                                           | TRISC5         | TRISC4           | TRISC3          | TRISC2       | TRISC1         | TRISC0        | 11 1111               | 11 1111                         |  |

| UOEII   | TRISC <sup>(3)</sup>               | TRISC7                                    | TRISC6                                      | TRISC5         | TRISC4           | TRISC3          | TRISC2       | TRISC1         | TRISC0        | 1111 1111             | 1111 1111                       |  |

| 091h    | PIE1                               | TMR1GIE                                   | AD1IE                                       | RCIE           | TXIE             | SSP1IE          | _            | TMR2IE         | TMR1IE        | 0000 0-00             | 0000 0-00                       |  |

| 092h    | PIE2                               | _                                         | AD2IE                                       | _              | 1                | BCLIE           | _            | _              | _             | -0 0                  | -0 0                            |  |

| 095h    | OPTION_REG                         | WPUEN                                     | INTEDG                                      | TMR0CS         | TMR0SE           | PSA             |              | PS<2:0>        |               | 1111 1111             | 1111 1111                       |  |

| 096h    | PCON                               | STKOVF                                    | STKUNF                                      | _              | RWDT             | RMCLR           | RI           | POR            | BOR           | 00-1 11qq             | 00-q qquu                       |  |

| 097h    | WDTCON                             | _                                         | ı                                           |                | V                | /DTPS<4:0>      |              |                | SWDTEN        | 01 0110               | 01 0110                         |  |

| 098h    | _                                  |                                           |                                             |                | Unimplem         | ented           |              |                |               | _                     | _                               |  |

| 099h    | OSCCON                             | SPLLEN                                    |                                             | IRCF<          | :3:0>            |                 | _            | SCS            | <1:0>         | 0011 1-00             | 0011 1-00                       |  |

| 09Ah    | OSCSTAT                            | _                                         | PLLSR                                       | _              | HFIOFR           | _               | _            | LFIOFR         | HFIOFS        | -0-000                | -q-q -q0q                       |  |

| 09Bh    | ADRESL/<br>AD1RES0L <sup>(4)</sup> |                                           |                                             | A              | DC1 Result Re    | gister 0 Low    |              |                |               | xxxx xxxx             | uuuu uuuu                       |  |

| 09Ch    | ADRESH/<br>AD1RES0H <sup>(4)</sup> | ADC1 Result Register 0 High               |                                             |                |                  |                 |              |                | xxxx xxxx     | uuuu uuuu             |                                 |  |

| 09Dh    | ADCON0/<br>AD1CON0 <sup>(4)</sup>  | - CHS4 CHS3 CHS2 CHS1 CHS0 GO/DONE1 AD10N |                                             |                |                  |                 | -000 0000    | -000 0000      |               |                       |                                 |  |

| 09Eh    | ADCON1/<br>ADCOMCON <sup>(4)</sup> | ADFM                                      | ADFM ADCS<2:0> — GO/ DONE_ALL ADPREF<1:0> ( |                |                  |                 |              |                |               | 0000 -000             | 0000 -000                       |  |

| 09Fh    | ADCON2/<br>AD1CON2 <sup>(4)</sup>  | _                                         | -                                           | TRIGSEL<2:0>   | ·                | _               | _            | _              | _             | -000                  | -000                            |  |

$\textbf{Legend:} \qquad \textbf{x} = \text{unknown}, \textbf{u} = \text{unchanged}, \textbf{q} = \text{depends on condition, -= unimplemented, read as '0'}, \textbf{r} = \text{reserved}. \\ \textbf{Shaded locations unimplemented, read as '0'}.$

Note 1: These registers can be accessed from any bank.

<sup>2:</sup> PIC16LF1554.

<sup>3:</sup> PIC16LF1559.

<sup>4:</sup> These registers/bits are available at two address locations, in Bank 1 and Bank 14.

## TABLE 3-9: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Name                  | Bit 7                                                                                                                                                                                 | Bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                             | Bit 5                                                                                                                                                                            | Bit 4            | Bit 3           | Bit 2                                                                       | Bit 1          | Bit 0                                                                                                                                                                                                                                   | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|-----------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------------|

|                       | 1                                                                                                                                                                                     | •                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                  | •                | •               |                                                                             | •              | •                                                                                                                                                                                                                                       |                       | •                               |

| INDF0 <sup>(1)</sup>  | Addressing t                                                                                                                                                                          | his location us                                                                                                                                                                                                                                                                                                                                                                                                                                   | es contents of                                                                                                                                                                   | FSR0H/FSR0       | L to address    | data memor                                                                  | y (not a physi | cal register)                                                                                                                                                                                                                           | xxxx xxxx             | uuuu uuuu                       |

| INDF1 <sup>(1)</sup>  | Addressing t                                                                                                                                                                          | his location us                                                                                                                                                                                                                                                                                                                                                                                                                                   | es contents of                                                                                                                                                                   | FSR1H/FSR1       | L to address    | data memor                                                                  | y (not a physi | cal register)                                                                                                                                                                                                                           | xxxx xxxx             | uuuu uuuu                       |

| PCL <sup>(1)</sup>    |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Program C                                                                                                                                                                        | Counter (PC) L   | east Significa  | int Byte                                                                    |                |                                                                                                                                                                                                                                         | 0000 0000             | 0000 0000                       |

| STATUS <sup>(1)</sup> | _                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _                                                                                                                                                                                | TO               | PD              | Z                                                                           | DC             | С                                                                                                                                                                                                                                       | 1 1000                | q quuu                          |

| FSR0L <sup>(1)</sup>  |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Indirect Da                                                                                                                                                                      | ita Memory Ad    | dress 0 Low     | Pointer                                                                     |                |                                                                                                                                                                                                                                         | 0000 0000             | uuuu uuuu                       |

| FSR0H <sup>(1)</sup>  |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Indirect Da                                                                                                                                                                      | ta Memory Ad     | ldress 0 High   | Pointer                                                                     |                |                                                                                                                                                                                                                                         | 0000 0000             | 0000 0000                       |

| FSR1L <sup>(1)</sup>  |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Indirect Da                                                                                                                                                                      | nta Memory Ad    | ldress 1 Low    | Pointer                                                                     |                |                                                                                                                                                                                                                                         | 0000 0000             | uuuu uuuu                       |

| FSR1H <sup>(1)</sup>  |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Indirect Da                                                                                                                                                                      | ta Memory Ad     | ldress 1 High   | Pointer                                                                     |                |                                                                                                                                                                                                                                         | 0000 0000             | 0000 0000                       |

| BSR <sup>(1)</sup>    | _                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _                                                                                                                                                                                |                  |                 | BSR<4:0>                                                                    |                |                                                                                                                                                                                                                                         | 0 0000                | 0 0000                          |

| WREG <sup>(1)</sup>   |                                                                                                                                                                                       | •                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                  | Working R        | egister         |                                                                             |                |                                                                                                                                                                                                                                         | 0000 0000             | uuuu uuuu                       |

| PCLATH <sup>(1)</sup> | _                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Write But                                                                                                                                                                        | ffer for the upp | er 7 bits of th | ne Program C                                                                | Counter        |                                                                                                                                                                                                                                         | -000 0000             | -000 0000                       |

| INTCON <sup>(1)</sup> | GIE                                                                                                                                                                                   | PEIE                                                                                                                                                                                                                                                                                                                                                                                                                                              | TMR0IE                                                                                                                                                                           | INTE             | IOCIE           | TMR0IF                                                                      | INTF           | IOCIF                                                                                                                                                                                                                                   | 0000 0000             | 0000 0000                       |

| LATA                  | _                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LATA5                                                                                                                                                                            | LATA4            | _               | LATA2                                                                       | LATA1          | LATA0                                                                                                                                                                                                                                   | xx xxxx               | uu uuuu                         |

| LATB <sup>(2)</sup>   | Unimplemented                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                  |                  |                 |                                                                             |                |                                                                                                                                                                                                                                         |                       | _                               |

| LATB <sup>(3)</sup>   | LATB7                                                                                                                                                                                 | LATB6                                                                                                                                                                                                                                                                                                                                                                                                                                             | LATB5                                                                                                                                                                            | LATB4            | _               | _                                                                           | _              | _                                                                                                                                                                                                                                       | xxxx                  | uuuu                            |

| LATC <sup>(2)</sup>   | _                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LATC5                                                                                                                                                                            | LATC4            | LATC3           | LATC2                                                                       | LATC1          | LATC0                                                                                                                                                                                                                                   | xx xxxx               | uu uuuu                         |

| LATC <sup>(3)</sup>   | LATC7                                                                                                                                                                                 | LATC6                                                                                                                                                                                                                                                                                                                                                                                                                                             | LATC5                                                                                                                                                                            | LATC4            | LATC3           | LATC2                                                                       | LATC1          | LATC0                                                                                                                                                                                                                                   | xxxx xxxx             | uuuu uuuu                       |

| _                     |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                  | Unimplem         | ented           |                                                                             |                |                                                                                                                                                                                                                                         | _                     | _                               |

| _                     |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                  | Unimplem         | ented           |                                                                             |                |                                                                                                                                                                                                                                         | _                     | _                               |

| _                     |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                  | Unimplem         | ented           |                                                                             |                |                                                                                                                                                                                                                                         | _                     | _                               |

| _                     |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                  | Unimplem         | ented           |                                                                             |                |                                                                                                                                                                                                                                         | _                     | _                               |

| _                     |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                  | Unimplem         | ented           |                                                                             |                |                                                                                                                                                                                                                                         | _                     | _                               |

| _                     |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                  | Unimplem         | ented           |                                                                             |                |                                                                                                                                                                                                                                         | _                     | _                               |

| _                     |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                  | Unimplem         | ented           |                                                                             |                |                                                                                                                                                                                                                                         | _                     | _                               |

| BORCON                | SBOREN                                                                                                                                                                                | BORFS                                                                                                                                                                                                                                                                                                                                                                                                                                             | _                                                                                                                                                                                | _                | _               | _                                                                           | _              | BORRDY                                                                                                                                                                                                                                  | 10q                   | uuu                             |

| FVRCON                | FVREN                                                                                                                                                                                 | FVRRDY                                                                                                                                                                                                                                                                                                                                                                                                                                            | TSEN                                                                                                                                                                             | TSRNG            | _               | _                                                                           | ADFVI          | R<1:0>                                                                                                                                                                                                                                  | 0q0000                | 0q0000                          |

| _                     |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                  | Unimplem         | ented           |                                                                             |                |                                                                                                                                                                                                                                         | _                     | _                               |

| 1                     |                                                                                                                                                                                       | Unimplemented                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                  |                  |                 |                                                                             |                |                                                                                                                                                                                                                                         |                       | _                               |

| _                     | Unimplemented                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                  |                  |                 |                                                                             |                |                                                                                                                                                                                                                                         | _                     | _                               |

| _                     | Unimplemented                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                  |                  |                 |                                                                             |                |                                                                                                                                                                                                                                         | _                     | _                               |

| _                     |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                  | Unimplem         | ented           |                                                                             |                |                                                                                                                                                                                                                                         |                       |                                 |

| APFCON                | RXDTSEL                                                                                                                                                                               | SDOSEL                                                                                                                                                                                                                                                                                                                                                                                                                                            | SSSEL                                                                                                                                                                            | SDSEL            | _               | TXCKSEL                                                                     | GRDBSEL        | GRDASEL                                                                                                                                                                                                                                 | 0000 -000             | 0000 -000                       |

| _                     |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                  | Unimplem         | ented           |                                                                             |                |                                                                                                                                                                                                                                         |                       |                                 |

| _                     |                                                                                                                                                                                       | Unimplemented                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                  |                  |                 |                                                                             |                |                                                                                                                                                                                                                                         |                       | _                               |

|                       | INDF0(1) INDF1(1) PCL(1) STATUS(1) FSR0L(1) FSR0L(1) FSR1L(1) FSR1L(1) FSR1H(1) BSR(1) WREG(1) PCLATH(1) INTCON(1) LATA LATB(2) LATC(2) LATC(3) — — — — — — — — — — — — — — — — — — — | INDF0 <sup>(1)</sup> Addressing to INDF1 <sup>(1)</sup> Addressing to PCL <sup>(1)</sup> STATUS <sup>(1)</sup> —  FSROL <sup>(1)</sup> FSROH <sup>(1)</sup> FSR1L <sup>(1)</sup> FSR1H <sup>(1)</sup> BSR <sup>(1)</sup> —  WREG <sup>(1)</sup> PCLATH <sup>(1)</sup> —  INTCON <sup>(1)</sup> GIE  LATA —  LATB <sup>(2)</sup> LATB <sup>(3)</sup> LATB7  LATC <sup>(2)</sup> —  LATC <sup>(3)</sup> LATC7  —  — — — — — — — — — — — — — — — — — | INDF0 <sup>(1)</sup> Addressing this location us INDF1 <sup>(1)</sup> Addressing this location us PCL <sup>(1)</sup> STATUS <sup>(1)</sup> — — — — — — — — — — — — — — — — — — — | INDF0(1)         | NDF0(1)         | INDFO(¹)   Addressing this location uses contents of FSR0H/FSR0L to address | INDF0(¹)       | INDFO <sup>(1)   Addressing this location uses contents of FSR0H/FSR0L to address data memory (not a physis INDF1<sup>(1)</sup>   Addressing this location uses contents of FSR1H/FSR1L to address data memory (not a physis)    </sup> | NDF0(1)               | Name                            |

Note 1: These registers can be accessed from any bank.

<sup>2:</sup> PIC16LF1554.

<sup>3:</sup> PIC16LF1559.

<sup>4:</sup> These registers/bits are available at two address locations, in Bank 1 and Bank 14.

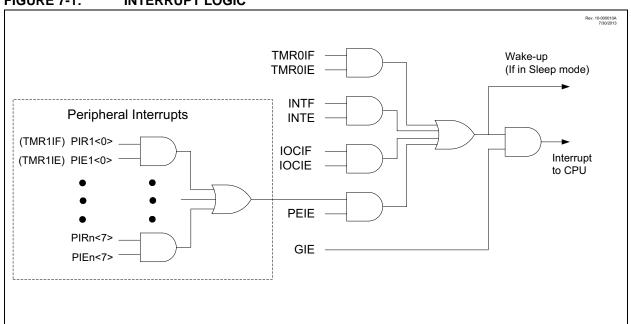

### 7.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for interrupts:

- Operation

- · Interrupt latency

- · Interrupts during Sleep

- INT pin

- · Automatic context saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

A block diagram of the interrupt logic is shown in Figure 7-1.

FIGURE 7-1: INTERRUPT LOGIC

## REGISTER 11-6: WPUA: WEAK PULL-UP PORTA REGISTER<sup>(1,2)</sup>

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   | WPUA5   | WPUA4   | WPUA3   | WPUA2   | WPUA1   | WPUA0   |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 WPUA<5:0>: Weak Pull-up Register bits<sup>(3)</sup>

1 = Pull-up enabled0 = Pull-up disabled

Note 1: Global WPUEN bit of the OPTION REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is configured as an output.

3: For the WPUA3 bit, when MCLRE = 1, weak pull-up is internally enabled, but not reported here.

#### TABLE 11-3: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name       | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2   | Bit 1   | Bit 0   | Register on Page |

|------------|---------|--------|--------|--------|-------|---------|---------|---------|------------------|

| ANSELA     | _       | _      | ANSA5  | ANSA4  | _     | ANSA2   | ANSA1   | ANSA0   | 109              |

| APFCON     | RXDTSEL | SDOSEL | SSSEL  | SDSEL  | _     | TXCKSEL | GRDBSEL | GRDASEL | 106              |

| LATA       | _       | _      | LATA5  | LATA4  |       | LATA2   | LATA1   | LATA0   | 109              |

| OPTION_REG | WPUEN   | INTEDG | TMR0CS | TMR0SE | PSA   |         | PS<2:0> |         | 166              |

| PORTA      | _       | _      | RA5    | RA4    | RA3   | RA2     | RA1     | RA0     | 108              |

| TRISA      | _       | _      | TRISA5 | TRISA4 | _(1)  | TRISA2  | TRISA1  | TRISA0  | 108              |

| WPUA       | _       | _      | WPUA5  | WPUA4  | WPUA3 | WPUA2   | WPUA1   | WPUA0   | 110              |

$\textbf{Legend:} \quad x = \text{unknown}, \ u = \text{unchanged}, - = \text{unimplemented locations read as `0'}. \ Shaded \ cells \ are \ not \ used \ by$

PORTA.

Note 1: Unimplemented, read as '1'.

### TABLE 11-4: SUMMARY OF CONFIGURATION WORD WITH PORTA

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4  | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register on Page |

|---------|------|---------|---------|----------|-----------|----------|----------|---------|---------|------------------|

| CONTION | 13:8 | 1       | -       | _        | -         | CLKOUTEN | BORE     | N<1:0>  | _       | 50               |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE<1:0> |          | _        | FOS     | C<2:0>  | 53               |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by PORTA.

# REGISTER 11-11: WPUB: WEAK PULL-UP PORTB REGISTER<sup>(1,2)</sup>

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| WPUB7   | WPUB6   | WPUB5   | WPUB4   | _   | _   | _   | _     |

| bit 7   |         |         |         |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-4 WPUB<7:4>: Weak Pull-up Register bits

1 = Pull-up enabled0 = Pull-up disabled

bit 3-0 **Unimplemented:** Read as '0'

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is configured as an output.

## TABLE 11-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB<sup>(1)</sup>

| Name       | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2   | Bit 1   | Bit 0   | Register on Page |

|------------|---------|--------|--------|--------|-------|---------|---------|---------|------------------|

| ANSELB     | ANSB7   | ANSB6  | ANSB5  | ANSB4  | _     | _       | -       | _       | 113              |

| APFCON     | RXDTSEL | SDOSEL | SSSEL  | SDSEL  | 1     | TXCKSEL | GRDBSEL | GRDASEL | 106              |

| LATB       | LATB7   | LATB6  | LATB5  | LATB4  | 1     |         | 1       | 1       | 113              |

| OPTION_REG | WPUEN   | INTEDG | TMR0CS | TMR0SE | PSA   |         | PS<2:0> |         | 166              |

| PORTB      | RB7     | RB6    | RB5    | RB4    | 1     | _       | 1       | 1       | 112              |

| TRISB      | TRISB7  | TRISB6 | TRISB5 | TRISB4 |       | _       | 1       |         | 112              |

| WPUB       | WPUB7   | WPUB6  | WPUB5  | WPUB4  |       | _       |         |         | 114              |

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by

PORTB.

Note 1: PIC16LF1559 only.

#### TABLE 11-7: SUMMARY OF CONFIGURATION WORD WITH PORTB

| Name     | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register on Page |

|----------|------|---------|---------|----------|----------|----------|----------|---------|---------|------------------|

| 00015104 | 13:8 |         | 1       | _        | -        | CLKOUTEN | BOREI    | V<1:0>  | _       | 50               |

| CONFIG1  | 7:0  | CP      | MCLRE   | PWRTE    | WE       | )TE<1:0> | _        | FOSC    | C<1:0>  | 53               |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by PORTB.

## 14.4 ADC Acquisition Time

To ensure accurate temperature measurements, the user must wait at least 200  $\mu s$  after the ADC input multiplexer is connected to the temperature indicator output before the conversion is performed. In addition, the user must wait 200  $\mu s$  between sequential conversions of the temperature indicator output.

TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE TEMPERATURE INDICATOR

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register on page |

|--------|-------|--------|-------|-------|-------|-------|-------|--------|------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG |       | _     | ADFV  | R<1:0> | 118              |

**Legend:** Shaded cells are unused by the temperature indicator module.

# 15.2.6 INDIVIDUAL ADC CONVERSION PROCEDURE

This is an example procedure for using the ADCx to perform an Analog-to-Digital conversion:

- Configure Port:

- Disable pin output driver (Refer to the TRISx register)

- Configure pin as analog (Refer to the ANSELx register)

- Disable weak pull-ups either globally (refer to the OPTION\_REG register) or individually (Refer to the appropriate WPUx register)

- 2. Configure the ADCx module:

- · Select ADCx conversion clock

- · Configure voltage reference

- · Select ADCx input channel

- Turn on ADCx module

- 3. Configure ADCx interrupt (optional):

- · Clear ADCx interrupt flag

- Enable ADCx interrupt

- · Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONEx bit.

- Wait for ADCx conversion to complete by one of the following:

- Polling the GO/DONEx bit

- Waiting for the ADCx interrupt (interrupts enabled)

- 7. Read ADCx Result.

- Clear the ADCx interrupt flag (required if interrupt is enabled).

- **Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

- 2: Refer to Section 15.4 "ADC Acquisition Requirements".

## **EXAMPLE 15-1: ADC CONVERSION**

```

;This code block configures the ADC1

;for polling, Vdd and Vss references, FRC

;oscillator and ANO input.

; Conversion start and polling for completion

; are included.

BANKSEL

ADCON1

B'11110000' ; Right justify, FRC

W.TVOM

;oscillator

MOVWF

ADCON1

; VDD is VREFH

BANKSEL

TRISA

BSF

TRISA,0

;Set RAO to input

BANKSEL

ANSELA

BSF

ANSELA,0

;Set RAO to analog

BANKSEL

WPUA

BCF

WPUA,0

;Disable RAO weak

pull-up

BANKSEL

ADCON0

B'00000001' ;Select channel AN0

MOVLW

MOVWF

ADCON0

;Turn ADC On

MOVLW

MOVWF

AAD1ACO

;Acquisiton delay

BSF

ADCON0, ADGO ; Start conversion

BTFSC

ADCON0, ADGO ; Is conversion done?

GOTO

$-1

;No, test again

AD1RES0H

BANKSEL

;

AD1RESOH,W ;Read upper 2 bits

MOVF

RESULTHI

MOVWF

;store in GPR space

BANKSEL

AD1RESOL

MOVF

AD1RESOL,W

;Read lower 8 bits

MOVWF

RESULTLO

;Store in GPR space

```

# REGISTER 16-4: AAD2CH: HARDWARE CVD 2 SECONDARY CHANNEL SELECT REGISTER<sup>(1,2,3,4)</sup>

| U-0   | R/W-0/0 |

|-------|---------|---------|---------|---------|---------|---------|---------|

| _     | CH26    | CH25    | CH24    | CH23    | CH22    | CH21    | CH20    |

| bit 7 |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7 | Unimplemented: Read as '0'                                                                                             |  |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| bit 6 | CH26: Channel 26 to ADC2 Connection bit <sup>(5)</sup> 1 = AN26 is connected to ADC2 0 = AN26 is not connected to ADC2 |  |  |  |  |  |

| bit 5 | CH25: Channel 25 to ADC2 Connection bit <sup>(5)</sup> 1 = AN25 is connected to ADC2 0 = AN25 is not connected to ADC2 |  |  |  |  |  |

| bit 4 | CH24: Channel 24 to ADC2 Connection bit <sup>(5)</sup> 1 = AN24 is connected to ADC2 0 = AN24 is not connected to ADC2 |  |  |  |  |  |

| bit 3 | CH23: Channel 23 to ADC2 Connection bit<br>1 = AN23 is connected to ADC2<br>0 = AN23 is not connected to ADC2          |  |  |  |  |  |

| bit 2 | CH22: Channel 22 to ADC2 Connection bit<br>1 = AN22 is connected to ADC2<br>0 = AN22 is not connected to ADC2          |  |  |  |  |  |

| bit 1 | CH21: Channel 21 to ADC2 Connection bit  1 = AN21 is connected to ADC2  0 = AN21 is not connected to ADC2              |  |  |  |  |  |

| bit 0 | CH20: Channel 20 to ADC2 Connection bit<br>1 = AN20 is connected to ADC2<br>0 = AN20 is not connected to ADC2          |  |  |  |  |  |

**Note 1:** This register selects secondary channels which are connected in parallel to the primary channel selected in AAD2CON0. Precharge bias is applied to both the primary and secondary channels.

- **2:** If the same channel is selected as both primary and secondary then the selection as primary takes precedence.

- 3: Enabling these bits automatically overrides the corresponding TRIS bit to tri-state the selected pin.

- **4:** In the same way that the CHS bits in AAD2CON0 only close the switch when the ADC is enabled, these connections and the TRISx overrides are only active if the ADC is enabled by setting ADxON.

- 5: PIC16LF1559 only. Unimplemented/Read as '0' on PIC16LF1554.

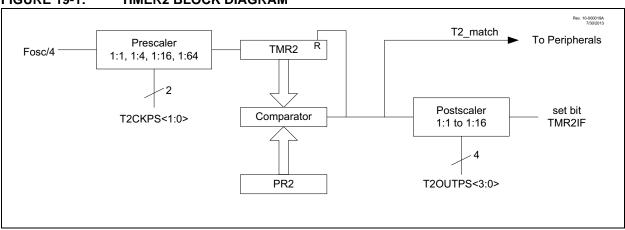

### 19.0 TIMER2 MODULE

The Timer2 module incorporates the following features:

- 8-bit Timer and Period registers (TMR2 and PR2, respectively)

- · Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16, and 1:64)

- Software programmable postscaler (1:1 to 1:16)

- · Interrupt on TMR2 match with PR2

See Figure 19-1 for a block diagram of Timer2.

## FIGURE 19-1: TIMER2 BLOCK DIAGRAM

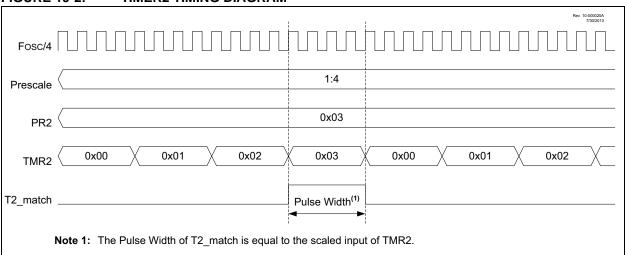

## FIGURE 19-2: TIMER2 TIMING DIAGRAM

## 20.3 I<sup>2</sup>C MODE OVERVIEW

The Inter-Integrated Circuit Bus ( $I^2C$ ) is a multi-master serial data communication bus. Devices communicate in a master/slave environment where the master devices initiate the communication. A Slave device is controlled through addressing.

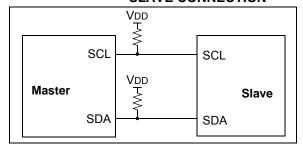

The I<sup>2</sup>C bus specifies two signal connections:

- · Serial Clock (SCL)

- · Serial Data (SDA)

Figure 20-2 and Figure 20-3 show the block diagrams of the MSSP module when operating in I<sup>2</sup>C mode.

Both the SCL and SDA connections are bidirectional open-drain lines, each requiring pull-up resistors for the supply voltage. Pulling the line to ground is considered a logical zero and letting the line float is considered a logical one.

Figure 20-11 shows a typical connection between two processors configured as master and slave devices.

The I<sup>2</sup>C bus can operate with one or more master devices and one or more slave devices.

There are four potential modes of operation for a given device:

- Master Transmit mode (master is transmitting data to a slave)

- Master Receive mode (master is receiving data from a slave)

- Slave Transmit mode (slave is transmitting data to a master)

- Slave Receive mode (slave is receiving data from the master)

To begin communication, a master device starts out in Master Transmit mode. The master device sends out a Start bit followed by the address byte of the slave it intends to communicate with. This is followed by a single Read/Write bit, which determines whether the master intends to transmit to or receive data from the slave device.

If the requested slave exists on the bus, it will respond with an Acknowledge bit, otherwise known as an ACK. The master then continues in either Transmit mode or Receive mode and the slave continues in the complement, either in Receive mode or Transmit mode, respectively.

A Start bit is indicated by a high-to-low transition of the SDA line while the SCL line is held high. Address and data bytes are sent out, Most Significant bit (MSb) first. The Read/Write bit is sent out as a logical one when the master intends to read data from the slave, and is sent out as a logical zero when it intends to write data to the slave.

## FIGURE 20-11: I<sup>2</sup>C MASTER/ SLAVE CONNECTION

The Acknowledge bit (ACK) is an active-low signal, which holds the SDA line low to indicate to the transmitter that the slave device has received the transmitted data and is ready to receive more.

The transition of a data bit is always performed while the SCL line is held low. Transitions that occur while the SCL line is held high are used to indicate Start and Stop bits.