Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

EXF

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 11                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                            |

| Supplier Device Package    | 14-TSSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1554-i-st |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                                    | Function | Input<br>Type    | Output<br>Type | Description                            |

|-------------------------------------------------------------------------|----------|------------------|----------------|----------------------------------------|

|                                                                         | RA0      | TTL              | CMOS           | General Purpose I/O                    |

|                                                                         | AN0      | AN               | —              | ADC Channel Input                      |

| RA0/AN0/ISCPDAT/ICDDAT                                                  | ICSPDAT  | ST               | CMOS           | ICSP™ Data I/O                         |

|                                                                         | ICDDAT   | ST               | CMOS           | In-Circuit Debug Data                  |

|                                                                         | RA1      | TTL              | CMOS           | General Purpose I/O                    |

|                                                                         | AN1      | AN               | _              | ADC Channel Input                      |

| RA1/AN1/VREF+/ICSPCLK/ICDCLK                                            | VREF+    | AN               | _              | ADC Positive Voltage Reference Input   |

|                                                                         | ICSPCLK  | ST               | CMOS           | ICSP Programming Clock                 |

|                                                                         | ICDCLK   | ST               | CMOS           | In-Circuit Debug Clock                 |

|                                                                         | RA2      | TTL              | CMOS           | General Purpose I/O                    |

|                                                                         | AN2      | AN               | _              | ADC Channel Input                      |

| RA2/AN2/TOCKI/INT                                                       | TOCKI    | ST               | _              | Timer0 Clock Input                     |

|                                                                         | INT      | ST               | _              | External Interrupt                     |

|                                                                         | RA3      | TTL              | CMOS           | General Purpose Input with IOC and WPU |

|                                                                         | Vpp      | HV               | _              | Programming Voltage                    |

| DADB ( (00)(1)(00 (1)(00)(1)(1)(1)(1)(1)(1)(1)(1)(1)(1)(1)(1)(1)        | SS       | ST               | —              | Slave Select Input                     |

| RA3/VPP/SS <sup>(1)</sup> /SDA <sup>(1)</sup> /SDI <sup>(1)</sup> /MCLR | SDA      | l <sup>2</sup> C | OD             | I <sup>2</sup> C Data Input/Output     |

|                                                                         | SDI      | CMOS             | —              | SPI Data Input                         |

|                                                                         | MCLR     | ST               | —              | Master Clear with Internal Pull-up     |

|                                                                         | RA4      | TTL              | CMOS           | General Purpose I/O                    |

|                                                                         | AN10     | AN               | —              | ADC Channel Input                      |

| RA4/AN10/ADTRIG/CLKOUT/T1G                                              | ADTRIG   | ST               | —              | ADC Conversion Trigger Input           |

|                                                                         | CLKOUT   | —                | CMOS           | Fosc/4 Output                          |

|                                                                         | T1G      | ST               | _              | Timer1 Gate input.                     |

|                                                                         | RA5      | TTL              | CMOS           | General Purpose I/O                    |

|                                                                         | AN20     | AN               | _              | ADC Channel Input                      |

| RA5/AN20/CLKIN/T1CKI                                                    | CLKIN    | CMOS             | —              | External Clock Input (EC mode)         |

|                                                                         | T1CKI    | ST               | _              | Timer1 clock Input                     |

|                                                                         | RB4      | TTL              | CMOS           | General Purpose I/O                    |

|                                                                         | AN26     | AN               | _              | ADC Channel Input                      |

| RB4/AN26/SDA <sup>(1)</sup> /SDI <sup>(1)</sup>                         | SDA      | l <sup>2</sup> C | OD             | I <sup>2</sup> C Data Input/Output     |

|                                                                         | SDI      | CMOS             | _              | SPI Data Input                         |

TARI E 1-3. PIC16LE1559 PINOUT DESCRIPTION

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$ HV = High Voltage XTAL = Crystal

levels

Note 1: Alternate pin function selected with the APFCON (Register 11-1) register.

| Address       | Name                  | Bit 7        | Bit 6                                                                                                  | Bit 5           | Bit 4            | Bit 3                   | Bit 2        | Bit 1          | Bit 0         | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------------|-----------------------|--------------|--------------------------------------------------------------------------------------------------------|-----------------|------------------|-------------------------|--------------|----------------|---------------|-----------------------|---------------------------------|

| Bank 0        |                       |              |                                                                                                        |                 |                  |                         |              |                |               |                       |                                 |

| 000h          | INDF0 <sup>(1)</sup>  | Addressing t | Addressing this location uses contents of FSR0H/FSR0L to address data memory (not a physical register) |                 |                  |                         |              |                |               |                       | uuuu uuuu                       |

| 001h          | INDF1 <sup>(1)</sup>  | Addressing t | his location us                                                                                        | es contents of  | FSR1H/FSR1       | L to address            | data memory  | y (not a physi | cal register) | xxxx xxxx             | uuuu uuuu                       |

| 002h          | PCL <sup>(1)</sup>    |              |                                                                                                        | Program C       | Counter (PC) L   | east Significa          | int Byte     |                |               | 0000 0000             | 0000 0000                       |

| 003h          | STATUS <sup>(1)</sup> | —            | _                                                                                                      | —               | TO               | PD                      | Z            | DC             | С             | 1 1000                | q quuu                          |

| 004h          | FSR0L <sup>(1)</sup>  |              |                                                                                                        | Indirect Da     | ata Memory Ac    | ldress 0 Low            | Pointer      |                |               | 0000 0000             | uuuu uuuu                       |

| 005h          | FSR0H <sup>(1)</sup>  |              |                                                                                                        | Indirect Da     | ta Memory Ad     | dress 0 High            | Pointer      |                |               | 0000 0000             | 0000 0000                       |

| 006h          | FSR1L <sup>(1)</sup>  |              |                                                                                                        | Indirect Da     | ata Memory Ac    | ldress 1 Low            | Pointer      |                |               | 0000 0000             | uuuu uuuu                       |

| 007h          | FSR1H <sup>(1)</sup>  |              |                                                                                                        | Indirect Da     | ta Memory Ad     | dress 1 High            | Pointer      |                |               | 0000 0000             | 0000 0000                       |

| 008h          | BSR <sup>(1)</sup>    | _            | _                                                                                                      | _               |                  |                         | BSR<4:0>     |                |               | 0 0000                | 0 0000                          |

| 009h          | WREG <sup>(1)</sup>   |              |                                                                                                        |                 | Working R        | egister                 |              |                |               | 0000 0000             | uuuu uuuu                       |

| 00Ah          | PCLATH <sup>(1)</sup> | _            |                                                                                                        | Write Bu        | ffer for the upp | er 7 bits of th         | ne Program C | ounter         |               | -000 0000             | -000 0000                       |

| 00Bh          | INTCON <sup>(1)</sup> | GIE          | PEIE                                                                                                   | TMR0IE          | INTE             | IOCIE                   | TMR0IF       | INTF           | IOCIF         | 0000 0000             | 0000 0000                       |

| 00Ch          | PORTA                 | _            | -                                                                                                      | RA5             | RA4              | RA3                     | RA2          | RA1            | RA0           | xx xxxx               | xx xxxx                         |

|               | PORTB <sup>(2)</sup>  |              |                                                                                                        |                 | Unimplem         | ented                   |              |                |               | _                     | _                               |

| 00Dh          | PORTB <sup>(3)</sup>  | RB7          | RB6                                                                                                    | RB5             | RB4              | —                       | —            | —              | —             | xxxx                  | xxxx                            |

| 00 <b>C</b> h | PORTC <sup>(2)</sup>  | _            | _                                                                                                      | RC5             | RC4              | RC3                     | RC2          | RC1            | RC0           | xx xxxx               | xx xxxx                         |

| 00Eh          | PORTC <sup>(3)</sup>  | RC7          | RC6                                                                                                    | RC5             | RC4              | RC3                     | RC2          | RC1            | RC0           | XXXX XXXX             | xxxx xxxx                       |

| 011h          | PIR1                  | TMR1GIF      | AD1IF                                                                                                  | RCIF            | TXIF             | SSP1IF                  | _            | TMR2IF         | TMR1IF        | 0000 0-00             | 0000 0-00                       |

| 012h          | PIR2                  | _            | AD2IF                                                                                                  | _               | _                | BCLIF                   | _            | _              | _             | -0 0                  | -0 0                            |

| 015h          | TMR0                  |              |                                                                                                        |                 | Timer0 Modul     | e Register              |              |                |               | XXXX XXXX             | uuuu uuuu                       |

| 016h          | TMR1L                 |              | Holding R                                                                                              | egister for the | Least Signific   | ant Byte of th          | e 16-bit TMR | 1 Count        |               | XXXX XXXX             | uuuu uuuu                       |

| 017h          | TMR1H                 |              | Holding R                                                                                              | egister for the | Most Significa   | ant Byte of the         | e 16-bit TMR | 1 Count        |               | XXXX XXXX             | uuuu uuuu                       |

| 018h          | T1CON                 | TMR1C        | S<1:0>                                                                                                 | T1CKP           | S<1:0>           | _                       | T1SYNC       | _              | TMR10N        | 0000 -0-0             | uuuu -u-u                       |

| 019h          | T1GCON                | TMR1GE       | T1GPOL                                                                                                 | T1GTM           | T1GSPM           | T <u>1GGO</u> /<br>DONE | T1GVAL       | _              | T1GSS         | 0000 0x-0             | uuuu ux-u                       |

| 01Ah          | TMR2                  |              |                                                                                                        |                 | Timer 2 Modul    | e Register              |              |                |               | 0000 0000             | 0000 0000                       |

| 01Bh          | PR2                   |              |                                                                                                        |                 | Timer 2 Perio    | d Register              |              |                |               | 1111 1111             | 1111 1111                       |

| 01Ch          | T2CON                 | _            |                                                                                                        | T2OUTP          | 'S<3:0>          |                         | TMR2ON       | T2CKF          | 'S<1:0>       | -000 0000             | -000 0000                       |

| 01Dh          | —                     |              |                                                                                                        |                 | Unimplem         | ented                   |              |                |               | _                     | _                               |

| 01Eh          | —                     |              |                                                                                                        |                 | Unimplem         | ented                   |              |                |               | —                     | _                               |

| 01Fh          | —                     |              |                                                                                                        |                 | Unimplem         | ented                   |              |                |               | _                     | _                               |

| l ogond:      |                       | u = unchange |                                                                                                        |                 |                  |                         |              |                |               |                       |                                 |

#### **TABLE 3-9:** SPECIAL FUNCTION REGISTER SUMMARY

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Note 1: These registers can be accessed from any bank. 2: PIC16I E1554

PIC16LF1554. 2:

3: PIC16LF1559.

These registers/bits are available at two address locations, in Bank 1 and Bank 14. 4:

| Address | Name                                  | Bit 7                                       | Bit 6                                                                                                  | Bit 5          | Bit 4           | Bit 3           | Bit 2           | Bit 1         | Bit 0          | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |  |

|---------|---------------------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------|-----------------|-----------------|-----------------|---------------|----------------|-----------------------|---------------------------------|--|

| Bank 14 |                                       |                                             | •                                                                                                      |                |                 | •               |                 |               |                |                       | •                               |  |

| 700h    | INDF0 <sup>(1)</sup>                  | Addressing t                                | this location us                                                                                       | es contents of | FSR0H/FSR0      | L to address    | data memory     | / (not a phys | ical register) | xxxx xxxx             | uuuu uuuu                       |  |

| 701h    | INDF1 <sup>(1)</sup>                  | Addressing t                                | Addressing this location uses contents of FSR1H/FSR1L to address data memory (not a physical register) |                |                 |                 |                 |               |                |                       |                                 |  |

| 702h    | PCL <sup>(1)</sup>                    | Program Counter (PC) Least Significant Byte |                                                                                                        |                |                 |                 |                 |               |                |                       | 0000 0000                       |  |

| 703h    | STATUS <sup>(1)</sup>                 | _                                           | _                                                                                                      | —              | TO              | PD              | Z               | DC            | С              | 1 1000                | q quuu                          |  |

| 704h    | FSR0L <sup>(1)</sup>                  |                                             |                                                                                                        | Indirect Da    | ta Memory Ad    | Idress 0 Low    | Pointer         |               | •              | 0000 0000             | uuuu uuuu                       |  |

| 705h    | FSR0H <sup>(1)</sup>                  |                                             |                                                                                                        | Indirect Da    | ta Memory Ad    | dress 0 High    | Pointer         |               |                | 0000 0000             | 0000 0000                       |  |

| 706h    | FSR1L <sup>(1)</sup>                  |                                             |                                                                                                        | Indirect Da    | ta Memory Ad    | Idress 1 Low    | Pointer         |               |                | 0000 0000             | uuuu uuuu                       |  |

| 707h    | FSR1H <sup>(1)</sup>                  |                                             |                                                                                                        | Indirect Da    | ta Memory Ad    | dress 1 High    | Pointer         |               |                | 0000 0000             | 0000 0000                       |  |

| 708h    | BSR <sup>(1)</sup>                    | _                                           | —                                                                                                      | —              |                 |                 | BSR<4:0>        |               |                | 0 0000                | 0 0000                          |  |

| 709h    | WREG <sup>(1)</sup>                   |                                             |                                                                                                        |                | Working R       | egister         |                 |               |                | 0000 0000             | uuuu uuuu                       |  |

| 70Ah    | PCLATH <sup>(1)</sup>                 | -                                           |                                                                                                        | Write But      | fer for the upp | er 7 bits of th | ne Program C    | ounter        |                | -000 0000             | -000 0000                       |  |

| 70Bh    | INTCON <sup>(1)</sup>                 | GIE                                         | PEIE                                                                                                   | TMR0IE         | INTE            | IOCIE           | TMR0IF          | INTF          | IOCIF          | 0000 000x             | 0000 000u                       |  |

| 70Ch    | _                                     |                                             |                                                                                                        |                | Unimplem        | ented           |                 |               | •              | _                     | —                               |  |

| 70Dh    | _                                     |                                             | Unimplemented                                                                                          |                |                 |                 |                 |               |                |                       |                                 |  |

| 70Eh    | _                                     |                                             | Unimplemented                                                                                          |                |                 |                 |                 |               |                |                       | —                               |  |

| 70Fh    | _                                     |                                             |                                                                                                        |                | Unimplem        | ented           |                 |               |                | _                     | _                               |  |

| 710h    | _                                     |                                             |                                                                                                        |                | Unimplem        | ented           |                 |               |                | _                     | _                               |  |

| 711h    | AD1CON0/<br>AAD1CON0 <sup>(4)</sup>   | _                                           | CHS4                                                                                                   | CHS3           | CHS2            | CHS1            | CHS0            | GO/DONE1      | AD10N          | -000 0000             | -000 0000                       |  |

| 712h    | AADCON1/<br>ADCOMCON <sup>(4)</sup>   | ADFM                                        |                                                                                                        | ADCS<2:0>      |                 | _               | GO/<br>DONE_ALL | ADPRI         | EF<1:0>        | 0000 -000             | 0000 -000                       |  |

| 713h    | AD1CON2/<br>AAD1CON2 <sup>(4)</sup>   | _                                           | ٢                                                                                                      | RIGSEL<2:0>    | •               | _               | _               | _             | _              | -000                  | -000                            |  |

| 714h    | AAD1CON3                              | AD1EPPOL                                    | AD1IPPOL                                                                                               | _              | —               | —               | _               | AD1IPEN       | AD1DSEN        | 0000                  | 0000                            |  |

| 715h    | AADSTAT                               | _                                           | AD2CONV                                                                                                | AD2ST          | G<1:0>          | _               | AD1CONV         | AD1ST         | G<1:0>         | -000 -000             | -000 -000                       |  |

| 716h    | AAD1PRE                               | _                                           |                                                                                                        |                | AD              | 01PRE<6:0>      |                 |               |                | -000 0000             | -000 0000                       |  |

| 717h    | AAD1ACQ                               | -                                           |                                                                                                        |                | AA              | D1ACQ<6:0>      |                 |               |                | -000 0000             | -000 0000                       |  |

| 718h    | AAD1GRD                               | GRD1BOE                                     | GRD1AOE                                                                                                | GRD1POL        | _               | _               | _               | _             | _              | 000                   | 000                             |  |

| 719h    | AAD1CAP                               | _                                           | _                                                                                                      | -              |                 |                 | ADD1C/          | AP<3:0>       | •              | 0000                  | 0000                            |  |

| 71Ah    | AD1RES0L/<br>AAD1RES0L <sup>(4)</sup> |                                             |                                                                                                        | AI             | DC Result 0 R   | egister Low     |                 |               |                | xxxx xxxx             | uuuu uuuu                       |  |

| 71Bh    | AD1RES0H/<br>AAD1RES0H <sup>(4)</sup> |                                             |                                                                                                        | A              | DC Result 0 R   | egister High    |                 |               |                | xxxx xxxx             | uuuu uuuu                       |  |

| 71Ch    | AD1RES1L/<br>AAD1RES1L                |                                             |                                                                                                        | AI             | DC Result 1 R   | egister Low     |                 |               |                | xxxx xxxx             | uuuu uuuu                       |  |

| 71Dh    | AD1RES1H/<br>AAD1RES1H                |                                             |                                                                                                        | A              | DC Result 1 R   | egister High    |                 |               |                | xxxx xxxx             | uuuu uuuu                       |  |

| 7156    | AAD1CH <sup>(2)</sup>                 | _                                           | _                                                                                                      | _              | _               | CH13            | CH12            | CH11          | CH10           | 0000                  | 0000                            |  |

| 71Eh    | AAD1CH <sup>(3)</sup>                 | _                                           | CH16                                                                                                   | CH15           | CH14            | CH13            | CH12            | CH11          | CH10           | -000 0000             | -000 0000                       |  |

| 71Fh    | —                                     |                                             |                                                                                                        |                | Unimplem        | ented           |                 |               |                | —                     | —                               |  |

#### **TABLE 3-9:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Note

1: These registers can be accessed from any bank.

PIC16LF1554. 2:

3: PIC16LF1559.

These registers/bits are available at two address locations, in Bank 1 and Bank 14. 4:

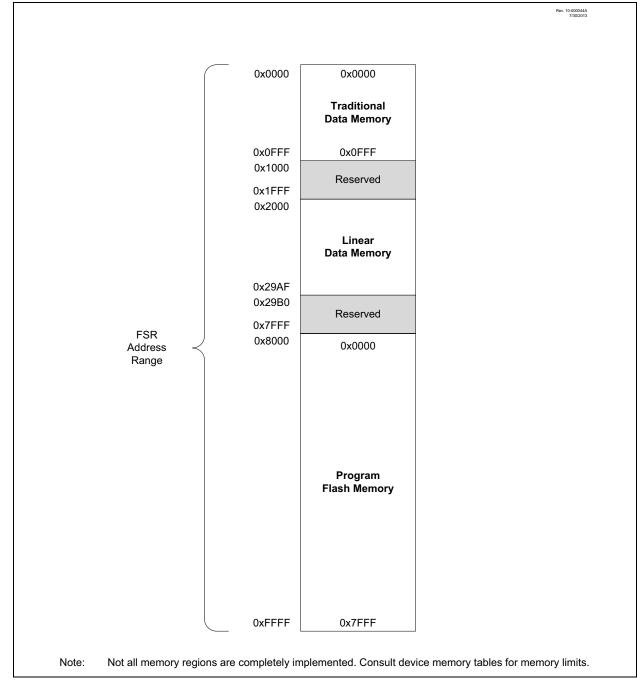

### 3.5 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

FIGURE 3-9: INDIRECT ADDRESSING

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- Traditional Data Memory

- Linear Data Memory

- Program Flash Memory

#### 6.1 **Power-on Reset (POR)**

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

#### 6.1.1 POWER-UP TIMER (PWRT)

The Power-up Timer provides a nominal 64 ms time-out on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Words.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00000607).

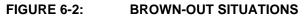

#### 6.2 Brown-out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- BOR is always on

- BOR is off when in Sleep

- BOR is controlled by software

- · BOR is always off

Refer to Table 6-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 6-2 for more information.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Instruction Execution upon:<br>Release of POR or Wake-up from Sleep |

|------------|--------|-------------|----------|---------------------------------------------------------------------|

| 11         | Х      | Х           | Active   | Waits for BOR ready <sup>(1)</sup><br>(BORRDY = 1)                  |

| 1.0        |        | Awake       | Active   | Waits for BOR ready                                                 |

| 10         | X      | Sleep       | Disabled | (BORRDY = 1)                                                        |

| 01         | 1      | х           | Active   | Waits for BOR ready <sup>(1)</sup><br>(BORRDY = 1)                  |

|            | 0      | х           | Disabled | Begins immediately                                                  |

| 00         | Х      | х           | Disabled | (BORRDY = x)                                                        |

TABLE 6-1:BOR OPERATING MODES

**Note 1:** In these specific cases, "release of POR" and "wake-up from Sleep," there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

### 6.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 6.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

### 6.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

# 6.3 Register Definitions: BOR Control

### REGISTER 6-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u | R/W-0/u | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|---------|---------|-----|-----|-----|-----|-----|--------|

| SBOREN  | BORFS   | —   | _   | —   | —   | —   | BORRDY |

| bit 7   |         |     |     |     |     |     | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | SBOREN: Software Brown-Out Reset Enable bit<br><u>If BOREN &lt;1:0&gt; in Configuration Words = 01</u> :<br>1 = BOR Enabled<br>0 = BOR Disabled<br><u>If BOREN &lt;1:0&gt; in Configuration Words ≠ 01</u> :<br>SBOREN is read/write, but has no effect on the BOR                                                                                                                                                             |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | BORFS: Brown-Out Reset Fast Start bit <sup>(1)</sup><br><u>If BOREN &lt;1:0&gt; = 10 (Disabled in Sleep) or BOREN&lt;1:0&gt; = 01 (Under software control):</u><br>1 = Band gap is forced on always (covers sleep/wake-up/operating cases)<br>0 = Band gap operates normally, and may turn off<br><u>If BOREN&lt;1:0&gt; = 11 (Always on) or BOREN&lt;1:0&gt; = 00 (Always off)</u><br>BORFS is Read/Write, but has no effect. |

| bit 5-1 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                     |

| bit 0   | <b>BORRDY:</b> Brown-Out Reset Circuit Ready Status bit<br>1 = The Brown-out Reset circuit is active<br>0 = The Brown-out Reset circuit is inactive                                                                                                                                                                                                                                                                            |

| Note 1: | BOREN<1:0> bits are located in Configuration Words.                                                                                                                                                                                                                                                                                                                                                                            |

# 6.13 Power Control (PCON) Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-On Reset (POR)

- Brown-Out Reset (BOR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

The PCON register bits are shown in Register 6-2.

# 6.14 Register Definitions: Power Control

#### REGISTER 6-2: PCON: POWER CONTROL REGISTER

| R/W/HS-0/q | R/W/HS-0/q | U-0 | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|-----|------------|------------|------------|------------|------------|

| STKOVF     | STKUNF     | —   | RWDT       | RMCLR      | RI         | POR        | BOR        |

| bit 7      |            |     | •          |            |            |            | bit 0      |

| Legend:                    |                      |                                                       |

|----------------------------|----------------------|-------------------------------------------------------|

| HC = Bit is cleared by har | dware                | HS = Bit is set by hardware                           |

| R = Readable bit           | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged       | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set           | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7 | STKOVF: Stack Overflow Flag bit                                                                                                   |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = A Stack Overflow occurred                                                                                                     |

|       | 0 = A Stack Overflow has not occurred or cleared by firmware                                                                      |

| bit 6 | STKUNF: Stack Underflow Flag bit                                                                                                  |

|       | 1 = A Stack Underflow occurred                                                                                                    |

|       | 0 = A Stack Underflow has not occurred or cleared by firmware                                                                     |

| bit 5 | Unimplemented: Read as '0'                                                                                                        |

| bit 4 | RWDT: Watchdog Timer Reset Flag bit                                                                                               |

|       | 1 = A Watchdog Timer Reset has not occurred or set by firmware                                                                    |

|       | 0 = A Watchdog Timer Reset has occurred (cleared by hardware)                                                                     |

| bit 3 | RMCLR: MCLR Reset Flag bit                                                                                                        |

|       | 1 = A MCLR Reset has not occurred or set by firmware                                                                              |

|       | 0 = A MCLR Reset has occurred (cleared by hardware)                                                                               |

| bit 2 | RI: RESET Instruction Flag bit                                                                                                    |

|       | 1 = A RESET instruction has not been executed or set by firmware                                                                  |

|       | 0 = A RESET instruction has been executed (cleared by hardware)                                                                   |

| bit 1 | POR: Power-On Reset Status bit                                                                                                    |

|       | 1 = No Power-on Reset occurred                                                                                                    |

|       | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)                                             |

| bit 0 | BOR: Brown-Out Reset Status bit                                                                                                   |

|       | 1 = No Brown-out Reset occurred                                                                                                   |

|       | <ul> <li>0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset<br/>occurs)</li> </ul> |

|       |                                                                                                                                   |

| Name   | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0  | Register<br>on Page |

|--------|--------|--------|-------|-------|-------|--------|-------|--------|---------------------|

| BORCON | SBOREN | BORFS  |       |       |       |        |       | BORRDY | 66                  |

| PCON   | STKOVF | STKUNF |       | RWDT  | RMCLR | RI     | POR   | BOR    | 70                  |

| STATUS |        | _      |       | TO    | PD    | Z      | DC    | С      | 22                  |

| WDTCON | _      |        |       | V     |       | SWDTEN | 86    |        |                     |

TABLE 6-5:

SUMMARY OF REGISTERS ASSOCIATED WITH RESETS<sup>(1)</sup>

**Legend:** — = unimplemented bit, reads as '0'. Shaded cells are not used by Resets.

**Note 1:** Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4   | Bit 11/3  | Bit 10/2 | Bit 9/1     | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|------------|-----------|----------|-------------|---------|---------------------|

|         | 13:8 | _       |         | _        | - CLKOUTEN |           | BORE     | N<1:0> —    |         | 50                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WD         | WDTE<1:0> |          | — FOSC<1:0> |         | 53                  |

|         | 13:8 | _       | _       | LVP      | DEBUG      | LPBOR     | BORV     | STVREN      | _       | - 1                 |

| CONFIG2 | 7:0  |         | _       |          |            |           | _        | WRT         | <1:0>   | 54                  |

TABLE 6-6: SUMMARY OF CONFIGURATION WORD WITH RESETS

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

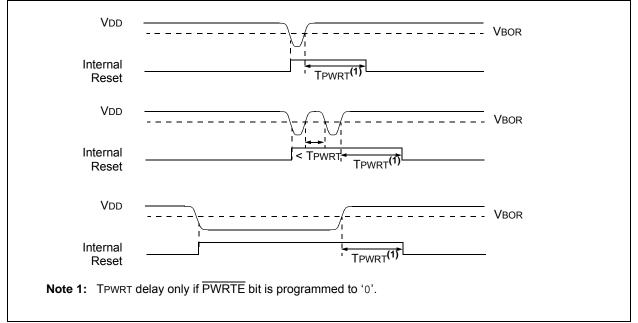

# 7.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is three or four instruction cycles. For asynchronous interrupts, the latency is three to five instruction cycles, depending on when the interrupt occurs. See Figure 7-2 and Figure 7-3 for more details.

#### FIGURE 7-2: INTERRUPT LATENCY

| REGISTE        | R 7-4: PIF | R1: PERIPHERA                               | L INTERRU          | PT REQUEST       | REGISTER        | 1                 |             |  |  |  |

|----------------|------------|---------------------------------------------|--------------------|------------------|-----------------|-------------------|-------------|--|--|--|

| R/W-0/0        | ) R/W-0/   | 0 R/W-0/0                                   | R/W-0/0            | R/W-0/0          | U-0             | R/W-0/0           | R/W-0/0     |  |  |  |

| TMR1GI         | F AD1IF    | RCIF                                        | TXIF               | SSP1IF           | —               | TMR2IF            | TMR1IF      |  |  |  |

| bit 7          |            |                                             |                    |                  |                 |                   | bit         |  |  |  |

| Legend:        |            |                                             |                    |                  |                 |                   |             |  |  |  |

| R = Reada      | ble bit    | W = Writable                                | bit                | U = Unimpler     | nented bit, rea | d as '0'          |             |  |  |  |

| u = Bit is u   |            | x = Bit is unk                              |                    | •                |                 | DR/Value at all c | ther Resets |  |  |  |

| '1' = Bit is s | •          | '0' = Bit is cle                            | ared               |                  |                 |                   |             |  |  |  |

|                |            |                                             |                    |                  |                 |                   |             |  |  |  |

| bit 7          |            | Timer1 Gate Inte                            | errupt Flag bit    |                  |                 |                   |             |  |  |  |

|                |            | upt is pending<br>upt is not pending        |                    |                  |                 |                   |             |  |  |  |

| bit 6          |            | DC 1 Interrupt Flag                         | n hit              |                  |                 |                   |             |  |  |  |

| bit 0          |            | upt is pending                              | y on               |                  |                 |                   |             |  |  |  |

|                |            | upt is not pending                          |                    |                  |                 |                   |             |  |  |  |

| bit 5          | RCIF: US   | ART Receive Inte                            | rrupt Flag bit     |                  |                 |                   |             |  |  |  |

|                |            | upt is pending                              |                    |                  |                 |                   |             |  |  |  |

| L:1            |            | upt is not pending                          | www.wat. Elean hit |                  |                 |                   |             |  |  |  |

| bit 4          |            | ART Transmit Inte<br>upt is pending         | rrupt Flag bit     |                  |                 |                   |             |  |  |  |

|                |            | upt is not pending                          |                    |                  |                 |                   |             |  |  |  |

| bit 3          | SSP1IF:    | Synchronous Seria                           | al Port (MSSP      | ) Interrupt Flag | bit             |                   |             |  |  |  |

|                |            | upt is pending                              |                    |                  |                 |                   |             |  |  |  |

|                |            | upt is not pending                          |                    |                  |                 |                   |             |  |  |  |

| bit 2          | -          | <b>nented:</b> Read as                      |                    |                  |                 |                   |             |  |  |  |

| bit 1          |            | Timer2 to PR2 Inte                          | errupt Flag bit    |                  |                 |                   |             |  |  |  |

|                |            | upt is pending<br>upt is not pending        |                    |                  |                 |                   |             |  |  |  |

| bit 0          |            | TMR1IF: Timer1 Overflow Interrupt Flag bit  |                    |                  |                 |                   |             |  |  |  |

|                |            | upt is pending                              |                    |                  |                 |                   |             |  |  |  |

|                | 0 = Interr | upt is not pending                          |                    |                  |                 |                   |             |  |  |  |

| N. (           |            | · · · · · · · · · · ·                       |                    |                  |                 |                   |             |  |  |  |

| Note:          |            | its are set when ar<br>rs, regardless of th |                    |                  |                 |                   |             |  |  |  |

|                |            | ing enable bit or th                        |                    |                  |                 |                   |             |  |  |  |

### REGISTER 7-4: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| Note: | Interrupt flag bits are set when an interrupt   |

|-------|-------------------------------------------------|

|       | condition occurs, regardless of the state of    |

|       | its corresponding enable bit or the Global      |

|       | Interrupt Enable bit, GIE of the INTCON         |

|       | register. User software should ensure the       |

|       | appropriate interrupt flag bits are clear prior |

|       | to enabling an interrupt.                       |

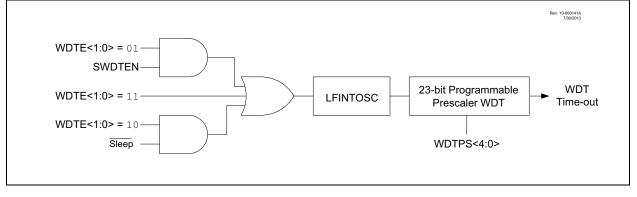

# 9.0 WATCHDOG TIMER (WDT)

The Watchdog Timer is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events.

The WDT has the following features:

- Independent clock source

- Multiple operating modes

- WDT is always on

- WDT is off when in Sleep

- WDT is controlled by software

- WDT is always off

- Configurable time-out period is from 1 ms to 256 seconds (nominal)

- Multiple Reset conditions

- Operation during Sleep

### FIGURE 9-1: WATCHDOG TIMER BLOCK DIAGRAM

#### EXAMPLE 10-2: ERASING ONE ROW OF PROGRAM MEMORY

- ; This row erase routine assumes the following:

- ; 1. A valid address within the erase row is loaded in ADDRH:ADDRL

; 2. ADDRH and ADDRL are located in shared data memory 0x70 - 0x7F (common RAM)

|                      | BCF                      | INTCON,GIE                                | ; Disable ints so required sequences will execute properly                                                         |

|----------------------|--------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

|                      | BANKSEL<br>MOVF<br>MOVWF | PMADRL<br>ADDRL,W<br>PMADRL               | ; Load lower 8 bits of erase address boundary                                                                      |

|                      | MOVF<br>MOVF             | ADDRH,W<br>PMADRH                         | ; Load upper 6 bits of erase address boundary                                                                      |

|                      | BCF<br>BSF<br>BSF        | PMCON1,CFGS<br>PMCON1,FREE<br>PMCON1,WREN | ; Specify an erase operation                                                                                       |

|                      | MOVLW<br>MOVWF           | 55h<br>PMCON2                             | <pre>; Start of required sequence to initiate erase ; Write 55h</pre>                                              |

| Required<br>Sequence | MOVLW<br>MOVWF           | 0AAh<br>PMCON2                            | ;<br>; Write AAh                                                                                                   |

| Re                   | BSF<br>NOP<br>NOP        | PMCON1,WR                                 | ; Set WR bit to begin erase<br>; NOP instructions are forced as processor starts<br>; row erase of program memory. |

|                      | ivor                     |                                           | ;<br>; The processor stalls until the erase process is complete                                                    |

|                      | BCF                      | PMCON1,WREN                               | ; after erase processor continues with 3rd instruction ; Disable writes                                            |

|                      | BSF                      | INTCON, GIE                               | ; Enable interrupts                                                                                                |

### 11.5 PORTB Registers (PIC16LF1559 Only)

#### 11.5.1 DATA REGISTER

PORTB is a 4-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 11-8). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., disable the output driver). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 11-1 shows how to initialize an I/O port.

Reading the PORTB register (Register 11-7) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATB).

### 11.5.2 DIRECTION CONTROL

The TRISB register (Register 11-8) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### 11.5.3 ANALOG CONTROL

The ANSELB register (Register 11-10) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELB bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELB bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSELx bits        |

|       | must be initialized to '0' by user software. |

### 11.5.4 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each PORTB pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 11-5.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input functions, such as ADC and comparator inputs, are not shown in the priority lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown below in Table 11-5.

| TABLE 11-5: | PORTB OUTPUT PRIORITY |

|-------------|-----------------------|

|-------------|-----------------------|

| Pin Name | Function Priority <sup>(1)</sup> |

|----------|----------------------------------|

| RB4      | SDA<br>RB4                       |

| RB5      | RB5                              |

| RB6      | SCL<br>SCK<br>RB6                |

| RB7      | TX<br>RB7                        |

Note 1: Priority listed from highest to lowest.

# 18.5.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

### 18.5.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-tohigh pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

# 18.5.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 18-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

**Note:** Enabling Toggle mode at the same time as changing the gate polarity may result in indeterminate operation.

#### 18.5.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/ DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/ DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 18-5 for timing details.

If the Single Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 18-6 for timing details.

# 18.5.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

# 18.5.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

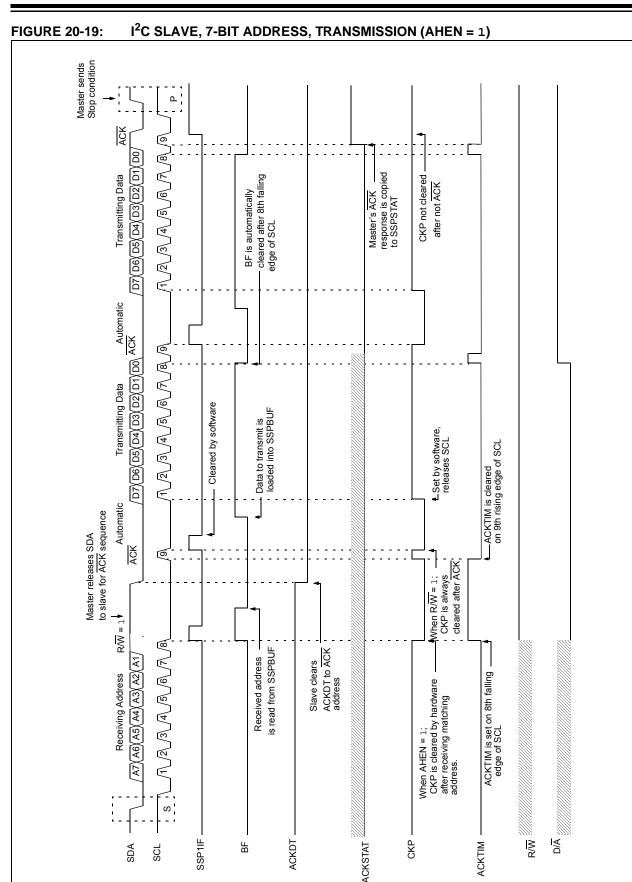

#### 20.5.3 SLAVE TRANSMISSION

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register, and an ACK pulse is sent by the slave on the ninth bit.

Following the ACK, slave hardware clears the CKP bit and the SCL pin is held low (see **Section 20.5.6** "**Clock Stretching**" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data.

The transmit data must be loaded into the SSPBUF register which also loads the SSPSR register. Then the SCL pin should be released by setting the CKP bit of the SSPCON1 register. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time.

The  $\overline{ACK}$  pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. This  $\overline{ACK}$ value is copied to the ACKSTAT bit of the SSPCON2 register. If ACKSTAT is set (not  $\overline{ACK}$ ), then the data transfer is complete. In this case, when the not  $\overline{ACK}$  is latched by the slave, the slave goes idle and waits for another occurrence of the Start bit. If the SDA line was low ( $\overline{ACK}$ ), the next transmit data must be loaded into the SSPBUF register. Again, the SCL pin must be released by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSP1IF bit must be cleared by software and the SSPSTAT register is used to determine the status of the byte. The SSP1IF bit is set on the falling edge of the ninth clock pulse.

#### 20.5.3.1 Slave Mode Bus Collision

A slave receives a Read request and begins shifting data out on the SDA line. If a bus collision is detected and the SBCDE bit of the SSPCON3 register is set, the BCLIF bit of the PIRx register is set. Once a bus collision is detected, the slave goes Idle and waits to be addressed again. User software can use the BCLIF bit to handle a slave bus collision.

#### 20.5.3.2 7-Bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 20-18 can be used as a reference to this list.

- 1. Master sends a Start condition on SDA and SCL.

- 2. S bit of SSPSTAT is set; SSP1IF is set if interrupt on Start detect is enabled.

- 3. Matching address with R/W bit set is received by the Slave setting SSP1IF bit.

- 4. Slave hardware generates an ACK and sets SSP1IF.

- 5. SSP1IF bit is cleared by user.

- 6. Software reads the received address from SSPBUF, clearing BF.

- 7.  $R/\overline{W}$  is set so CKP was automatically cleared after the  $\overline{ACK}$ .

- 8. The slave software loads the transmit data into SSPBUF.

- 9. CKP bit is set releasing SCL, allowing the master to clock the data out of the slave.

- 10. SSP1IF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSP1IF bit is cleared.

- 12. The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

- **Note 1:** If the master ACKs the clock will be stretched.

- ACKSTAT is the only bit updated on the rising edge of SCL (9th) rather than the falling.

- 13. Steps 9-13 are repeated for each transmitted byte.

- 14. If the master sends a not ACK; the clock is not held, but SSP1IF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.

| FIGURE 21-12: | SYNCHRONOUS RECEPTION (MASTER MODE, SREN)     |

|---------------|-----------------------------------------------|

|               |                                               |

|               |                                               |

| RX/DT         | bit 0 bit 1 bit 2 bit 3 bit 4 bit 5 bit 6 bit |

| RX/DT<br>pin                         | bit 0 bit 1 bit 2 bit 3 bit 4 bit 5 bit 6 bit 7                                  |     |

|--------------------------------------|----------------------------------------------------------------------------------|-----|

| TX/CK pin<br>(SCKP = 0)-             |                                                                                  |     |

| TX/CK pin-<br>(SCKP = 1)<br>Write to |                                                                                  |     |

| bit SREN                             |                                                                                  |     |

| CREN bit                             | ·0 <sup>,</sup>                                                                  | ·0' |

| RCIF bit<br>(Interrupt) -            |                                                                                  |     |

| Read<br>RCREG                        | Timing diagram demonstrates Sync Master mode with bit SREN = 1 and bit BRGH = 0. | Ĺ   |

| Note.                                |                                                                                  |     |

# TABLE 21-8:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER<br/>RECEPTION

| Name    | Bit 7     | Bit 6  | Bit 5  | Bit 4      | Bit 3       | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-----------|--------|--------|------------|-------------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF    | RCIDL  | _      | SCKP       | BRG16       |        | WUE    | ABDEN  | 245                 |

| INTCON  | GIE       | PEIE   | TMR0IE | INTE       | IOCIE       | TMR0IF | INTF   | IOCIF  | 77                  |

| PIE1    | TMR1GIE   | AD1IE  | RCIE   | TXIE       | SSP1IE      | _      | TMR2IE | TMR1IE | 78                  |

| PIR1    | TMR1GIF   | AD1IF  | RCIF   | TXIF       | SSP1IF      | _      | TMR2IF | TMR1IF | 80                  |

| RCREG   |           |        | EUS    | ART Receiv | ve Data Reg | gister |        |        | 239*                |

| RCSTA   | SPEN      | RX9    | SREN   | CREN       | ADDEN       | FERR   | OERR   | RX9D   | 244                 |

| SPBRGL  | BRG<7:0>  |        |        |            |             |        | 246*   |        |                     |

| SPBRGH  | BRG<15:8> |        |        |            |             | 246*   |        |        |                     |

| TRISB   | TRISB7    | TRISB6 | TRISB5 | TRISB4     | _           | _      |        | _      | 112                 |

| TXSTA   | CSRC      | TX9    | TXEN   | SYNC       | SENDB       | BRGH   | TRMT   | TX9D   | 243                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for synchronous master reception.

\* Page provides register information.

# 27.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

# 27.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 27.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 27.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

# 27.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

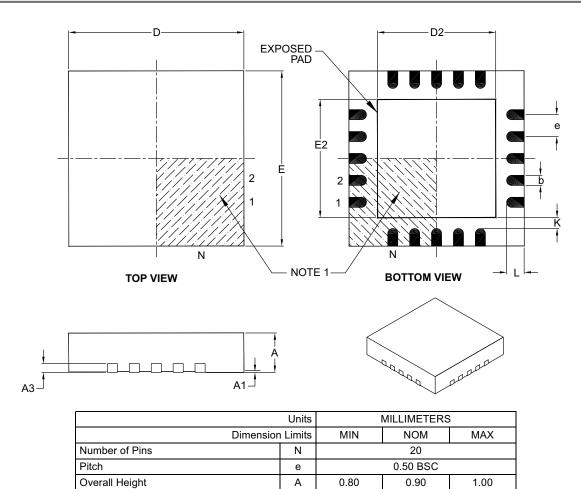

# 20-Lead Plastic Quad Flat, No Lead Package (ML) – 4x4x0.9 mm Body [QFN]

For the most current package drawings, please see the Microchip Packaging Specification located at Note: http://www.microchip.com/packaging

| Contact Thickness      | A3 |      | 0.20 REF |      |

|------------------------|----|------|----------|------|

| Overall Width          | E  |      | 4.00 BSC |      |

| Exposed Pad Width      | E2 | 2.60 | 2.70     | 2.80 |

| Overall Length         | D  |      | 4.00 BSC |      |

| Exposed Pad Length     | D2 | 2.60 | 2.70     | 2.80 |

| Contact Width          | b  | 0.18 | 0.25     | 0.30 |

| Contact Length         | L  | 0.30 | 0.40     | 0.50 |

| Contact-to-Exposed Pad | K  | 0.20 | _        | _    |

А

A1

0.00

0.90

0.02

1.00

0.05

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

**Overall Height**

Standoff

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-126B

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.