Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·><Fl

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 11                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                              |

| Supplier Device Package    | 14-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1554t-i-sl |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

| Address       | Name                  | Bit 7         | Bit 6                                                                                                  | Bit 5           | Bit 4            | Bit 3                   | Bit 2        | Bit 1          | Bit 0         | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------------|-----------------------|---------------|--------------------------------------------------------------------------------------------------------|-----------------|------------------|-------------------------|--------------|----------------|---------------|-----------------------|---------------------------------|

| Bank 0        |                       |               |                                                                                                        |                 |                  |                         |              |                |               |                       |                                 |

| 000h          | INDF0 <sup>(1)</sup>  | Addressing t  | his location us                                                                                        | es contents of  | FSR0H/FSR0       | L to address            | data memory  | y (not a physi | cal register) | xxxx xxxx             | uuuu uuuu                       |

| 001h          | INDF1 <sup>(1)</sup>  | Addressing t  | Addressing this location uses contents of FSR1H/FSR1L to address data memory (not a physical register) |                 |                  |                         |              |                |               | xxxx xxxx             | uuuu uuuu                       |

| 002h          | PCL <sup>(1)</sup>    |               |                                                                                                        | Program C       | Counter (PC) L   | east Significa          | int Byte     |                |               | 0000 0000             | 0000 0000                       |

| 003h          | STATUS <sup>(1)</sup> | —             | _                                                                                                      | —               | TO               | PD                      | Z            | DC             | С             | 1 1000                | q quuu                          |

| 004h          | FSR0L <sup>(1)</sup>  |               |                                                                                                        | Indirect Da     | ata Memory Ac    | ldress 0 Low            | Pointer      |                |               | 0000 0000             | uuuu uuuu                       |

| 005h          | FSR0H <sup>(1)</sup>  |               |                                                                                                        | Indirect Da     | ta Memory Ad     | dress 0 High            | Pointer      |                |               | 0000 0000             | 0000 0000                       |

| 006h          | FSR1L <sup>(1)</sup>  |               |                                                                                                        | Indirect Da     | ata Memory Ac    | ldress 1 Low            | Pointer      |                |               | 0000 0000             | uuuu uuuu                       |

| 007h          | FSR1H <sup>(1)</sup>  |               |                                                                                                        | Indirect Da     | ta Memory Ad     | dress 1 High            | Pointer      |                |               | 0000 0000             | 0000 0000                       |

| 008h          | BSR <sup>(1)</sup>    | _             | _                                                                                                      | _               |                  |                         | BSR<4:0>     |                |               | 0 0000                | 0 0000                          |

| 009h          | WREG <sup>(1)</sup>   |               |                                                                                                        |                 | Working R        | egister                 |              |                |               | 0000 0000             | uuuu uuuu                       |

| 00Ah          | PCLATH <sup>(1)</sup> | _             |                                                                                                        | Write Bu        | ffer for the upp | er 7 bits of th         | ne Program C | ounter         |               | -000 0000             | -000 0000                       |

| 00Bh          | INTCON <sup>(1)</sup> | GIE           | PEIE                                                                                                   | TMR0IE          | INTE             | IOCIE                   | TMR0IF       | INTF           | IOCIF         | 0000 0000             | 0000 0000                       |

| 00Ch          | PORTA                 | _             | -                                                                                                      | RA5             | RA4              | RA3                     | RA2          | RA1            | RA0           | xx xxxx               | xx xxxx                         |

|               | PORTB <sup>(2)</sup>  | Unimplemented |                                                                                                        |                 |                  |                         |              |                |               | _                     | _                               |

| 00Dh          | PORTB <sup>(3)</sup>  | RB7           | RB6                                                                                                    | RB5             | RB4              | —                       | —            | —              | —             | xxxx                  | xxxx                            |

| 00 <b>C</b> h | PORTC <sup>(2)</sup>  | _             | _                                                                                                      | RC5             | RC4              | RC3                     | RC2          | RC1            | RC0           | xx xxxx               | xx xxxx                         |

| 00Eh          | PORTC <sup>(3)</sup>  | RC7           | RC6                                                                                                    | RC5             | RC4              | RC3                     | RC2          | RC1            | RC0           | xxxx xxxx             | xxxx xxxx                       |

| 011h          | PIR1                  | TMR1GIF       | AD1IF                                                                                                  | RCIF            | TXIF             | SSP1IF                  | _            | TMR2IF         | TMR1IF        | 0000 0-00             | 0000 0-00                       |

| 012h          | PIR2                  | _             | AD2IF                                                                                                  | _               | _                | BCLIF                   | _            | _              | _             | -0 0                  | -0 0                            |

| 015h          | TMR0                  |               |                                                                                                        |                 | Timer0 Modul     | e Register              |              |                |               | XXXX XXXX             | uuuu uuuu                       |

| 016h          | TMR1L                 |               | Holding R                                                                                              | egister for the | Least Signific   | ant Byte of th          | e 16-bit TMR | 1 Count        |               | XXXX XXXX             | uuuu uuuu                       |

| 017h          | TMR1H                 |               | Holding R                                                                                              | egister for the | Most Significa   | ant Byte of the         | e 16-bit TMR | 1 Count        |               | XXXX XXXX             | uuuu uuuu                       |

| 018h          | T1CON                 | TMR1C         | S<1:0>                                                                                                 | T1CKP           | S<1:0>           | _                       | T1SYNC       | _              | TMR10N        | 0000 -0-0             | uuuu -u-u                       |

| 019h          | T1GCON                | TMR1GE        | T1GPOL                                                                                                 | T1GTM           | T1GSPM           | T <u>1GGO</u> /<br>DONE | T1GVAL       | _              | T1GSS         | 0000 0x-0             | uuuu ux-u                       |

| 01Ah          | TMR2                  |               |                                                                                                        |                 | Timer 2 Modul    | e Register              |              |                |               | 0000 0000             | 0000 0000                       |

| 01Bh          | PR2                   |               |                                                                                                        |                 | Timer 2 Perio    | d Register              |              |                |               | 1111 1111             | 1111 1111                       |

| 01Ch          | T2CON                 | _             |                                                                                                        | T2OUTP          | 'S<3:0>          |                         | TMR2ON       | T2CKF          | 'S<1:0>       | -000 0000             | -000 0000                       |

| 01Dh          | —                     |               |                                                                                                        |                 | Unimplem         | ented                   |              |                |               | _                     | _                               |

| 01Eh          | —                     |               |                                                                                                        |                 | Unimplem         | ented                   |              |                |               | —                     | _                               |

| 01Fh          | —                     |               |                                                                                                        |                 | Unimplem         | ented                   |              |                |               | _                     | _                               |

| l ogond:      |                       | u = unchange  |                                                                                                        |                 |                  |                         |              |                |               |                       |                                 |

#### **TABLE 3-9:** SPECIAL FUNCTION REGISTER SUMMARY

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Note 1: These registers can be accessed from any bank. 2: PIC16I F1554

PIC16LF1554. 2:

3: PIC16LF1559.

These registers/bits are available at two address locations, in Bank 1 and Bank 14. 4:

| IADLL         | J-J. JIL              |              |                                             |                |                  |                  |              | /              |                |                       |                                 |

|---------------|-----------------------|--------------|---------------------------------------------|----------------|------------------|------------------|--------------|----------------|----------------|-----------------------|---------------------------------|

| Address       | Name                  | Bit 7        | Bit 6                                       | Bit 5          | Bit 4            | Bit 3            | Bit 2        | Bit 1          | Bit 0          | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

| Banks 16-30   |                       |              |                                             |                |                  |                  |              |                |                |                       |                                 |

| x00h/<br>x80h | INDF0 <sup>(1)</sup>  | Addressing t | his location us                             | es contents of | FSR0H/FSR0       | )L to address    | data memor   | y (not a physi | ical register) | XXXX XXXX             | uuuu uuuu                       |

| x00h/<br>x81h | INDF1 <sup>(1)</sup>  | Addressing t | his location us                             | es contents of | FSR1H/FSR1       | L to address     | data memor   | y (not a physi | ical register) | XXXX XXXX             | uuuu uuuu                       |

| x02h/<br>x82h | PCL <sup>(1)</sup>    |              |                                             | Program C      | Counter (PC) L   | east Significa   | int Byte     |                |                | 0000 0000             | 0000 0000                       |

| x03h/<br>x83h | STATUS <sup>(1)</sup> | _            | _                                           | _              | TO               | PD               | Z            | DC             | С              | 1 1000                | q quuu                          |

| x04h/<br>x84h | FSR0L <sup>(1)</sup>  |              | Indirect Data Memory Address 0 Low Pointer  |                |                  |                  |              |                |                | 0000 0000             | uuuu uuuu                       |

| x05h/<br>x85h | FSR0H <sup>(1)</sup>  |              | Indirect Data Memory Address 0 High Pointer |                |                  |                  |              |                |                | 0000 0000             | 0000 0000                       |

| x06h/<br>x86h | FSR1L <sup>(1)</sup>  |              |                                             | Indirect Da    | ata Memory Ac    | Idress 1 Low     | Pointer      |                |                | 0000 0000             | uuuu uuuu                       |

| x07h/<br>x87h | FSR1H <sup>(1)</sup>  |              |                                             | Indirect Da    | ta Memory Ad     | ldress 1 High    | Pointer      |                |                | 0000 0000             | 0000 0000                       |

| x08h/<br>x88h | BSR <sup>(1)</sup>    | -            | _                                           | -              |                  |                  | BSR<4:0>     |                |                | 0 0000                | 0 0000                          |

| x09h/<br>x89h | WREG <sup>(1)</sup>   |              |                                             |                | Working R        | egister          |              |                |                | 0000 0000             | uuuu uuuu                       |

| x0Ah/<br>x8Ah | PCLATH <sup>(1)</sup> | _            |                                             | Write Bur      | ffer for the upp | per 7 bits of th | ne Program C | ounter         |                | -000 0000             | -000 0000                       |

| x0Bh/<br>x8Bh | INTCON <sup>(1)</sup> | GIE          | PEIE                                        | TMR0IE         | INTE             | IOCIE            | TMR0IF       | INTF           | IOCIF          | 0000 0000             | 0000 0000                       |

#### TABLE 3-9: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: These registers can be accessed from any bank.

2: PIC16LF1554.

3: PIC16LF1559.

4: These registers/bits are available at two address locations, in Bank 1 and Bank 14.

# 9.6 Register Definitions: Watchdog Control

| REGISTER 9       | -1: WDT              | CON: WATCH                                                   | DOG TIME       | R CONTROL                             | REGISTER         |                  |              |

|------------------|----------------------|--------------------------------------------------------------|----------------|---------------------------------------|------------------|------------------|--------------|

| U-0              | U-0                  | R/W-0/0                                                      | R/W-1/1        | R/W-0/0                               | R/W-1/1          | R/W-1/1          | R/W-0/0      |

| —                | _                    |                                                              |                | WDTPS<4:0                             | >                |                  | SWDTEN       |

| bit 7            |                      |                                                              |                |                                       |                  |                  | bit (        |

| Legend:          |                      |                                                              |                |                                       |                  |                  |              |

| R = Readable     | bit                  | W = Writable                                                 | bit            | U = Unimpler                          | nented bit, read | d as '0'         |              |

| u = Bit is unch  | anged                | x = Bit is unkr                                              | nown           | -n/n = Value a                        | at POR and BC    | R/Value at all o | other Resets |

| '1' = Bit is set |                      | '0' = Bit is cle                                             | ared           |                                       |                  |                  |              |

| bit 7-6          | Unimpleme            | nted: Read as '                                              | 0'             |                                       |                  |                  |              |

| bit 5-1          | -                    | )>: Watchdog Ti                                              |                | elect bits <sup>(1)</sup>             |                  |                  |              |

|                  |                      | Prescale Rate                                                |                |                                       |                  |                  |              |

|                  | 11111 = R            | eserved. Result                                              | s in minimum   | interval (1:32)                       |                  |                  |              |

|                  | •                    |                                                              |                | , , , , , , , , , , , , , , , , , , , |                  |                  |              |

|                  | •                    |                                                              |                |                                       |                  |                  |              |

|                  | •<br>10011 - D       |                                                              |                | interrel (1.22)                       |                  |                  |              |

|                  | 10011 = R            | eserved. Result                                              | s in minimum   | interval (1:32)                       |                  |                  |              |

|                  | 10010 = 1:           | 8388608 (2 <sup>23</sup> ) (                                 | Interval 256s  | nominal)                              |                  |                  |              |

|                  | 10001 = 1:           | 4194304 (2 <sup>22</sup> ) (                                 | Interval 128s  | nominal)                              |                  |                  |              |

|                  | 10000 = 1:           | 4194304 (2 <sup>22</sup> ) (<br>2097152 (2 <sup>21</sup> ) ( | Interval 64s n | ominal)                               |                  |                  |              |

|                  | 01111 = 1:           | 1048576 (2 <sup>20</sup> ) (                                 | Interval 32s n | ominal)                               |                  |                  |              |

|                  |                      | 524288 (2 <sup>19</sup> ) (Ir                                |                |                                       |                  |                  |              |

|                  |                      | 262144 (2 <sup>18</sup> ) (Ir                                |                |                                       |                  |                  |              |

|                  |                      | 131072 (2 <sup>17</sup> ) (Ir<br>65536 (Interval             |                |                                       |                  |                  |              |

|                  |                      | 32768 (Interval                                              | , ,            | Reset value)                          |                  |                  |              |

|                  |                      | 16384 (Interval                                              | ,              | nal)                                  |                  |                  |              |

|                  |                      | 8192 (Interval 2                                             |                |                                       |                  |                  |              |

|                  |                      | 4096 (Interval 1                                             |                |                                       |                  |                  |              |

|                  |                      | 2048 (Interval 6                                             |                |                                       |                  |                  |              |

|                  |                      | 1024 (Interval 3                                             |                | )                                     |                  |                  |              |

|                  |                      | 512 (Interval 16                                             |                |                                       |                  |                  |              |

|                  |                      | 256 (Interval 8 r                                            | ,              |                                       |                  |                  |              |

|                  |                      | 128 (Interval 4 r<br>64 (Interval 2 m                        |                |                                       |                  |                  |              |

|                  |                      | 32 (Interval 1 m                                             |                |                                       |                  |                  |              |

| bit 0            |                      | Software Enable                                              |                | /atchdog Timer                        | bit              |                  |              |

|                  | If WDTE<1:           |                                                              |                |                                       |                  |                  |              |

|                  | This bit is ig       |                                                              |                |                                       |                  |                  |              |

|                  | <u>If WDTE&lt;1:</u> |                                                              |                |                                       |                  |                  |              |

|                  | 1 = WDT is           |                                                              |                |                                       |                  |                  |              |

|                  | 0 = WDT is           |                                                              |                |                                       |                  |                  |              |

|                  | If WDTE<1:           |                                                              |                |                                       |                  |                  |              |

|                  | This bit is ig       | norea.                                                       |                |                                       |                  |                  |              |

|                  |                      |                                                              |                |                                       |                  |                  |              |

### REGISTER 9-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

Note 1: Times are approximate. WDT time is based on 31 kHz LFINTOSC.

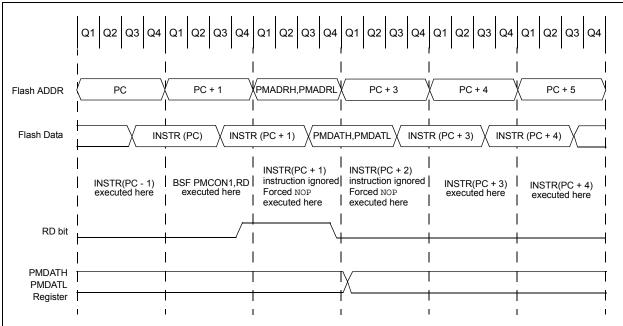

### FIGURE 10-2: FLASH PROGRAM MEMORY READ CYCLE EXECUTION

### EXAMPLE 10-1: FLASH PROGRAM MEMORY READ

\* This code block will read 1 word of program

- \* memory at the memory address:

- PROG\_ADDR\_HI : PROG\_ADDR\_LO

- \* data will be returned in the variables;

- \* PROG\_DATA\_HI, PROG\_DATA\_LO

| BANKSEL                  | PMADRL                   | ; Select Bank for PMCON registers                                                                                          |

|--------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------|

| MOVLW                    | PROG_ADDR_LO             | ;                                                                                                                          |

| MOVWF                    | PMADRL                   | ; Store LSB of address                                                                                                     |

| MOVLW                    | PROG_ADDR_HI             | ;                                                                                                                          |

| MOVWF                    | PMADRH                   | ; Store MSB of address                                                                                                     |

| BCF<br>BSF<br>NOP<br>NOP | PMCON1,CFGS<br>PMCON1,RD | <pre>; Do not select Configuration Space<br/>; Initiate read<br/>; Ignored (Figure 10-2)<br/>; Ignored (Figure 10-2)</pre> |

| MOVF                     | PMDATL,W                 | ; Get LSB of word                                                                                                          |

| MOVWF                    | PROG_DATA_LO             | ; Store in user location                                                                                                   |

| MOVF                     | PMDATH,W                 | ; Get MSB of word                                                                                                          |

| MOVWF                    | PROG_DATA_HI             | ; Store in user location                                                                                                   |

### 12.6 Register Definitions: Interrupt-on-Change Control

| R/W-0/0<br>IOCAP5                       | R/W-0/0<br>IOCAP4 | R/W-0/0<br>IOCAP3                                              | R/W-0/0<br>IOCAP2                  | R/W-0/0<br>IOCAP1                                     | R/W-0/0<br>IOCAP0                                                   |  |  |  |

|-----------------------------------------|-------------------|----------------------------------------------------------------|------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------|--|--|--|

| IOCAP5                                  | IOCAP4            | IOCAP3                                                         | IOCAP2                             | IOCAP1                                                |                                                                     |  |  |  |

|                                         |                   |                                                                |                                    |                                                       |                                                                     |  |  |  |

|                                         |                   |                                                                |                                    |                                                       | bit 0                                                               |  |  |  |

|                                         |                   |                                                                |                                    |                                                       |                                                                     |  |  |  |

|                                         |                   |                                                                |                                    |                                                       |                                                                     |  |  |  |

| W = Writable bi                         | it                | U = Unimpleme                                                  | ented bit, read as                 | '0'                                                   |                                                                     |  |  |  |

| u = Bit is unchanged x = Bit is unknown |                   |                                                                |                                    | -n/n = Value at POR and BOR/Value at all other Resets |                                                                     |  |  |  |

| '0' = Bit is clear                      | red               |                                                                |                                    |                                                       |                                                                     |  |  |  |

|                                         | x = Bit is unkno  | W = Writable bit<br>x = Bit is unknown<br>'0' = Bit is cleared | x = Bit is unknown -n/n = Value at | x = Bit is unknown -n/n = Value at POR and BOR/V      | x = Bit is unknown -n/n = Value at POR and BOR/Value at all other I |  |  |  |

### REGISTER 12-1: IOCAP: INTERRUPT-ON-CHANGE PORTA POSITIVE EDGE REGISTER

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **IOCAP<5:0>:** Interrupt-on-Change PORTA Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

### REGISTER 12-2: IOCAN: INTERRUPT-ON-CHANGE PORTA NEGATIVE EDGE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | _   | IOCAN5  | IOCAN4  | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

bit 5-0

bit 5-0

IOCAN<5:0>: Interrupt-on-Change PORTA Negative Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

### REGISTER 12-3: IOCAF: INTERRUPT-ON-CHANGE PORTA FLAG REGISTER

| U-0   | U-0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|------------|------------|------------|------------|------------|------------|

| —     | _   | IOCAF5     | IOCAF4     | IOCAF3     | IOCAF2     | IOCAF1     | IOCAF0     |

| bit 7 |     |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-6 Unimplemented: Read as '0'

IOCAF<5:0>: Interrupt-on-Change PORTA Flag bits

1 = An enabled change was detected on the associated pin.

Set when IOCAPx = 1 and a rising edge was detected on RAx, or when IOCANx = 1 and a falling edge was detected on RAx.

0 = No change was detected, or the user cleared the detected change.

|                  |                   |                           |                | <b>OONTINOL</b> |                  |                  |              |

|------------------|-------------------|---------------------------|----------------|-----------------|------------------|------------------|--------------|

| U-0              | R/W-0/0           | R/W-0/0                   | R/W-0/0        | U-0             | U-0              | U-0              | U-0          |

| —                |                   | TRIGSEL<2:0>(1            | )              |                 | —                | —                | _            |

| bit 7            |                   |                           |                | •               | •                | •                | bit 0        |

|                  |                   |                           |                |                 |                  |                  |              |

| Legend:          |                   |                           |                |                 |                  |                  |              |

| R = Readable     | bit               | W = Writable I            | oit            | U = Unimpler    | mented bit, read | d as '0'         |              |

| u = Bit is uncha | anged             | x = Bit is unkn           | own            | -n/n = Value a  | at POR and BC    | R/Value at all o | other Resets |

| '1' = Bit is set |                   | '0' = Bit is clea         | ared           |                 |                  |                  |              |

|                  |                   |                           |                |                 |                  |                  |              |

| bit 7            | Unimpleme         | nted: Read as '           | )'             |                 |                  |                  |              |

| bit 6-4          | TRIGSEL<2         | ::0>: Auto-Conve          | ersion Trigger | Selection bits  |                  |                  |              |

|                  | 000 <b>= No A</b> | uto Conversion T          | rigger selecte | ed              |                  |                  |              |

|                  | 001 = Rese        |                           |                |                 |                  |                  |              |

|                  | 010 = Rese        |                           |                |                 |                  |                  |              |

|                  |                   | 0 Overflow <sup>(2)</sup> |                |                 |                  |                  |              |

|                  |                   | 1 Overflow <sup>(2)</sup> | 2)             |                 |                  |                  |              |

|                  |                   | 2 Match to PR2            | 2)             |                 |                  |                  |              |

|                  |                   | RIG Rising Edge           |                |                 |                  |                  |              |

|                  | 111 = ADTF        | RIG Falling Edge          |                |                 |                  |                  |              |

| bit 3-0          | Unimpleme         | nted: Read as '           | )'             |                 |                  |                  |              |

| Note 1: See      | Section 16.       | 1.11 "Hardware            | CVD Registe    | er Mapping" fo  | r more informat  | tion.            |              |

# REGISTER 16-6: AADxCON2: HARDWARE CVD CONTROL REGISTER 2<sup>(1)</sup>

See Section 16.1.11 "Hardware CVD Register Mapping" for more information. 1:

2: Signal used to set the corresponding interrupt flag.

# 18.5.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

### 18.5.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-tohigh pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

# 18.5.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 18-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

**Note:** Enabling Toggle mode at the same time as changing the gate polarity may result in indeterminate operation.

### 18.5.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/ DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/ DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 18-5 for timing details.

If the Single Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 18-6 for timing details.

# 18.5.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

# 18.5.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

# 18.6 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- TMR1ON bit of the T1CON register

- TMR1IE bit of the PIE1 register

- · PEIE bit of the INTCON register

- GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

**Note:** The TMR1H:TMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

# 18.7 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- PEIE bit of the INTCON register must be set

- T1SYNC bit of the T1CON register must be set

- TMR1CS bits of the T1CON register must be configured

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine.

Timer1 oscillator will continue to operate in Sleep regardless of the T1SYNC bit setting.

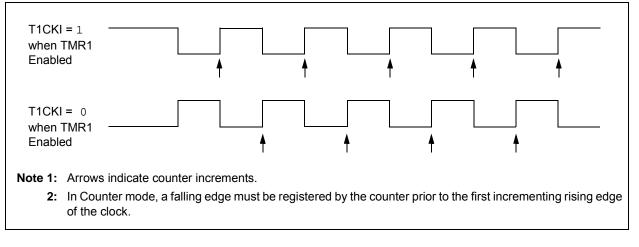

### FIGURE 18-2: TIMER1 INCREMENTING EDGE

### 18.7.1 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register, APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 11.1 "Alternate Pin Function"** for more information.

| FIGURE 18-6: TIMER1 G | ATE SINGLE-PULSE AND TOGGLE COMBINED MODE                         |               |

|-----------------------|-------------------------------------------------------------------|---------------|

| TMR1GE                |                                                                   |               |

| T1GPOL                |                                                                   |               |

| T1GSPM                |                                                                   |               |

| T1GTM                 | Cleared by hardv                                                  | vare on       |

| DONE Cour             | et by software falling edge of T1                                 | GVAL          |

| t1g_in                | ing edge of T1G                                                   |               |

| т1СКІ                 |                                                                   |               |

| T1GV <u>AL</u>        |                                                                   |               |

| Timer1 N              | <u>N+1</u> <u>N+2</u> <u>N+3</u> <u>N+4</u>                       |               |

| TMR1GIF Cleared by    | Set by hardware on Clear<br>software falling edge of T1GVAL Clear | ed by<br>vare |

### 20.2.2 SPI MODE OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON1<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- · Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- · Slave Select mode (Slave mode only)

To enable the serial port, SSP Enable bit, SSPEN of the SSPCON1 register, must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPCONx registers and then set the SSPEN bit. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRISx register) appropriately programmed as follows:

- · SDI must have corresponding TRISx bit set

- SDO must have corresponding TRISx bit cleared

- SCK (Master mode) must have corresponding TRISx bit cleared

- SCK (Slave mode) must have corresponding TRISx bit set

- SS must have corresponding TRISx bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRISx) register to the opposite value.

The MSSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the eight bits of data have been received, that byte is moved to the SSPBUF register. Then, the Buffer Full Detect bit, BF of the SSPSTAT register, and the interrupt flag bit, SSP1IF, are set. This double-buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored and the write collision detect bit WCOL of the SSPCON1 register, will be set. User software must clear the WCOL bit to allow the following write(s) to the SSPBUF register to complete successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. The Buffer Full bit, BF of the SSPSTAT register, indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPBUF register. Additionally, the SSPSTAT register indicates the various Status conditions.

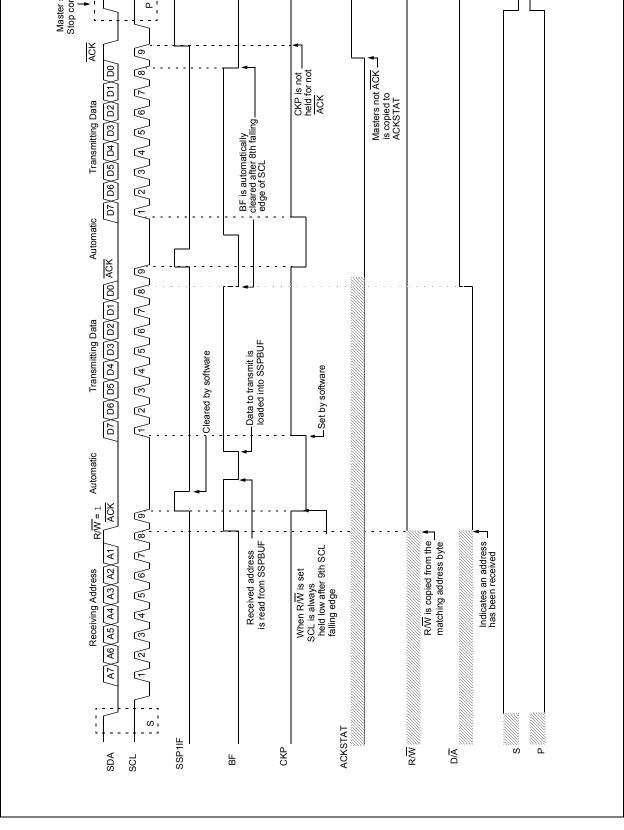

# 20.4 I<sup>2</sup>C MODE OPERATION

All MSSP I<sup>2</sup>C communication is byte oriented and shifted out MSb first. Six SFR registers and two interrupt flags interface the module with the PIC<sup>®</sup> microcontroller and user software. Two pins, SDA and SCL, are exercised by the module to communicate with other external I<sup>2</sup>C devices.

### 20.4.1 BYTE FORMAT

All communication in  $I^2C$  is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent back. After the 8th falling edge of the SCL line, the device outputting data on the SDA changes that pin to an input and reads in an acknowledge value on the next clock pulse.

The clock signal, SCL, is provided by the master. Data is valid to change while the SCL signal is low, and sampled on the rising edge of the clock. Changes on the SDA line while the SCL line is high define special conditions on the bus, explained below.

### 20.4.2 DEFINITION OF I<sup>2</sup>C TERMINOLOGY

There is language and terminology in the description of  $I^2C$  communication that have definitions specific to  $I^2C$ . That word usage is defined below and may be used in the rest of this document without explanation. This table was adapted from the Philips  $I^2C$  specification.

### 20.4.3 SDA AND SCL PINS

Selection of any  $I^2C$  mode with the SSPEN bit set, forces the SCL and SDA pins to be open-drain. These pins should be set by the user to inputs by setting the appropriate TRISx bits.

**Note:** Data is tied to output zero when an I<sup>2</sup>C mode is enabled.

### 20.4.4 SDA HOLD TIME

The hold time of the SDA pin is selected by the SDAHT bit of the SSPCON3 register. Hold time is the time SDA is held valid after the falling edge of SCL. Setting the SDAHT bit selects a longer 300 ns minimum hold time and may help on buses with large capacitance.

| TABLE 20-2:         |                                                                                                                                                                                                                 |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TERM                | Description                                                                                                                                                                                                     |

| Transmitter         | The device which shifts data out onto the bus.                                                                                                                                                                  |

| Receiver            | The device which shifts data in<br>from the bus.                                                                                                                                                                |

| Master              | The device that initiates a transfer, generates clock signals and terminates a transfer.                                                                                                                        |

| Slave               | The device addressed by the master.                                                                                                                                                                             |

| Multi-master        | A bus with more than one device that can initiate data transfers.                                                                                                                                               |

| Arbitration         | Procedure to ensure that only one master at a time controls the bus. Winning arbitration ensures that the message is not corrupted.                                                                             |

| Synchronization     | Procedure to synchronize the<br>clocks of two or more devices on<br>the bus.                                                                                                                                    |

| Idle                | No master is controlling the bus,<br>and both SDA and SCL lines are<br>high.                                                                                                                                    |

| Active              | Any time one or more master devices are controlling the bus.                                                                                                                                                    |

| Addressed<br>Slave  | Slave device that has received a matching address and is actively being clocked by a master.                                                                                                                    |

| Matching<br>Address | Address byte that is clocked into a slave that matches the value stored in SSPADD.                                                                                                                              |

| Write Request       | Slave receives a matching<br>address with R/W bit clear, and is<br>ready to clock in data.                                                                                                                      |

| Read Request        | Master sends an address byte with<br>the $R/\overline{W}$ bit set, indicating that it<br>wishes to clock data out of the<br>slave. This data is the next and all<br>following bytes until a Restart or<br>Stop. |

| Clock Stretching    | When a device on the bus hold SCL low to stall communication.                                                                                                                                                   |

| Bus Collision       | Any time the SDA line is sampled<br>low by the module while it is<br>outputting and expected high<br>state.                                                                                                     |

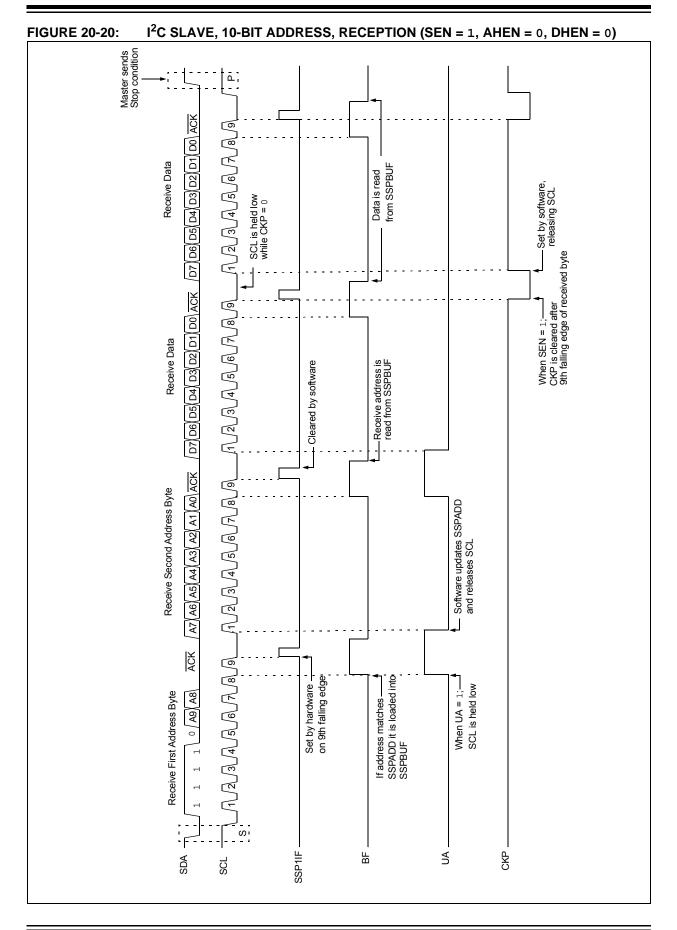

### 20.5.4 SLAVE MODE 10-BIT ADDRESS RECEPTION

This section describes a standard sequence of events for the MSSP module configured as an  $I^2C$  Slave in 10-bit Addressing mode.

Figure 20-20 is used as a visual reference for this description.

This is a step by step process of what must be done by slave software to accomplish  $I^2C$  communication.

- 1. Bus starts Idle.

- 2. Master sends Start condition; S bit of SSPSTAT is set; SSP1IF is set if interrupt on Start detect is enabled.

- 3. Master sends matching high address with  $R/\overline{W}$  bit clear; UA bit of the SSPSTAT register is set.

- 4. Slave sends ACK and SSP1IF is set.

- 5. Software clears the SSP1IF bit.

- 6. Software reads received address from SSPBUF clearing the BF flag.

- 7. Slave loads low address into SSPADD, releasing SCL.

- 8. Master sends matching low address byte to the Slave; UA bit is set.

**Note:** Updates to the SSPADD register are not allowed until after the ACK sequence.

9. Slave sends ACK and SSP1IF is set.

**Note:** If the low address does not match, SSP1IF and UA are still set so that the slave software can set SSPADD back to the high address. BF is not set because there is no match. CKP is unaffected.

- 10. Slave clears SSP1IF.

- 11. Slave reads the received matching address from SSPBUF clearing BF.

- 12. Slave loads high address into SSPADD.

- 13. Master clocks a data byte to the slave and clocks out the slaves ACK on the 9th SCL pulse; SSP1IF is set.

- 14. If SEN bit of SSPCON2 is set, CKP is cleared by hardware and the clock is stretched.

- 15. Slave clears SSP1IF.

- 16. Slave reads the received byte from SSPBUF clearing BF.

- 17. If SEN is set the slave sets CKP to release the SCL.

- 18. Steps 13-17 repeat for each received byte.

- 19. Master sends Stop to end the transmission.

### 20.5.5 10-BIT ADDRESSING WITH ADDRESS OR DATA HOLD

Reception using 10-bit addressing with AHEN or DHEN set is the same as with 7-bit modes. The only difference is the need to update the SSPADD register

using the UA bit. All functionality, specifically when the CKP bit is cleared and SCL line is held low are the same. Figure 20-21 can be used as a reference of a slave in 10-bit addressing with AHEN set.

Figure 20-22 shows a standard waveform for a slave transmitter in 10-bit Addressing mode.

### 20.5.6 CLOCK STRETCHING

Clock stretching occurs when a device on the bus holds the SCL line low, effectively pausing communication. The slave may stretch the clock to allow more time to handle data or prepare a response for the master device. A master device is not concerned with stretching as anytime it is active on the bus and not transferring data, it is stretching. Any stretching done by a slave is invisible to the master software and handled by the hardware that generates SCL.

The CKP bit of the SSPCON1 register is used to control stretching in software. Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. Setting CKP will release SCL and allow more communication.

### 20.5.6.1 Normal Clock Stretching

Following an  $\overline{ACK}$  if the  $R/\overline{W}$  bit of SSPSTAT is set, a read request, the slave hardware will clear CKP. This allows the slave time to update SSPBUF with data to transfer to the master. If the SEN bit of SSPCON2 is set, the slave hardware will always stretch the clock after the  $\overline{ACK}$  sequence. Once the slave is ready; CKP is set by software and communication resumes.

- Note 1: The BF bit has no effect on if the clock will be stretched or not. This is different than previous versions of the module that would not stretch the clock, clear CKP, if SSPBUF was read before the 9th falling edge of SCL.

- 2: Previous versions of the module did not stretch the clock for a transmission if SSPBUF was loaded before the 9th falling edge of SCL. It is now always cleared for read requests.

### 20.5.6.2 10-Bit Addressing Mode

In 10-bit Addressing mode, when the UA bit is set, the clock is always stretched. This is the only time the SCL is stretched without CKP being cleared. SCL is released immediately after a write to SSPADD.

**Note:** Previous versions of the module did not stretch the clock if the second address byte did not match.

### 20.5.6.3 Byte NACKing

When AHEN bit of SSPCON3 is set; CKP is cleared by hardware after the 8th falling edge of SCL for a received matching address byte. When DHEN bit of SSPCON3 is set; CKP is cleared after the 8th falling edge of SCL for received data.

Stretching after the 8th falling edge of SCL allows the slave to look at the received address or data and decide if it wants to ACK the received data.

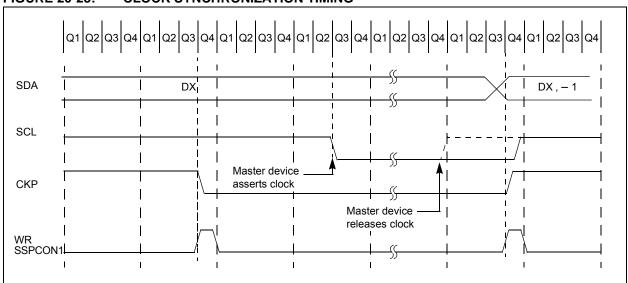

### 20.5.7 CLOCK SYNCHRONIZATION AND THE CKP BIT

Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. However, clearing the CKP bit will not assert the SCL output low until the SCL output is already sampled low. Therefore, the CKP bit will not assert the SCL line until an external  $I^2C$  master device has already asserted the SCL line. The SCL output will remain low until the CKP bit is set and all other devices on the  $I^2C$  bus have released SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (see Figure 20-23).

### FIGURE 20-23: CLOCK SYNCHRONIZATION TIMING

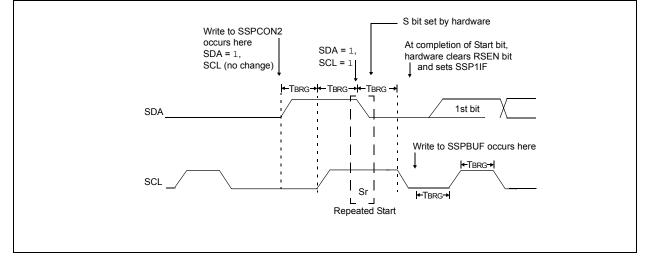

### 20.6.5 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition (Figure 20-27) occurs when the RSEN bit of the SSPCON2 register is programmed high and the master state machine is no longer active. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. SCL is asserted low. Following this, the RSEN bit of the SSPCON2 register will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit of the SSPSTAT register will be set. The SSP1IF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

# FIGURE 20-27: REPEAT START CONDITION WAVEFORM

### 20.6.6 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full flag bit, BF and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted. SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high. When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKSTAT bit on the rising edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSP1IF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 20-28).

After the write to the SSPBUF, each bit of the address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will release the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT Status bit of the SSPCON2 register. Following the falling edge of the ninth clock transmission of the address, the SSP1IF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

| DC CHARACTERISTICS |        | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |        |       |        |       |                                                                       |

|--------------------|--------|-----------------------------------------------------------------------------------------------------------------------|--------|-------|--------|-------|-----------------------------------------------------------------------|

| Param.<br>No.      | Sym.   | Characteristic                                                                                                        | Min.   | Тур.† | Max.   | Units | Conditions                                                            |

|                    |        | Program Memory Programming<br>Specifications                                                                          |        |       |        |       |                                                                       |

| D110               | VIHH   | Voltage on MCLR/VPP pin                                                                                               | 8.0    | _     | 9.0    | V     | (Note 2)                                                              |

| D111               | IDDP   | Supply Current during Programming                                                                                     | _      | _     | 10     | mA    |                                                                       |

| D112               | VBE    | VDD for Bulk Erase                                                                                                    | 2.7    |       | VDDMAX | V     |                                                                       |

| D113               | VPEW   | VDD for Write or Row Erase                                                                                            | VDDMIN | _     | VDDMAX | V     |                                                                       |

| D114               | IPPPGM | Current on MCLR/VPP during<br>Erase/Write                                                                             | _      | _     | 1.0    | mA    |                                                                       |

| D115               | IDDPGM | Current on VDD during Erase/Write                                                                                     | _      |       | 5.0    | mA    |                                                                       |

|                    |        | Program Flash Memory                                                                                                  |        |       |        |       |                                                                       |

| D121               | Eр     | Cell Endurance                                                                                                        | 10K    | _     | _      | E/W   | -40°C to +85°C (Note 1)                                               |

| D122               | VPRW   | VDD for Read/Write                                                                                                    | VDDMIN | _     | VDDMAX | V     |                                                                       |

| D123               | Tiw    | Self-timed Write Cycle Time                                                                                           | _      | 2     | 2.5    | ms    |                                                                       |

| D124               | TRETD  | Characteristic Retention                                                                                              | —      | 40    | _      | Year  | Provided no other specifications are violated                         |

| D125               | EHEFC  | High-Endurance Flash Cell                                                                                             | 100K   | _     | _      | E/W   | 0°C to +60°C,<br>Lower byte,<br>Last 128 Addresses in<br>Flash Memory |

# TABLE 25-5: MEMORY PROGRAMMING SPECIFICATIONS

† Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Self-write and Block Erase.

**2:** Required only if single-supply programming is disabled.

# 27.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

### 27.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB X IDE projects

- User-defined macros to streamline

assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

# 27.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

### 27.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- Rich directive set

- · Flexible macro language

- MPLAB X IDE compatibility

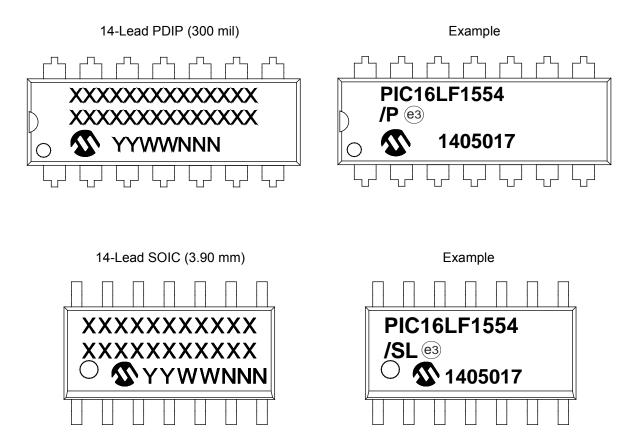

# 28.0 PACKAGING INFORMATION

# 28.1 Package Marking Information

| Legen | d: XXX<br>Y<br>YY<br>WW<br>NNN<br>(e3)<br>*                                                                                                                                                                   | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Note: | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                                             |  |  |