# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 17x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 20-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1559-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## PIC16LF1554/1559

- Master Synchronous Serial Port (MSSP) with SPI and I<sup>2</sup>C with:

- 7-bit address masking

- SMBus/PMBus™ compatibility

- Enhanced Universal Synchronous Asynchronous

- Receiver Transmitter (EUSART):

- RS-232, RS-485 and LIN compatible

- Auto-Baud Detect

- Auto-wake-up on start

### PIC16LF1554/1559 Family Types

| Device      | Data Sheet Index | Program Memory Flash<br>(words) | Data EEPROM (bytes) | SRAM (bytes) | I/OS <sup>(1)</sup> | 10-bit ADC (ch) <sup>(2)</sup> | Timers<br>8/16-Bit | EUSART | MSSP | MWA | Cap Touch Channels | Debug <sup>(3)</sup> |

|-------------|------------------|---------------------------------|---------------------|--------------|---------------------|--------------------------------|--------------------|--------|------|-----|--------------------|----------------------|

| PIC16LF1554 | (A)              | 4096                            | 0                   | 256          | 12                  | 11                             | 2/1                | 1      | 1    | 2   | 11                 | I                    |

| PIC16LF1559 | (A)              | 8192                            | 0                   | 512          | 18                  | 17                             | 2/1                | 1      | 1    | 2   | 17                 | Ι                    |

Note 1: RA3 is input only.

- 2: 11/17 analog channels are connected to two ADC modules.

- 3: Debugging Methods: (I) Integrated on Chip; (H) available using Debug Header

Data Sheet Index: (Unshaded devices are described in this document)

A. DS40001761 PIC16LF1554/1559 Data Sheet, 14/20-Pin, 8-Bit Flash Microcontrollers.

**Note:** For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

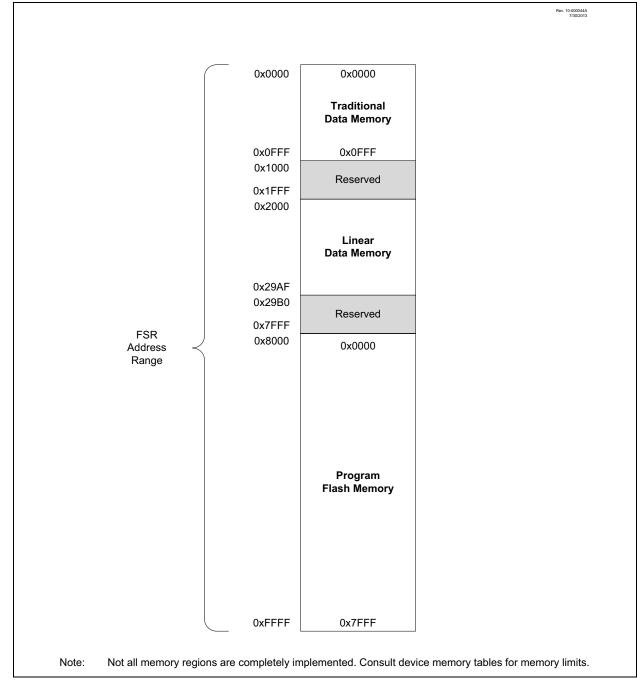

#### 3.5 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

FIGURE 3-9: INDIRECT ADDRESSING

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- Traditional Data Memory

- Linear Data Memory

- Program Flash Memory

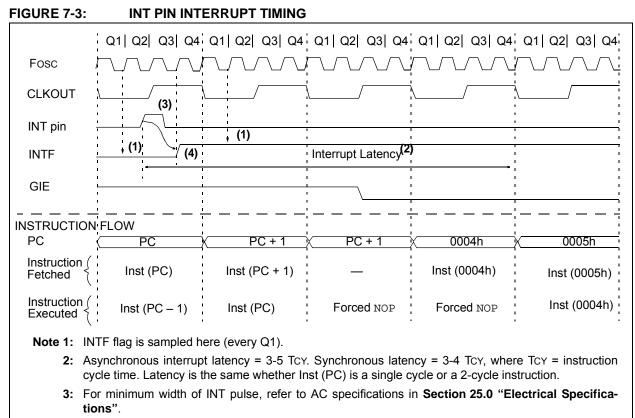

4: INTF is enabled to be set any time during the Q4-Q1 cycles.

### 8.0 POWER-DOWN MODE (SLEEP)

The Power-Down mode is entered by executing a SLEEP instruction.

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running, if enabled for operation during Sleep.

- 2. PD bit of the STATUS register is cleared.

- 3.  $\overline{\text{TO}}$  bit of the STATUS register is set.

- 4. CPU clock is disabled.

- 5. 31 kHz LFINTOSC is unaffected and peripherals that operate from it may continue operation in Sleep.

- 6. Timer1 and peripherals that operate from Timer1 continue operation in Sleep when the Timer1 clock source selected is:

- LFINTOSC

- T1CKI

- Timer1 oscillator

- 7. ADC is unaffected, if the dedicated FRC oscillator is selected.

- 8. I/O ports maintain the status they had before SLEEP was executed (driving high, low or highimpedance).

- 9. Resets other than WDT are not affected by Sleep mode.

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- · I/O pins should not be floating

- External circuitry sinking current from I/O pins

- · Internal circuitry sourcing current from I/O pins

- Current draw from pins with internal weak pull-ups

- Modules using 31 kHz LFINTOSC

I/O pins that are high-impedance inputs should be pulled to VDD or VSS externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include the FVR module. See **Section 13.0 "Fixed Voltage Reference (FVR)"** for more information on this module.

#### 8.1 Wake-up from Sleep

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled

- 2. BOR Reset, if enabled

- 3. POR Reset

- 4. Watchdog Timer, if enabled

- 5. Any external interrupt

- 6. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information)

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to **Section 6.12 "Determining the Cause of a Reset"**.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will then call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

## PIC16LF1554/1559

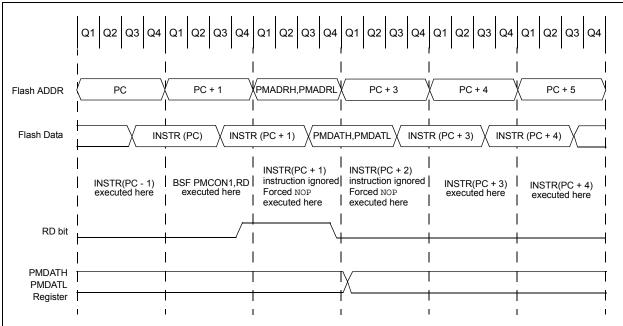

#### FIGURE 10-2: FLASH PROGRAM MEMORY READ CYCLE EXECUTION

#### EXAMPLE 10-1: FLASH PROGRAM MEMORY READ

\* This code block will read 1 word of program

- \* memory at the memory address:

- PROG\_ADDR\_HI : PROG\_ADDR\_LO

- \* data will be returned in the variables;

- \* PROG\_DATA\_HI, PROG\_DATA\_LO

| BANKSEL                  | PMADRL                   | ; Select Bank for PMCON registers                                                                                          |

|--------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------|

| MOVLW                    | PROG_ADDR_LO             | ;                                                                                                                          |

| MOVWF                    | PMADRL                   | ; Store LSB of address                                                                                                     |

| MOVLW                    | PROG_ADDR_HI             | ;                                                                                                                          |

| MOVWF                    | PMADRH                   | ; Store MSB of address                                                                                                     |

| BCF<br>BSF<br>NOP<br>NOP | PMCON1,CFGS<br>PMCON1,RD | <pre>; Do not select Configuration Space<br/>; Initiate read<br/>; Ignored (Figure 10-2)<br/>; Ignored (Figure 10-2)</pre> |

| MOVF                     | PMDATL,W                 | ; Get LSB of word                                                                                                          |

| MOVWF                    | PROG_DATA_LO             | ; Store in user location                                                                                                   |

| MOVF                     | PMDATH,W                 | ; Get MSB of word                                                                                                          |

| MOVWF                    | PROG_DATA_HI             | ; Store in user location                                                                                                   |

#### REGISTER 10-3: PMADRL: PROGRAM MEMORY ADDRESS LOW BYTE REGISTER

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|--------------|

|                  |         |                   | PMAC    | )R<7:0>        |                  |                  |              |

| bit 7            |         |                   |         |                |                  |                  | bit 0        |

|                  |         |                   |         |                |                  |                  |              |

| Legend:          |         |                   |         |                |                  |                  |              |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | mented bit, read | l as '0'         |              |

| u = Bit is unch  | anged   | x = Bit is unkr   | nown    | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |              |

bit 7-0 **PMADR<7:0>**: Specifies the Least Significant bits for program memory address

#### REGISTER 10-4: PMADRH: PROGRAM MEMORY ADDRESS HIGH BYTE REGISTER

| U-1   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|------------|---------|---------|---------|

| —     |         |         |         | PMADR<14:8 | >       |         |         |

| bit 7 |         |         |         |            |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 Unimplemented: Read as '1'

bit 6-0 **PMADR<14:8>**: Specifies the Most Significant bits for program memory address

| W-0/0            | W-0/0    | W-0/0             | W-0/0       | W-0/0          | W-0/0            | W-0/0            | W-0/0        |

|------------------|----------|-------------------|-------------|----------------|------------------|------------------|--------------|

|                  |          | Prog              | gram Memory | Control Regist | ter 2            |                  |              |

| bit 7            |          |                   |             |                |                  |                  | bit 0        |

|                  |          |                   |             |                |                  |                  |              |

| Legend:          |          |                   |             |                |                  |                  |              |

| R = Readable     | bit      | W = Writable I    | bit         | U = Unimpler   | mented bit, read | l as '0'         |              |

| S = Bit can onl  | y be set | x = Bit is unkn   | iown        | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set |          | '0' = Bit is clea | ared        |                |                  |                  |              |

#### REGISTER 10-6: PMCON2: PROGRAM MEMORY CONTROL 2 REGISTER

#### bit 7-0 Flash Memory Unlock Pattern bits

To unlock writes, a 55h must be written first, followed by an AAh, before setting the WR bit of the PMCON1 register. The value written to this register is used to unlock the writes. There are specific timing requirements on these writes.

#### TABLE 10-3: SUMMARY OF REGISTERS ASSOCIATED WITH FLASH PROGRAM MEMORY

| Name   | Bit 7 | Bit 6                             | Bit 5  | Bit 4 | Bit 3     | Bit 2  | Bit 1 | Bit 0 | Register<br>on Page |

|--------|-------|-----------------------------------|--------|-------|-----------|--------|-------|-------|---------------------|

| INTCON | GIE   | PEIE                              | TMR0IE | INTE  | IOCIE     | TMR0IF | INTF  | IOCIF | 77                  |

| PMCON1 | (1)   | CFGS                              | LWLO   | FREE  | WRERR     | WREN   | WR    | RD    | 103                 |

| PMCON2 |       | Program Memory Control Register 2 |        |       |           |        |       |       |                     |

| PMADRL |       |                                   |        | PMAD  | R<7:0>    |        |       |       | 102                 |

| PMADRH | (1)   |                                   |        | Р     | MADR<14:8 | }>     |       |       | 102                 |

| PMDATL |       | PMDAT<7:0>                        |        |       |           |        |       |       | 101                 |

| PMDATH |       |                                   |        |       |           |        |       |       | 101                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Flash program memory. **Note 1:** Unimplemented, read as '1'.

#### TABLE 10-4: SUMMARY OF CONFIGURATION WORD WITH FLASH PROGRAM MEMORY

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4        | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|-----------------|----------|----------|---------|---------|---------------------|

|         | 13:8 |         |         |          |                 | CLKOUTEN | BORE     | N<1:0>  |         | 50                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WD <sup>-</sup> | TE<1:0>  |          | FOSC    | <1:0>   | 53                  |

|         | 13:8 | _       |         | LVP      | DEBUG           | LPBOR    | BORV     | STVREN  | _       | 54                  |

| CONFIG2 | 7:0  | _       |         |          |                 | _        |          | WRT     | <1:0>   | 54                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Flash program memory.

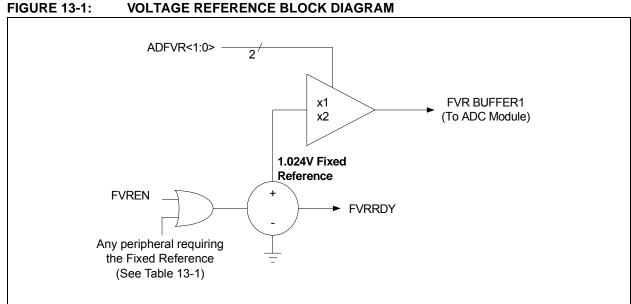

#### 13.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference, or FVR, is a stable voltage reference, independent of VDD, with 1.024V and 2.048V selectable output levels. The output of the FVR can be configured as the FVR input channel on the ADC.

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

#### 13.1 Independent Gain Amplifier

The output of the FVR supplied to the ADC is routed through a programmable gain amplifier. Each amplifier can be programmed for a gain of 1x or 2x, to produce the two possible voltage levels.

The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference **Section 15.0 "Analog-to-Digital Converter (ADC) Module"** for additional information.

### 13.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize. Once the circuits stabilize and are ready for use, the FVRRDY bit of the FVRCON register will be set. See **Section 25.0** "**Electrical Specifications**" for the minimum delay requirement.

| TABLE 13-1: | PERIPHERALS REQUIRING THE FIXED VOLTAGE REFERENCE (FVR) |

|-------------|---------------------------------------------------------|

|-------------|---------------------------------------------------------|

| Peripheral | Conditions                             | Description                                         |

|------------|----------------------------------------|-----------------------------------------------------|

| HFINTOSC   | FOSC<1:0> = 00 and<br>IRCF<3:0> = 000x | INTOSC is active and device is not in Sleep.        |

|            | BOREN<1:0> = 11                        | BOR always enabled.                                 |

| BOR        | BOREN<1:0> = 10 and BORFS = 1          | BOR disabled in Sleep mode, BOR Fast Start enabled. |

|            | BOREN<1:0> = 01 and BORFS = 1          | BOR under software control, BOR Fast Start enabled. |

## 15.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADxRESxH:ADxRESxL register pair). The ADC voltage reference is software selectable to be either internally generated or externally supplied.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

The PIC16LF1554/1559 has two ADCs, which can operate together or separately. Both ADCs can generate an interrupt upon completion of a conversion. This interrupt can be used to wake up the device from Sleep. Figure 15-1 shows the block diagram of the two ADCs.

#### AAD1CON3 AD10N AAD1PRE AN1x AAD1ACQ AN0 AAD1GRD $\boxtimes$ AN1 AAD1CAP AD1RES<sub>x</sub>H AD1RESxL AN2 \*\*\* AN10 CH1x ΕN Hardware 16 AN11 CVD AN12 0 = Left Justify AN13 AN14<sup>(1)</sup> IN ADC1 OUT 1 = Right Justify AAD1CH - Secondary Channel Select AN15<sup>(1)</sup> AN16<sup>(1)</sup> VPOS GO CLK Automatic Trigger $\mathsf{V}_{\mathsf{REFH}}$ Temp Indicator Sources FVR Buffer1 AAD1CON2 CHS<4.0> GO/DONE1 OR Positive Voltage Clock GO/DONE\_ALL Reference Source ADFM ADPREF<1:0> ADCS<2:0> GO/DONE2 OR Automatic Trigger Sources AAD2CON2 GO CLK AN20 V<sub>POS</sub> AN21 AAD2CH - Secondary Channel Select AN22 0 = Left Justify AN23 AN24<sup>(1)</sup> IN ADC2 OUT 1 = Right Justify AN25<sup>(1)</sup> Hardware 16 AN26<sup>(1)</sup> CVD CH2x ΕN VREEH AD2RESxH AD2RESxL AAD2CAP Temp Indicator $\boxtimes$ AAD2GRD . FVR Buffer2 AAD2ACO AN2x AD2ON AAD2PRE CHS<4:0> AAD2CON3 (1) PIC16LF1559 only.

### FIGURE 15-1: ADC SIMPLIFIED BLOCK DIAGRAM

## **REGISTER 16-13:** AADxRESxH: HARDWARE CVD RESULT REGISTER MSB ADFM = $0^{(1)}$

| R/W-x/u                           | R/W-x/u                             | R/W-x/u | R/W-x/u      | R/W-x/u          | R/W-x/u       | R/W-x/u          | R/W-x/u      |

|-----------------------------------|-------------------------------------|---------|--------------|------------------|---------------|------------------|--------------|

|                                   |                                     |         | ADRES        | Sx<9:2>          |               |                  |              |

| bit 7                             |                                     |         |              |                  |               |                  | bit 0        |

|                                   |                                     |         |              |                  |               |                  |              |

| Legend:                           |                                     |         |              |                  |               |                  |              |

| R = Readable bit W = Writable bit |                                     | bit     | U = Unimpler | mented bit, read | d as '0'      |                  |              |

| u = Bit is unch                   | Bit is unchanged x = Bit is unknown |         | iown         | -n/n = Value a   | at POR and BO | R/Value at all o | other Resets |

bit 7-0 ADRESx<9:2>: ADC Result Register bits Upper eight bits of 10-bit conversion result

'1' = Bit is set

Note 1: See Section 16.1.11 "Hardware CVD Register Mapping" for more information.

'0' = Bit is cleared

#### **REGISTER 16-14:** AADxRESxL: HARDWARE CVD RESULT REGISTER LSL ADFM = $0^{(1)}$

| R/W-x/u | R/W-x/u | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|-----|-----|-----|-----|-----|-------|

| ADRES   | x<1:0>  | —   | —   | —   | _   | _   | —     |

| bit 7   |         |     |     |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 ADRESx<1:0>: ADC Result Register bits

Lower two bits of 10-bit conversion result

bit 5-0 Reserved: Do not use.

Note 1: See Section 16.1.11 "Hardware CVD Register Mapping" for more information.

| R/W-0/u          | R/W-0/u                                                                                                                                                                                                                            | R/W-0/u                           | R/W-0/u       | R/W/HC-0/u                                            | R-x/x       | U-0 | R/W-0/u |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------|-------------------------------------------------------|-------------|-----|---------|

| TMR1GE           | T1GPOL                                                                                                                                                                                                                             | T1GTM                             | T1GSPM        | T1GGO/DONE                                            | T1GVAL      | —   | T1GSS   |

| pit 7            |                                                                                                                                                                                                                                    |                                   |               |                                                       |             |     | bit C   |

| lagandi          |                                                                                                                                                                                                                                    |                                   |               |                                                       |             |     |         |

| Legend:          | L :1                                                                                                                                                                                                                               |                                   | . : 4         |                                                       |             | 3   |         |

| R = Readable     |                                                                                                                                                                                                                                    | W = Writable bit                  |               | U = Unimplemente                                      |             |     |         |

| u = Bit is unch  | anged                                                                                                                                                                                                                              | x = Bit is unknown                |               | -n/n = Value at POR and BOR/Value at all other Resets |             |     |         |

| '1' = Bit is set |                                                                                                                                                                                                                                    | '0' = Bit is clea                 | ared          | HC = Bit is cleared                                   | by hardware |     |         |

| bit 7            | TMR1GE: Timer1 Gate Enable bit<br><u>If TMR1ON = 0</u> :<br>This bit is ignored<br><u>If TMR1ON = 1</u> :<br>1 = Timer1 counting is controlled by the Timer1 gate function<br>0 = Timer1 counts regardless of Timer1 gate function |                                   |               |                                                       |             |     |         |

| bit 6            | <b>T1GPOL:</b> Timer1 Gate Polarity bit<br>1 = Timer1 gate is active-high (Timer1 counts when gate is high)<br>0 = Timer1 gate is active-low (Timer1 counts when gate is low)                                                      |                                   |               |                                                       |             |     |         |

| bit 5            | <b>T1GTM:</b> Timer1 Gate Toggle Mode bit<br>1 = Timer1 Gate Toggle mode is enabled<br>0 = Timer1 Gate Toggle mode is disabled and toggle flip-flop is cleared<br>Timer1 gate flip-flop toggles on every rising edge.              |                                   |               |                                                       |             |     |         |

| bit 4            | <b>T1GSPM:</b> Timer1 Gate Single-Pulse Mode bit<br>1 = Timer1 gate Single-Pulse mode is enabled and is controlling Timer1 gate<br>0 = Timer1 gate Single-Pulse mode is disabled                                                   |                                   |               |                                                       |             |     |         |

| bit 3            | <b>T1GGO/DONE:</b> Timer1 Gate Single-Pulse Acquisition Status bit<br>1 = Timer1 gate single-pulse acquisition is ready, waiting for an edge<br>0 = Timer1 gate single-pulse acquisition has completed or has not been started     |                                   |               |                                                       |             |     |         |

| bit 2            | <b>T1GVAL:</b> Timer1 Gate Value Status bit<br>Indicates the current state of the Timer1 gate that could be provided to TMR1H:TMR1L.<br>Unaffected by Timer1 Gate Enable (TMR1GE).                                                 |                                   |               |                                                       |             |     |         |

| bit 1            | Unimplement                                                                                                                                                                                                                        | ted: Read as '0                   | 3             |                                                       |             |     |         |

| bit 0            | T1GSS: Time                                                                                                                                                                                                                        | r1 Gate Source                    | Select bits   |                                                       |             |     |         |

|                  | 01 = Timer0 c<br>00 = Timer1 g                                                                                                                                                                                                     | overflow output<br>gate pin (T1G) | (T0_overflow) |                                                       |             |     |         |

#### REGISTER 18-2: T1GCON: TIMER1 GATE CONTROL REGISTER

#### 20.2 SPI Mode Overview

The Serial Peripheral Interface (SPI) bus is a synchronous serial data communication bus that operates in Full-Duplex mode. Devices communicate in a master/slave environment where the master device initiates the communication. A slave device is controlled through a Chip Select known as Slave Select.

The SPI bus specifies four signal connections:

- · Serial Clock (SCK)

- Serial Data Out (SDO)

- · Serial Data In (SDI)

- Slave Select (SS)

Figure 20-1 shows the block diagram of the MSSP module when operating in SPI mode.

The SPI bus operates with a single master device and one or more slave devices. When multiple slave devices are used, an independent Slave Select connection is required from the master device to each slave device.

Figure 20-4 shows a typical connection between a master device and multiple slave devices.

The master selects only one slave at a time. Most slave devices have tri-state outputs so their output signal appears disconnected from the bus when they are not selected.

Transmissions involve two shift registers, eight bits in size, one in the master and one in the slave. With either the master or the slave device, data is always shifted out one bit at a time, with the Most Significant bit (MSb) shifted out first. At the same time, a new Least Significant bit (LSb) is shifted into the same register.

Figure 20-5 shows a typical connection between two processors configured as master and slave devices.

Data is shifted out of both shift registers on the programmed clock edge and latched on the opposite edge of the clock.

The master device transmits information out on its SDO output pin which is connected to, and received by, the slave's SDI input pin. The slave device transmits information out on its SDO output pin, which is connected to, and received by, the master's SDI input pin.

To begin communication, the master device first sends out the clock signal. Both the master and the slave devices should be configured for the same clock polarity.

The master device starts a transmission by sending out the MSb from its shift register. The slave device reads this bit from that same line and saves it into the LSb position of its shift register.

During each SPI clock cycle, a full-duplex data transmission occurs. This means that while the master device is sending out the MSb from its shift register (on

its SDO pin) and the slave device is reading this bit and saving it as the LSb of its shift register, that the slave device is also sending out the MSb from its shift register (on its SDO pin) and the master device is reading this bit and saving it as the LSb of its shift register.

After eight bits have been shifted out, the master and slave have exchanged register values.

If there is more data to exchange, the shift registers are loaded with new data and the process repeats itself.

Whether the data is meaningful or not (dummy data), depends on the application software. This leads to three scenarios for data transmission:

- Master sends useful data and slave sends dummy data.

- Master sends useful data and slave sends useful data.

- Master sends dummy data and slave sends useful data.

Transmissions may involve any number of clock cycles. When there is no more data to be transmitted, the master stops sending the clock signal and it deselects the slave.

Every slave device connected to the bus that has not been selected through its slave select line must disregard the clock and transmission signals and must not transmit out any data of its own.

#### 20.4 I<sup>2</sup>C MODE OPERATION

All MSSP I<sup>2</sup>C communication is byte oriented and shifted out MSb first. Six SFR registers and two interrupt flags interface the module with the PIC<sup>®</sup> microcontroller and user software. Two pins, SDA and SCL, are exercised by the module to communicate with other external I<sup>2</sup>C devices.

#### 20.4.1 BYTE FORMAT

All communication in  $I^2C$  is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent back. After the 8th falling edge of the SCL line, the device outputting data on the SDA changes that pin to an input and reads in an acknowledge value on the next clock pulse.

The clock signal, SCL, is provided by the master. Data is valid to change while the SCL signal is low, and sampled on the rising edge of the clock. Changes on the SDA line while the SCL line is high define special conditions on the bus, explained below.

#### 20.4.2 DEFINITION OF I<sup>2</sup>C TERMINOLOGY

There is language and terminology in the description of  $I^2C$  communication that have definitions specific to  $I^2C$ . That word usage is defined below and may be used in the rest of this document without explanation. This table was adapted from the Philips  $I^2C$  specification.

#### 20.4.3 SDA AND SCL PINS

Selection of any  $I^2C$  mode with the SSPEN bit set, forces the SCL and SDA pins to be open-drain. These pins should be set by the user to inputs by setting the appropriate TRISx bits.

**Note:** Data is tied to output zero when an I<sup>2</sup>C mode is enabled.

#### 20.4.4 SDA HOLD TIME

The hold time of the SDA pin is selected by the SDAHT bit of the SSPCON3 register. Hold time is the time SDA is held valid after the falling edge of SCL. Setting the SDAHT bit selects a longer 300 ns minimum hold time and may help on buses with large capacitance.

| TABLE 20-2:         |                                                                                                                                                                                                                 |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TERM                | Description                                                                                                                                                                                                     |

| Transmitter         | The device which shifts data out onto the bus.                                                                                                                                                                  |

| Receiver            | The device which shifts data in<br>from the bus.                                                                                                                                                                |

| Master              | The device that initiates a transfer, generates clock signals and terminates a transfer.                                                                                                                        |

| Slave               | The device addressed by the master.                                                                                                                                                                             |

| Multi-master        | A bus with more than one device that can initiate data transfers.                                                                                                                                               |

| Arbitration         | Procedure to ensure that only one master at a time controls the bus. Winning arbitration ensures that the message is not corrupted.                                                                             |

| Synchronization     | Procedure to synchronize the<br>clocks of two or more devices on<br>the bus.                                                                                                                                    |

| Idle                | No master is controlling the bus,<br>and both SDA and SCL lines are<br>high.                                                                                                                                    |

| Active              | Any time one or more master devices are controlling the bus.                                                                                                                                                    |

| Addressed<br>Slave  | Slave device that has received a matching address and is actively being clocked by a master.                                                                                                                    |

| Matching<br>Address | Address byte that is clocked into a slave that matches the value stored in SSPADD.                                                                                                                              |

| Write Request       | Slave receives a matching address with $R/\overline{W}$ bit clear, and is ready to clock in data.                                                                                                               |

| Read Request        | Master sends an address byte with<br>the $R/\overline{W}$ bit set, indicating that it<br>wishes to clock data out of the<br>slave. This data is the next and all<br>following bytes until a Restart or<br>Stop. |

| Clock Stretching    | When a device on the bus hold SCL low to stall communication.                                                                                                                                                   |

| Bus Collision       | Any time the SDA line is sampled<br>low by the module while it is<br>outputting and expected high<br>state.                                                                                                     |

#### 20.5.3.3 7-Bit Transmission with Address Hold Enabled

Setting the AHEN bit of the SSPCON3 register enables additional clock stretching and interrupt generation after the 8th falling edge of a received matching address. Once a matching address has been clocked in, CKP is cleared and the SSP1IF interrupt is set.

Figure 20-19 displays a standard waveform of a 7-bit Address Slave Transmission with AHEN enabled.

- 1. Bus starts Idle.

- Master sends Start condition; the S bit of SSPSTAT is set; SSP1IF is set if interrupt on Start detect is enabled.

- Master sends matching address with R/W bit set. After the 8th falling edge of the SCL line the CKP bit is cleared and SSP1IF interrupt is generated.

- 4. Slave software clears SSP1IF.

- 5. Slave software reads ACKTIM bit of SSPCON3 register, and  $R/\overline{W}$  and  $D/\overline{A}$  of the SSPSTAT register to determine the source of the interrupt.

- 6. Slave reads the address value from the SSPBUF register clearing the BF bit.

- Slave software decides from this information if it wishes to ACK or not ACK and sets the ACKDT bit of the SSPCON2 register accordingly.

- 8. Slave sets the CKP bit releasing SCL.

- 9. Master clocks in the  $\overline{ACK}$  value from the slave.

- Slave hardware automatically clears the CKP bit and sets SSP1IF after the ACK if the R/W bit is set.

- 11. Slave software clears SSP1IF.

- 12. Slave loads value to transmit to the master into SSPBUF setting the BF bit.

Note: SSPBUF cannot be loaded until after the ACK.

- 13. Slave sets CKP bit releasing the clock.

- 14. Master clocks out the data from the slave and sends an ACK value on the 9th SCL pulse.

- 15. Slave hardware copies the ACK value into the ACKSTAT bit of the SSPCON2 register.

- 16. Steps 10-15 are repeated for each byte transmitted to the master from the slave.

- 17. If the master sends a not ACK the slave releases the bus allowing the master to send a Stop and end the communication.

**Note:** Master must send a not ACK on the last byte to ensure that the slave releases the SCL line to receive a Stop.

#### 21.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH Mark state which represents a '1' data bit, and a VOL Space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the Mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 21-5 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

#### 21.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 21-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXREG register.

#### 21.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART and automatically configures the TX/CK I/O pin as an output. If the TX/CK pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSELx bit.

**Note:** The TXIF Transmitter Interrupt flag is set when the TXEN enable bit is set.

#### 21.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXREG until the Stop bit of the previous character has been transmitted. The pending character in the TXREG is then transferred to the TSR in one TCY immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXREG.

#### 21.1.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the SCKP bit of the BAUDCON register. The default state of this bit is '0' which selects high true transmit idle and data bits. Setting the SCKP bit to '1' will invert the transmit data resulting in low true idle and data bits. The SCKP bit controls transmit data polarity in Asynchronous mode only. In Synchronous mode, the SCKP bit has a different function. See **Section 21.5.1.2 "Clock Polarity"**.

#### 21.1.1.4 Transmit Interrupt Flag

The TXIF interrupt flag bit of the PIR1 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXREG. In other words, the TXIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXREG. The TXIF flag bit is not cleared immediately upon writing TXREG. TXIF becomes valid in the second instruction cycle following the write execution. Polling TXIF immediately following the TXREG write will return invalid results. The TXIF bit is read-only, it cannot be set or cleared by software.

The TXIF interrupt can be enabled by setting the TXIE interrupt enable bit of the PIE1 register. However, the TXIF flag bit will be set whenever the TXREG is empty, regardless of the state of TXIE enable bit.

To use interrupts when transmitting data, set the TXIE bit only when there is more data to send. Clear the TXIE interrupt enable bit upon writing the last character of the transmission to the TXREG.

#### 21.1.2.8 Asynchronous Reception Set-up:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 21.4 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSELx bit for the RX pin (if applicable).

- Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 4. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set the RX9 bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 8. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

#### 21.1.2.9 9-Bit Address Detection Mode Set-up

This mode would typically be used in RS-485 systems. To set up an asynchronous reception with address detect enable:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 21.4 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSELx bit for the RX pin (if applicable).

- Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. Enable 9-bit reception by setting the RX9 bit.

- 6. Enable address detection by setting the ADDEN bit.

- 7. Enable reception by setting the CREN bit.

- 8. The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 9. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- 10. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 11. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 12. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

#### **Instruction Descriptions** 24.2

| ADDFSR           | Add Literal to FSRn                                                                           |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] ADDFSR FSRn, k                                                                      |  |  |  |

| Operands:        | $-32 \le k \le 31$<br>n $\in$ [ 0, 1]                                                         |  |  |  |

| Operation:       | $FSR(n) + k \rightarrow FSR(n)$                                                               |  |  |  |

| Status Affected: | None                                                                                          |  |  |  |

| Description:     | The signed 6-bit literal 'k' is added to<br>the contents of the FSRnH:FSRnL<br>register pair. |  |  |  |

|                  | FSRn is limited to the range 0000h -                                                          |  |  |  |

FFFFh. Moving beyond these bounds will cause the FSR to wrap-around.

| ANDLW            | AND literal with W                                                                                              |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] ANDLW k                                                                                               |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                             |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                 |  |  |  |

| Status Affected: | Z                                                                                                               |  |  |  |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |  |  |  |

| ADDLW            | Add literal and W                                                                                                   |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                            |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                 |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                   |  |  |  |

| Status Affected: | C, DC, Z                                                                                                            |  |  |  |

| Description:     | The contents of the W register are<br>added to the 8-bit literal 'k' and the<br>result is placed in the W register. |  |  |  |

| ANDWF            | AND W with f                                                                                                                                                    |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                      |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |

| Description:     | AND the W register with register 'f'. If<br>'d' is '0', the result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f'. |  |  |

| ADDWF            | Add W and f                                                                                                                                                                     |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                 |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                           |

| Status Affected: | C, DC, Z                                                                                                                                                                        |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the result is<br>stored in the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |

| ASRF             | Arithmetic Right Shift                                                                                                                                                                                             |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]ASRF f{,d}                                                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                  |

| Operation:       | (f<7>)→ dest<7><br>(f<7:1>) → dest<6:0>,<br>(f<0>) → C,                                                                                                                                                            |

| Status Affected: | C, Z                                                                                                                                                                                                               |

| Description:     | The contents of register 'f' are shifted<br>one bit to the right through the Carry<br>flag. The MSb remains unchanged. If<br>'d' is '0', the result is placed in W. If 'd'<br>is '1', the result is stored back in |

register 'f'.

| ► | register f | - | С |  |

|---|------------|---|---|--|

| ADDWFC |

|--------|

|--------|

ADD W and CARRY bit to f

| Syntax:          | [ label ] ADDWFC f {,d}                                                                                                                                               |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                           |  |

| Operation:       | $(W) + (f) + (C) \rightarrow dest$                                                                                                                                    |  |

| Status Affected: | C, DC, Z                                                                                                                                                              |  |

| Description:     | Add W, the Carry flag and data men<br>ory location 'f'. If 'd' is '0', the result<br>placed in W. If 'd' is '1', the result is<br>placed in data memory location 'f'. |  |

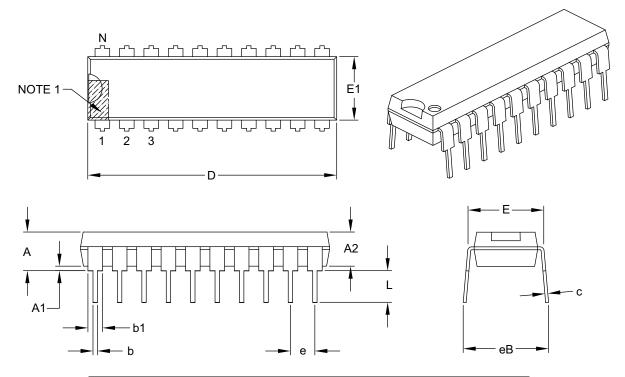

#### 20-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    |          | INCHES |       |  |

|----------------------------|----------|----------|--------|-------|--|

| Dimension                  | n Limits | MIN      | NOM    | MAX   |  |

| Number of Pins             | Ν        |          | 20     |       |  |

| Pitch                      | е        | .100 BSC |        |       |  |

| Top to Seating Plane       | А        | _        | -      | .210  |  |

| Molded Package Thickness   | A2       | .115     | .130   | .195  |  |

| Base to Seating Plane      | A1       | .015     | -      | -     |  |

| Shoulder to Shoulder Width | E        | .300     | .310   | .325  |  |

| Molded Package Width       |          | .240     | .250   | .280  |  |

| Overall Length             | D        | .980     | 1.030  | 1.060 |  |

| Tip to Seating Plane       | L        | .115     | .130   | .150  |  |

| Lead Thickness             | С        | .008     | .010   | .015  |  |

| Upper Lead Width           |          | .045     | .060   | .070  |  |

| Lower Lead Width           |          | .014     | .018   | .022  |  |

| Overall Row Spacing §      |          | -        | _      | .430  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-019B

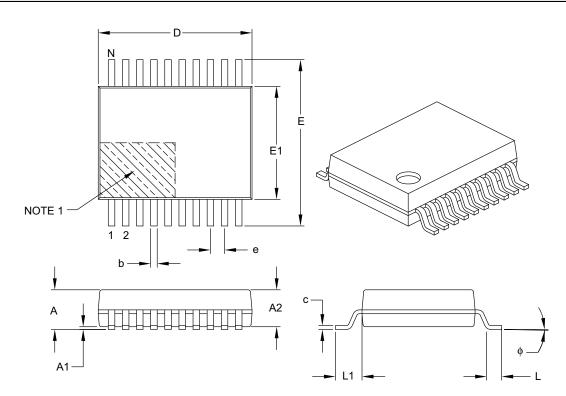

#### 20-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    |          | MILLIMETERS |      |  |

|--------------------------|----------|----------|-------------|------|--|

| Dimensio                 | n Limits | MIN      | NOM         | MAX  |  |

| Number of Pins N         |          | 20       |             |      |  |

| Pitch                    | е        | 0.65 BSC |             |      |  |

| Overall Height           | А        | -        | -           | 2.00 |  |

| Molded Package Thickness | A2       | 1.65     | 1.75        | 1.85 |  |

| Standoff                 | A1       | 0.05     | -           | -    |  |

| Overall Width            | Е        | 7.40     | 7.80        | 8.20 |  |

| Molded Package Width     | E1       | 5.00     | 5.30        | 5.60 |  |

| Overall Length           | D        | 6.90     | 7.20        | 7.50 |  |

| Foot Length              | L        | 0.55     | 0.75        | 0.95 |  |

| Footprint                | L1       | 1.25 REF |             |      |  |

| Lead Thickness           | с        | 0.09     | -           | 0.25 |  |

| Foot Angle               | φ        | 0°       | 4°          | 8°   |  |

| Lead Width               | b        | 0.22     | -           | 0.38 |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-072B

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KEELOQ, KEELOQ logo, Kleer, LANCheck, LINK MD, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC32 logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, ETHERSYNCH, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and QUIET-WIRE are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, RightTouch logo, REAL ICE, Ripple Blocker, Serial Quad I/O, SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2014-2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-0458-3