Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1559-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address | Name                  | Bit 7                            | Bit 6                                                    | Bit 5          | Bit 4                         | Bit 3          | Bit 2         | Bit 1          | Bit 0         | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-----------------------|----------------------------------|----------------------------------------------------------|----------------|-------------------------------|----------------|---------------|----------------|---------------|-----------------------|---------------------------------|

| Bank 4  |                       |                                  |                                                          |                |                               |                |               |                |               |                       |                                 |

| 200h    | INDF0 <sup>(1)</sup>  | Addressing t                     | his location us                                          | es contents of | FSR0H/FSR0                    | L to address   | data memor    | y (not a physi | cal register) | XXXX XXXX             | uuuu uuuu                       |

| 201h    | INDF1 <sup>(1)</sup>  | Addressing t                     | his location us                                          | es contents of | FSR1H/FSR1                    | L to address   | data memor    | y (not a physi | cal register) | XXXX XXXX             | uuuu uuuu                       |

| 202h    | PCL <sup>(1)</sup>    |                                  |                                                          | Program C      | Counter (PC) L                | east Significa | ant Byte      |                |               | 0000 0000             | 0000 0000                       |

| 203h    | STATUS <sup>(1)</sup> | — — — <u>TO</u> <u>PD</u> Z DC C |                                                          |                |                               |                |               |                | 1 1000        | q quuu                |                                 |

| 204h    | FSR0L <sup>(1)</sup>  |                                  |                                                          | Indirect Da    | ata Memory Ac                 | Idress 0 Low   | Pointer       |                |               | 0000 0000             | uuuu uuuu                       |

| 205h    | FSR0H <sup>(1)</sup>  |                                  |                                                          | Indirect Da    | ita Memory Ad                 | ldress 0 High  | Pointer       |                |               | 0000 0000             | 0000 0000                       |

| 206h    | FSR1L <sup>(1)</sup>  |                                  |                                                          | Indirect Da    | ata Memory Ac                 | Idress 1 Low   | Pointer       |                |               | 0000 0000             | uuuu uuuu                       |

| 207h    | FSR1H <sup>(1)</sup>  |                                  | Indirect Data Memory Address 1 High Pointer              |                |                               |                |               |                |               | 0000 0000             | 0000 0000                       |

| 208h    | BSR <sup>(1)</sup>    | _                                | — — — BSR<4:0>                                           |                |                               |                |               |                |               | 0 0000                | 0 0000                          |

| 209h    | WREG <sup>(1)</sup>   | Working Register                 |                                                          |                |                               |                |               |                | 0000 0000     | uuuu uuuu             |                                 |

| 20Ah    | PCLATH <sup>(1)</sup> | _                                | Write Buffer for the upper 7 bits of the Program Counter |                |                               |                |               |                | -000 0000     | -000 0000             |                                 |

| 20Bh    | INTCON <sup>(1)</sup> | GIE                              | PEIE                                                     | TMR0IE         | INTE                          | IOCIE          | TMR0IF        | INTF           | IOCIF         | 0000 0000             | 0000 0000                       |

| 20Ch    | WPUA                  | _                                | _                                                        | WPUA5          | WPUA4                         | WPUA3          | WPUA2         | WPUA1          | WPUA0         | 11 1111               | 11 1111                         |

| 20Dh    | WPUB <sup>(2)</sup>   |                                  |                                                          |                | Unimplem                      | ented          |               |                |               | _                     | _                               |

|         | WPUB <sup>(3)</sup>   | WPUB7                            | WPUB6                                                    | WPUB5          | WPUB4                         | _              | _             | _              | _             | 1111                  | 1111                            |

| 20Eh    | —                     |                                  |                                                          |                | Unimplem                      | ented          |               |                |               | —                     | —                               |

| 20Fh    | —                     |                                  |                                                          |                | Unimplem                      | ented          |               |                |               | —                     | _                               |

| 210h    | —                     |                                  |                                                          |                | Unimplem                      | ented          |               |                |               | _                     | _                               |

| 211h    | SSPBUF                |                                  | Sy                                                       | nchronous Ser  | ial Port Recei                | ve Buffer/Trai | nsmit Registe | er             |               | XXXX XXXX             | uuuu uuuu                       |

| 212h    | SSPADD                |                                  | 9                                                        | Synchronous S  | Serial Port (I <sup>2</sup> C | mode) Addre    | ess Register  |                |               | 0000 0000             | 0000 0000                       |

| 213h    | SSPMSK                |                                  | Syn                                                      | chronous Seri  | al Port (I <sup>2</sup> C mo  | ode) Address   | Mask Regist   | er             |               | 1111 1111             | 1111 1111                       |

| 214h    | SSPSTAT               | SMP                              | CKE                                                      | D/A            | Р                             | S              | R/W           | UA             | BF            | 0000 0000             | 0000 0000                       |

| 215h    | SSPCON1               | WCOL                             | SSPOV                                                    | SSPEN          | CKP                           | SSPM3          | SSPM2         | SSPM1          | SSPM0         | 0000 0000             | 0000 0000                       |

| 216h    | SSPCON2               | GCEN                             | ACKSTAT                                                  | ACKDT          | ACKEN                         | RCEN           | PEN           | RSEN           | SEN           | 0000 0000             | 0000 0000                       |

| 217h    | SSPCON3               | ACKTIM                           | PCIE                                                     | SCIE           | BOEN                          | SDAHT          | SBCDE         | AHEN           | DHEN          | 0000 0000             | 0000 0000                       |

| 218h    | —                     |                                  |                                                          |                | Unimplem                      | ented          |               |                |               | —                     | —                               |

| 219h    | —                     |                                  |                                                          |                | Unimplem                      | ented          |               |                |               | —                     | —                               |

| 21Ah    | —                     |                                  |                                                          |                | Unimplem                      | ented          |               |                |               | —                     | —                               |

| 21Bh    | -                     |                                  |                                                          |                | Unimplem                      | ented          |               |                |               | _                     | _                               |

| 21Ch    | _                     |                                  |                                                          |                | Unimplem                      | ented          |               |                |               | —                     | —                               |

| 21Dh    | _                     |                                  |                                                          |                | Unimplem                      | ented          |               |                |               | —                     | _                               |

| 21Eh    | _                     |                                  |                                                          |                | Unimplem                      | ented          |               |                |               | _                     | _                               |

| 21Fh    | _                     |                                  |                                                          |                | Unimplem                      | ented          |               |                |               | _                     | _                               |

#### **TABLE 3-9:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Legend:

Note 1: These registers can be accessed from any bank.

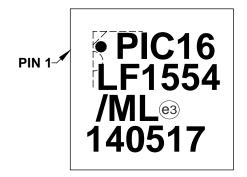

PIC16LF1554. 2:

3: PIC16LF1559.

4: These registers/bits are available at two address locations, in Bank 1 and Bank 14.

#### 5.2.2.3 Internal Oscillator Frequency Selection

The system clock speed can be selected via software using the Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register.

The outputs of the 16 MHz HFINTOSC postscaler and the LFINTOSC connect to a multiplexer (see Figure 5-1). The Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register select the frequency. One of the following frequencies can be selected via software:

- 32 MHz (requires 4x PLL)

- 16 MHz

- 8 MHz

- 4 MHz

- 2 MHz

- 1 MHz

- 500 kHz (default after Reset)

- 250 kHz

- 125 kHz

- 62.5 kHz

- 31.25 kHz

- 31 kHz (LFINTOSC)

| Note: | Following any Reset, the IRCF<3:0> bits  |

|-------|------------------------------------------|

|       | of the OSCCON register are set to '0111' |

|       | and the frequency selection is set to    |

|       | 500 kHz. The user can modify the IRCF    |

|       | bits to select a different frequency.    |

The IRCF<3:0> bits of the OSCCON register allow duplicate selections for some frequencies. These duplicate choices can offer system design trade-offs. Lower power consumption can be obtained when changing oscillator sources for a given frequency. Faster transition times can be obtained between frequency changes that use the same oscillator source.

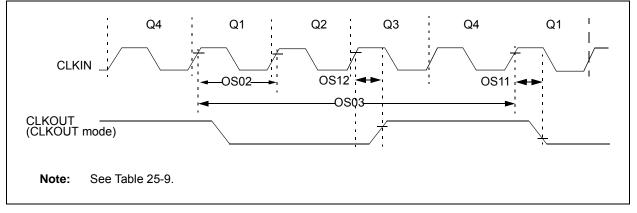

# 5.2.2.4 Internal Oscillator Clock Switch Timing

When switching between the HFINTOSC and the LFINTOSC, the new oscillator may already be shut down to save power (see Figure 5-3). If this is the case, there is a delay after the IRCF<3:0> bits of the OSCCON register are modified before the frequency selection takes place. The OSCSTAT register will reflect the current active status of the HFINTOSC and LFINTOSC oscillators. The sequence of a frequency selection is as follows:

- 1. IRCF<3:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. Clock switch is complete.

See Figure 5-3 for more details.

If the internal oscillator speed is switched between two clocks of the same source, there is no start-up delay before the new frequency is selected.

Start-up delay specifications are located in the oscillator tables of **Section 25.0** "**Electrical Specifications**".

# 5.2.2.5 32 MHz Internal Oscillator Frequency Selection

The Internal Oscillator Block can be used with the 4x PLL to produce a 32 MHz internal system clock source. The following settings are required to use the 32 MHz internal clock source:

- The FOSC bits in Configuration Word 1 must be set to use the INTOSC source as the device system clock (FOSC<1:0> = 00).

- The SCS bits in the OSCCON register must be cleared to use the clock determined by FOSC<1:0> in Configuration Word 1 (SCS<1:0> = 00).

- The IRCF bits in the OSCCON register must be set to the 8 MHz HFINTOSC set to use (IRCF<3:0> = 1110).

- The SPLLEN bit in the OSCCON register must be set to enable the 4x PLL.

The 4x PLL is not available for use with the internal oscillator when the SCS bits of the OSCCON register are set to '1x'. The SCS bits must be set to '00' to use the 4x PLL with the internal oscillator.

# 6.3 Register Definitions: BOR Control

# REGISTER 6-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u | R/W-0/u | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|---------|---------|-----|-----|-----|-----|-----|--------|

| SBOREN  | BORFS   | —   | _   | —   | —   | —   | BORRDY |

| bit 7   |         |     |     |     |     |     | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | SBOREN: Software Brown-Out Reset Enable bit<br><u>If BOREN &lt;1:0&gt; in Configuration Words = 01</u> :<br>1 = BOR Enabled<br>0 = BOR Disabled<br><u>If BOREN &lt;1:0&gt; in Configuration Words ≠ 01</u> :<br>SBOREN is read/write, but has no effect on the BOR                                                                                                                                                             |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | BORFS: Brown-Out Reset Fast Start bit <sup>(1)</sup><br><u>If BOREN &lt;1:0&gt; = 10 (Disabled in Sleep) or BOREN&lt;1:0&gt; = 01 (Under software control):</u><br>1 = Band gap is forced on always (covers sleep/wake-up/operating cases)<br>0 = Band gap operates normally, and may turn off<br><u>If BOREN&lt;1:0&gt; = 11 (Always on) or BOREN&lt;1:0&gt; = 00 (Always off)</u><br>BORFS is Read/Write, but has no effect. |

| bit 5-1 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                     |

| bit 0   | <b>BORRDY:</b> Brown-Out Reset Circuit Ready Status bit<br>1 = The Brown-out Reset circuit is active<br>0 = The Brown-out Reset circuit is inactive                                                                                                                                                                                                                                                                            |

| Note 1: | BOREN<1:0> bits are located in Configuration Words.                                                                                                                                                                                                                                                                                                                                                                            |

# 9.1 Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See **Section 25.0 "Electrical Specifications**" for the LFINTOSC tolerances.

# 9.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 9-1.

#### 9.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 9.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

#### 9.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 9-1 for more details.

#### TABLE 9-1: WDT OPERATING MODES

| WDTE<1:0> | SWDTEN | Device Mode | WDT Mode |  |

|-----------|--------|-------------|----------|--|

| 11        | Х      | Х           | Active   |  |

| 1.0       | 37     | Awake       | Active   |  |

| 10        | Х      | Sleep       | Disabled |  |

| 01        | 1      | Х           | Active   |  |

| 01        | 0      | Х           | Disabled |  |

| 00        | Х      | Х           | Disabled |  |

#### TABLE 9-2: WDT CLEARING CONDITIONS

#### 9.3 Time-out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

# 9.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- CLRWDT instruction is executed

- Device enters Sleep

- · Device wakes up from Sleep

- Oscillator fail

- WDT is disabled

- Oscillator Start-up Timer (OST) is running

See Table 9-2 for more information.

# 9.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting. When the device exits Sleep, the WDT is cleared again.

The WDT remains clear until the OST, if enabled, completes. See **Section 5.0** "**Oscillator Module**" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. The RWDT bit in the PCON register can also be used. See **Section 3.0** "**Memory Organization**" for more information.

| Conditions                                               | WDT                          |  |  |

|----------------------------------------------------------|------------------------------|--|--|

| WDTE<1:0> = 00                                           |                              |  |  |

| WDTE<1:0> = 01 and SWDTEN = 0                            |                              |  |  |

| WDTE<1:0> = 10 and enter Sleep                           | Cleared                      |  |  |

| CLRWDT Command                                           | Cleared                      |  |  |

| Oscillator Fail Detected                                 |                              |  |  |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTOSC, EXTCLK |                              |  |  |

| Exit Sleep + System Clock = XT, HS, LP                   | Cleared until the end of OST |  |  |

| Change INTOSC divider (IRCF bits)                        | Unaffected                   |  |  |

# 10.5 Write Verify

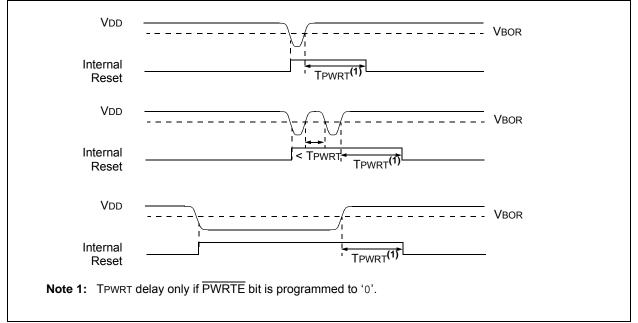

It is considered good programming practice to verify that program memory writes agree with the intended value. Since program memory is stored as a full page then the stored program memory contents are compared with the intended data stored in RAM after the last write is complete.

#### FIGURE 10-8: FLASH PROGRAM MEMORY VERIFY FLOWCHART

# 11.2 Register Definitions: Alternate Pin Function Control

| R/W-0/0                               | R/W-0/0                          | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0/0 | U-0            | R/W-0/0           | R/W-0/0  | R/W-0/0     |  |  |  |

|---------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------|-------------------|----------|-------------|--|--|--|

| RXDTSEL                               | SDOSEL                           | SSSEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SDSEL   | _              | TXCKSEL           | GRDBSEL  | GRDASEL     |  |  |  |

| bit 7                                 |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |                |                   |          | bit         |  |  |  |

|                                       |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |                |                   |          |             |  |  |  |

| Legend:<br>R = Readable               | > hit                            | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | hit     | II = I Inimple | emented bit, read | 1 as '0' |             |  |  |  |

| u = Bit is uncl                       |                                  | x = Bit is unk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |                | at POR and BC     |          | ther Resets |  |  |  |

| (1' = Bit is set (0' = Bit is cleared |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |                |                   |          |             |  |  |  |

|                                       |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |                |                   |          |             |  |  |  |

| bit 7                                 | RXDTSEL: F                       | Pin Selection bi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | t(1)    |                |                   |          |             |  |  |  |

|                                       |                                  | unction is on R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |                |                   |          |             |  |  |  |

|                                       |                                  | unction is on R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |                |                   |          |             |  |  |  |

| bit 6                                 |                                  | n Selection bit <sup>(</sup><br>nction is on RC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |                |                   |          |             |  |  |  |

|                                       |                                  | iction is on RC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |                |                   |          |             |  |  |  |

| bit 5                                 | SSSEL: Pin                       | Selection bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |                |                   |          |             |  |  |  |

|                                       | For 14 Pin Device (PIC16LF1554): |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |                |                   |          |             |  |  |  |

|                                       |                                  | tion is on RA3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ,       |                |                   |          |             |  |  |  |

|                                       | $1 = \overline{SS}$ funct        | tion is on RC3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |                |                   |          |             |  |  |  |

|                                       |                                  | <u>evice</u> (PIC16LF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | =1559): |                |                   |          |             |  |  |  |

|                                       |                                  | tion is on RA3<br>tion is on RC6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |                |                   |          |             |  |  |  |

| bit 4                                 | SDSEL: Pin                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |                |                   |          |             |  |  |  |

| Sit 1                                 |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -1554): |                |                   |          |             |  |  |  |

|                                       |                                  | For 14 Pin Device (PIC16LF1554):<br>0 = SDA / SDI function is on RC1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |                |                   |          |             |  |  |  |

|                                       |                                  | DI function is o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |                |                   |          |             |  |  |  |