Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Detuils                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 17                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 17x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

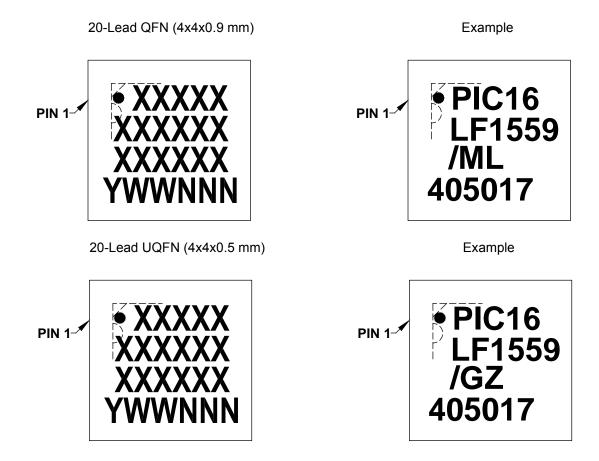

| Package / Case             | 20-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 20-QFN (4x4)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1559t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 7.5 "Automatic Context Saving"**, for more information.

# 2.2 16-Level Stack with Overflow and Underflow

These devices have a hardware stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled, will cause a software Reset. See section **Section 3.4** "**Stack**" for more details.

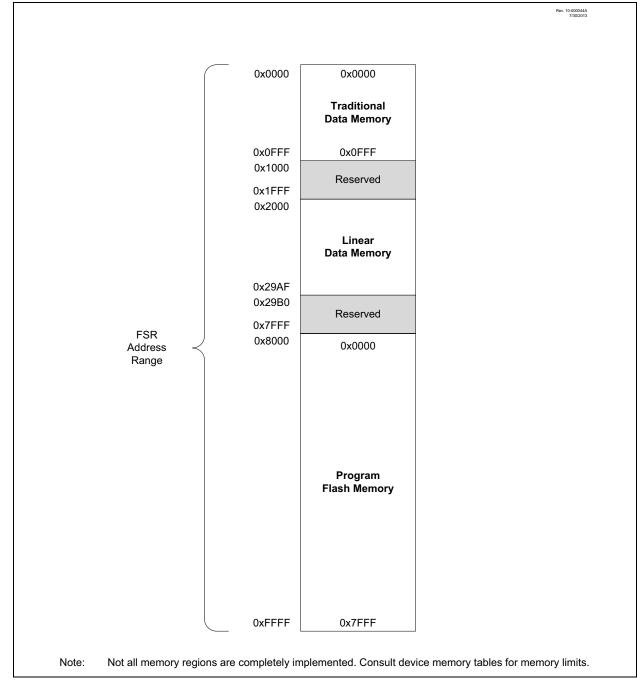

# 2.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can now also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. There are also new instructions to support the FSRs. See **Section 3.5 "Indirect Addressing"** for more details.

# 2.4 Instruction Set

There are 49 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 24.0** "Instruction Set Summary" for more details.

#### **TABLE 3-3:** PIC16LF1554 MEMORY MAP, BANKS 0-7

|              | BANK 0                                     |              | BANK 1                                     |              | BANK 2                                     |              | BANK 3                       |               | BANK 4                       |               | BANK 5                       |              | BANK 6                       |              | BANK 7                       |

|--------------|--------------------------------------------|--------------|--------------------------------------------|--------------|--------------------------------------------|--------------|------------------------------|---------------|------------------------------|---------------|------------------------------|--------------|------------------------------|--------------|------------------------------|

| 000h         | INDF0                                      | 080h         | INDF0                                      | 100h         | INDF0                                      | 180h         | INDF0                        | 200h          | INDF0                        | 280h          | INDF0                        | 300h         | INDF0                        | 380h         | INDF0                        |

| 001h         | INDF1                                      | 081h         | INDF1                                      | 101h         | INDF1                                      | 181h         | INDF1                        | 201h          | INDF1                        | 281h          | INDF1                        | 301h         | INDF1                        | 381h         | INDF1                        |

| 002h         | PCL                                        | 082h         | PCL                                        | 102h         | PCL                                        | 182h         | PCL                          | 202h          | PCL                          | 282h          | PCL                          | 302h         | PCL                          | 382h         | PCL                          |

| 003h         | STATUS                                     | 083h         | STATUS                                     | 103h         | STATUS                                     | 183h         | STATUS                       | 203h          | STATUS                       | 283h          | STATUS                       | 303h         | STATUS                       | 383h         | STATUS                       |

| 004h         | FSR0L                                      | 084h         | FSR0L                                      | 104h         | FSR0L                                      | 184h         | FSR0L                        | 204h          | FSR0L                        | 284h          | FSR0L                        | 304h         | FSR0L                        | 384h         | FSR0L                        |

| 005h         | FSR0H                                      | 085h         | FSR0H                                      | 105h         | FSR0H                                      | 185h         | FSR0H                        | 205h          | FSR0H                        | 285h          | FSR0H                        | 305h         | FSR0H                        | 385h         | FSR0H                        |

| 006h         | FSR1L                                      | 086h         | FSR1L                                      | 106h         | FSR1L                                      | 186h         | FSR1L                        | 206h          | FSR1L                        | 286h          | FSR1L                        | 306h         | FSR1L                        | 386h         | FSR1L                        |

| 007h         | FSR1H                                      | 087h         | FSR1H                                      | 107h         | FSR1H                                      | 187h         | FSR1H                        | 207h          | FSR1H                        | 287h          | FSR1H                        | 307h         | FSR1H                        | 387h         | FSR1H                        |

| 008h         | BSR                                        | 088h         | BSR                                        | 108h         | BSR                                        | 188h         | BSR                          | 208h          | BSR                          | 288h          | BSR                          | 308h         | BSR                          | 388h         | BSR                          |

| 009h         | WREG                                       | 089h         | WREG                                       | 109h         | WREG                                       | 189h         | WREG                         | 209h          | WREG                         | 289h          | WREG                         | 309h         | WREG                         | 389h         | WREG                         |

| 00Ah         | PCLATH                                     | 08Ah         | PCLATH                                     | 10Ah         | PCLATH                                     | 18Ah         | PCLATH                       | 20Ah          | PCLATH                       | 28Ah          | PCLATH                       | 30Ah         | PCLATH                       | 38Ah         | PCLATH                       |

| 00Bh         | INTCON                                     | 08Bh         | INTCON                                     | 10Bh         | INTCON                                     | 18Bh         | INTCON                       | 20Bh          | INTCON                       | 28Bh          | INTCON                       | 30Bh         | INTCON                       | 38Bh         | INTCON                       |

| 00Ch         | PORTA                                      | 08Ch         | TRISA                                      | 10Ch         | LATA                                       | 18Ch         | ANSELA                       | 20Ch          | WPUA                         | 28Ch          | —                            | 30Ch         | —                            | 38Ch         | —                            |

| 00Dh         |                                            | 08Dh         | _                                          | 10Dh         | _                                          | 18Dh         | _                            | 20Dh          | _                            | 28Dh          | _                            | 30Dh         | _                            | 38Dh         | _                            |

| 00Eh         | PORTC                                      | 08Eh         | TRISC                                      | 10Eh         | LATC                                       | 18Eh         | ANSELC                       | 20Eh          | _                            | 28Eh          | _                            | 30Eh         | —                            | 38Eh         | _                            |

| 00Fh         | —                                          | 08Fh         | —                                          | 10Fh         | _                                          | 18Fh         | _                            | 20Fh          | _                            | 28Fh          | -                            | 30Fh         | _                            | 38Fh         | _                            |

| 010h         |                                            | 090h         | _                                          | 110h         | _                                          | 190h         | _                            | 210h          | _                            | 290h          | —                            | 310h         | —                            | 390h         | -                            |

| 011h         | PIR1                                       | 091h         | PIE1                                       | 111h         | _                                          | 191h         | PMADRL                       | 211h          | SSPBUF                       | 291h          | _                            | 311h         | —                            | 391h         | IOCAP                        |

| 012h         | PIR2                                       | 092h         | PIE2                                       | 112h         | _                                          | 192h         | PMADRH                       | 212h          | SSPADD                       | 292h          | _                            | 312h         | —                            | 392h         | IOCAN                        |

| 013h         | _                                          | 093h         | _                                          | 113h         | _                                          | 193h         | PMDATL                       | 213h          | SSPMSK                       | 293h          | _                            | 313h         | _                            | 393h         | IOCAF                        |

| 014h         | -                                          | 094h         | -                                          | 114h         | _                                          | 194h         | PMDATH                       | 214h          | SSPSTAT                      | 294h          | _                            | 314h         | _                            | 394h         | _                            |

| 015h         | TMR0                                       | 095h         | OPTION                                     | 115h         |                                            | 195h         | PMCON1                       | 215h          | SSPCON1                      | 295h          | _                            | 315h         | _                            | 395h         | _                            |

| 016h         | TMR1L<br>TMR1H                             | 096h         | PCON                                       | 116h         | BORCON                                     | 196h         | PMCON2                       | 216h          | SSPCON2                      | 296h<br>297h  |                              | 316h         | _                            | 396h         |                              |

| 017h<br>018h | TICON                                      | 097h<br>098h | WDTCON                                     | 117h<br>118h | FVRCON                                     | 197h<br>198h | _                            | 217h<br>218h  | SSPCON3                      | 297h<br>298h  |                              | 317h<br>318h | _                            | 397h<br>398h |                              |

| 018h         | TIGCON                                     | 0901<br>099h | <br>OSCCON                                 | 119h         |                                            | 1901<br>199h | RCREG                        | 21011<br>219h |                              | 29011<br>299h |                              | 319h         |                              | 399h         |                              |

| 019h         | TMR2                                       | 0990<br>09Ah | OSCCON                                     | 11Ah         |                                            | 1990<br>19Ah | TXREG                        | 2190<br>21Ah  |                              | 2990<br>29Ah  |                              | 31Ah         |                              | 3990<br>39Ah |                              |

| F            |                                            | 1 . 1        | ADRESL/                                    | 1 1          |                                            | 1 1          |                              |               |                              |               |                              | -            | _                            | t t          |                              |

| 01Bh         | PR2                                        | 09Bh         | AD1RES0L <sup>(1)</sup>                    | 11Bh         | _                                          | 19Bh         | SPBRGL                       | 21Bh          | _                            | 29Bh          | -                            | 31Bh         | -                            | 39Bh         | _                            |

| 01Ch         | T2CON                                      | 09Ch         | ADRESH/<br>AD1RES0H <sup>(1)</sup>         | 11Ch         | _                                          | 19Ch         | SPBRGH                       | 21Ch          | _                            | 29Ch          | _                            | 31Ch         | -                            | 39Ch         | —                            |

| 01Dh         | _                                          | 09Dh         | ADCON0/<br>AD1CON0 <sup>(1)</sup>          | 11Dh         | APFCON                                     | 19Dh         | RCSTA                        | 21Dh          | —                            | 29Dh          | -                            | 31Dh         | -                            | 39Dh         | _                            |

| 01Eh         | _                                          | 09Eh         | ADCON1/<br>ADCOMCON <sup>(1)</sup>         | 11Eh         | _                                          | 19Eh         | TXSTA                        | 21Eh          | _                            | 29Eh          | _                            | 31Eh         | _                            | 39Eh         | _                            |

| 01Fh         | _                                          | 09Fh         | ADCON2/<br>AD1CON2 <sup>(1)</sup>          | 11Fh         | -                                          | 19Fh         | BAUDCON                      | 21Fh          | -                            | 29Fh          | -                            | 31Fh         | _                            | 39Fh         | -                            |

| 020h         |                                            | 0A0h         |                                            | 120h         |                                            | 1A0h         |                              | 220h          |                              | 2A0h          |                              | 320h         |                              | 3A0h         |                              |

|              | General<br>Purpose<br>Register<br>96 Bytes |              | General<br>Purpose<br>Register<br>80 Bytes |              | General<br>Purpose<br>Register<br>80 Bytes |              | Unimplemented<br>Read as '0' |               | Unimplemented<br>Read as '0' |               | Unimplemented<br>Read as '0' |              | Unimplemented<br>Read as '0' |              | Unimplemented<br>Read as '0' |

| 06Fh         |                                            | 0EFh         |                                            | 16Fh         |                                            | 1EFh         |                              | 26Fh          |                              | 2EFh          |                              | 36Fh         |                              | 3EFh         |                              |

| 070h         |                                            | 0F0h         | Accesses                                   | 170h         | Accesses                                   | 1F0h         | Accesses                     | 270h          | Accesses                     | 2F0h          | Accesses                     | 370h         | Accesses                     | 3F0h         | Accesses                     |

|              |                                            |              | 70h – 7Fh                                  |              | 70h – 7Fh                                  |              | 70h – 7Fh                    |               | 70h – 7Fh                    |               | 70h – 7Fh                    |              | 70h – 7Fh                    |              | 70h – 7Fh                    |

| 07Fh         |                                            | 0FFh         |                                            | 17Fh         |                                            | 1FFh         |                              | 27Fh          |                              | 2FFh          |                              | 37Fh         |                              | 3FFh         |                              |

PIC16LF1554/1559

Legend: = Unimplemented data memory locations, read as '0'.

Note 1: These ADC registers are the same as the registers in Bank 14.

# TABLE 3-4: PIC16LF1559 MEMORY MAP, BANKS 0-7

|      | BANK 0                                     |      | BANK 1                                     |      | BANK 2                                     |      | BANK 3                                     |      | BANK 4                                     |      | BANK 5                                     |      | BANK 6                               |      | BANK 7                       |

|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------|------|------------------------------|

| 000h | INDF0                                      | 080h | INDF0                                      | 100h | INDF0                                      | 180h | INDF0                                      | 200h | INDF0                                      | 280h | INDF0                                      | 300h | INDF0                                | 380h | INDF0                        |

| 001h | INDF1                                      | 081h | INDF1                                      | 101h | INDF1                                      | 181h | INDF1                                      | 201h | INDF1                                      | 281h | INDF1                                      | 301h | INDF1                                | 381h | INDF1                        |

| 002h | PCL                                        | 082h | PCL                                        | 102h | PCL                                        | 182h | PCL                                        | 202h | PCL                                        | 282h | PCL                                        | 302h | PCL                                  | 382h | PCL                          |

| 003h | STATUS                                     | 083h | STATUS                                     | 103h | STATUS                                     | 183h | STATUS                                     | 203h | STATUS                                     | 283h | STATUS                                     | 303h | STATUS                               | 383h | STATUS                       |

| 004h | FSR0L                                      | 084h | FSR0L                                      | 104h | FSR0L                                      | 184h | FSR0L                                      | 204h | FSR0L                                      | 284h | FSR0L                                      | 304h | FSR0L                                | 384h | FSR0L                        |

| 005h | FSR0H                                      | 085h | FSR0H                                      | 105h | FSR0H                                      | 185h | FSR0H                                      | 205h | FSR0H                                      | 285h | FSR0H                                      | 305h | FSR0H                                | 385h | FSR0H                        |

| 006h | FSR1L                                      | 086h | FSR1L                                      | 106h | FSR1L                                      | 186h | FSR1L                                      | 206h | FSR1L                                      | 286h | FSR1L                                      | 306h | FSR1L                                | 386h | FSR1L                        |

| 007h | FSR1H                                      | 087h | FSR1H                                      | 107h | FSR1H                                      | 187h | FSR1H                                      | 207h | FSR1H                                      | 287h | FSR1H                                      | 307h | FSR1H                                | 387h | FSR1H                        |

| 008h | BSR                                        | 088h | BSR                                        | 108h | BSR                                        | 188h | BSR                                        | 208h | BSR                                        | 288h | BSR                                        | 308h | BSR                                  | 388h | BSR                          |

| 009h | WREG                                       | 089h | WREG                                       | 109h | WREG                                       | 189h | WREG                                       | 209h | WREG                                       | 289h | WREG                                       | 309h | WREG                                 | 389h | WREG                         |

| 00Ah | PCLATH                                     | 08Ah | PCLATH                                     | 10Ah | PCLATH                                     | 18Ah | PCLATH                                     | 20Ah | PCLATH                                     | 28Ah | PCLATH                                     | 30Ah | PCLATH                               | 38Ah | PCLATH                       |

| 00Bh | INTCON                                     | 08Bh | INTCON                                     | 10Bh | INTCON                                     | 18Bh | INTCON                                     | 20Bh | INTCON                                     | 28Bh | INTCON                                     | 30Bh | INTCON                               | 38Bh | INTCON                       |

| 00Ch | PORTA                                      | 08Ch | TRISA                                      | 10Ch | LATA                                       | 18Ch | ANSELA                                     | 20Ch | WPUA                                       | 28Ch | —                                          | 30Ch | _                                    | 38Ch | _                            |

| 00Dh | PORTB                                      | 08Dh | TRISB                                      | 10Dh | LATB                                       | 18Dh | ANSELB                                     | 20Dh | WPUB                                       | 28Dh | —                                          | 30Dh | —                                    | 38Dh | —                            |

| 00Eh | PORTC                                      | 08Eh | TRISC                                      | 10Eh | LATC                                       | 18Eh | ANSELC                                     | 20Eh |                                            | 28Eh |                                            | 30Eh | —                                    | 38Eh | —                            |

| 00Fh | —                                          | 08Fh | _                                          | 10Fh | —                                          | 18Fh | _                                          | 20Fh |                                            | 28Fh |                                            | 30Fh | —                                    | 38Fh | —                            |

| 010h | —                                          | 090h | _                                          | 110h | —                                          | 190h | —                                          | 210h | -                                          | 290h | _                                          | 310h | —                                    | 390h | —                            |

| 011h | PIR1                                       | 091h | PIE1                                       | 111h | —                                          | 191h | PMADRL                                     | 211h | SSPBUF                                     | 291h |                                            | 311h | —                                    | 391h | IOCAP                        |

| 012h | PIR2                                       | 092h | PIE2                                       | 112h | —                                          | 192h | PMADRH                                     | 212h | SSPADD                                     | 292h |                                            | 312h | —                                    | 392h | IOCAN                        |

| 013h | —                                          | 093h | _                                          | 113h | —                                          | 193h | PMDATL                                     | 213h | SSPMSK                                     | 293h | _                                          | 313h | —                                    | 393h | IOCAF                        |

| 014h | _                                          | 094h | _                                          | 114h | _                                          | 194h | PMDATH                                     | 214h | SSPSTAT                                    | 294h | _                                          | 314h | —                                    | 394h | IOCBP                        |

| 015h | TMR0                                       | 095h | OPTION                                     | 115h | —                                          | 195h | PMCON1                                     | 215h | SSPCON1                                    | 295h |                                            | 315h | —                                    | 395h | IOCBN                        |

| 016h | TMR1L                                      | 096h | PCON                                       | 116h | BORCON                                     | 196h | PMCON2                                     | 216h | SSPCON2                                    | 296h | _                                          | 316h | —                                    | 396h | IOCBF                        |

| 017h | TMR1H                                      | 097h | WDTCON                                     | 117h | FVRCON                                     | 197h | _                                          | 217h | SSPCON3                                    | 297h | —                                          | 317h | —                                    | 397h | —                            |

| 018h | T1CON                                      | 098h | _                                          | 118h | —                                          | 198h | _                                          | 218h | _                                          | 298h | _                                          | 318h | —                                    | 398h | —                            |

| 019h | T1GCON                                     | 099h | OSCCON                                     | 119h | _                                          | 199h | RCREG                                      | 219h |                                            | 299h | _                                          | 319h | —                                    | 399h | —                            |

| 01Ah | TMR2                                       | 09Ah | OSCSTAT                                    | 11Ah | —                                          | 19Ah | TXREG                                      | 21Ah | _                                          | 29Ah | —                                          | 31Ah | —                                    | 39Ah | —                            |

| 01Bh | PR2                                        | 09Bh | ADRESL/<br>AD1RES0L <sup>(1)</sup>         | 11Bh | _                                          | 19Bh | SPBRGL                                     | 21Bh | _                                          | 29Bh | _                                          | 31Bh | —                                    | 39Bh | _                            |

| 01Ch | T2CON                                      | 09Ch | ADRESH/<br>AD1RES0H <sup>(1)</sup>         | 11Ch | _                                          | 19Ch | SPBRGH                                     | 21Ch | _                                          | 29Ch | _                                          | 31Ch | —                                    | 39Ch | _                            |

| 01Dh | _                                          | 09Dh | ADCON0/<br>AD1CON0 <sup>(1)</sup>          | 11Dh | APFCON                                     | 19Dh | RCSTA                                      | 21Dh | _                                          | 29Dh | _                                          | 31Dh | —                                    | 39Dh | _                            |

| 01Eh | _                                          | 09Eh | ADCON1/<br>ADCOMCON <sup>(1)</sup>         | 11Eh | _                                          | 19Eh | TXSTA                                      | 21Eh | _                                          | 29Eh | _                                          | 31Eh | _                                    | 39Eh | _                            |

| 01Fh | _                                          | 09Fh | ADCON2/<br>AD1CON2 <sup>(1)</sup>          | 11Fh | _                                          | 19Fh | BAUDCON                                    | 21Fh | _                                          | 29Fh | _                                          | 31Fh | —                                    | 39Fh | _                            |

| 020h |                                            | 0A0h |                                            | 120h |                                            | 1A0h |                                            | 220h |                                            | 2A0h |                                            | 320h | General Purpose<br>Register 16 Bytes | 3A0h |                              |

|      | General<br>Purpose<br>Register<br>96 Bytes |      | General<br>Purpose<br>Register<br>80 Bytes | 330h | Unimplemented<br>Read as '0'         |      | Unimplemented<br>Read as '0' |

| 06Fh |                                            | 0EFh |                                            | 16Fh |                                            | 1EFh |                                            | 26Fh |                                            | 2EFh |                                            | 36Fh |                                      | 3EFh |                              |

| 070h |                                            | 0F0h |                                            | 170h | A                                          | 1F0h | A                                          | 270h |                                            | 2F0h |                                            | 370h |                                      | 3F0h |                              |

|      |                                            |      | Accesses<br>70h – 7Fh                      |      | Accesses<br>70h – 7Fh                |      | Accesses<br>70h – 7Fh        |

| 07Fh |                                            | 0FFh | /011 - / F11                               | 17Fh | 7011 - 7711                                | 1FFh | /011 - / 11                                | 27Fh | /011 - / FII                               | 2FFh | 7011 - 7711                                | 37Fh | /011 - / F11                         | 3FFh | /011 - / 11                  |

Legend: = Unimplemented data memory locations, read as '0'.

Note 1: These ADC registers are the same as the registers in Bank 14.

DS40001761E-page 25

# 3.5 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

FIGURE 3-9: INDIRECT ADDRESSING

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- Traditional Data Memory

- Linear Data Memory

- Program Flash Memory

# 4.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Internal access to the program memory is unaffected by any code protection setting.

# 4.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See **Section 4.4** "Write **Protection**" for more information.

# 4.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as bootloader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Words define the size of the program memory block that is protected.

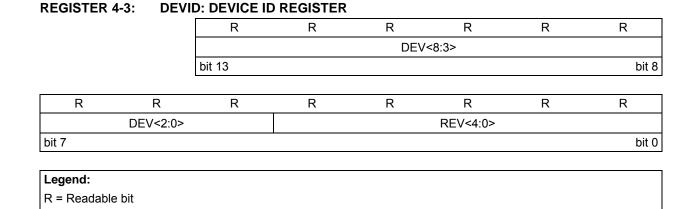

# 4.7 Register Definitions: Device ID

# 4.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See **Section 10.4 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations. For more information on checksum calculation, see the "*PIC16LF1554/1559 Memory Programming Specification*" (DS40001743).

# 4.6 Device ID and Revision ID

The memory location 8006h is where the Device ID and Revision ID are stored. The upper nine bits hold the Device ID. The lower five bits hold the Revision ID. See **Section 10.4 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

| bit 13-5 | DEV<8:0>: Device ID bits |

|----------|--------------------------|

'1' = Bit is set

| Device      | DEVID<13:0> Values |          |  |  |  |  |  |  |

|-------------|--------------------|----------|--|--|--|--|--|--|

| Device      | DEV<8:0>           | REV<4:0> |  |  |  |  |  |  |

| PIC16LF1554 | 0010 1111 000      | x xxxx   |  |  |  |  |  |  |

| PIC16LF1559 | 0010 1111 001      | x xxxx   |  |  |  |  |  |  |

'0' = Bit is cleared

### bit 4-0 REV<4:0>: Revision ID bits

These bits are used to identify the revision (see Table above under DEV<8:0>).

| REGISTER        |                   |                                |                  |                 | REGISTER 1               |                  |              |  |  |  |  |  |

|-----------------|-------------------|--------------------------------|------------------|-----------------|--------------------------|------------------|--------------|--|--|--|--|--|

| R/W-0/0         | R/W-0/0           | R/W-0/0                        | R/W-0/0          | R/W-0/0         | U-0                      | R/W-0/0          | R/W-0/0      |  |  |  |  |  |

| TMR1GIE         | AD1IE             | RCIE                           | TXIE             | SSP1IE          |                          | TMR2IE           | TMR1IE       |  |  |  |  |  |

| bit 7           |                   |                                |                  |                 |                          |                  | bit          |  |  |  |  |  |

| Lonondi         |                   |                                |                  |                 |                          |                  |              |  |  |  |  |  |

| Legend:         | - h:t             |                                | L 14             |                 | we are to all hit are ad | (0)              |              |  |  |  |  |  |

| R = Readabl     |                   | W = Writable                   |                  | •               | mented bit, read         |                  |              |  |  |  |  |  |

| u = Bit is und  | 0                 | x = Bit is unk                 |                  | -n/n = value    | at POR and BOI           | R/Value at all c | other Resets |  |  |  |  |  |

| '1' = Bit is se | et                | '0' = Bit is cle               | ared             |                 |                          |                  |              |  |  |  |  |  |

| bit 7           | TMR1GIE: T        | ïmer1 Gate Inte                | errupt Enable    | bit             |                          |                  |              |  |  |  |  |  |

|                 | 1 = Enables       | the Timer1 gate                | e acquisition in | nterrupt        |                          |                  |              |  |  |  |  |  |

|                 | 0 = Disables      | the Timer1 gat                 | e acquisition i  | nterrupt        |                          |                  |              |  |  |  |  |  |

| bit 6           | AD1IE: Anal       | og-to-Digital Co               | onverter (ADC    | 1) Interrupt Er | nable bit                |                  |              |  |  |  |  |  |

|                 |                   | 1 = Enables the ADC interrupt  |                  |                 |                          |                  |              |  |  |  |  |  |

|                 | 0 = Disables      | the ADC interr                 | upt              |                 |                          |                  |              |  |  |  |  |  |

| bit 5           | RCIE: USAR        | RT Receive Inte                | rrupt Enable b   | bit             |                          |                  |              |  |  |  |  |  |

|                 |                   | the USART rec                  | •                |                 |                          |                  |              |  |  |  |  |  |

|                 |                   | the USART re                   | -                |                 |                          |                  |              |  |  |  |  |  |

| bit 4           |                   | T Transmit Inte                | •                |                 |                          |                  |              |  |  |  |  |  |

|                 |                   | the USART tra<br>the USART tra | •                |                 |                          |                  |              |  |  |  |  |  |

| bit 3           | SSP1IE: Syr       | nchronous Seria                | al Port (MSSP    | ) Interrupt Ena | able bit                 |                  |              |  |  |  |  |  |

|                 | 1 = Enables       | 1 = Enables the MSSP interrupt |                  |                 |                          |                  |              |  |  |  |  |  |

|                 | 0 = Disables      | the MSSP inte                  | rrupt            |                 |                          |                  |              |  |  |  |  |  |

| bit 2           | Unimpleme         | nted: Read as '                | 0'               |                 |                          |                  |              |  |  |  |  |  |

| bit 1           | TMR2IE: TM        | IR2 to PR2 Mat                 | ch Interrupt E   | nable bit       |                          |                  |              |  |  |  |  |  |

|                 |                   | the Timer2 to F                |                  |                 |                          |                  |              |  |  |  |  |  |

|                 | 0 = Disables      | the Timer2 to I                | PR2 match int    | errupt          |                          |                  |              |  |  |  |  |  |

| bit 0           | TMR1IE: Tin       | ner1 Overflow I                | nterrupt Enabl   | le bit          |                          |                  |              |  |  |  |  |  |

|                 |                   | the Timer1 ove                 |                  |                 |                          |                  |              |  |  |  |  |  |

|                 | 0 = Disables      | the Timer1 ove                 | erflow interrup  | t               |                          |                  |              |  |  |  |  |  |

|                 |                   |                                |                  |                 |                          |                  |              |  |  |  |  |  |

| Note: B         | it PEIE of the IN | ITCON register                 | must be          |                 |                          |                  |              |  |  |  |  |  |

set to enable any peripheral interrupt.

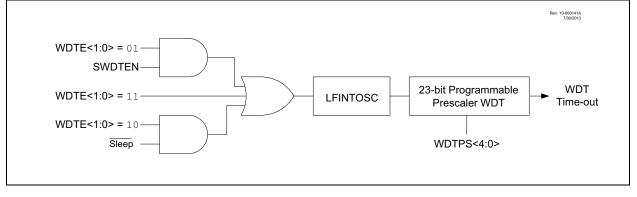

# 9.0 WATCHDOG TIMER (WDT)

The Watchdog Timer is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events.

The WDT has the following features:

- Independent clock source

- Multiple operating modes

- WDT is always on

- WDT is off when in Sleep

- WDT is controlled by software

- WDT is always off

- Configurable time-out period is from 1 ms to 256 seconds (nominal)

- Multiple Reset conditions

- Operation during Sleep

# FIGURE 9-1: WATCHDOG TIMER BLOCK DIAGRAM

# EXAMPLE 10-2: ERASING ONE ROW OF PROGRAM MEMORY

- ; This row erase routine assumes the following:

- ; 1. A valid address within the erase row is loaded in ADDRH:ADDRL

; 2. ADDRH and ADDRL are located in shared data memory 0x70 - 0x7F (common RAM)

|                      | BCF                      | INTCON,GIE                                | ; Disable ints so required sequences will execute properly                                                         |

|----------------------|--------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

|                      | BANKSEL<br>MOVF<br>MOVWF | PMADRL<br>ADDRL,W<br>PMADRL               | ; Load lower 8 bits of erase address boundary                                                                      |

|                      | MOVF<br>MOVF             | ADDRH,W<br>PMADRH                         | ; Load upper 6 bits of erase address boundary                                                                      |

|                      | BCF<br>BSF<br>BSF        | PMCON1,CFGS<br>PMCON1,FREE<br>PMCON1,WREN | ; Specify an erase operation                                                                                       |

|                      | MOVLW<br>MOVWF           | 55h<br>PMCON2                             | <pre>; Start of required sequence to initiate erase ; Write 55h</pre>                                              |

| Required<br>Sequence | MOVLW<br>MOVWF           | 0AAh<br>PMCON2                            | ;<br>; Write AAh                                                                                                   |

| Re                   | BSF<br>NOP<br>NOP        | PMCON1,WR                                 | ; Set WR bit to begin erase<br>; NOP instructions are forced as processor starts<br>; row erase of program memory. |

|                      | ivor                     |                                           | ;<br>; The processor stalls until the erase process is complete                                                    |

|                      | BCF                      | PMCON1,WREN                               | ; after erase processor continues with 3rd instruction ; Disable writes                                            |

|                      | BSF                      | INTCON, GIE                               | ; Enable interrupts                                                                                                |

#### 15.3 **Register Definitions: ADC Control** ADCON0<sup>(1)</sup>/AD1CON0<sup>(2)</sup>: ANALOG-TO-DIGITAL (ADC) 1 CONTROL REGISTER 0 **REGISTER 15-1:** R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 U-0 CHS4 CHS3 CHS2 CHS1 CHS0 GO/DONE1(4) AD10N bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets '1' = Bit is set '0' = Bit is cleared bit 7 Unimplemented: Read as '0' bit 6-2 CHS<4:0>: Analog Channel Select bits for ADC1 00000 = Channel 0, (AN0) 00001 = Channel 1, (AN1) 00010 = Channel 2, (AN2) 00011 = Reserved 00100 = Reserved 00101 = Reserved 00110 = Reserved 00111 = Reserved 01000 = Reserved 01001 = Reserved 01010 = Channel 10, (AN10) 01011 = Channel 11, (AN11) 01100 = Channel 12, (AN12) 01101 = Channel 13, (AN13) 01110 = Channel 14, (AN14)<sup>(3)</sup> 01111 = Channel 15, (AN15)<sup>(3)</sup> 10000 = Channel 16, (AN16)<sup>(3)</sup> 10001 = Reserved 10010 = Reserved 10011 = Reserved 10100 = Reserved 10101 = Reserved 10110 = Reserved 10111 = Reserved 11000 = Reserved 11001 = Reserved 11010 = Reserved 11011 = VREFH (ADC Positive Reference) 11100 = Reserved 11101 = Temperature Indicator 11110 = Reserved 11111 = Fixed Voltage Reference (FVREF) Buffer 1 Output bit 1 GO/DONE1: ADC1 Conversion Status bit (4) If AD1ON = 1ADC conversion in progress. Setting this bit starts the ADC conversion. When the RC clock source is selected, the 1 = ADC module waits one instruction before starting the conversion. ADC conversion not in progress (This bit is automatically cleared by hardware when the ADC conversion is com-0 = plete.) If this bit is cleared while a conversion is in progress, the conversion will stop and the results of the conversion up to this point will be transferred to the result registers, but the AD1IF interrupt flag bit will not be set. If AD1ON = 0= ADC conversion not in progress 0 bit 0 AD10N: ADC Module 1 Enable bit 1 = ADC converter module 1 is operating 0 = ADC converter module 1 is shut off and consumes no operating current. All Analog channels are disconnected. Bank 1 name is ADCON0. Note 1: 2: Bank 14 name is AD1CON0.

- 3: PIC16LF1559 only. Not implemented on PIC16LF1554.

- When the AD1DSEN bit is set; the GO/DONE1 bit will clear after a second conversion has completed. 4:

| Name                 | Bit 7    | Bit 6    | Bit 5      | Bit 4        | Bit 3         | Bit 2       | Bit 1    | Bit 0       | Register<br>on Page |  |  |

|----------------------|----------|----------|------------|--------------|---------------|-------------|----------|-------------|---------------------|--|--|

| AADxCAP              | —        | —        | _          | —            |               | ADDxCAF     | P<3:0>   |             | 160                 |  |  |

| AAD1CON0             | —        | CHS4     | CHS3       | CHS2         | CHS1          | CHS0        | GO/DONE1 | DONE1 AD10N |                     |  |  |

| AAD2CON0             | —        | CHS4     | CHS3       | CHS2         | CHS1          | CHS0        | GO/DONE2 | AD2ON       | 151                 |  |  |

| AADCON1/<br>ADCOMCON | ADFM     |          | ADCS<2:0>  | •            | _             | GO/DONE_ALL | ADPRE    | F<1:0>      | 154                 |  |  |

| AADxCON2             | —        | Т        | RIGSEL<2:0 | >            | _             | _           | —        |             |                     |  |  |

| AADxCON3             | ADxEPPOL | ADxIPPOL | _          | _            | _             | _           | ADxIPEN  | ADxDSEN     | 156                 |  |  |

| AADxGRD              | GRDxBOE  | GRDxAOE  | GRDxPOL    | _            | _             | _           | —        | _           | 159                 |  |  |

| AADxPRE              | —        |          |            |              | ADxPRE<6      | :0>         |          |             | 158                 |  |  |

| AADxRES0H            |          |          | /          | ADC Result 0 | Register Hi   | igh         |          |             | 161                 |  |  |

| AADxRES0L            |          |          |            | ADC Result ( | ) Register Lo | ow          |          |             | 161                 |  |  |

| AADxRES1H            |          |          | /          | ADC Result 1 | Register Hi   | igh         |          |             | 162                 |  |  |

| AADxRES1L            |          |          |            | ADC Result 1 | Register Lo   | w           |          |             | 162                 |  |  |

| AADSTAT              | —        | AD2CONV  | AD2ST      | G<1:0>       | _             | AD1CONV     | AD1ST    | G<1:0>      | 157                 |  |  |

| AADxACQ              | —        |          |            | ŀ            | ADxACQ<6      | 6:0>        |          |             | 158                 |  |  |

| ANSELA               | —        | —        | ANSA5      | ANSA4        | _             | ANSA2       | ANSA1    | ANSA0       | 109                 |  |  |

| ANSELB               | ANSB7    | ANSB6    | ANSB5      | ANSB4        | _             | _           | —        | _           | 113                 |  |  |

| ANSELC               | ANSC7    | ANSC6    | ANSC5      | ANSC4        | ANSC3         | ANSC2       | ANSC1    | ANSC0       | 117                 |  |  |

| FVRCON               | FVREN    | FVRRDY   | TSEN       | TSRNG        | _             | _           | ADFVI    | R<1:0>      | 124                 |  |  |

| INTCON               | GIE      | PEIE     | TMR0IE     | INTE         | IOCIE         | TMR0IF      | INTF     | IOCIF       | 77                  |  |  |

| PIE1                 | TMR1GIE  | AD1IE    | RCIE       | TXIE         | SSP1IE        | —           | TMR2IE   | TMR1IE      | 78                  |  |  |

| PIE2                 | —        | AD2IE    | _          | _            | BCLIE         | —           | —        | —           | 79                  |  |  |

| PIR1                 | TMR1GIF  | AD1IF    | RCIF       | TXIF         | SSP1IF        |             | TMR2IF   | TMR1IF      | 80                  |  |  |

| PIR2                 | —        | AD2IF    | _          | _            | BCLIF         | _           | _        | _           | 81                  |  |  |

| TRISA                | —        | —        | TRISA5     | TRISA4       | _(1)          | TRISA2      | TRISA1   | TRISA0      | 108                 |  |  |

| TRISB                | TRISB7   | TRISB6   | TRISB5     | TRISB4       | _             | _           | —        | —           | 112                 |  |  |

| TRISC                | TRISC7   | TRISC6   | TRISC5     | TRISC4       | TRISC3        | TRISC2      | TRISC1   | TRISC0      | 116                 |  |  |

| TABLE 16-2: | SUMMARY OF REGISTERS ASSOCIATED WITH HARDWARE CVD |

|-------------|---------------------------------------------------|

|-------------|---------------------------------------------------|

Legend: — = unimplemented read as '0'. Shaded cells are not used for hardware CVD module.

**Note 1:** Unimplemented, read as '1'.

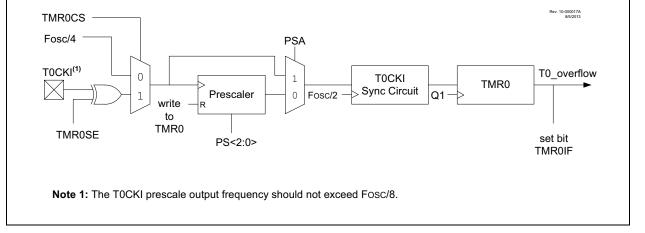

# 17.0 TIMER0 MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 3-bit prescaler (independent of Watchdog Timer)

- · Programmable internal or external clock source

- Programmable external clock edge selection

- Interrupt on overflow

- TMR0 can be used to gate Timer1

Figure 17-1 is a block diagram of the Timer0 module.

# 17.1 Timer0 Operation

The Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

# 17.1.1 8-BIT TIMER MODE

The Timer0 module will increment every instruction cycle, if used without a prescaler. 8-bit Timer mode is selected by clearing the TMR0CS bit of the OPTION REG register.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

**Note:** The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

# FIGURE 17-1: TIMER0 BLOCK DIAGRAM

### 17.1.2 8-BIT COUNTER MODE

In 8-Bit Counter mode, the Timer0 module will increment on every rising or falling edge of the T0CKI pin.

8-Bit Counter mode using the T0CKI pin is selected by setting the TMR0CS bit in the OPTION\_REG register to '1'.

The rising or falling transition of the incrementing edge for either input source is determined by the TMR0SE bit in the OPTION\_REG register.

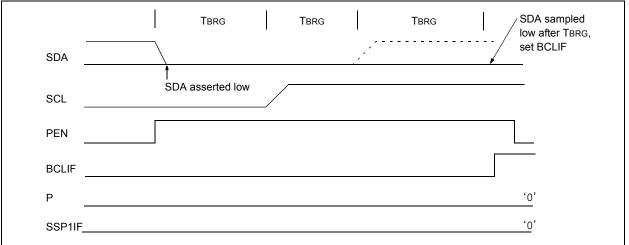

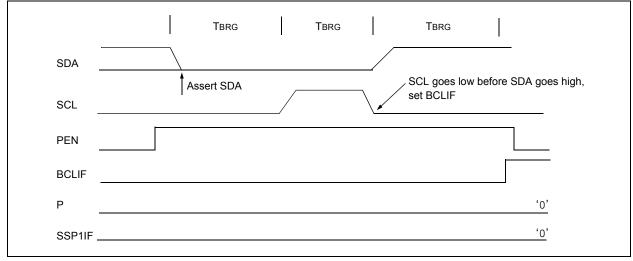

### 20.6.13.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out (Case 1).

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high (Case 2).

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPADD and counts down to 0. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 20-38). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 20-39).

# FIGURE 20-38: BUS COLLISION DURING A STOP CONDITION (CASE 1)

# FIGURE 20-39: BUS COLLISION DURING A STOP CONDITION (CASE 2)

# 21.1.2 EUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 21-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCREG register.

# 21.1.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCSTA register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART. The programmer must set the corresponding TRISx bit to configure the RX/DT I/O pin as an input.

**Note:** If the RX/DT function is on an analog pin, the corresponding ANSELx bit must be cleared for the receiver to function.

# 21.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section 21.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RCIF interrupt flag bit of the PIR1 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCREG register.

| Note: | If the receive FIFO is overrun, no additional characters will be received until the overrun condition is cleared. See <b>Section 21.1.2.5</b> |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|       | "Receive Overrun Error" for more information on overrun errors.                                                                               |

# 21.1.2.3 Receive Interrupts

The RCIF interrupt flag bit of the PIR1 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RCIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCIF interrupts are enabled by setting all of the following bits:

- RCIE, Interrupt Enable bit of the PIE1 register

- PEIE, Peripheral Interrupt Enable bit of the INTCON register

- GIE, Global Interrupt Enable bit of the INTCON register

The RCIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

# 21.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCSTA register, which resets the EUSART. Clearing the CREN bit of the RCSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

| Note: | If all receive characters in the receive  |

|-------|-------------------------------------------|

|       | FIFO have framing errors, repeated reads  |

|       | of the RCREG will not clear the FERR bit. |

# 21.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCSTA register or by resetting the EUSART by clearing the SPEN bit of the RCSTA register.

# 21.1.2.6 Receiving 9-Bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set, the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

# 21.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

|        |                | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                   |            |                             |                |            |                             |                    |            |                             |  |

|--------|----------------|------------------------------------------------------|-----------------------------|-------------------|------------|-----------------------------|----------------|------------|-----------------------------|--------------------|------------|-----------------------------|--|

| BAUD   | Foso           | : = 32.00                                            | 0 MHz                       | Fosc = 20.000 MHz |            |                             | Fosc           | : = 18.43  | 2 MHz                       | Fosc = 11.0592 MHz |            |                             |  |

| RATE   | Actual<br>Rate | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300    | 300.0          | 0.00                                                 | 26666                       | 300.0             | 0.00       | 16665                       | 300.0          | 0.00       | 15359                       | 300.0              | 0.00       | 9215                        |  |

| 1200   | 1200           | 0.00                                                 | 6666                        | 1200              | -0.01      | 4166                        | 1200           | 0.00       | 3839                        | 1200               | 0.00       | 2303                        |  |

| 2400   | 2400           | 0.01                                                 | 3332                        | 2400              | 0.02       | 2082                        | 2400           | 0.00       | 1919                        | 2400               | 0.00       | 1151                        |  |

| 9600   | 9604           | 0.04                                                 | 832                         | 9597              | -0.03      | 520                         | 9600           | 0.00       | 479                         | 9600               | 0.00       | 287                         |  |

| 10417  | 10417          | 0.00                                                 | 767                         | 10417             | 0.00       | 479                         | 10425          | 0.08       | 441                         | 10433              | 0.16       | 264                         |  |

| 19.2k  | 19.18k         | -0.08                                                | 416                         | 19.23k            | 0.16       | 259                         | 19.20k         | 0.00       | 239                         | 19.20k             | 0.00       | 143                         |  |

| 57.6k  | 57.55k         | -0.08                                                | 138                         | 57.47k            | -0.22      | 86                          | 57.60k         | 0.00       | 79                          | 57.60k             | 0.00       | 47                          |  |

| 115.2k | 115.9k         | 0.64                                                 | 68                          | 116.3k            | 0.94       | 42                          | 115.2k         | 0.00       | 39                          | 115.2k             | 0.00       | 23                          |  |

# TABLE 21-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |            |                             |                  |            |                             |                   |            |                             |                  |            |                             |

|--------|------------------------------------------------------|------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz                                     |            |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate                                       | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0                                                | 0.00       | 6666                        | 300.0            | 0.01       | 3332                        | 300.0             | 0.00       | 3071                        | 300.1            | 0.04       | 832                         |

| 1200   | 1200                                                 | -0.02      | 1666                        | 1200             | 0.04       | 832                         | 1200              | 0.00       | 767                         | 1202             | 0.16       | 207                         |

| 2400   | 2401                                                 | 0.04       | 832                         | 2398             | 0.08       | 416                         | 2400              | 0.00       | 383                         | 2404             | 0.16       | 103                         |

| 9600   | 9615                                                 | 0.16       | 207                         | 9615             | 0.16       | 103                         | 9600              | 0.00       | 95                          | 9615             | 0.16       | 25                          |

| 10417  | 10417                                                | 0          | 191                         | 10417            | 0.00       | 95                          | 10473             | 0.53       | 87                          | 10417            | 0.00       | 23                          |

| 19.2k  | 19.23k                                               | 0.16       | 103                         | 19.23k           | 0.16       | 51                          | 19.20k            | 0.00       | 47                          | 19.23k           | 0.16       | 12                          |

| 57.6k  | 57.14k                                               | -0.79      | 34                          | 58.82k           | 2.12       | 16                          | 57.60k            | 0.00       | 15                          | _                | _          | _                           |

| 115.2k | 117.6k                                               | 2.12       | 16                          | 111.1k           | -3.55      | 8                           | 115.2k            | 0.00       | 7                           |                  | _          | —                           |

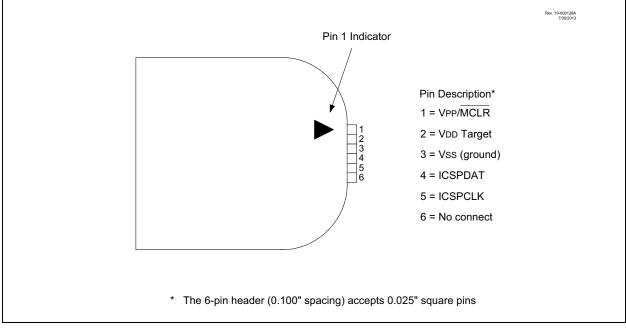

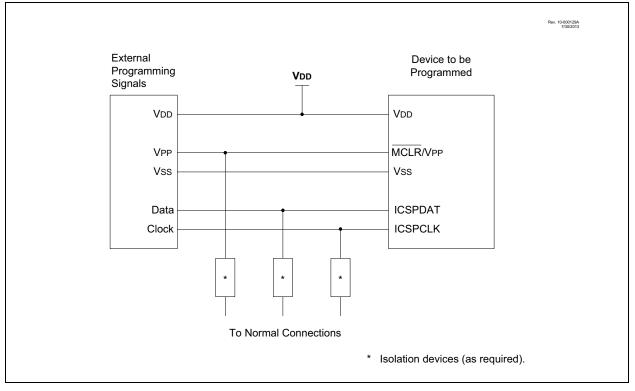

# FIGURE 23-2: PICkit<sup>™</sup> PROGRAMMER STYLE CONNECTOR INTERFACE

For additional interface recommendations, refer to your specific device programmer manual prior to PCB design.

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices such as resistors, diodes, or even jumpers. See Figure 23-3 for more information.

# FIGURE 23-3: TYPICAL CONNECTION FOR ICSP™ PROGRAMMING

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                          |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                           |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Description:     | The contents of register 'f' are decre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', then a<br>NOP is executed instead, making it a<br>2-cycle instruction. |  |  |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                                    |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                 |  |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                    |  |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<6:3> $\rightarrow$ PC<14:11>                                                                                                                         |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                    |  |  |  |  |