Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFL

| Product Status             | Last Time Buy                                                                    |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | SH-2A                                                                            |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 100MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, FIFO, I <sup>2</sup> C, SCI, Serial Sound                       |

| Peripherals                | DMA, POR, PWM, WDT                                                               |

| Number of I/O              | 104                                                                              |

| Program Memory Size        | -                                                                                |

| Program Memory Type        | ROMIess                                                                          |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                              |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 176-LQFP                                                                         |

| Supplier Device Package    | 176-LFQFP (24x24)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/ds72011rw100fpv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|         | 5.2.2     | Types of Reset                                                        | 97  |

|---------|-----------|-----------------------------------------------------------------------|-----|

|         | 5.2.3     | Power-On Reset                                                        | 98  |

|         | 5.2.4     | Manual Reset                                                          | 100 |

| 5.3     | Address   | Errors                                                                | 101 |

|         | 5.3.1     | Address Error Sources                                                 | 101 |

|         | 5.3.2     | Address Error Exception Handling                                      | 102 |

| 5.4     | Bus Erro  | r                                                                     | 103 |

|         | 5.4.1     | Bus Error Generation Source                                           | 103 |

|         | 5.4.2     | Bus Error Exception Handling                                          | 103 |

| 5.5     | Register  | Bank Errors                                                           | 104 |

|         | 5.5.1     | Register Bank Error Sources                                           | 104 |

|         | 5.5.2     | Register Bank Error Exception Handling                                | 104 |

| 5.6     | Interrupt | S                                                                     | 105 |

|         | 5.6.1     | Interrupt Sources                                                     | 105 |

|         | 5.6.2     | Interrupt Priority Level                                              | 106 |

|         | 5.6.3     | Interrupt Exception Handling                                          | 107 |

| 5.7     | Exceptio  | ns Triggered by Instructions                                          | 108 |

|         | 5.7.1     | Types of Exceptions Triggered by Instructions                         | 108 |

|         | 5.7.2     | Trap Instructions                                                     | 109 |

|         | 5.7.3     | Slot Illegal Instructions                                             | 109 |

|         | 5.7.4     | General Illegal Instructions                                          | 109 |

|         | 5.7.5     | Integer Division Exceptions                                           | 110 |

|         | 5.7.6     | FPU Exceptions                                                        | 110 |

| 5.8     | When Ex   | ception Sources Are Not Accepted                                      | 111 |

| 5.9     |           | atus after Exception Handling Ends                                    |     |

| 5.10    | Usage N   | otes                                                                  | 114 |

|         | 5.10.1    | Value of Stack Pointer (SP)                                           | 114 |

|         | 5.10.2    | Value of Vector Base Register (VBR)                                   |     |

|         | 5.10.3    | Address Errors Caused by Stacking of Address Error Exception Handling | 114 |

| Section | on 6 In   | terrupt Controller (INTC)                                             | 115 |

| 6.1     |           |                                                                       |     |

| 6.2     |           | itput Pins                                                            |     |

| 6.3     | -         | Descriptions                                                          |     |

| 0.5     | 6.3.1     | Interrupt Priority Registers 01, 02, 05 to 16                         | 117 |

|         | 0.5.1     | (IPR01, IPR02, IPR05 to IPR16)                                        | 110 |

|         | 6.3.2     | Interrupt Control Register 0 (ICR0)                                   |     |

|         | 6.3.3     | Interrupt Control Register 0 (ICR0)                                   |     |

|         | 6.3.4     | Interrupt Control Register 2 (ICR2)                                   |     |

|         | 6.3.5     | IRQ Interrupt Request Register (IRQRR)                                |     |

|         | 0.5.5     | ווע וווכוועףו הפעופגו הפצוגופו (והעהה)                                | 123 |

| Bit      | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                              |

|----------|----------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 to 15 |          | All 0            | R   | Reserved                                                                                                                                                 |

|          |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                     |

| 14       | BO       | 0                | R/W | BO Bit                                                                                                                                                   |

|          |          |                  |     | Indicates that a register bank has overflowed.                                                                                                           |

| 13       | CS       | 0                | R/W | CS Bit                                                                                                                                                   |

|          |          |                  |     | Indicates that, in CLIP instruction execution, the value has exceeded the saturation upper-limit value or fallen below the saturation lower-limit value. |

| 12 to 10 | _        | All 0            | R   | Reserved                                                                                                                                                 |

|          |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                     |

| 9        | Μ        | _                | R/W | M Bit                                                                                                                                                    |

| 8        | Q        | _                | R/W | Q Bit                                                                                                                                                    |

|          |          |                  |     | Used by the DIV0S, DIV0U, and DIV1 instructions.                                                                                                         |

| 7 to 4   | I[3:0]   | 1111             | R/W | Interrupt Mask Level                                                                                                                                     |

| 3, 2     |          | All 0            | R   | Reserved                                                                                                                                                 |

|          |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                     |

| 1        | S        | _                | R/W | S Bit                                                                                                                                                    |

|          |          |                  |     | Specifies a saturation operation for a MAC instruction.                                                                                                  |

| 0        | Т        | _                | R/W | T Bit                                                                                                                                                    |

|          |          |                  |     | True/false condition or carry/borrow bit                                                                                                                 |

These possibilities of each exceptional handling on floating-point operation are shown in the individual instruction descriptions. All exception events that originate in the floating-point operation are assigned as the same FPU exceptional handling event. The meaning of an exception generated by floating-point operation is determined by software by reading from FPSCR and interpreting the information it contains. Also, the destination register is not changed when FPU exception handling operation occurs.

Except for the above, the FPU disables exception handling. In every processing, the bit corresponding to source V, Z, O, U, or I is set to 1, and a default value is generated as the operation result.

- Invalid operation (V): qNaN is generated as the result.

- Division by zero (Z): Infinity with the same sign as the unrounded value is generated.

- Overflow (O):

When rounding mode = RZ, the maximum normalized number, with the same sign as the unrounded value, is generated.

When rounding mode = RN, infinity with the same sign as the unrounded value is generated.

- Underflow (U): Zero with the same sign as the unrounded value is generated.

- Inexact exception (I): An inexact result is generated.

| P         H1226         ON (x3)         ON (x2)         2:2:1/2         10 to 20         20 to 40         20 to 40         5 to 10           H1303         ON (x4)         ON (x2)         6:2:2         10 to 15         20 to 30         80 to 120         20 to 30         20 to 30           H1305         ON (x4)         ON (x2)         6:2:1         10 to 15         20 to 30         80 to 120         20 to 30         667 to 10           H1305         ON (x4)         ON (x2)         6:2:2/3         10 to 15         20 to 30         80 to 120         20 to 30         667 to 10           H1315         ON (x4)         ON (x2)         4:2:2         10 to 25         20 to 50         40 to 80         20 to 40         20 to 40           H1315         ON (x4)         ON (x2)         4:2:2         10 to 25         20 to 50         40 to 100         20 to 50         667 to 16.6           H1335         ON (x4)         ON (x2)         2:2:2         10 to 25         20 to 50         20 to 50         20 to 50         10 to 25           H1336         ON (x4)         ON (x2)         2:2:2         10         to 20         20         20         10         10 to 25           H1336         ON (x4)         ON (x2) <th>011-</th> <th></th> <th colspan="2">PLL Frequenc<br/>Multiplier</th> <th>Ratio of</th> <th colspan="6">Selectable Frequency Range (MHz)</th>                                                                                                                                          | 011-      |        | PLL Frequenc<br>Multiplier |         | Ratio of    | Selectable Frequency Range (MHz) |             |             |             |                                                   |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------|----------------------------|---------|-------------|----------------------------------|-------------|-------------|-------------|---------------------------------------------------|--|

| H1303         ON (~4)         ON (~2)         8:2:2         10 to 15         20 to 30         80 to 120         20 to 30         10 to 15           H1305         ON (~4)         ON (~2)         8:2:1         10 to 15         20 to 30         80 to 120         20 to 30         10 to 15           H1306         ON (~4)         ON (~2)         8:2:2'3         10 to 15         20 to 30         80 to 120         20 to 30         6.67 to 10           H1313         ON (~4)         ON (~2)         4:2:2         10 to 25         20 to 50         40 to 80         20 to 30         6.67 to 10           H1315         ON (~4)         ON (~2)         4:2:2         10 to 25         20 to 50         40 to 100         20 to 50         10 to 25           H1313         ON (~4)         ON (~2)         4:2:2'3         10 to 25         20 to 50         40 to 100         20 to 50         6.67 to 16.6           H1333         ON (~4)         ON (~2)         2:2:2         10 to 25         20 to 50         20 to 50         20 to 50         10 to 25           H136         ON (~4)         ON (~2)         12:2:2         10         20         10 to 50         20 to 50         20 to 50         20 to 50         30 to 33.33         20 to 33.33                                                                                                                                                                                                                                                                        | Operating |        |                            |         | Frequencies |                                  |             |             |             | Peripheral<br>Clock (Pø) <sup>*<sup>3</sup></sup> |  |

| H1305         ON (x4)         ON (x2)         8:2:1         10 to 15         20 to 30         80 to 120         20 to 30         10 to 15           H1306         ON (x4)         ON (x2)         8:2:2/3         10 to 15         20 to 30         80 to 120         20 to 30         66 77 to 10           H1313         ON (x4)         ON (x2)         4:2:2         10 to 20         20 to 40         40 to 80         20 to 40         20 to 40           H1315         ON (x4)         ON (x2)         4:2:2         10 to 25         20 to 50         40 to 100         20 to 50         66 77 to 16           H1335         ON (x4)         ON (x2)         4:2:23         10 to 25         20 to 50         40 to 100         20 to 50         66 77 to 16           H1335         ON (x4)         ON (x2)         2:2:2         10 to 25         20 to 50         10 to 25           H1336         ON (x4)         ON (x2)         2:2:2         10         20         10 to 25         20 to 50         20 to 33.3         20 to 33.3         20 to 33.3         20 to 33.3         20                                                                                                                                                                                                                                                      | 2         | H'1226 | ON (×3)                    | ON (×2) | 2:2:1/2     | 10 to 20                         | 20 to 40    | 20 to 40    | 20 to 40    | 5 to 10                                           |  |

| H1306         ON (x2)         8:2:2/3         10 to 15         20 to 30         80 to 120         20 to 30         6.67 to 10           H1313         ON (x4)         ON (x2)         4:2:2         10 to 20         20 to 40         40 to 80         20 to 40         20 to 40           H1315         ON (x4)         ON (x2)         4:2:1         10 to 25         20 to 50         40 to 100         20 to 50         6.67 to 16.6           H1335         ON (x4)         ON (x2)         4:2:23         10 to 25         20 to 50         40 to 100         20 to 50         6.67 to 16.6           H1335         ON (x4)         ON (x2)         2:2:2         10 to 25         20 to 50         10 to 25           H1336         ON (x4)         ON (x2)         2:2:1         10 to 25         20 to 50         6.67 to 16.6           H1404         ON (x6)         ON (x2)         2:2:1         10 to 25         20 to 50         20 to 50         20 to 53.33         20 to 33.33                                                                                                                                                                                                                                              |           | H'1303 | ON (×4)                    | ON (×2) | 8:2:2       | 10 to 15                         | 20 to 30    | 80 to 120   | 20 to 30    | 20 to 30                                          |  |

| H1313         ON (x4)         ON (x2)         4:2:2         10 to 20         20 to 40         40 to 80         20 to 40         20 to 40           H1315         ON (x4)         ON (x2)         4:2:1         10 to 25         20 to 50         40 to 100         20 to 50         10 to 25           H1316         ON (x4)         ON (x2)         4:2:1         10 to 25         20 to 50         40 to 100         20 to 50         6.67 to 16.6           H1333         ON (x4)         ON (x2)         2:2:2         10 to 25         20 to 50         20 to 50         20 to 40         20 to 40         20 to 40         20 to 40           H1335         ON (x4)         ON (x2)         2:2:1         10 to 25         20 to 50         20 to 50         20 to 50         20 to 50         10 to 25           H1305         ON (x4)         ON (x2)         2:2:2         10         20         120         20         20           H1406         ON (x6)         ON (x2)         12:2:1         10         20         120         20         10           H1414         ON (x6)         ON (x2)         6:2:1         10 to 16.67         20 to 33.33         60 to 100         20 to 33.33         20 to 33.33         10 to 16.67                                                                                                                                                                                                                                                                                                     |           | H'1305 | ON (×4)                    | ON (×2) | 8:2:1       | 10 to 15                         | 20 to 30    | 80 to 120   | 20 to 30    | 10 to 15                                          |  |

| H'1315         ON (-4)         ON (-2)         42:1         10 to 25         20 to 50         40 to 100         20 to 50         10 to 25           H'1316         ON (-4)         ON (-2)         42:23         10 to 25         20 to 50         40 to 100         20 to 50         6.67 to 16.6           H'1333         ON (-4)         ON (-2)         2:2:2         10 to 25         20 to 40           H'1335         ON (-4)         ON (-2)         2:2:1         10 to 25         20 to 50         20 to 50         20 to 50         10 to 25           H'1336         ON (-4)         ON (-2)         2:2:1         10 to 25         20 to 50         20 to 50         6.67 to 16.6           H'1404         ON (-6)         ON (-2)         12:2:1         10         20         120         20         20           H'1414         ON (-6)         ON (-2)         6:2:1         10 to 16.67         20 to 33.33         60 to 100         20 to 33.33         20 to 33.33         10 to 16.67           H'1424         ON (-6)         ON (-2)         4:2:1         10 to 16.67         20 to 33.33         20 to 33.33         20 to 33.33         10 to 16.67           H'1424                                                                                                                                                                                                                                                                                |           | H'1306 | ON (×4)                    | ON (×2) | 8:2:2/3     | 10 to 15                         | 20 to 30    | 80 to 120   | 20 to 30    | 6.67 to 10                                        |  |

| H'1316         ON (x4)         ON (x2)         4:2:2/3         10 to 25         20 to 50         40 to 100         20 to 50         6.67 to 16.6           H'1333         ON (x4)         ON (x2)         2:2:2         10 to 20         20 to 40         20 to 50         10 to 25         20 to 50         20 to 50         10 to 25         20 to 50         20 to 50         20 to 50         20 to 50         6.67 to 16.6           H'1404         ON (x6)         ON (x2)         12:2:2         10         20         120         20         20         10           H'1414         ON (x6)         ON (x2)         6:2:1         10 to 16.67         20 to 33.33         60 to 100         20 to 33.33         10 to 16.67         20 to 33.33         20 to 33.33         10 to 16.67         20 to 33.33         20 to 33.33         20 to 33.33                                                                                                                                                                                                            |           | H'1313 | ON (×4)                    | ON (×2) | 4:2:2       | 10 to 20                         | 20 to 40    | 40 to 80    | 20 to 40    | 20 to 40                                          |  |

| H1333         ON (x4)         ON (x2)         2:2:2         10 to 20         20 to 40           H1335         ON (x4)         ON (x2)         2:2:1         10 to 25         20 to 50         6.67 to 16.6           H1336         ON (x4)         ON (x2)         2:2:2         10         20         120         20         20           H1404         ON (x6)         ON (x2)         12:2:2         10         20         120         20         20           H1406         ON (x6)         ON (x2)         12:2:1         10         20         120         20         10           H1414         ON (x6)         ON (x2)         6:2:2         10 to 16.67         20 to 33.33         60 to 100         20 to 33.33         10 to 16.67           H1424         ON (x6)         ON (x2)         4:2:2         10 to 16.67         20 to 33.33         20 to 33.33         10 to 16.67           H1426         ON (x6)         ON (x2)         4:2:1         10 to 16.67         20 to 33.33                                                                                                                                                                                                                                                                                    |           | H'1315 | ON (×4)                    | ON (×2) | 4:2:1       | 10 to 25                         | 20 to 50    | 40 to 100   | 20 to 50    | 10 to 25                                          |  |

| H1335         ON (×4)         ON (×2)         2:2:1         10 to 25         20 to 50         20 to 50         20 to 50         10 to 25           H1336         ON (×4)         ON (×2)         2:2:2/3         10 to 25         20 to 50         20 to 50         20 to 50         20 to 50         6.67 to 16.6           H1404         ON (×6)         ON (×2)         12:2:2         10         20         120         20         20           H1406         ON (×6)         ON (×2)         12:2:1         10         20         120         20         10           H1406         ON (×6)         ON (×2)         6:2:2         10 to 16.67         20 to 33.33         60 to 100         20 to 33.33         10 to 16.67           H1414         ON (×6)         ON (×2)         6:2:1         10 to 16.67         20 to 33.33         40 to 66.67         20 to 33.33         10 to 16.67           H1424         ON (×6)         ON (×2)         4:2:1         10 to 16.67         20 to 33.33         20 to 33.33         20 to 33.33         10 to 16.67           H1426         ON (×6)         ON (×2)         4:2:1         10 to 16.67         20 to 33.33         10 to 16.67                                                                                                                                                                                                                                                                     |           | H'1316 | ON (×4)                    | ON (×2) | 4:2:2/3     | 10 to 25                         | 20 to 50    | 40 to 100   | 20 to 50    | 6.67 to 16.67                                     |  |

| H1336         ON (×4)         ON (×2)         2:2:2/3         10 to 25         20 to 50         20 to 50         20 to 50         6.67 to 16.6           H1404         ON (×6)         ON (×2)         12:2:2         10         20         120         20         20           H1404         ON (×6)         ON (×2)         12:2:1         10         20         120         20         10           H1406         ON (×6)         ON (×2)         6:2:1         10 to 16.67         20 to 33.33         60 to 100         20 to 33.33         10 to 16.67           H1416         ON (×6)         ON (×2)         6:2:1         10 to 16.67         20 to 33.33         40 to 66.67         20 to 33.33         10 to 16.67           H1424         ON (×6)         ON (×2)         4:2:2         10 to 16.67         20 to 33.33         40 to 66.67         20 to 33.33         10 to 16.67           H1424         ON (×6)         ON (×2)         2:2:2         10 to 16.67         20 to 33.33         20 to 33.33         10 to 16.67           H1444         ON (×6)         ON (×2)         2:2:2         10 to 12.5         20 to 33.33         20 to 33.33         20 to 33.33         10 to 16.67           H1444         ON (×6)         ON (×2)         <                                                                                                                                                                                                                                                                          |           | H'1333 | ON (×4)                    | ON (×2) | 2:2:2       | 10 to 20                         | 20 to 40    | 20 to 40    | 20 to 40    | 20 to 40                                          |  |

| H1404         ON (x6)         ON (x2)         12:2:2         10         20         120         20         20           H1406         ON (x6)         ON (x2)         12:2:1         10         20         120         20         10           H1406         ON (x6)         ON (x2)         6:2:2         10 to 16.67         20 to 33.33         60 to 100         20 to 33.33         20 to 33.33           H1416         ON (x6)         ON (x2)         6:2:1         10 to 16.67         20 to 33.33         60 to 100         20 to 33.33         10 to 16.67           H1424         ON (x6)         ON (x2)         4:2:2         10 to 16.67         20 to 33.33         40 to 66.67         20 to 33.33         10 to 16.67           H1426         ON (x6)         ON (x2)         4:2:1         10 to 16.67         20 to 33.33         20 to 33.33         20 to 33.33         10 to 16.67           H1446         ON (x6)         ON (x2)         2:2:2         10 to 16.67         20 to 33.33         20 to 33.33         20 to 33.33         10 to 16.67           H1446         ON (x6)         ON (x2)         2:2:2         10 to 12.5         20 to 25         80 to 33.33         20 to 33.33         10 to 16.67           H1555         ON (x8)                                                                                                                                                                                                                                                                            |           | H'1335 | ON (×4)                    | ON (×2) | 2:2:1       | 10 to 25                         | 20 to 50    | 20 to 50    | 20 to 50    | 10 to 25                                          |  |

| H'1406         ON (×6)         ON (×2)         12:2:1         10         20         120         20         10           H'1406         ON (×6)         ON (×2)         6:2:2         10 to 16.67         20 to 33.33         60 to 100         20 to 33.33         20 to 33.33         10 to 16.67           H'1416         ON (×6)         ON (×2)         6:2:1         10 to 16.67         20 to 33.33         60 to 100         20 to 33.33         10 to 16.67           H'1424         ON (×6)         ON (×2)         4:2:2         10 to 16.67         20 to 33.33         40 to 66.67         20 to 33.33         10 to 16.67           H'1426         ON (×6)         ON (×2)         4:2:2         10 to 16.67         20 to 33.33         40 to 66.67         20 to 33.33         10 to 16.67           H'1446         ON (×6)         ON (×2)         2:2:1         10 to 16.67         20 to 33.33         10 to 16.67           H'1446         ON (×6)         ON (×2)         2:2:2         10 to 12.5         20 to 33.33         20 to 25                                                                                                                                                                                                                                   |           | H'1336 | ON (×4)                    | ON (×2) | 2:2:2/3     | 10 to 25                         | 20 to 50    | 20 to 50    | 20 to 50    | 6.67 to 16.67                                     |  |

| H'1414         ON (×6)         ON (×2)         6:2:2         10 to 16.67         20 to 33.33         60 to 100         20 to 33.33         20 to 33.33           H'1416         ON (×6)         ON (×2)         6:2:1         10 to 16.67         20 to 33.33         60 to 100         20 to 33.33         10 to 16.67           H'1424         ON (×6)         ON (×2)         4:2:2         10 to 16.67         20 to 33.33         40 to 66.67         20 to 33.33         10 to 16.67           H'1426         ON (×6)         ON (×2)         4:2:1         10 to 16.67         20 to 33.33         40 to 66.67         20 to 33.33         10 to 16.67           H'1446         ON (×6)         ON (×2)         2:2:2         10 to 16.67         20 to 33.33         20 to 33.33         20 to 33.33         20 to 33.33         10 to 16.67           H'1446         ON (×6)         ON (×2)         2:2:1         10 to 16.67         20 to 33.33         10 to 16.67           H'1446         ON (×6)         ON (×2)         2:2:1         10 to 12.5         20 to 25         80 to 100         20 to 25                                                                                                                                                                                                                       |           | H'1404 | ON (×6)                    | ON (×2) | 12:2:2      | 10                               | 20          | 120         | 20          | 20                                                |  |

| H'1416         ON (×6)         ON (×2)         6:2:1         10 to 16.67         20 to 33.33         60 to 100         20 to 33.33         10 to 16.67           H'1424         ON (×6)         ON (×2)         4:2:2         10 to 16.67         20 to 33.33         40 to 66.67         20 to 33.33         20 to 33.33           H'1426         ON (×6)         ON (×2)         4:2:1         10 to 16.67         20 to 33.33         40 to 66.67         20 to 33.33         10 to 16.67           H'1426         ON (×6)         ON (×2)         2:2:2         10 to 16.67         20 to 33.33         20 to 33.33         20 to 33.33         10 to 16.67           H'1446         ON (×6)         ON (×2)         2:2:2         10 to 16.67         20 to 33.33         20 to 25         20 to                                                                                                                                                                                |           | H'1406 | ON (×6)                    | ON (×2) | 12:2:1      | 10                               | 20          | 120         | 20          | 10                                                |  |

| H'1424         ON (×6)         ON (×2)         4:2:2         10 to 16.67         20 to 33.33         40 to 66.67         20 to 33.33         20 to 33.33           H'1426         ON (×6)         ON (×2)         4:2:1         10 to 16.67         20 to 33.33         40 to 66.67         20 to 33.33         10 to 16.67           H'1426         ON (×6)         ON (×2)         2:2:2         10 to 16.67         20 to 33.33         10 to 16.67           H'1555         ON (×8)         ON (×2)         8:2:2         10 to 12.5         20 to 25         20 to 25         20 to 25                                                                                                                                                                |           | H'1414 | ON (×6)                    | ON (×2) | 6:2:2       | 10 to 16.67                      | 20 to 33.33 | 60 to 100   | 20 to 33.33 | 20 to 33.33                                       |  |

| H'1426         ON (×6)         ON (×2)         4:2:1         10 to 16.67         20 to 33.33         40 to 66.67         20 to 33.33         10 to 16.67           H'1444         ON (×6)         ON (×2)         2:2:2         10 to 16.67         20 to 33.33         20 to 25         2                                                                                                                            |           | H'1416 | ON (×6)                    | ON (×2) | 6:2:1       | 10 to 16.67                      | 20 to 33.33 | 60 to 100   | 20 to 33.33 | 10 to 16.67                                       |  |

| H'1444         ON (×6)         ON (×2)         2:2:2         10 to 16.67         20 to 33.33         10 to 16.67           H'1446         ON (×6)         ON (×2)         2:2:1         10 to 12.5         20 to 25         80 to 100         20 to 25         20 to 25           H'1515         ON (×8)         ON (×2)         4:2:2         10 to 12.5         20 to 25         40 to 50         20 to 25         20 to 25           H'1555         ON (×8)         ON (×2)         4:2:2         10 to 12.5         20 to 25                                                                                                                                                                                                  |           | H'1424 | ON (×6)                    | ON (×2) | 4:2:2       | 10 to 16.67                      | 20 to 33.33 | 40 to 66.67 | 20 to 33.33 | 20 to 33.33                                       |  |

| H'1446         ON (×6)         ON (×2)         2:2:1         10 to 16.67         20 to 33.33         20 to 33.33         20 to 33.33         10 to 16.67           H'1515         ON (×8)         ON (×2)         8:2:2         10 to 12.5         20 to 25         80 to 100         20 to 25         20 to 25           H'1535         ON (×8)         ON (×2)         4:2:2         10 to 12.5         20 to 25         40 to 50         20 to 25         20 to 25           H'1555         ON (×8)         ON (×2)         2:2:2         10 to 12.5         20 to 25                                                                                                                                                                                                                |           | H'1426 | ON (×6)                    | ON (×2) | 4:2:1       | 10 to 16.67                      | 20 to 33.33 | 40 to 66.67 | 20 to 33.33 | 10 to 16.67                                       |  |

| H'1515         ON (×8)         ON (×2)         8:2:2         10 to 12.5         20 to 25         80 to 100         20 to 25         20 to 25           H'1535         ON (×8)         ON (×2)         4:2:2         10 to 12.5         20 to 25         40 to 50         20 to 25         20 to 25 <td></td> <td>H'1444</td> <td>ON (×6)</td> <td>ON (×2)</td> <td>2:2:2</td> <td>10 to 16.67</td> <td>20 to 33.33</td> <td>20 to 33.33</td> <td>20 to 33.33</td> <td>20 to 33.33</td> |           | H'1444 | ON (×6)                    | ON (×2) | 2:2:2       | 10 to 16.67                      | 20 to 33.33 | 20 to 33.33 | 20 to 33.33 | 20 to 33.33                                       |  |

| H'1535         ON (×8)         ON (×2)         4:2:2         10 to 12.5         20 to 25         40 to 50         20 to 25         20 to 25           H'1535         ON (×8)         ON (×2)         2:2:2         10 to 12.5         20 to 25         20 to 40         20 to 60         10 to 30         20 to 60         20 to 60 <td></td> <td>H'1446</td> <td>ON (×6)</td> <td>ON (×2)</td> <td>2:2:1</td> <td>10 to 16.67</td> <td>20 to 33.33</td> <td>20 to 33.33</td> <td>20 to 33.33</td> <td>10 to 16.67</td>  |           | H'1446 | ON (×6)                    | ON (×2) | 2:2:1       | 10 to 16.67                      | 20 to 33.33 | 20 to 33.33 | 20 to 33.33 | 10 to 16.67                                       |  |

| H'1555         ON (×8)         ON (×2)         2:2:2         10 to 12.5         20 to 25         20 to 25         20 to 25         20 to 25           3         H'1000         ON (×1)         OFF         1:1:1         20 to 40         —         20 to 40         20 to 40         20 to 40           H'1001         ON (×1)         OFF         1:1:1/2         20 to 60         —         20 to 60         20 to 60         10 to 30           H'1002         ON (×1)         OFF         1:1:1/2         20 to 60         —         20 to 60         20 to 60         6.67 to 20           H'1003         ON (×1)         OFF         1:1:1/4         20 to 60         —         20 to 60         20 to 60         5 to 15           H'1004         ON (×1)         OFF         1:1:1/8         20 to 60         —         20 to 60         20 to 60         3.33 to 10           H'1005         ON (×1)         OFF         1:1:1/8         20 to 60         —         20 to 60         20 to 60         2.5 to 7.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           | H'1515 | ON (×8)                    | ON (×2) | 8:2:2       | 10 to 12.5                       | 20 to 25    | 80 to 100   | 20 to 25    | 20 to 25                                          |  |

| 3         H'1000         ON (×1)         OFF         1:1:1         20 to 40         —         20 to 40         20 to 40         20 to 40           H'1001         ON (×1)         OFF         1:1:1/2         20 to 60         —         20 to 60         20 to 60         10 to 30           H'1002         ON (×1)         OFF         1:1:1/2         20 to 60         —         20 to 60         20 to 60         10 to 30           H'1002         ON (×1)         OFF         1:1:1/3         20 to 60         —         20 to 60         20 to 60         6.67 to 20           H'1003         ON (×1)         OFF         1:1:1/4         20 to 60         —         20 to 60         20 to 60         5 to 15           H'1004         ON (×1)         OFF         1:1:1/8         20 to 60         —         20 to 60         20 to 60         3.33 to 10           H'1005         ON (×1)         OFF         1:1:1/8         20 to 60         —         20 to 60         20 to 60         2.5 to 7.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           | H'1535 | ON (×8)                    | ON (×2) | 4:2:2       | 10 to 12.5                       | 20 to 25    | 40 to 50    | 20 to 25    | 20 to 25                                          |  |

| H'1001       ON (x1)       OFF       1:1:1/2       20 to 60       —       20 to 60       20 to 60       10 to 30         H'1002       ON (x1)       OFF       1:1:1/3       20 to 60       —       20 to 60       20 to 60       6.67 to 20         H'1003       ON (x1)       OFF       1:1:1/4       20 to 60       —       20 to 60       20 to 60       5 to 15         H'1004       ON (x1)       OFF       1:1:1/6       20 to 60       —       20 to 60       20 to 60       3.33 to 10         H'1005       ON (x1)       OFF       1:1:1/8       20 to 60       —       20 to 60       20 to 60       2.5 to 7.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           | H'1555 | ON (×8)                    | ON (×2) | 2:2:2       | 10 to 12.5                       | 20 to 25    | 20 to 25    | 20 to 25    | 20 to 25                                          |  |

| H'1002       ON (×1)       OFF       1:1:1/3       20 to 60        20 to 60       20 to 60       6.67 to 20         H'1003       ON (×1)       OFF       1:1:1/4       20 to 60        20 to 60       20 to 60       5 to 15         H'1004       ON (×1)       OFF       1:1:1/6       20 to 60        20 to 60       20 to 60       3.33 to 10         H'1005       ON (×1)       OFF       1:1:1/8       20 to 60        20 to 60       20 to 60       2.5 to 7.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3         | H'1000 | ON (×1)                    | OFF     | 1:1:1       | 20 to 40                         | _           | 20 to 40    | 20 to 40    | 20 to 40                                          |  |

| H'1003       ON (×1)       OFF       1:1:1/4       20 to 60       —       20 to 60       20 to 60       5 to 15         H'1004       ON (×1)       OFF       1:1:1/6       20 to 60       —       20 to 60       20 to 60       3.33 to 10         H'1005       ON (×1)       OFF       1:1:1/8       20 to 60       —       20 to 60       20 to 60       2.5 to 7.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           | H'1001 | ON (×1)                    | OFF     | 1:1:1/2     | 20 to 60                         | _           | 20 to 60    | 20 to 60    | 10 to 30                                          |  |

| H'1004       ON (×1)       OFF       1:1:1/6       20 to 60       —       20 to 60       20 to 60       3.33 to 10         H'1005       ON (×1)       OFF       1:1:1/8       20 to 60       —       20 to 60       20 to 60       2.5 to 7.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           | H'1002 | ON (×1)                    | OFF     | 1:1:1/3     | 20 to 60                         | _           | 20 to 60    | 20 to 60    | 6.67 to 20                                        |  |

| H'1005 ON (x1) OFF 1:1:1/8 20 to 60 — 20 to 60 20 to 60 2.5 to 7.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           | H'1003 | ON (×1)                    | OFF     | 1:1:1/4     | 20 to 60                         | _           | 20 to 60    | 20 to 60    | 5 to 15                                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           | H'1004 | ON (×1)                    | OFF     | 1:1:1/6     | 20 to 60                         | _           | 20 to 60    | 20 to 60    | 3.33 to 10                                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           | H'1005 | ON (×1)                    | OFF     | 1:1:1/8     | 20 to 60                         | _           | 20 to 60    | 20 to 60    | 2.5 to 7.5                                        |  |

| H'1006 ON (×1) OFF 1:1:1/12 20 to 60 — 20 to 60 20 to 60 1.67 to 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           | H'1006 | ON (×1)                    | OFF     | 1:1:1/12    | 20 to 60                         | _           | 20 to 60    | 20 to 60    | 1.67 to 5                                         |  |

### 5.2.4 Manual Reset

### (1) Manual Reset by Means of $\overline{\text{MRES}}$ Pin

When the  $\overline{\text{MRES}}$  pin is driven low, this LSI enters the manual reset state. To reset this LSI without fail, the  $\overline{\text{MRES}}$  pin should be kept at the low level for at least 20-tcyc. In the manual reset state, the CPU's internal state is initialized, but all the on-chip peripheral module registers are not initialized. In the manual reset state, manual reset exception handling starts when the  $\overline{\text{MRES}}$  pin is first driven low for a fixed period and then returned to high. The CPU operates as follows:

- 1. The initial value (execution start address) of the program counter (PC) is fetched from the exception handling vector table.

- 2. The initial value of the stack pointer (SP) is fetched from the exception handling vector table.

- 3. The vector base register (VBR) is cleared to H'00000000, the interrupt mask level bits (I3 to I0) of the status register (SR) are initialized to H'F (B'1111), and the BO and CS bits are initialized. The BN bit in IBNR of the INTC is also initialized to 0.

- 4. The values fetched from the exception handling vector table are set in the PC and SP, and the program begins executing.

#### (2) Manual Reset Initiated by WDT

When a setting is made for a manual reset to be generated in the WDT's watchdog timer mode, and WTCNT of the WDT overflows, this LSI enters the manual reset state.

When manual reset exception processing is started by the WDT, the CPU operates in the same way as when a manual reset was caused by the  $\overline{\text{MRES}}$  pin.

#### (3) Notes at a Manual Reset

When a manual reset is generated, the bus cycle is retained. Thus, manual reset exception handling will be deferred until the CPU acquires the bus mastership. The CPU and the BN bit in IBNR of the INTC are initialized by a manual reset. The FPU and other modules are not initialized.

### 5.10 Usage Notes

### 5.10.1 Value of Stack Pointer (SP)

The value of the stack pointer must always be a multiple of four. If it is not, an address error will occur when the stack is accessed during exception handling.

### 5.10.2 Value of Vector Base Register (VBR)

The value of the vector base register must always be a multiple of four. If it is not, an address error will occur when the stack is accessed during exception handling.

### 5.10.3 Address Errors Caused by Stacking of Address Error Exception Handling

When the stack pointer is not a multiple of four, an address error will occur during stacking of the exception handling (interrupts, etc.) and address error exception handling will start up as soon as the first exception handling is ended. Address errors will then also occur in the stacking for this address error exception handling. To ensure that address error exception handling does not go into an endless loop, no address errors are accepted at that point. This allows program control to be shifted to the address error exception service routine and enables error processing.

When an address error occurs during exception handling stacking, the stacking bus cycle (write) is executed. During the stacking of the status register (SR) and program counter (PC), the SP is decremented by 4 for both, so the value of SP will not be a multiple of four after the stacking either. The address value output during stacking is the SP value, so the address where the error occurred is itself output. This means the write data stacked will be undefined.

| Interrupt Vector |      |                                       |     |                                             | IPR                        |                  |                     |           |

|------------------|------|---------------------------------------|-----|---------------------------------------------|----------------------------|------------------|---------------------|-----------|

| Interrupt Source |      | Vector Table<br>Vector Address Offset |     | Interrupt<br>Priority<br>(Initial<br>Value) | Corresponding<br>IPR (Bit) |                  | Default<br>Priority |           |

| MTU2             | MTU3 | TGI3A                                 | 132 | H'00000210 to<br>H'00000213                 | 0 to 15 (0)                | IPR07 (3 to 0)   | 1                   | High<br>♠ |

|                  |      | TGI3B                                 | 133 | H'00000214 to<br>H'00000217                 |                            |                  | 2                   |           |

|                  |      | TGI3C                                 | 134 | H'00000218 to<br>H'0000021B                 | _                          |                  | 3                   |           |

|                  |      | TGI3D                                 | 135 | H'0000021C to<br>H'0000021F                 | _                          |                  | 4                   |           |

|                  |      | TCI3V                                 | 136 | H'00000220 to<br>H'00000223                 | 0 to 15 (0)                | IPR08 (15 to 12) | _                   |           |

|                  | MTU4 | TGI4A                                 | 140 | H'00000230 to<br>H'00000233                 | 0 to 15 (0)                | IPR08 (11 to 8)  | 1                   |           |

|                  |      | TGI4B                                 | 141 | H'00000234 to<br>H'00000237                 |                            |                  | 2                   |           |

|                  |      | TGI4C                                 | 142 | H'00000238 to<br>H'0000023B                 |                            |                  | 3                   |           |

|                  |      | TGI4D                                 | 143 | H'0000023C to<br>H'0000023F                 |                            |                  | 4                   |           |

|                  |      | TCI4V                                 | 144 | H'00000240 to<br>H'00000243                 | 0 to 15 (0)                | IPR08 (7 to 4)   | _                   |           |

|                  | MTU5 | TGI5U                                 | 148 | H'00000250 to<br>H'00000253                 | 0 to 15 (0)                | IPR08 (3 to 0)   | 1                   |           |

|                  |      | TGI5V                                 | 149 | H'00000254 to<br>H'00000257                 | _                          |                  | 2                   |           |

|                  |      | TGI5W                                 | 150 | H'00000258 to<br>H'0000025B                 | _                          |                  | 3                   |           |

| RTC              | ARM  |                                       | 152 | H'00000260 to<br>H'00000263                 | 0 to 15 (0)                | IPR09 (15 to 12) | 1                   |           |

|                  | PRD  |                                       | 153 | H'00000264 to<br>H'00000267                 | -                          |                  | 2                   |           |

|                  | CUP  |                                       | 154 | H'00000268 to<br>H'0000026B                 | _                          |                  | 3                   | Low       |

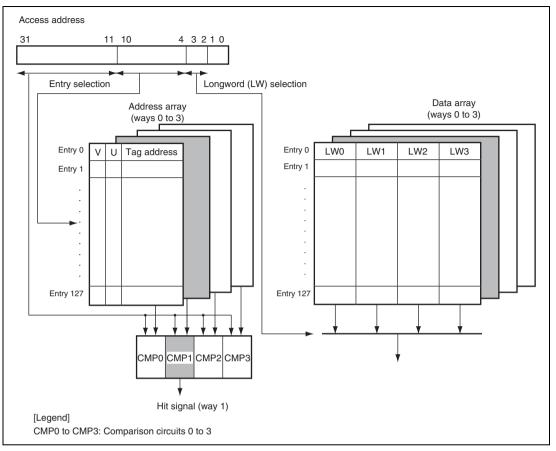

Figure 8.2 Cache Search Scheme

| Bit      | Bit Name   | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                 |

|----------|------------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18 to 16 | SZSEL[2:0] | Undefined        | R/W | Transfer Data Size Selection                                                                                                                                                                                                                                                                |

|          |            |                  |     | These bits are used to specify the number of bits<br>transferred in each single data transfer. The unit for<br>transfer can be selected as byte (8 bit), word (16 bit),<br>or longword (32 bit). For details, see section 11.9,<br>Units of Transfer and Positioning of Bytes for Transfer. |

|          |            |                  |     | Set the transfer size so that it doesn't exceed the<br>widths of the data buses supported by the source and<br>destination for DMA transfer. The bus widths of the<br>data buses are fixed by hardware.                                                                                     |

|          |            |                  |     | 000: Byte (8 bits)                                                                                                                                                                                                                                                                          |

|          |            |                  |     | 001: Word (16 bits)                                                                                                                                                                                                                                                                         |

|          |            |                  |     | 010: Longword (32 bits)                                                                                                                                                                                                                                                                     |

|          |            |                  |     | 011 to 111: Setting prohibited                                                                                                                                                                                                                                                              |

| 15       |            | 0                | R   | Reserved                                                                                                                                                                                                                                                                                    |

|          |            |                  |     | This bit is always read as 0. The write value should always be 0.                                                                                                                                                                                                                           |

| 14 to 12 | SAMOD      | Undefined        | R/W | Source Address Direction Control                                                                                                                                                                                                                                                            |

|          | [2:0]      |                  |     | These bits are used to specify the direction of counting for the source address.                                                                                                                                                                                                            |

|          |            |                  |     | 000: Fixed                                                                                                                                                                                                                                                                                  |

|          |            |                  |     | 001: Incrementation                                                                                                                                                                                                                                                                         |

|          |            |                  |     | 010: Decrementation                                                                                                                                                                                                                                                                         |

|          |            |                  |     | 011: Rotation                                                                                                                                                                                                                                                                               |

|          |            |                  |     | 100 to 111: Setting prohibited                                                                                                                                                                                                                                                              |

| 11       | _          | 0                | R   | Reserved                                                                                                                                                                                                                                                                                    |

|          |            |                  |     | This bit is always read as 0. The write value should always be 0.                                                                                                                                                                                                                           |

| 10 to 8  | DAMOD      | Undefined        | R/W | Destination Address Direction Control                                                                                                                                                                                                                                                       |

|          | [2:0]      |                  |     | These bits are used to specify the direction of counting for the source address.                                                                                                                                                                                                            |

|          |            |                  |     | 000: Fixed                                                                                                                                                                                                                                                                                  |

|          |            |                  |     | 001: Incrementation                                                                                                                                                                                                                                                                         |

|          |            |                  |     | 010: Decrementation                                                                                                                                                                                                                                                                         |

|          |            |                  |     | 011: Rotation                                                                                                                                                                                                                                                                               |

|          |            |                  |     | 100 to 111: Setting prohibited                                                                                                                                                                                                                                                              |

| Bit      | Bit Name  | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|-----------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17, 16   | STRG[1:0] | 00               | R/W | Input Sense Mode Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          |           |                  |     | These bits specify input sense modes for DMA request<br>signals input to the DMAC. The requesting source is<br>that selected from among the possible sources by the<br>DMA request source selection bits (DCTG).                                                                                                                                                                                                                                                                                           |

|          |           |                  |     | Select rising edge sense by setting these bits to "00" if<br>the software trigger (DCTG = "000000") and pins<br>DREQ0 to DREQ3 are selected as the source for DMA<br>requests. Select falling edge sense by setting the bits<br>to "10" when operation is with IIC3, SCIF, SSI, RCAN-<br>ET, MTU2, or ADC (DCTG = "000101" to "100100").<br>Table 11.4 shows the relationships between DMA<br>request sources and the possible input sense modes.<br>00: Rising edge<br>01: High level<br>10: Falling edge |

| 15 to 11 |           | All 0            | R   | 11: Low level Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 13 10 11 | _         | All U            | n   | These bits are always read as 0. The write value should always be 0.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 10       | BRLOD     | 0                | R/W | DMA Byte Count Reload Function Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |