Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                            |

|----------------------------|------------------------------------------------------------|

| Product Status             | Obsolete                                                   |

| Core Processor             | HC05                                                       |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 2.1MHz                                                     |

| Connectivity               | SCI, SPI                                                   |

| Peripherals                | POR, WDT                                                   |

| Number of I/O              | 24                                                         |

| Program Memory Size        | 8KB (8K x 8)                                               |

| Program Memory Type        | ОТР                                                        |

| EEPROM Size                | -                                                          |

| RAM Size                   | 304 x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                  |

| Data Converters            | -                                                          |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                            |

| Mounting Type              | Through Hole                                               |

| Package / Case             | 42-SDIP (0.600", 15.24mm)                                  |

| Supplier Device Package    | 42-PDIP                                                    |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68hc705c8ab |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# MC68HC705C8A MC68HSC705C8A

## **Technical Data**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://www.freescale.com

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

MC68HC705C8A — Rev. 3

**Technical Data**

16

## List of Figures

| Figure | Title                                     | Page       |

|--------|-------------------------------------------|------------|

| 5-1    | Programmable COP Watchdog Diagram         | 63         |

| 5-2    | Programmable COP Reset Register (COPRST)  | 64         |

| 5-3    | Programmable COP Control Register (COPCR) |            |

| 5-4    | Non-Programmable COP Watchdog Diagram     |            |

| 6-1    | Stop/Wait Mode Function Flowchart         |            |

| 6-2    | Programmable COP Watchdog                 |            |

|        | in Stop Mode (PCOPE = 1) Flowchart        | 72         |

| 6-3    | Non-Programmable COP Watchdog             |            |

|        | in Stop Mode (NCOPE = 1) Flowchart        | 74         |

| 7-1    | Port A Data Register (PORTA)              | 78         |

| 7-2    | Data Direction Register A (DDRA)          |            |

| 7-3    | Port A I/O Logic                          |            |

| 7-4    | Port B Data Register (PORTB)              |            |

| 7-5    | Data Direction Register B (DDRB)          |            |

| 7-6    | Port B I/O Logic                          |            |

| 7-7    | Port C Data Register (PORTC)              |            |

| 7-8    | Data Direction Register C (DDRC)          |            |

| 7-9    | Port C I/O Logic                          |            |

| 7-10   | Port D Fixed Input Register (PORTD)       |            |

| 8-1    | Timer Block Diagram                       | 90         |

| 8-2    | Timer I/O Register Summary                |            |

| 8-3    | Input Capture Operation                   |            |

| 8-4    | Output Compare Operation                  |            |

| 8-5    | Timer Control Register (TCR)              |            |

| 8-6    | Timer Status Register (TSR)               |            |

| 8-7    | Timer Registers (TRH and TRL)             | 97         |

| 8-8    | Timer Register Reads                      |            |

| 8-10   | Alternate Timer Register Reads            | 99         |

| 8-9    | Alternate Timer Registers (ATRH and ATRL) | 99         |

| 8-11   | Input Capture Registers (ICRH and ICRL)   | 100        |

| 8-12   | Output Compare Registers (OCRH and OCRL)  | 101        |

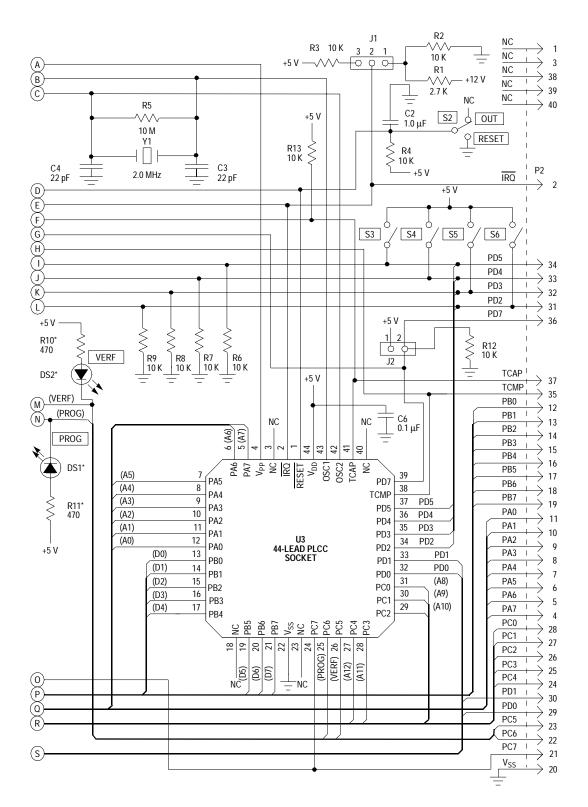

| 9-1    | EPROM/OTPROM Programming Flowchart        | 105        |

| 9-2    | PROM Programming Circuit                  | 106        |

|        | MC68HC705C8                               | A — Rev. 3 |

Resets Reset Sources

CME — Clock Monitor Enable Bit

This read/write bit enables the clock monitor. The clock monitor sets the COPF bit and generates a reset if it detects an absent internal clock for a period of from 5  $\mu s$  to 100  $\mu s$ . CME is readable and writable at any time. Reset clears the CME bit.

1 = Clock monitor enabled

0 = Clock monitor disabled

**NOTE:** Do not enable the clock monitor in applications with an internal clock frequency of 200 kHz or less.

If the clock monitor detects a slow clock, it drives the bidirectional RESET pin low for four clock cycles. If the clock monitor detects an absent clock, it drives the RESET pin low until the clock recovers.

PCOPE — Programmable COP Enable Bit

This read/write bit enables the programmable COP watchdog. PCOPE is readable at any time but can be written only once after reset. Reset clears the PCOPE bit.

1 = Programmable COP watchdog enabled

0 = Programmable COP watchdog disabled

**NOTE:** Programming the non-programmable COP enable bit (NCOPE) in mask option register 2 (MOR2) to logic 1 enables the non-programmable COP watchdog. Setting the PCOPE bit while the NCOPE bit is programmed to logic 1 enables both COP watchdogs to operate at the same time. (See **9.5.3 Mask Option Register 2**.)

CM1 and CM0 — COP Mode Bits

These read/write bits select the timeout period of the programmable COP watchdog. (See **Table 5-1**.) CM1 and CM0 can be read anytime but can be written only once. They can be cleared only by reset.

Bits 7-5 — Unused

Bits 7–5 always read as logic 0s. Reset clears bits 7–5.

MC68HC705C8A — Rev. 3

Low-Power Modes Wait Mode

#### 6.3.4 Non-Programmable COP Watchdog in Stop Mode

The STOP instruction has these effects on the non-programmable COP watchdog:

- Turns off the oscillator and the COP watchdog counter

- Clears the COP watchdog counter

If the RESET pin brings the MCU out of stop mode, the COP watchdog begins counting immediately. The reset function clears the COP counter again after the 4064- $t_{\rm CYC}$  clock stabilization delay.

If the  $\overline{\text{IRQ}}$  pin brings the MCU out of stop mode, the COP watchdog begins counting immediately. The IRQ function does not clear the COP counter again after the 4064-t<sub>CYC</sub> clock stabilization delay. See Figure 6-3.

NOTE:

If the clock monitor is enabled (CME = 1), the STOP instruction causes it to time out and reset the MCU.

#### 6.4 Wait Mode

The WAIT instruction places the MCU in an intermediate power consumption mode. All central processor unit (CPU) activity is suspended, but the oscillator, capture/compare timer, SCI, and SPI remain active. Any interrupt or reset brings the MCU out of wait mode. See **Figure 6-1**.

The WAIT instruction has these effects on the CPU:

- Clears the I bit in the condition code register, enabling interrupts

- Stops the CPU clock, but allows the internal clock to drive the capture/compare timer, SCI, and SPI

The WAIT instruction does not affect any other registers or I/O lines. The capture/compare timer, SCI, and SPI can be enabled to allow a periodic exit from wait mode.

MC68HC705C8A — Rev. 3

**Low-Power Modes**

Technical Data MC68HC705C8A — Rev. 3

## Technical Data — MC68HC705C8A

## Section 7. Parallel Input/Output (I/O)

#### 7.1 Contents

| 7.2   | Introduction//              |

|-------|-----------------------------|

| 7.3   | Port A                      |

| 7.3.1 | Port A Data Register78      |

| 7.3.2 | Data Direction Register A79 |

| 7.3.3 | Port A Logic                |

| 7.4   | Port B                      |

| 7.4.1 | Port B Data Register81      |

| 7.4.2 | Data Direction Register B82 |

| 7.4.3 | Port B Logic                |

| 7.5   | Port C                      |

| 7.5.1 | Port C Data Register85      |

| 7.5.2 | Data Direction Register C86 |

| 7.5.3 | Port C Logic                |

| 7.6   | Port D88                    |

## 7.2 Introduction

This section describes the programming of ports A, B, C, and D.

MC68HC705C8A — Rev. 3

Capture/Compare Timer Timer I/O Registers

TOF — Timer Overflow Flag

The TOF bit is automatically set when the 16-bit counter rolls over from \$FFFF to \$0000. Clear the TOF bit by reading the timer status register with TOF set and then reading the low byte (\$0019) of the timer registers. Reset has no effect on TOF.

1 = Timer overflow

0 = No timer overflow

Bits 4–0 — Not used; these bits always read 0

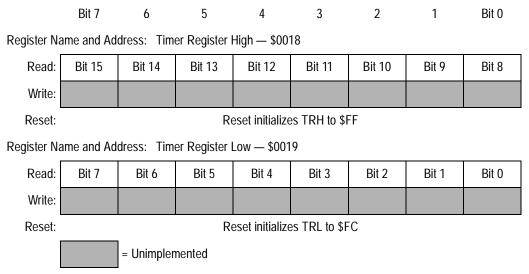

#### 8.4.3 Timer Registers

The read-only timer registers (TRH and TRL) shown in **Figure 8-7** contain the current high and low bytes of the 16-bit counter. Reading TRH before reading TRL causes TRL to be latched until TRL is read. Reading TRL after reading the timer status register clears the timer overflow flag bit (TOF). Writing to the timer registers has no effect.

Figure 8-7. Timer Registers (TRH and TRL)

MC68HC705C8A — Rev. 3

Capture/Compare Timer Timer I/O Registers

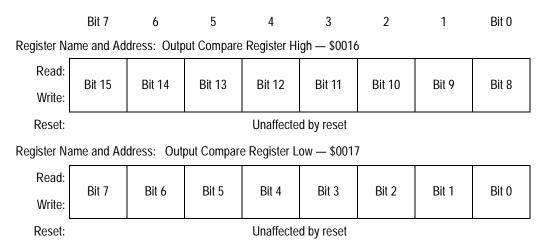

#### 8.4.6 Output Compare Registers

When the value of the 16-bit counter matches the value in the read/write output compare registers (OCRH and OCRL) shown in **Figure 8-12**, the planned TCMP pin action takes place. Writing to OCRH before writing to OCRL inhibits timer compares until OCRL is written. Reading or writing to OCRL after reading the timer status register clears the output compare flag (OCF).

Figure 8-12. Output Compare Registers (OCRH and OCRL)

To prevent OCF from being set between the time it is read and the time the output compare registers are updated, use this procedure:

- 1. Disable interrupts by setting the I bit in the condition code register.

- 2. Write to OCRH. Compares are now inhibited until OCRL is written.

- 3. Clear bit OCF by reading the timer status register (TSR).

- 4. Enable the output compare function by writing to OCRL.

- 5. Enable interrupts by clearing the I bit in the condition code register.

MC68HC705C8A — Rev. 3

## Technical Data — MC68HC705C8A

## Section 9. EPROM/OTPROM (PROM)

#### 9.1 Contents

| 9.2                   | Introduction                                                                    |

|-----------------------|---------------------------------------------------------------------------------|

| 9.3<br>9.3.1<br>9.3.2 | EPROM/OTPROM (PROM) Programming.104Program Register.109Preprogramming Steps.110 |

| 9.4                   | PROM Programming Routines                                                       |

| 9.4.1                 | Program and Verify PROM111                                                      |

| 9.4.2                 | Verify PROM Contents112                                                         |

| 9.4.3                 | Secure PROM112                                                                  |

| 9.4.4                 | Secure PROM and Verify113                                                       |

| 9.4.5                 | Secure PROM and Dump113                                                         |

| 9.4.6                 | Load Program into RAM and Execute                                               |

| 9.4.7                 | Execute Program in RAM115                                                       |

| 9.4.8                 | Dump PROM Contents115                                                           |

| 9.5                   | Control Registers                                                               |

| 9.5.1                 | Option Register                                                                 |

| 9.5.2                 | Mask Option Register 1                                                          |

| 9.5.3                 | Mask Option Register 2                                                          |

| 9.6                   | EPROM Erasing                                                                   |

## 9.2 Introduction

This section describes erasable, programmable read-only memory/one-time programmable read-only memory (EPROM/OTPROM (PROM)) programming.

MC68HC705C8A — Rev. 3

EPROM/OTPROM (PROM)

EPROM/OTPROM (PROM) Programming

Figure 9-2. PROM Programming Circuit (Continued)

MC68HC705C8A — Rev. 3

### 9.6 EPROM Erasing

The erased state of an EPROM or OTPROM byte is \$00. EPROM devices can be erased by exposure to a high intensity ultraviolet (UV) light with a wave length of 2537 Å. The recommended erasure dosage (UV intensity on a given surface area x exposure time) is 15 Ws/cm<sup>2</sup>. UV lamps should be used without short-wave filters, and the EPROM device should be positioned about one inch from the UV source.

OTPROM devices are shipped in an erased state. Once programmed, they cannot be erased. Electrical erasing procedures cannot be performed on either EPROM or OTPROM devices.

## Serial Communications Interface (SCI)

#### 10.3 Features

#### Features of the SCI module include:

- Standard mark/space non-return-to-zero format

- Full-duplex operation

- 32 programmable baud rates

- Programmable 8-bit or 9-bit character length

- Separately enabled transmitter and receiver

- Two receiver wakeup methods:

- Idle line wakeup

- Address mark wakeup

- Interrupt-driven operation capability with five interrupt flags:

- Transmitter data register empty

- Transmission complete

- Receiver data register full

- Receiver overrun

- Idle receiver input

- Receiver framing error detection

- 1/16 bit-time noise detection

#### 10.4 SCI Data Format

The SCI uses the standard non-return-to-zero mark/space data format illustrated in **Figure 10-1**.

Serial Communications Interface (SCI)

SCI I/O Registers

WAKE — Wakeup Bit

This read/write bit determines which condition wakes up the SCI: a logic 1 (address mark) in the most significant bit position of a received character or an idle condition of the PD0/RDI pin. Reset has no effect on the WAKE bit.

1 = Address mark wakeup

0 = Idle line wakeup

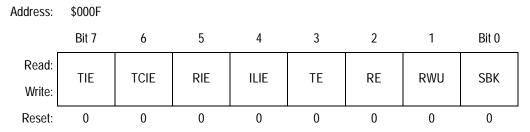

#### 10.6.3 SCI Control Register 2

SCI control register 2 (SCCR2) shown in **Figure 10-7** has these functions:

- Enables the SCI receiver and SCI receiver interrupts

- Enables the SCI transmitter and SCI transmitter interrupts

- Enables SCI receiver idle interrupts

- Enables SCI transmission complete interrupts

- Enables SCI wakeup

- Transmits SCI break characters

Figure 10-7. SCI Control Register 2 (SCCR2)

TIE — Transmit Interrupt Enable Bit

This read/write bit enables SCI interrupt requests when the TDRE bit becomes set. Reset clears the TIE bit.

1 = TDRE interrupt requests enabled

0 = TDRE interrupt requests disabled

MC68HC705C8A — Rev. 3

## Serial Peripheral Interface (SPI)

#### 11.3 Features

Features of the SPI include:

- Full-duplex operation

- Master and slave modes

- Four programmable master mode frequencies (1.05 MHz maximum)

- 2.1-MHz maximum slave mode frequency

- Serial clock with programmable polarity and phase

- End of transmission interrupt flag

- Write collision error flag

- Bus contention error flag

Figure 11-1 shows the structure of the SPI module. Figure 11-2 is a summary of the SPI input/output (I/O) registers.

Instruction Set Addressing Modes

#### 12.3.1 Inherent

Inherent instructions are those that have no operand, such as return from interrupt (RTI) and stop (STOP). Some of the inherent instructions act on data in the CPU registers, such as set carry flag (SEC) and increment accumulator (INCA). Inherent instructions require no operand address and are one byte long.

#### 12.3.2 Immediate

Immediate instructions are those that contain a value to be used in an operation with the value in the accumulator or index register. Immediate instructions require no operand address and are two bytes long. The opcode is the first byte, and the immediate data value is the second byte.

#### 12.3.3 Direct

Semiconductor, Inc.

Direct instructions can access any of the first 256 memory locations with two bytes. The first byte is the opcode, and the second is the low byte of the operand address. In direct addressing, the CPU automatically uses \$00 as the high byte of the operand address.

#### 12.3.4 Extended

Extended instructions use three bytes and can access any address in memory. The first byte is the opcode; the second and third bytes are the high and low bytes of the operand address.

When using the Motorola assembler, the programmer does not need to specify whether an instruction is direct or extended. The assembler automatically selects the shortest form of the instruction.

MC68HC705C8A — Rev. 3

## **Electrical Specifications**

#### 13.8 3.3-Volt DC Electrical Characteristics

| Characteristic <sup>(1)</sup>                                                                                                                                                                  | Symbol                             | Min                        | Тур <sup>(2)</sup>   | Max                   | Unit           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------------|----------------------|-----------------------|----------------|

| Output voltage, I <sub>Load</sub> ≤ 10.0 μA                                                                                                                                                    | V <sub>OL</sub><br>V <sub>OH</sub> | —<br>V <sub>DD</sub> – 0.1 | _<br>_               | 0.1<br>—              | V              |

| Output high voltage  I <sub>Load</sub> = -0.2 mA  PA7-PA0, PB7-PB0, PC6-PC0, TCMP  (see Figure 13-2)  I <sub>Load</sub> = -0.4 mA  PD4-PD1 (see Figure 13-3)  I <sub>Load</sub> = -1.5 mA  PC7 | V <sub>ОН</sub>                    | V <sub>DD</sub> – 0.3      | _<br>_<br>_          | _<br>_<br>_           | V              |

| Output low voltage (see Figure 13-4) $I_{Load} = 0.4 \text{ mA}$ $PA7-PA0, PB7-PB0, PC6-PC0, PD4-PD1$ $I_{Load} = 6.0 \text{ mA}$ $PC7$                                                        | V <sub>OL</sub>                    | _                          |                      | 0.3                   | V              |

| Input high voltage PA7-PA0, PB7-PB0, PC7-PC0, PD5-PD0, PD7, TCAP, IRQ, RESET, OSC1                                                                                                             | V <sub>IH</sub>                    | 0.7 x V <sub>DD</sub>      | _                    | V <sub>DD</sub>       | V              |

| Input low voltage PA7-PA0, PB7-PB0, PC7-PC0, PD5-PD0, PD7, TCAP, IRQ, RESET, OSCI                                                                                                              | V <sub>IL</sub>                    | V <sub>SS</sub>            | _                    | 0.2 x V <sub>DD</sub> | V              |

| Data-retention mode (0°C to 70°C)                                                                                                                                                              | $V_{RM}$                           | 2.0                        | _                    | _                     | V              |

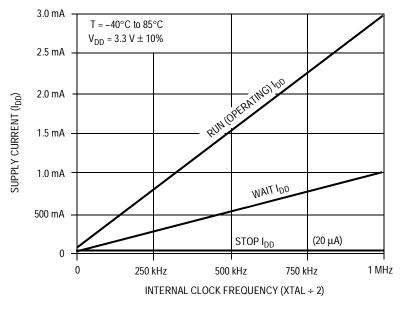

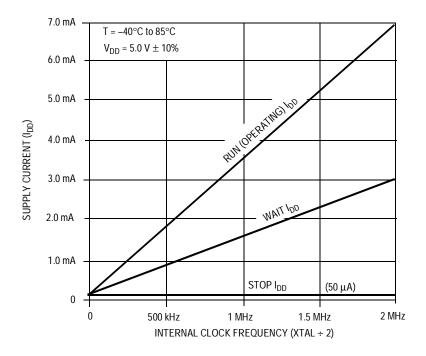

| Supply current <sup>(3)</sup> Run <sup>(4)</sup> Wait <sup>(5)</sup> Stop <sup>(6)</sup>                                                                                                       | I <sub>DD</sub>                    | _<br>_<br>_                | 1.53<br>0.711<br>2.0 | 3.0<br>1.0<br>20      | mA<br>mA<br>μA |

| I/O ports hi-z leakage current PA7-PA0, PB7-PB0, PC7-PC0, PD4-PD1, PD7, RESET                                                                                                                  | I <sub>IL</sub>                    | _                          | _                    | ± 10                  | μΑ             |

| Input current IRQ, TCAP, OSC1, PD5, PD0                                                                                                                                                        | I <sub>In</sub>                    | _                          | _                    | ± 1                   | μΑ             |

<sup>1.</sup>  $V_{DD}$  = 3.3 V  $\pm$  10%;  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted

**Technical Data**

MC68HC705C8A — Rev. 3

<sup>2.</sup> Typical values at midpoint of voltage range, 25°C only.

<sup>3.</sup> I<sub>DD</sub> measured with port B pullup devices disabled.

<sup>4.</sup> Run (operating) I<sub>DD</sub> measured using external square wave clock source (f<sub>OSC</sub> = 2.0 MHz). All inputs 0.2 V from rail. No dc loads. Less than 50 pF on all outputs. C<sub>L</sub> = 20 pF on OSC2. OSC2 capacitance linearly affects run I<sub>DD</sub>.

<sup>5.</sup> Wait  $I_{DD}$  measured using external square wave clock source ( $f_{OSC}$  = 2.0 MHz). All inputs 0.2 V from rail. No dc loads. Less than 50 pF on all outputs.  $C_L$  = 20 pF on OSC2.  $V_{IL}$  = 0.2 V,  $V_{IH}$  =  $V_{DD}$  – 0.2 V. All ports configured as inputs. SPI and SCI disabled. If SPI and SCI enabled, add 10% current draw. OSC2 capacitance linearly affects wait  $I_{DD}$ .

Stop I<sub>DD</sub> measured with OSC1 = V<sub>DD</sub>. All ports configured as inputs. V<sub>IL</sub> = 0.2 V; V<sub>IH</sub> = V<sub>DD</sub> − 0.2 V.

## **Electrical Specifications**

#### (a) Maximum Current Drain versus Frequency @ 3.3 $V \pm 10 \%$

(b) Maximum Current Drain versus Frequency @ 5 V  $\pm\,10\%$

Figure 13-4. Total Current Drain versus Frequency

# NP

## **Electrical Specifications**

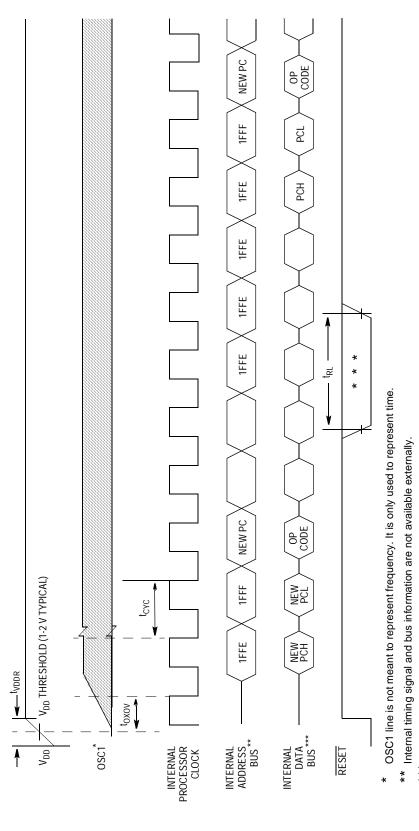

Figure 13-7. Power-On Reset and External Reset Timing Diagram

\*\*\*The next rising edge of the internal processor clock following the rising edge of RESET initiates the reset sequence.

## **Mechanical Specifications**

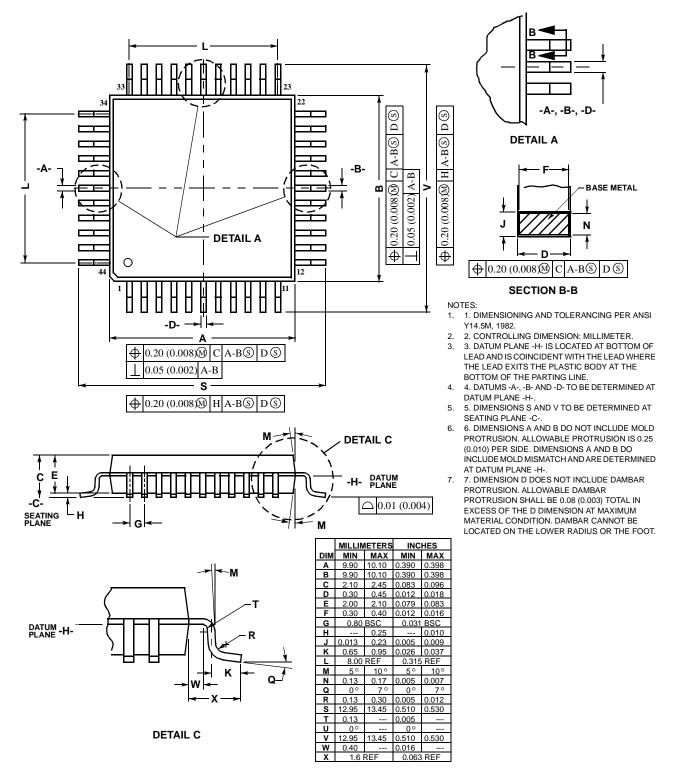

## 14.7 44-Pin Quad Flat Pack (QFP)

Figure 14-5. MC68HC705C8AFB Package Dimensions (Case #824A)

Technical Data MC68HC705C8A — Rev. 3

#### M

| mask option registers                                | 23, 117, 118 |

|------------------------------------------------------|--------------|

| MC68HSC705C8A (high-speed part)                      | 204          |

| ordering information                                 | 209          |

| programmable COP timeout period selection SPI timing |              |

| mechanical specifications                            | 191          |

| memory<br>bootloader ROM                             | 37           |

| I/O                                                  | 36           |

| I/O register summary                                 | 39           |

| memory map                                           |              |

| PROM (EPROM/OTPROM)                                  |              |

| RAM                                                  | 36           |

| memory map                                           | 35, 38       |

| Ο                                                    |              |

| on-chip memory                                       | 35           |

| opcode map                                           | 170          |

| option register                                      | 23           |

| ordering informationorder numbers                    |              |

| OSC1 pin                                             | 30           |

| OSC2 pin                                             | 30           |

| oscillator                                           |              |

| ceramic resonator                                    | 30           |

| crystal resonator                                    |              |

| external clock signal                                | 30           |

MC68HC705C8A — Rev. 3