Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HC05                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 2.1MHz                                                                  |

| Connectivity               | SCI, SPI                                                                |

| Peripherals                | POR, WDT                                                                |

| Number of I/O              | 24                                                                      |

| Program Memory Size        | 8KB (8K x 8)                                                            |

| Program Memory Type        | ОТР                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 304 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                               |

| Data Converters            |                                                                         |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-LCC (J-Lead)                                                         |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc705c8acfn |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Section 1. General Description

## 1.1 Contents

| 1.2    | Introduction                         |

|--------|--------------------------------------|

| 1.3    | Features                             |

| 1.4    | Programmable Options23               |

| 1.5    | Block Diagram                        |

| 1.6    | Pin Assignments                      |

| 1.7    | Pin Functions                        |

| 1.7.1  | V <sub>DD</sub> and V <sub>SS</sub>  |

| 1.7.2  | V <sub>PP</sub>                      |

| 1.7.3  | OSC1 and OSC2                        |

| 1.7.3. | 1 Crystal Resonator                  |

| 1.7.3. | 2 Ceramic Resonator                  |

| 1.7.3. |                                      |

| 1.7.4  | External Reset Pin (RESET)           |

| 1.7.5  | External Interrupt Request Pin (IRQ) |

| 1.7.6  | Input Capture Pin (TCAP)             |

| 1.7.7  | Output Compare Pin (TCMP)            |

| 1.7.8  | Port A I/O Pins (PA7–PA0)            |

| 1.7.9  | Port B I/O Pins (PB7–PB0)            |

| 1.7.10 |                                      |

|        |                                      |

| 1.7.11 | Port D I/O Pins (PD7 and PD5–PD0)    |

MC68HC705C8A — Rev. 3

Freescale Semiconductor, Inc.

### 1.7.7 Output Compare Pin (TCMP)

The TCMP pin is the output compare pin for the on-chip capture/compare timer. See Section 8. Capture/Compare Timer .

1.7.8 Port A I/O Pins (PA7 -PA0)

These eight I/O lines comprise port A, a general-purpose, bidirectional I/O port. The pins are programmable as either inputs or outputs under software control of the data direction registers. See 7.3 Port A.

## 1.7.9 Port B I/O Pins (PB7 -PB0)

These eight I/O pins comprise port B, a general-purpose, bidirectional I/O port. The pins are programmable as either inputs or outputs under software control of the data direction registers. Port B pins also can be configured to function as external interrupts. See 7.4 Port B.

### 1.7.10 Port C I/O Pins (PC7 -PC0)

These eight I/O pins comprise port C, a general-purpose, bidirectional I/O port. The pins are programmable as either inputs or outputs under software control of the data direction registers. PC7 has a high current sink and source capability. See 7.5 Port C.

1.7.11 Port D I/O Pins (PD7 and PD5 -PD0)

These seven lines comprise port D, a fixed input port. All special functions that are enabled (SPI and SCI) affect this port. See 7.6 Port D.

MC68HC705C8A — Rev. 3

**Technical Data**

Freescale Semiconductor, Inc.

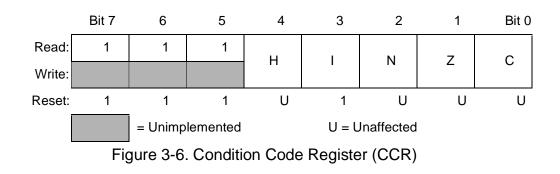

#### 3.3.5 Condition Code Register

The condition code register (CCR) shown in Figure 3-6 is an 8-bit register whose three most significant bits are permanently fixed at 111. The condition code register contains the interrupt mask and four bits that indicate the results of prior instructions.

#### H — Half-Carry Bit

The CPU sets the half-carry flag when a carry occurs between bits 3 and 4 of the accumulator during an add without carry (ADD) or add with carry (ADC) operation. The half-carry bit is required for binary-coded decimal (BCD) arithmetic operations. Reset has no affect on the half-carry flag.

I — Interrupt Mask Bit

Setting the interrupt mask (I) disables interrupts. If an interrupt request occurs while the interrupt mask is a logic 0, the CPU saves the CPU registers on the stack, sets the interrupt mask, and then fetches the interrupt vector. If an interrupt request occurs while the interrupt mask is set, the interrupt request is latched. The CPU processes the latched interrupt as soon as the interrupt mask is cleared again.

A return-from-interrupt (RTI) instruction pulls the CPU registers from the stack, restoring the interrupt mask to its cleared state. After a reset, the interrupt mask is set and can be cleared only by a CLI, STOP, or WAIT instruction.

MC68HC705C8A — Rev. 3

MOTOROLA

**Technical Data**

### Central Processor Unit (CPU)

N — Negative Flag

The CPU sets the negative flag when an arithmetic operation, logical operation, or data manipulation produces a negative result (bit 7 in the results is a logic 1). Reset has no effect on the negative flag.

Z — Zero Flag

The CPU sets the zero flag when an arithmetic operation, logical operation, or data manipulation produces a result of \$00. Reset has no effect on the zero flag.

C — Carry/Borrow Flag

The CPU sets the carry/borrow flag when an addition operation produces a carry out of bit 7 of the accumulator or when a subtraction operation requires a borrow. Some logical operations and data manipulation instructions also clear or set the carry/borrow bit. Reset has no effect on the carry/borrow flag.

# 3.4 Arithmetic/Logic Unit (ALU)

The arithmetic/logic unit (ALU) performs the arithmetic and logical operations defined by the instruction set. The binary arithmetic circuits decode instructions and set up the ALU for the selected operation. Most binary arithmetic is based on the addition algorithm, carrying out subtraction as negative addition. Multiplication is not performed as a discrete operation but as a chain of addition and shift operations within the ALU. The multiply instruction requires 11 internal clock cycles to complete this chain of operations.

reescale Semiconductor, Inc.

Technical Data

MC68HC705C8A — Rev. 3

# Section 4. Interrupts

## 4.1 Contents

| 4.2   | Introduction                     |

|-------|----------------------------------|

| 4.3   | Interrupt Sources                |

| 4.3.1 | Software Interrupt               |

| 4.3.2 | External Interrupt (IRQ)51       |

| 4.3.3 | Port B Interrupts                |

| 4.3.4 | Capture/Compare Timer Interrupts |

| 4.3.5 | SCI Interrupts                   |

| 4.3.6 | SPI Interrupts                   |

| 4.4   | Interrupt Processing             |

# 4.2 Introduction

This section describes how interrupts temporarily change the normal processing sequence.

#### MC68HC705C8A — Rev. 3

#### 4.3.2 External Interrupt (IRQ)

An interrupt signal on the  $\overline{IRQ}$  pin latches an external interrupt request. After completing the current instruction, the CPU tests these bits:

- IRQ latch

- I bit in the CCR

Setting the I bit in the CCR disables external interrupts.

If the IRQ latch is set and the I bit is clear, the CPU then begins the interrupt sequence. The CPU clears the IRQ latch while it fetches the interrupt vector, so that another external interrupt request can be latched during the interrupt service routine. As soon as the I bit is cleared during the return-from-interrupt (RTI) instruction, the CPU can recognize the new interrupt request. Figure 4-1 shows the logic for external interrupts.

Figure 4-1 shows an external interrupt functional diagram. Figure 4-2 shows an external interrupt timing diagram for the interrupt line. The tiL15()v9 Tc6(r)-4(upt)21( func012 111015( )v9 e )18(ter)4(u)15(he )]TJon, i7.44.

2. COP clear bit (COPC) at address \$1FF0

To clear the non-programmable COP watchdog and start a new COP timeout period, write a logic 0 to bit 0 of address \$1FF0. Reading address \$1FF0 returns the mask option register 1 (MOR1) data at that location. See 9.5.2 Mask Option Register 1 .

NOTE: The non-programmable watchdog COP is disabled in bootloader mode, even if the NCOPE bit is programmed.

Figure 5-4 is a diagram of the non-programmable COP.

# Freescale Semiconductor, Inc.

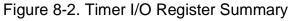

| Addr.                          | Register Name                                                      | Bit 7                  | <b>7</b> 6 | 5        | 4           | 3          | 2         |        | 1 B   | it O  |  |

|--------------------------------|--------------------------------------------------------------------|------------------------|------------|----------|-------------|------------|-----------|--------|-------|-------|--|

| \$0012                         | Read:<br>Timer Control Register<br>(TCR) Write:                    |                        | OCIE       | TOIE     | 0           | 0          | 0         | IEI    | DG O  | LVL   |  |

|                                | See page 94<br>Reset:                                              | 0                      | 0          | 0        | 0           | 0          | 0         | U      | 0     | -     |  |

| \$0013                         | Read:<br>Timer Status Register                                     | ICF                    | OCF        | TOF      | 0           | 0          | 0         | (      | φ     | φ     |  |

|                                | (ISR) Write                                                        |                        |            |          |             |            |           |        |       |       |  |

|                                | See page 96<br>Reset:                                              | U                      | U          | U        | 0           | 0          | 0         | 0      | 0     | -     |  |

| \$0014                         | F                                                                  | Bit 15                 | Bit 1      | Bit 13   | 3 Bit       | 12 Bit     | 11 E      | Bit 10 | Bit 9 | Bit 8 |  |

|                                | Read:<br>Input Capture Register<br>High (ICRH)Write                |                        |            |          |             |            |           |        |       |       |  |

|                                | See page 100<br>Reset:                                             | t: Unaffected by reset |            |          |             |            |           |        |       |       |  |

|                                | г                                                                  |                        | Bit 6      | Bit 5    | Bit         | -          |           | it 2   | Bit 1 | Bit 0 |  |

| \$0015                         | Read:<br>Input Capture Register<br>Low (ICRL)Write                 |                        |            |          |             |            |           |        |       |       |  |

|                                | See page 100<br>Reset:                                             | Unaffected by reset    |            |          |             |            |           |        |       |       |  |

|                                | Output Compare Regis <b>Re</b> ad:<br>High (OCRH) <sub>Write</sub> |                        |            |          |             |            |           |        |       | ]     |  |

| \$0016                         |                                                                    | Bit 15                 | Bit 14     | Bit 13   | Bit 1       | 2 Bit      | 11 Bi     | t 10   | Bit 9 | Bit 8 |  |

| φουτο                          | See page 101. <sup>WIIIE</sup><br>Reset:                           |                        |            |          |             |            |           |        |       |       |  |

|                                | Read:<br>Output Compare Register<br>Low (OCRL)Write:               |                        |            |          | onane       |            | 501       |        |       | _     |  |

| \$0017                         |                                                                    | Bit 7                  | Bit 6      | Bit 5    | Bit 4       | Bit 3      | 8 Bit     | 2 E    | 3it 1 | Bit O |  |

|                                | See page 101<br>Reset:                                             | Unaffected by reset    |            |          |             |            |           |        |       |       |  |

|                                | Read:<br>Timer Register High                                       |                        | Bit 1      | Bit 13   |             |            |           | Bit 10 | Bit 9 | Bit 8 |  |

| \$0018                         |                                                                    | DICTO                  | DIL 14     | F DIL I  | 5 Bit       | TZ BI      |           |        | Bit 9 | ыго   |  |

|                                | (TRH) Write<br>See page 97<br>Reset:                               |                        |            |          |             |            |           |        |       |       |  |

|                                | F                                                                  |                        |            |          |             |            |           |        | bira  |       |  |

| \$0019                         | Timer Register Low                                                 | Bit 7                  | Bit 6      | Bit 5    | Bit         | 4 Bit      | 3 В       | it 2   | Bit 1 | Bit 0 |  |

|                                | (TRL) Write<br>See page 97<br>Reset:                               |                        |            |          |             |            |           |        |       |       |  |

|                                | F                                                                  |                        |            |          |             |            |           |        |       |       |  |

| \$001A                         | Read:<br>Alternate Timer Register                                  | Bit 15                 | Bit 1      | Bit 13   | 3 Bit       | 12 Bit     | 11 E      | Bit 10 | Bit 9 | Bit 8 |  |

|                                | HIGN (AT RH)VVIITE                                                 |                        |            |          |             |            |           |        |       |       |  |

|                                | See page 99<br>Reset:                                              |                        |            |          |             |            |           |        |       |       |  |

| \$001B                         | Alternate Timer Register                                           | Bit 7                  | Bit 6      | Bit 5    | Bit         | 4 Bit      | 3 B       | it 2   | Bit 1 | Bit 0 |  |

|                                | Low (ALRI)Write                                                    |                        |            |          |             |            |           |        |       |       |  |

|                                | See page 99<br>Reset:                                              |                        |            | R        | eset initia | alizes ATR | L to \$FC |        |       |       |  |

| = Unimplemented U = Unaffected |                                                                    |                        |            |          |             |            |           |        |       |       |  |

|                                | Figure 8                                                           | R-2 Tin                | ner I/O I  | Reaister | Summa       | arv/       |           |        |       |       |  |

MC68HC705C8A — Rev. 3

MOTOROLA

**Technical Data**