Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | HC05                                                         |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 2.1MHz                                                       |

| Connectivity               | SCI, SPI                                                     |

| Peripherals                | POR, WDT                                                     |

| Number of I/O              | 24                                                           |

| Program Memory Size        | 8KB (8K x 8)                                                 |

| Program Memory Type        | ОТР                                                          |

| EEPROM Size                | -                                                            |

| RAM Size                   | 304 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                    |

| Data Converters            | -                                                            |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 44-LCC (J-Lead)                                              |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                        |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68hc705c8afne |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 5.3   | Reset Sources                     |

|-------|-----------------------------------|

| 5.3.1 | Power-On Reset (POR)62            |

| 5.3.2 | External Reset                    |

| 5.3.3 | Programmable and Non-Programmable |

|       | COP Watchdog Resets62             |

| 5.3.4 | Clock Monitor Reset67             |

## Section 6. Low-Power Modes

| 6.1                                     | Contents            |

|-----------------------------------------|---------------------|

| 6.2                                     | Introduction        |

| 6.3<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4 | Stop Mode           |

| 6.4<br>6.4.1<br>6.4.2                   | Wait Mode.          |

| 6.5                                     | Data-Retention Mode |

|                                         |                     |

# Section 7. Parallel Input/Output (I/O)

| 7.1   | Contents                    |

|-------|-----------------------------|

| 7.2   | Introduction                |

| 7.3   | Port A                      |

| 7.3.1 | Port A Data Register        |

| 7.3.2 | Data Direction Register A79 |

| 7.3.3 | Port A Logic                |

| 7.4   | Port B                      |

| 7.4.1 | Port B Data Register81      |

| 7.4.2 | Data Direction Register B   |

| 7.4.3 | Port B Logic                |

Semiconductor, Inc.

Freescale

## Freescale Semiconductor, Inc.

### Section 13. Electrical Specifications

| 13.1  | Contents                                          |

|-------|---------------------------------------------------|

| 13.2  | Introduction                                      |

| 13.3  | Maximum Ratings172                                |

| 13.4  | Operating Temperature Range                       |

| 13.5  | Thermal Characteristics                           |

| 13.6  | Power Considerations                              |

| 13.7  | 5.0-Volt DC Electrical Characteristics            |

| 13.8  | 3.3-Volt DC Electrical Characteristics            |

| 13.9  | 5.0-Volt Control Timing                           |

| 13.10 | 3.3-Volt Control Timing                           |

| 13.11 | 5.0-Volt Serial Peripheral Interface (SPI) Timing |

| 13.12 | 3.3-Volt Serial Peripheral Interface (SPI) Timing |

#### **Section 14. Mechanical Specifications**

| 14.1 | Contents                                        |

|------|-------------------------------------------------|

| 14.2 | Introduction                                    |

| 14.3 | 40-Pin Plastic Dual In-Line Package (PDIP)192   |

| 14.4 | 40-Pin Ceramic Dual In-Line Package (Cerdip)193 |

| 14.5 | 44-Lead Plastic-Leaded Chip Carrier (PLCC)194   |

| 14.6 | 44-Lead Ceramic-Leaded Chip Carrier (CLCC)      |

| 14.7 | 44-Pin Quad Flat Pack (QFP)196                  |

| 14.8 | 42-Pin Shrink Dual In-Line Package (SDIP)       |

# **List of Tables**

| Table                                                | Title                                                                                                                                                                                                | Page                                 |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 2-1                                                  | Memory Configurations                                                                                                                                                                                | 36                                   |

| 4-1                                                  | Reset/Interrupt Vector Addresses                                                                                                                                                                     | 57                                   |

| 5-1                                                  | Programmable COP Timeout Period Selection                                                                                                                                                            | 66                                   |

| 7-1<br>7-2<br>7-3                                    | Port A Pin Functions.<br>Port B Pin Functions.<br>Port C Pin Functions.                                                                                                                              | 84                                   |

| 9-1<br>9-2                                           | MC68HC05PGMR PCB Reference Designators<br>PROM Programming Routines                                                                                                                                  |                                      |

| 10-1<br>10-2<br>10-3                                 | Baud Rate Generator Clock PrescalingBaud Rate SelectionBaud Rate Selection Examples                                                                                                                  | .137                                 |

| 11-1                                                 | SPI Clock Rate Selection                                                                                                                                                                             | .150                                 |

| 12-1<br>12-2<br>12-3<br>12-4<br>12-5<br>12-6<br>12-7 | Register/Memory Instructions.<br>Read-Modify-Write Instructions<br>Jump and Branch Instructions<br>Bit Manipulation Instructions.<br>Control Instructions.<br>Instruction Set Summary<br>Opcode Map. | .159<br>.161<br>.162<br>.163<br>.164 |

| 15-1                                                 | MC68HC705C8A Order Numbers                                                                                                                                                                           | .199                                 |

|   | 1  | ß  | ij |    |  |

|---|----|----|----|----|--|

|   | 1  | h  | J  |    |  |

|   | (  | E  |    |    |  |

|   | 1  |    |    |    |  |

|   |    |    |    |    |  |

|   |    |    | ÷  | •  |  |

|   | ì  | s. | _  |    |  |

|   | 1  |    | -  |    |  |

|   |    | 6  | 2  | )  |  |

| ÷ | ł  | í  | 1  | 1  |  |

|   | 7  | ī  | h  |    |  |

|   | (  | 6  | 2  |    |  |

|   | l  |    |    | Į. |  |

| _ | I  |    | 1  |    |  |

|   | (  | c  |    |    |  |

|   | 2  | 2  | 1  | í. |  |

|   | 1  | F  |    | i. |  |

|   | 4  | į  |    | ì  |  |

|   | (  | b  | J  |    |  |

|   | (  | Ł  | 3  |    |  |

|   | ì  |    | 2  |    |  |

|   |    |    |    |    |  |

|   | i. |    |    |    |  |

|   | (  |    |    |    |  |

|   |    |    |    |    |  |

|   |    |    |    |    |  |

|   |    |    |    |    |  |

|   |    |    |    |    |  |

|   |    |    |    |    |  |

|   |    |    |    | ,  |  |

|   |    |    |    |    |  |

|   |    |    |    | ,  |  |

|   |    |    |    |    |  |

|   |    |    |    | ,  |  |

|   |    |    |    |    |  |

|   |    |    |    |    |  |

|   |    |    |    |    |  |

|   |    |    |    |    |  |

|   |    |    |    |    |  |

|   |    |    | J  |    |  |

|   |    |    |    |    |  |

|   |    |    |    |    |  |

Memory Bootloader ROM

| Addr.  | Register Name                                                   |                 | Bit 7 | 6         | 5      | 4           | 3           | 2     | 1     | Bit 0 |

|--------|-----------------------------------------------------------------|-----------------|-------|-----------|--------|-------------|-------------|-------|-------|-------|

| \$0000 | Port A Data Register<br>(PORTA)                                 | Read:<br>Write: | PA7   | PA6       | PA5    | PA4         | PA3         | PA2   | PA1   | PA0   |

|        | See page 78.                                                    | Reset:          |       |           |        | Unaffecte   | ed by reset |       |       |       |

| \$0001 |                                                                 | Read:<br>Write: | PB7   | PB6       | PB5    | PB4         | PB3         | PB2   | PB1   | PB0   |

|        | See page 81.                                                    | Reset:          |       |           |        | Unaffecte   | ed by reset |       |       |       |

| \$0002 | · · · · · · · · · · · · · · · · · · ·                           | Read:<br>Write: | PC7   | PC6       | PC5    | PC4         | PC3         | PC2   | PC1   | PC0   |

|        | See page 85.                                                    | Reset:          |       |           |        | Unaffecte   | ed by reset |       |       |       |

|        | Port D Fixed Input Register                                     | Read:           | PD7   |           | SS     | SCK         | MOSI        | MISO  | TDO   | RDI   |

| \$0003 | (PORTD)                                                         | Write:          |       |           |        |             |             |       |       |       |

|        | See page 88.                                                    | Reset:          |       |           |        | Unaffecte   | ed by reset |       |       |       |

| \$0004 | Port A Data Direction<br>Register (DDRA)                        | Read:<br>Write: | DDRA7 | DDRA6     | DDRA5  | DDRA4       | DDRA3       | DDRA2 | DDRA1 | DDRA0 |

|        | See page 79.                                                    | Reset:          | 0     | 0         | 0      | 0           | 0           | 0     | 0     | 0     |

| \$0005 | \$0005 Port B Data Direction<br>Register (DDRB)<br>See page 82. | Read:<br>Write: | DDRB7 | DDRB6     | DDRB5  | DDRB4       | DDRB3       | DDRB2 | DDRB1 | DDRB0 |

|        |                                                                 | Reset:          | 0     | 0         | 0      | 0           | 0           | 0     | 0     | 0     |

| \$0006 |                                                                 | Read:<br>Write: | DDRC7 | DDRC6     | DDRC5  | DDRC4       | DDRC3       | DDRC2 | DDRC1 | DDRC0 |

|        | See page 86.                                                    | Reset:          | 0     | 0         | 0      | 0           | 0           | 0     | 0     | 0     |

| \$0007 | Unimplemented                                                   |                 |       |           |        |             |             |       |       |       |

| \$0008 | Unimplemented                                                   |                 |       |           |        |             |             |       |       |       |

| \$0009 | Unimplemented                                                   |                 |       |           |        |             |             |       |       |       |

|        |                                                                 |                 |       | = Unimple | mented | U = Unaffec | ted         |       |       |       |

Figure 2-2. I/O Register Summary (Sheet 1 of 4)

MC68HC705C8A — Rev. 3

MOTOROLA

Memory For More Information On This Product, Go to: www.freescale.com

**Technical Data**

#### Resets

#### 5.3.1 Power-On Reset (POR)

A positive transition on the  $V_{DD}$  pin generates a power-on reset (POR). The POR is strictly for the power-up condition and cannot be used to detect drops in power supply voltage.

A 4064  $t_{CYC}$  (internal clock cycle) delay after the oscillator becomes active allows the clock generator to stabilize. If the RESET pin is at logic 0 at the end of 4064  $t_{CYC}$ , the MCU remains in the reset condition until the signal on the RESET pin goes to logic 1.

#### 5.3.2 External Reset

The minimum time required for the MCU to recognize a reset is 1 1/2  $t_{CYC}$ . However, to guarantee that the MCU recognizes an external reset as an external reset and not as a COP or clock monitor reset, the RESET pin must be low for eight  $t_{CYC}$ . After six  $t_{CYC}$ , the input on the RESET pin is sampled. If the pin is still low, an external reset has occurred. If the input is high, then the MCU assumes that the reset was initiated internally by either the COP watchdog timer or by the clock monitor. This method of differentiating between external and internal reset conditions assumes that the RESET pin will rise to a logic 1 less than two  $t_{CYC}$  after its release and that an externally generated reset should stay active for at least eight  $t_{CYC}$ .

#### 5.3.3 Programmable and Non-Programmable COP Watchdog Resets

A timeout of a COP watchdog generates a COP reset. A COP watchdog, once enabled, is part of a software error detection system and must be cleared periodically to start a new timeout period.

The MC68HC705C8A has two different COP watchdogs for compatibility with devices such as the MC68HC705C8 and the MC68HC05C4A:

- 1. Programmable COP watchdog reset

- 2. Non-programmable COP watchdog

One COP has four programmable timeout periods and the other has a fixed non-programmable timeout period.

Technical Data

Parallel Input/Output (I/O)

When a port B pin is programmed as an output, reading the port bit reads the value of the data latch and not the voltage on the pin itself. When a port B pin is programmed as an input, reading the port bit reads the voltage level on the pin. The data latch can always be written, regardless of the state of its DDRB bit.

| DDRB Bit | I/O Pin Mode               | Accesses to DDRB | Accesses to PORTB |                        |  |

|----------|----------------------------|------------------|-------------------|------------------------|--|

|          |                            | Read/Write       | Read              | Write                  |  |

| 0        | Input, Hi-Z <sup>(1)</sup> | DDRB7-DDRB0      | Pin               | PB7-PB0 <sup>(2)</sup> |  |

| 1        | Output                     | DDRB7-DDRB0      | PB7–PB0           | PB7–PB0                |  |

1. Hi-Z = high impedance

2. Writing affects data register but does not affect input.

**NOTE:** To avoid excessive current draw, tie all unused input pins to  $V_{DD}$  or  $V_{SS}$ , or for I/O pins change to outputs by writing to DDRB in user code as early as possible.

Technical Data

ICIE — Input Capture Interrupt Enable Bit

This read/write bit enables interrupts caused by an active signal on the TCAP pin. Reset clears the ICIE bit.

- 1 = Input capture interrupts enabled

- 0 = Input capture interrupts disabled

- OCIE Output Compare Interrupt Enable Bit

This read/write bit enables interrupts caused by an active signal on the TCMP pin. Reset clears the OCIE bit.

- 1 = Output compare interrupts enabled

- 0 = Output compare interrupts disabled

- TOIE Timer Overflow Interrupt Enable Bit

This read/write bit enables interrupts caused by a timer overflow. Reset clears the TOIE bit.

1 = Timer overflow interrupts enabled

- 0 = Timer overflow interrupts disabled

- IEDG Input Edge Bit

The state of this read/write bit determines whether a positive or negative transition on the TCAP pin triggers a transfer of the contents of the timer register to the input capture registers. Reset has no effect on the IEDG bit.

- 1 = Positive edge (low-to-high transition) triggers input capture

- 0 = Negative edge (high-to-low transition) triggers input capture

OLVL — Output Level Bit

The state of this read/write bit determines whether a logic 1 or a logic 0 appears on the TCMP pin when a successful output compare occurs. Reset clears the OLVL bit.

1 = TCMP goes high on output compare

0 = TCMP goes low on output compare

Bits 4–2 — Not used; these bits always read 0

Capture/Compare Timer

**Technical Data**

#### 10.5.2 Receiver

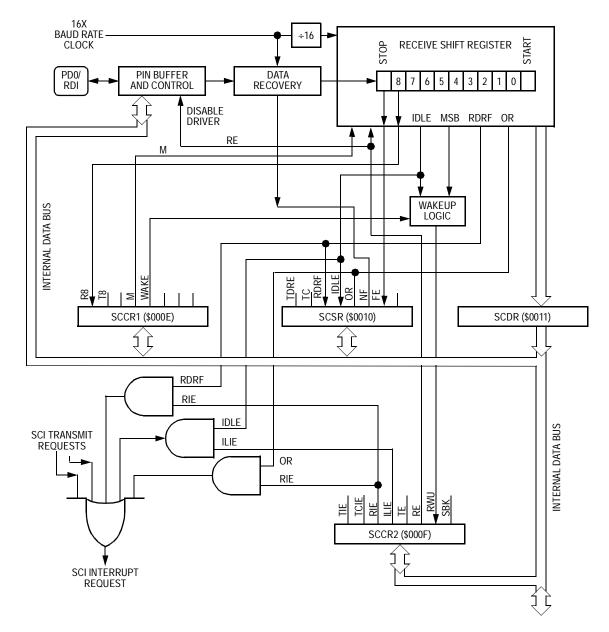

**Figure 10-4** shows the structure of the SCI receiver. Refer to **Figure 10-3** for a summary of the SCI receiver I/O registers.

#### Serial Communications Interface (SCI)

- Character Length The receiver can accommodate either 8-bit or 9-bit data. The state of the M bit in SCI control register 1 (SCCR1) determines character length. When receiving 9-bit data, bit R8 in SCCR1 is the ninth bit (bit 8).

- Character Reception During reception, the receive shift register shifts characters in from the PD0/RDI pin. The SCI data register (SCDR) is the read-only buffer between the internal data bus and the receive shift register.

After a complete character shifts into the receive shift register, the data portion of the character is transferred to the SCDR, setting the receive data register full (RDRF) flag. The RDRF flag can be used to generate an interrupt.

Receiver Wakeup — So that the MCU can ignore transmissions intended only for other receivers in multiple-receiver systems, the MCU can be put into a standby state. Setting the receiver wakeup enable (RWU) bit in SCI control register 2 (SCCR2) puts the MCU into a standby state during which receiver interrupts are disabled.

Either of two conditions on the PD0/RDI pin can bring the MCU out of the standby state:

- Idle input line condition If the PD0/RDI pin is at logic 1 long enough for 10 or 11 logic 1s to shift into the receive shift register, receiver interrupts are again enabled.

- Address mark If a logic 1 occurs in the most significant bit position of a received character, receiver interrupts are again enabled.

The state of the WAKE bit in SCCR1 determines which of the two conditions wakes up the MCU.

Receiver Noise Immunity — The data recovery logic samples each bit 16 times to identify and verify the start bit and to detect noise. Any conflict between noise detection samples sets the noise flag (NF) in the SCSR. The NF bit is set at the same time that the RDRF bit is set.

Freescale Semiconductor, Inc.

#### Serial Communications Interface (SCI)

TCIE — Transmission Complete Interrupt Enable Bit

This read/write bit enables SCI interrupt requests when the TC bit becomes set. Reset clears the TCIE bit.

- 1 = TC interrupt requests enabled

- 0 = TC interrupt requests disabled

- RIE Receive Interrupt Enable Bit

This read/write bit enables SCI interrupt requests when the RDRF bit or the OR bit becomes set. Reset clears the RIE bit.

- 1 = RDRF interrupt requests enabled

- 0 = RDRF interrupt requests disabled

- ILIE Idle Line Interrupt Enable Bit

This read/write bit enables SCI interrupt requests when the IDLE bit becomes set. Reset clears the ILIE bit.

1 = IDLE interrupt requests enabled

0 = IDLE interrupt requests disabled

TE — Transmit Enable Bit

Setting this read/write bit begins the transmission by sending a preamble of 10 or 11 logic 1s from the transmit shift register to the PD1/TDO pin. Reset clears the TE bit.

- 1 = Transmission enabled

- 0 = Transmission disabled

- RE Receive Enable Bit

Setting this read/write bit enables the receiver. Clearing the RE bit disables the receiver and receiver interrupts but does not affect the receiver interrupt flags. Reset clears the RE bit.

- 1 = Receiver enabled

- 0 = Receiver disabled

RWU — Receiver Wakeup Enable Bit

This read/write bit puts the receiver in a standby state. Typically, data transmitted to the receiver clears the RWU bit and returns the receiver to normal operation. The WAKE bit in SCCR1 determines whether an

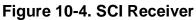

### Serial Peripheral Interface (SPI)

### 11.4 Operation

The master/slave SPI allows full-duplex, synchronous, serial communication between the microcontroller unit (MCU) and peripheral devices, including other MCUs. As the 8-bit shift register of a master SPI transmits each byte to another device, a byte from the receiving device enters the master SPI shift register. A clock signal from the master SPI synchronizes data transmission.

Only a master SPI can initiate transmissions. Software begins the transmission from a master SPI by writing to the SPI data register (SPDR). The SPDR does not buffer data being transmitted from the SPI. Data written to the SPDR goes directly into the shift register and begins the transmission immediately under the control of the serial clock. The transmission ends after eight cycles of the serial clock when the SPI flag (SPIF) becomes set. At the same time that SPIF becomes set, the data shifted into the master SPI from the receiving device transfers to the SPDR. The SPDR buffers data being received by the SPI. Before the master SPI sends the next byte, software must clear the SPIF bit by reading the SPSR and then accessing the SPDR.

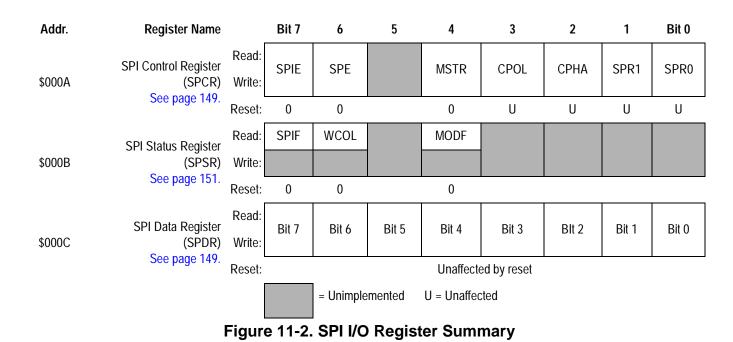

#### 11.9.3 SPI Status Register

The SPSR shown in **Figure 11-9** contains flags to signal these conditions:

- SPI transmission complete

- Write collision

- Mode fault

Address: \$000B

#### SPIF — SPI Flag

This clearable, read-only bit is set each time a byte shifts out of or into the shift register. SPIF generates an interrupt request if the SPIE bit in the SPCR is also set. Clear SPIF by reading the SPSR with SPIF set and then reading or writing the SPDR. Reset clears the SPIF bit.

- 1 = Transmission complete

- 0 = Transmission not complete

WCOL - Write Collision Bit

This clearable, read-only flag is set when software writes to the SPDR while a transmission is in progress. Clear the WCOL bit by reading the SPSR with WCOL set and then reading or writing the SPDR. Reset clears WCOL.

- 1 = Invalid write to SPDR

- 0 = No invalid write to SPDR

MC68HC705C8A — Rev. 3

Serial Peripheral Interface (SPI)

MODF — Mode Fault Bit

This clearable, read-only bit is set when a logic 0 occurs on the PD5/SS pin while the MSTR bit is set. MODF generates an interrupt request if the SPIE bit is also set. Clear the MODF bit by reading the SPSR with MODF set and then writing to the SPCR. Reset clears MODF.

$1 = PD5/\overline{SS}$  pulled low while MSTR bit set

$0 = PD5/\overline{SS}$  not pulled low while MSTR bit set

Technical Data

#### **12.4.5 Control Instructions**

These instructions act on CPU registers and control CPU operation during program execution.

| Instruction                            | Mnemonic |  |  |

|----------------------------------------|----------|--|--|

| Clear carry bit                        | CLC      |  |  |

| Clear interrupt mask                   | CLI      |  |  |

| No operation                           | NOP      |  |  |

| Reset stack pointer                    | RSP      |  |  |

| Return from interrupt                  | RTI      |  |  |

| Return from subroutine                 | RTS      |  |  |

| Set carry bit                          | SEC      |  |  |

| Set interrupt mask                     | SEI      |  |  |

| Stop oscillator and enable IRQ pin     | STOP     |  |  |

| Software interrupt                     | SWI      |  |  |

| Transfer accumulator to index register | TAX      |  |  |

| Transfer index register to accumulator | TXA      |  |  |

| Stop CPU clock and enable interrupts   | WAIT     |  |  |

Instruction Set

#### 13.3 Maximum Ratings

Maximum ratings are the extreme limits to which the MCU can be exposed without permanently damaging it.

The MCU contains circuitry to protect the inputs against damage from high static voltages; however, do not apply voltages higher than those shown in the table here. Keep V<sub>In</sub> and V<sub>Out</sub> within the range  $V_{SS} \leq (V_{In} \text{ or } V_{Out}) \leq V_{DD}$ . Connect unused inputs to the appropriate voltage level, either V<sub>SS</sub> or V<sub>DD</sub>.

| Rating <sup>(1)</sup>                                                                       | Symbol           | Value                                           | Unit |

|---------------------------------------------------------------------------------------------|------------------|-------------------------------------------------|------|

| Supply voltage                                                                              | V <sub>DD</sub>  | -0.3 to +7.0                                    | V    |

| Input voltage                                                                               | V <sub>In</sub>  | V <sub>SS</sub> –0.3<br>to V <sub>DD</sub> +0.3 | V    |

| Programming voltage                                                                         | V <sub>PP</sub>  | V <sub>DD</sub> –0.3 to<br>16.0                 |      |

| Bootstrap mode (IRQ pin only)                                                               | V <sub>In</sub>  | $V_{SS} - 0.3$<br>to 2 x $V_{DD}$ + 0.3         | V    |

| Current drain per pin excluding $V_{\mbox{\scriptsize DD}}$ and $V_{\mbox{\scriptsize SS}}$ | Ι                | 25                                              | mA   |

| Storage temperature range                                                                   | T <sub>STG</sub> | –65 to +150                                     | °C   |

1. Voltages referenced to  $\mathrm{V}_{\mathrm{SS}}$

**NOTE:** This device is not guaranteed to operate properly at the maximum ratings. Refer to **13.7 5.0-Volt DC Electrical Characteristics** and **13.8 3.3-Volt DC Electrical Characteristics** for guaranteed operating conditions.

## MC68HSC705C8A

| Diagram<br>Number <sup>(1)</sup> | Characteristic <sup>(2)</sup>                                                                         | Symbol                                   | Min       | Мах       | Unit                      |

|----------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------|-----------|-----------|---------------------------|

| 11                               | Data hold time (outputs)<br>Master (after capture edge)<br>Slave (after enable edge)                  | <sup>t</sup> HO(M)<br><sup>t</sup> HO(S) | 0.25<br>0 |           | t <sub>CYC(M)</sub><br>ns |

| 12                               | Rise time <sup>(7)</sup><br>SPI outputs (SCK, MOSI, MISO <u>)</u><br>SPI inputs (SCK, MOSI, MISO, SS) | t <sub>RM</sub><br>t <sub>RS</sub>       |           | 50<br>2.0 | ns<br>μs                  |

| 13                               | Fall time <sup>(8)</sup><br>SPI outputs (SCK, MOSI, MISO <u>)</u><br>SPI inputs (SCK, MOSI, MISO, SS) | t <sub>FM</sub><br>t <sub>FS</sub>       |           | 50<br>2.0 | ns<br>μs                  |

1. Diagram numbers refer to dimensions in Figure 13-8. SPI Master Timing and Figure 13-9. SPI Slave Timing.

2. V<sub>DD</sub> = 5 V  $\pm$  10%; V<sub>SS</sub> = 0 Vdc, T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub>, unless otherwise noted

3. Signal production depends on software.

4. Time to data active from high-impedance state

5. Hold time to high-impedance state

6. With 200 pF on all SPI pins.

7. 20% of  $V_{DD}$  to 70% of  $V_{DD}$ ;  $C_L$  = 200 pF 8. 70% of  $V_{DD}$  to 20% of  $V_{DD}$ ;  $C_L$  = 200 pF

**Technical Data**

MC68HC705C8A — Rev. 3

MC68HSC705C8A

#### For More Information On This Product, Go to: www.freescale.com

Technical Data