Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                     |

|----------------------------|---------------------------------------------------------------------|

| Product Status             | Obsolete                                                            |

| Core Processor             | HC05                                                                |

| Core Size                  | 8-Bit                                                               |

| Speed                      | 2.1MHz                                                              |

| Connectivity               | SCI, SPI                                                            |

| Peripherals                | POR, WDT                                                            |

| Number of I/O              | 24                                                                  |

| Program Memory Size        | 8KB (8K x 8)                                                        |

| Program Memory Type        | OTP                                                                 |

| EEPROM Size                | -                                                                   |

| RAM Size                   | 304 x 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                           |

| Data Converters            | -                                                                   |

| Oscillator Type            | Internal                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                   |

| Mounting Type              | Through Hole                                                        |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                            |

| Supplier Device Package    | 40-PDIP                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc705c8acpe |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

20

# Freescale Semiconductor, Inc.

## List of Tables

| Table | Title                                     | Page |

|-------|-------------------------------------------|------|

| A-1   | Programmable COP Timeout Period Selection | 202  |

| A-2   | MC68HSC705C8A Order Numbers               | 209  |

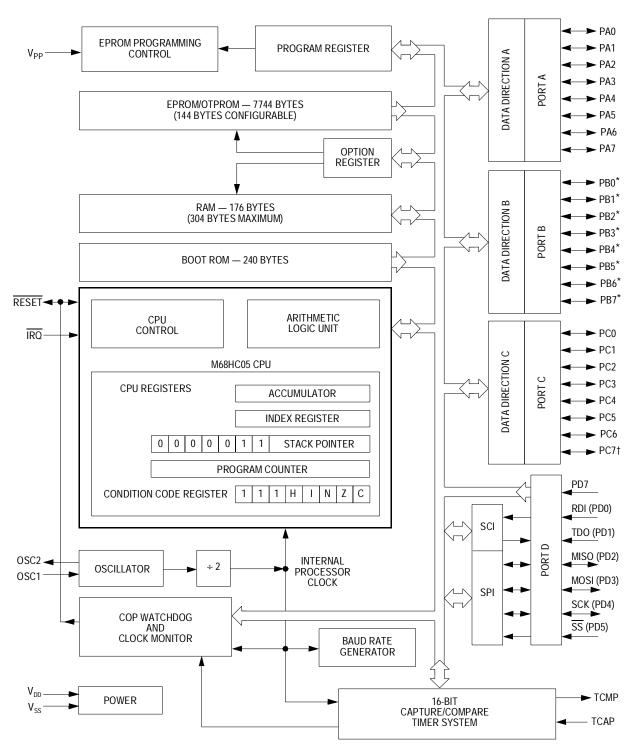

General Description Block Diagram

<sup>\*</sup> Port B pins also function as external interrupts.

Figure 1-2. MC68HC705C8A Block Diagram

MC68HC705C8A — Rev. 3

<sup>†</sup> PC7 has a high current sink and source capability.

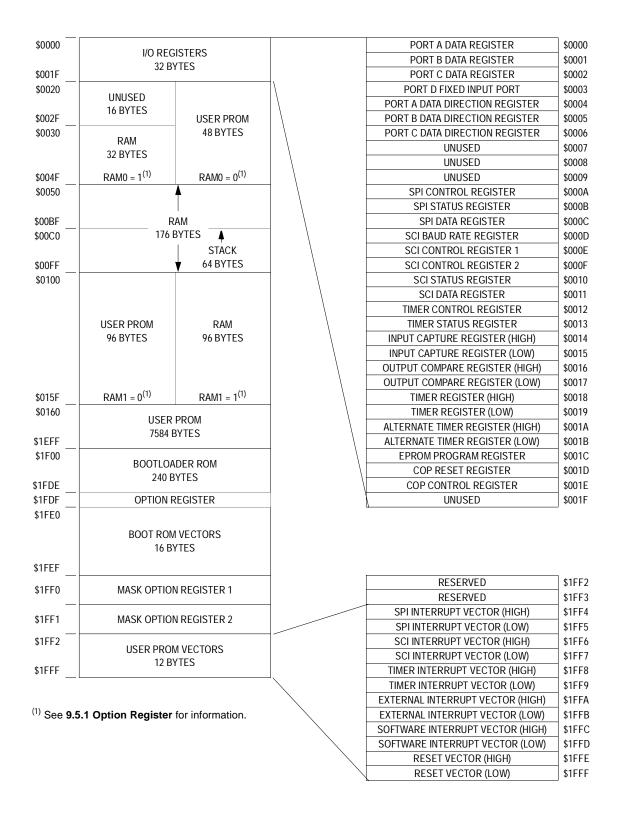

#### Memory

Figure 2-1. Memory Map

### Technical Data — MC68HC705C8A

# **Section 4. Interrupts**

### 4.1 Contents

| 4.2   | Introduction49                     |

|-------|------------------------------------|

| 4.3   | Interrupt Sources50                |

| 4.3.1 | Software Interrupt50               |

| 4.3.2 | External Interrupt (IRQ)           |

| 4.3.3 | Port B Interrupts                  |

| 4.3.4 | Capture/Compare Timer Interrupts55 |

| 4.3.5 | SCI Interrupts                     |

| 4.3.6 | SPI Interrupts                     |

| 4.4   | Interrupt Processing               |

### 4.2 Introduction

This section describes how interrupts temporarily change the normal processing sequence.

MC68HC705C8A — Rev. 3

Interrupts

Interrupt Sources

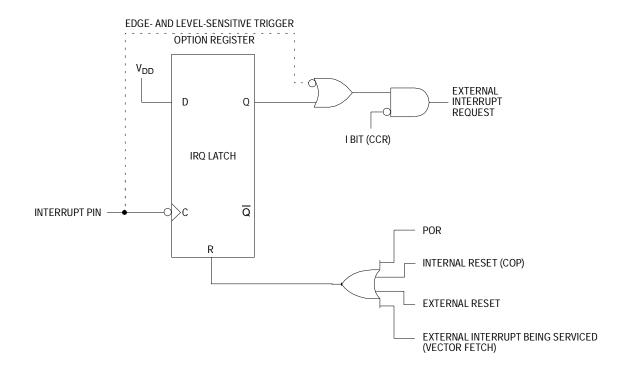

### 4.3.2 External Interrupt (IRQ)

An interrupt signal on the  $\overline{IRQ}$  pin latches an external interrupt request. After completing the current instruction, the CPU tests these bits:

- IRQ latch

- I bit in the CCR

Setting the I bit in the CCR disables external interrupts.

If the IRQ latch is set and the I bit is clear, the CPU then begins the interrupt sequence. The CPU clears the IRQ latch while it fetches the interrupt vector, so that another external interrupt request can be latched during the interrupt service routine. As soon as the I bit is cleared during the return-from-interrupt (RTI) instruction, the CPU can recognize the new interrupt request. Figure 4-1 shows the logic for external interrupts.

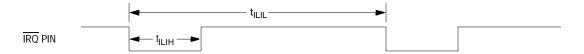

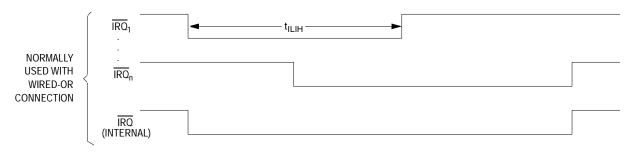

**Figure 4-1** shows an external interrupt functional diagram. **Figure 4-2** shows an external interrupt timing diagram for the interrupt line. The timing diagram illustrates two treatments of the interrupt line to the processor.

- 1. Two single pulses on the interrupt line are spaced far enough apart to be serviced. The minimum time between pulses is a function of the length of the interrupt service.

- Once a pulse occurs, the next pulse normally should not occur until an RTI occurs. This time  $(t_{ILIL})$  is obtained by adding 19 instruction cycles to the total number of cycles needed to complete the service routine (not including the RTI instruction).

- 2. Many interrupt lines are "wire-ORed" to the IRQ line. If the interrupt line remains low after servicing an interrupt, then the CPU continues to recognize an interrupt.

**NOTE:** The internal interrupt latch is cleared in the first part of the interrupt service routine. Therefore, a new external interrupt pulse could be latched and serviced as soon as the I bit is cleared.

If the  $\overline{IRQ}$  pin is not in use, connect it to the  $V_{DD}$  pin.

MC68HC705C8A — Rev. 3

52

### Interrupts

Figure 4-1. External Interrupt Internal Function Diagram

a. Edge-Sensitive Trigger Condition. The minimum pulse width  $(t_{ILIH})$  is either 125 ns  $(f_{OP} = 2.1 \text{ MHz})$  or 250 ns  $(f_{OP} = 1 \text{ MHz})$ . The period  $t_{ILIL}$  should not be less than the number of  $t_{CYC}$  cycles it takes to execute the interrupt service routine plus 19  $t_{CYC}$  cycles.

**b. Level-Sensitive Trigger Condition.** If the interrupt line remains low after servicing an interrupt, then the CPU continues to recognize an interrupt.

Figure 4-2. External Interrupt Timing

#### Technical Data — MC68HC705C8A

## Section 5. Resets

#### 5.1 Contents

| 5.2     | Introduction61                    |

|---------|-----------------------------------|

| 5.3     | Reset Sources                     |

| 5.3.1   | Power-On Reset (POR)              |

| 5.3.2   | External Reset62                  |

| 5.3.3   | Programmable and Non-Programmable |

|         | COP Watchdog Resets               |

| 5.3.3.  | Programmable COP Watchdog Reset   |

| 5.3.3.2 | Non-Programmable COP Watchdog     |

| 5.3.4   | Clock Monitor Reset               |

#### 5.2 Introduction

This section describes how resets initialize the microcontroller unit (MCU).

#### 5.3 Reset Sources

A reset immediately stops the operation of the instruction being executed, initializes certain control bits, and loads the program counter with a user-defined reset vector address. These conditions produce a reset:

- Power-on reset (POR) Initial power-up

- External reset A logic 0 applied to the RESET pin

- Internal programmable computer operating properly (COP) watchdog timer reset

- Internal non-programmable COP watchdog timer reset

- Internal clock monitor reset

MC68HC705C8A — Rev. 3

Resets

Address: \$001D Bit 7 6 5 4 3 2 1 Bit 0 Read: Write: Bit 7 6 5 4 3 2 1 Bit 0 IJ U IJ Reset: U U = Unimplemented U = Unaffected

Figure 5-2. Programmable COP Reset Register (COPRST)

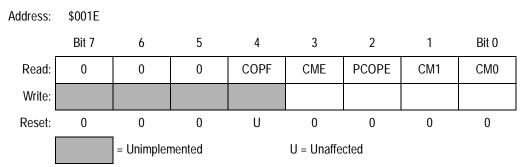

The programmable COP control register (COPCR) shown in **Figure 5-3** does these functions:

- Flags programmable COP watchdog resets

- Enables the clock monitor

- Enables the programmable COP watchdog

- Controls the timeout period of the programmable COP watchdog

Figure 5-3. Programmable COP Control Register (COPCR)

COPF — COP Flag

This read-only bit is set when a timeout of the programmable COP watchdog occurs or when the clock monitor detects a slow or absent internal clock. Clear the COPF bit by reading the COP control register. Reset has no effect on the COPF bit.

- 1 = COP timeout or internal clock failure

- 0 = No COP timeout and no internal clock failure

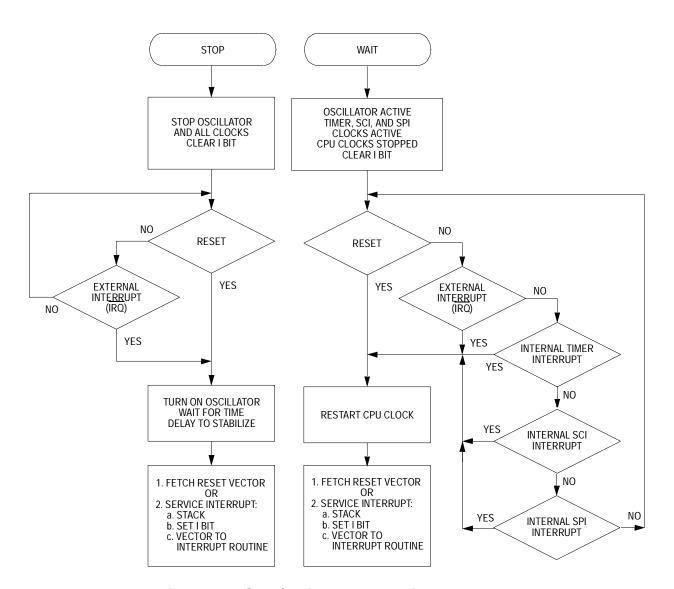

## Low-Power Modes

Figure 6-1. Stop/Wait Mode Function Flowchart

During stop mode, the I bit in the condition code register (CCR) is cleared to enable external interrupts. All other registers and memory remain unaltered. All input/output (I/O) lines remain unchanged. The processor can be brought out of stop mode only by an external interrupt or reset.

### Parallel Input/Output (I/O)

#### **7.6 Port D**

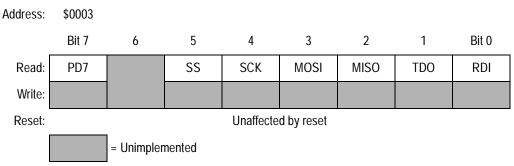

Port D is a 7-bit, special-purpose, input-only port that has no data register. Reading address \$0003 returns the logic states of the port D pins.

Port D shares pins PD5–PD2 with the serial peripheral interface module (SPI). When the SPI is enabled, PD5–PD2 read as logic 0s. When the SPI is disabled, reading address \$0003 returns the logic states of the PD5–PD2 pins.

Port D shares pins PD1 and PD0 with the SCI module. When the SCI is enabled, PD1 and PD0 read as logic 0s. When the SCI is disabled, reading address \$0003 returns the logic states of the PD1 and PD0 pins.

Figure 7-10. Port D Fixed Input Register (PORTD)

### Technical Data — MC68HC705C8A

# Section 9. EPROM/OTPROM (PROM)

#### 9.1 Contents

| 9.2                   | Introduction                                                                    |

|-----------------------|---------------------------------------------------------------------------------|

| 9.3<br>9.3.1<br>9.3.2 | EPROM/OTPROM (PROM) Programming.104Program Register.109Preprogramming Steps.110 |

| 9.4                   | PROM Programming Routines                                                       |

| 9.4.1                 | Program and Verify PROM111                                                      |

| 9.4.2                 | Verify PROM Contents112                                                         |

| 9.4.3                 | Secure PROM112                                                                  |

| 9.4.4                 | Secure PROM and Verify113                                                       |

| 9.4.5                 | Secure PROM and Dump113                                                         |

| 9.4.6                 | Load Program into RAM and Execute                                               |

| 9.4.7                 | Execute Program in RAM115                                                       |

| 9.4.8                 | Dump PROM Contents115                                                           |

| 9.5                   | Control Registers                                                               |

| 9.5.1                 | Option Register                                                                 |

| 9.5.2                 | Mask Option Register 1                                                          |

| 9.5.3                 | Mask Option Register 2                                                          |

| 9.6                   | EPROM Erasing                                                                   |

### 9.2 Introduction

This section describes erasable, programmable read-only memory/one-time programmable read-only memory (EPROM/OTPROM (PROM)) programming.

MC68HC705C8A — Rev. 3

EPROM/OTPROM (PROM)

EPROM/OTPROM (PROM) Programming

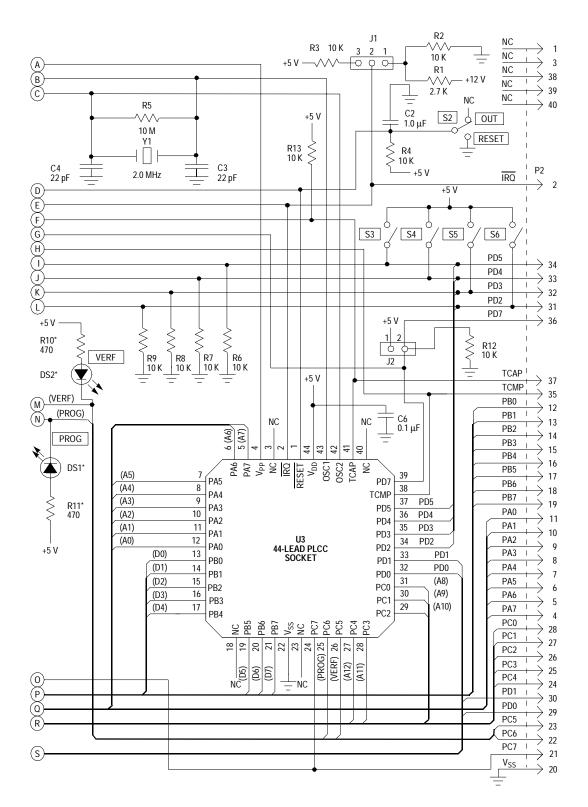

Figure 9-2. PROM Programming Circuit (Continued)

MC68HC705C8A — Rev. 3

EPROM/OTPROM (PROM)

EPROM/OTPROM (PROM) Programming

#### 9.3.1 Program Register

The program register (PROG) shown in **Figure 9-3** is used for PROM programming.

Address: \$001C Bit 7 6 5 4 3 2 1 Bit 0 Read: 0 0 0 0 0 LAT 0 **PGM** Write: 0 0 Reset: 0 0 0 0

Figure 9-3. Program Register (PROG)

#### LAT — Latch Enable Bit

This bit is both readable and writable.

- 1 = Enables PROM data and address bus latches for programming on the next byte write cycle

- 0 = Latch disabled. PROM data and address buses are unlatched for normal CPU operations.

#### PGM — Program Bit

If LAT is cleared, PGM cannot be set.

1 = Enables V<sub>PP</sub> power to the PROM for programming

$0 = V_{PP}$  is disabled.

Bits 1 and 3–7 — Not used; always read 0

EPROM/OTPROM (PROM)

### Serial Communications Interface (SCI)

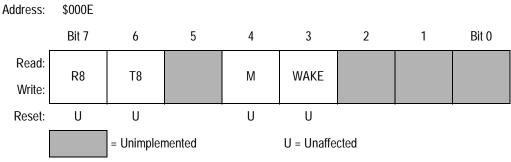

#### 10.6.2 SCI Control Register 1

SCI control register 1 (SCCR1) shown in **Figure 10-6** has these functions:

- Stores ninth SCI data bit received and ninth SCI data bit transmitted

- Controls SCI character length

- · Controls SCI wakeup method

Figure 10-6. SCI Control Register 1 (SCCR1)

#### R8 — Bit 8 (Received)

When the SCI is receiving 9-bit characters, R8 is the ninth bit of the received character. R8 receives the ninth bit at the same time that the SCDR receives the other eight bits. Reset has no effect on the R8 bit.

#### T8 — Bit 8 (Transmitted)

When the SCI is transmitting 9-bit characters, T8 is the ninth bit of the transmitted character. T8 is loaded into the transmit shift register at the same time that SCDR is loaded into the transmit shift register. Reset has no effect on the T8 bit.

#### M — Character Length Bit

This read/write bit determines whether SCI characters are eight or nine bits long. The ninth bit can be used as an extra stop bit, as a receiver wakeup signal, or as a mark or space parity bit. Reset has no effect on the M bit.

1 = 9-bit SCI characters

0 = 8-bit SCI characters

Serial Peripheral Interface (SPI)

Operation

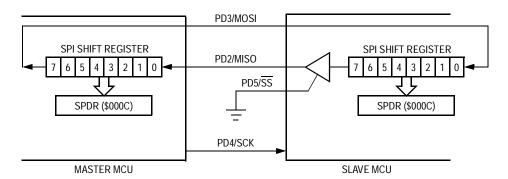

In a slave SPI, data enters the shift register under the control of the serial clock from the master SPI. After a byte enters the shift register of a slave SPI, it transfers to the SPDR. To prevent an overrun condition, slave software must then read the byte in the SPDR before another byte enters the shift register and is ready to transfer to the SPDR.

Figure 11-3 shows how a master SPI exchanges data with a slave SPI.

Figure 11-3. Master/Slave Connections

#### 11.4.1 Pin Functions in Master Mode

Setting the MSTR bit in the SPI control register (SPCR) configures the SPI for operation in master mode. The master-mode functions of the SPI pins are:

- PD4/SCK (serial clock) In master mode, the PD4/SCK pin is the synchronizing clock output.

- PD3/MOSI (master output, slave input) In master mode, the PD3/MOSI pin is the serial output.

- PD2/MISO (master input, slave output) In master mode, the PD2/MISO pin is configured as the serial input.

- PD5/SS (slave select) In master mode, the PD5/SS pin protects against driver contention caused by the simultaneous operation of two SPIs in master mode. A logic 0 on the PD5/SS pin of a master SPI disables the SPI, clears the MSTR bit, and sets the mode-fault flag (MODF).

MC68HC705C8A — Rev. 3

Electrical Specifications 5.0-Volt Serial Peripheral Interface (SPI) Timing

### 13.11 5.0-Volt Serial Peripheral Interface (SPI) Timing

| Number <sup>(1)</sup> | Characteristic <sup>(2)</sup>                                                               | Symbol                                     | Min        | Max        | Unit                   |

|-----------------------|---------------------------------------------------------------------------------------------|--------------------------------------------|------------|------------|------------------------|

|                       | Operating frequency<br>Master<br>Slave                                                      | f <sub>OP(M)</sub><br>f <sub>OP(S)</sub>   | dc<br>dc   | 0.5<br>2.1 | f <sub>OP</sub><br>MHz |

| 1                     | Cycle time<br>Master<br>Slave                                                               | tcyc(M) tcyc(S)                            | 2.0<br>480 |            | t <sub>CYC</sub>       |

| 2                     | Enable lead time<br>Master<br>Slave                                                         | t <sub>Lead(M)</sub> t <sub>Lead(S)</sub>  | (3)<br>240 | _          | ns                     |

| 3                     | Enable lag time<br>Master<br>Slave                                                          | t <sub>Lag(M)</sub><br>t <sub>Lag(S)</sub> | (2)<br>720 | _          | ns                     |

| 4                     | Clock (SCK) high time<br>Master<br>Slave                                                    | t <sub>W</sub> (SCKH)M                     | 340<br>190 |            | ns                     |

| 5                     | Clock (SCK) low time<br>Master<br>Slave                                                     | tw(sckl)m                                  | 340<br>190 | _          | ns                     |

| 6                     | Data setup time (inputs) Master Slave                                                       | t <sub>SU(M)</sub>                         | 100<br>100 |            | ns                     |

| 7                     | Data hold time (inputs) Master Slave                                                        | t <sub>H(M)</sub>                          | 100<br>100 |            | ns                     |

| 8                     | Access time <sup>(4)</sup> Slave                                                            | t <sub>A</sub>                             | 0          | 120        | ns                     |

| 9                     | Disable time <sup>(5)</sup> Slave                                                           | t <sub>DIS</sub>                           | _          | 240        | ns                     |

| 10                    | Data valid time<br>Master (before capture edge)<br>Slave (after enable edge) <sup>(6)</sup> | t <sub>V(M)</sub>                          | 0.25<br>—  | <br>240    | t <sub>CYC(M)</sub>    |

Continued

MC68HC705C8A — Rev. 3

Technical Data

**Electrical Specifications**

### MC68HSC705C8A

| Diagram<br>Number <sup>(1)</sup> | Characteristic <sup>(2)</sup>                                                           | Symbol             | Min       | Max       | Unit                |

|----------------------------------|-----------------------------------------------------------------------------------------|--------------------|-----------|-----------|---------------------|

| 11                               | Data hold time (outputs)  Master (after capture edge)  Slave (after enable edge)        | t <sub>HO(M)</sub> | 0.25<br>0 |           | t <sub>CYC(M)</sub> |

| 12                               | Rise time <sup>(7)</sup> SPI outputs (SCK, MOSI, MISO) SPI inputs (SCK, MOSI, MISO, SS) | t <sub>RM</sub>    |           | 50<br>2.0 | ns<br>μs            |

| 13                               | Fall time <sup>(8)</sup> SPI outputs (SCK, MOSI, MISO) SPI inputs (SCK, MOSI, MISO, SS) | t <sub>FM</sub>    | _<br>_    | 50<br>2.0 | ns<br>μs            |

- 1. Diagram numbers refer to dimensions in Figure 13-8. SPI Master Timing and Figure 13-9. SPI Slave Timing.

- 2.  $V_{DD}$  = 5 V  $\pm$  10%;  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted

- 3. Signal production depends on software.

- 4. Time to data active from high-impedance state

- 5. Hold time to high-impedance state

- 6. With 200 pF on all SPI pins.

- 7. 20% of  $V_{DD}$  to 70% of  $V_{DD}$ ;  $C_L$  = 200 pF 8. 70% of  $V_{DD}$  to 20% of  $V_{DD}$ ;  $C_L$  = 200 pF

### MC68HSC705C8A

| Diagram<br>Number <sup>(1)</sup> | Characteristic <sup>(2)</sup>                                                           | Symbol                             | Min       | Max        | Unit                |

|----------------------------------|-----------------------------------------------------------------------------------------|------------------------------------|-----------|------------|---------------------|

| 11                               | Data hold time (outputs)  Master (after capture edge)  Slave (after enable edge)        | t <sub>HO(M)</sub>                 | 0.25<br>0 |            | t <sub>CYC(M)</sub> |

| 12                               | Rise time <sup>(7)</sup> SPI outputs (SCK, MOSI, MISO) SPI inputs (SCK, MOSI, MISO, SS) | t <sub>RM</sub><br>t <sub>RS</sub> | _         | 100<br>2.0 | ns<br>μs            |

| 13                               | Fall time <sup>(8)</sup> SPI outputs (SCK, MOSI, MISO) SPI inputs (SCK, MOSI, MISO, SS) | t <sub>FM</sub><br>t <sub>FS</sub> | _<br>_    | 100<br>2.0 | ns<br>µs            |

- 1. Diagram numbers refer to dimensions in Figure 13-8. SPI Master Timing and Figure 13-9. SPI Slave Timing.

- 2.  $V_{DD}$  = 3.3 V  $\pm$  10%;  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted

- 3. Signal production depends on software.

- 4. Time to data active from high-impedance state

- 5. Hold time to high-impedance state

- 6. With 200 pF on all SPI pins

- 7. 20% of  $V_{DD}$  to 70% of  $V_{DD}$ ;  $C_L$  = 200 pF 8. 70% of  $V_{DD}$  to 20% of  $V_{DD}$ ;  $C_L$  = 200 pF

MC68HC705C8A/D