Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | HC05                                                         |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 4MHz                                                         |

| Connectivity               | SCI, SPI                                                     |

| Peripherals                | POR, WDT                                                     |

| Number of I/O              | 24                                                           |

| Program Memory Size        | 8KB (8K x 8)                                                 |

| Program Memory Type        | OTP                                                          |

| EEPROM Size                | -                                                            |

| RAM Size                   | 304 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                    |

| Data Converters            | -                                                            |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 44-QFP                                                       |

| Supplier Device Package    | 44-QFP (10x10)                                               |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mchsc705c8acfbe |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **1.7 Pin Functions**

This subsection describes the MC68HC705C8A signals. Reference is made, where applicable, to other sections that contain more detail about the function being performed.

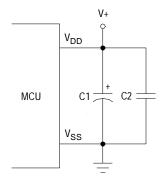

### 1.7.1 $V_{DD}$ and $V_{SS}$

$V_{\text{DD}}$  and  $V_{\text{SS}}$  are the power supply and ground pins. The MCU operates from a single power supply.

Very fast signal transitions occur on the MCU pins, placing high short-duration current demands on the power supply. To prevent noise problems, take special care to provide good power supply bypassing at the MCU. Place bypass capacitors as close to the MCU as possible, as shown in **Figure 1-7**.

Figure 1-7. Bypassing Layout Recommendation

## 1.7.2 V<sub>PP</sub>

This pin provides the programming voltage to the EPROM array. For normal operation,  $V_{PP}$  shuld be tied to  $V_{DD}$ .

**NOTE:** Connecting the  $V_{PP}$  pin (programming voltage) to  $V_{SS}$  (ground) could result in damage to the MCU.

subroutine call to save the CPU state. The stack pointer decrements during pushes and increments during pulls.

**Figure 2-1** is a memory map of the MCU. Addresses \$0000–\$001F, shown in **Figure 2-2**, contain most of the control, status, and data registers. Additional I/O registers have these addresses:

- \$1FDF, option register

- \$1FF0, mask option register 1 (MOR1)

- \$1FF1, mask option register 2 (MOR2)

## 2.4 Input/Output (I/O)

The first 32 addresses of memory space, from \$0000 to \$001F, are the I/O section. These are the addresses of the I/O control registers, status registers, and data registers. See Figure 2-2 for more information.

## 2.5 RAM

One of four selectable memory configurations is selected by the state of the RAM1 and RAM0 bits in the option register located at \$1FDF. Reset or power-on reset (POR) clears these bits, automatically selecting the first memory configuration as shown in Table 2-1. See 9.5.1 Option Register.

|      |      | · ) · · · J· |            |

|------|------|--------------|------------|

| RAM0 | RAM1 | RAM Bytes    | PROM Bytes |

| 0    | 0    | 176          | 7744       |

| 1    | 0    | 208          | 7696       |

| 0    | 1    | 272          | 7648       |

304

Table 2-1. Memory Configurations

**NOTE:** Be careful when using nested subroutines or multiple interrupt levels. The CPU can overwrite data in the stack RAM during a subroutine or during the interrupt stacking operation.

1

**Technical Data**

MC68HC705C8A — Rev. 3

7600

1

Interrupts

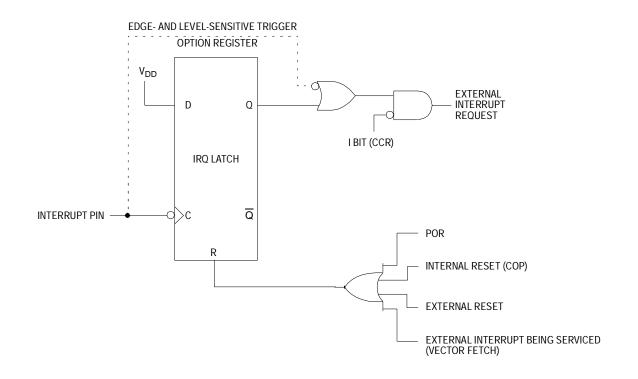

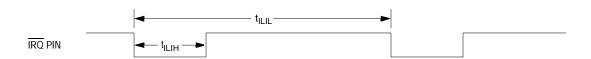

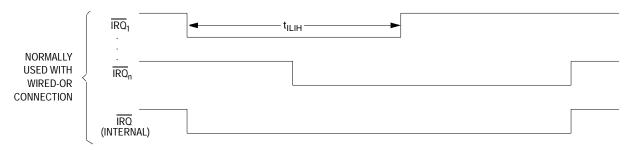

a. Edge-Sensitive Trigger Condition. The minimum pulse width ( $t_{ILIH}$ ) is either 125 ns ( $f_{OP}$  = 2.1 MHz) or 250 ns (for = 1 MHz). The period t<sub>ILIL</sub> should not be less than the number of t<sub>CYC</sub> cycles it takes to execute the interrupt service routine plus 19 t<sub>CYC</sub> cycles.

b. Level-Sensitive Trigger Condition. If the interrupt line remains low after servicing an interrupt, then the CPU continues to recognize an interrupt.

**Technical Data**

#### 4.3.4 Capture/Compare Timer Interrupts

Setting the I bit in the CCR disables all interrupts except for SWI.

#### 4.3.5 SCI Interrupts

The serial communications interface (SCI) can generate these interrupts:

- Transmit data register empty interrupt

- Transmission complete interrupt

- Receive data register full interrupt

- Receiver overrun interrupt

- Receiver input idle interrupt

Setting the I bit in the CCR disables all SCI interrupts.

- SCI Transmit Data Register Empty Interrupt The transmit data register empty bit (TDRE) indicates that the SCI data register is ready to receive a byte for transmission. TDRE becomes set when data in the SCI data register transfers to the transmit shift register. TDRE generates an interrupt request if the transmit interrupt enable bit (TIE) is set also.

- SCI Transmission Complete Interrupt The transmission complete bit (TC) indicates the completion of an SCI transmission. TC becomes set when the TDRE bit becomes set and no data, preamble, or break character is being transmitted. TC generates an interrupt request if the transmission complete interrupt enable bit (TCIE) is set also.

- SCI Receive Data Register Full Interrupt The receive data register full bit (RDRF) indicates that a byte is ready to be read in the SCI data register. RDRF becomes set when the data in the receive shift register transfers to the SCI data register. RDRF generates an interrupt request if the receive interrupt enable bit (RIE) is set also.

Semiconductor, Inc

reescale

#### Freescale Semiconductor, Inc.

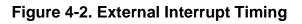

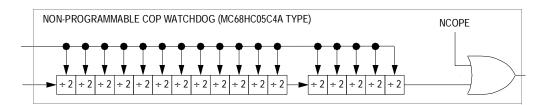

#### 5.3.3.1 Programmable COP Watchdog Reset

A timeout of the 18-stage ripple counter in the programmable COP watchdog generates a reset. **Figure 5-1** is a diagram of the programmable COP watchdog. Two registers control and monitor operation of the programmable COP watchdog:

- COP reset register (COPRST), \$001D

- COP control register (COPCR), \$001E

To clear the programmable COP watchdog and begin a new timeout period, write these values to the COP reset register (COPRST). See Figure 5-2.

- 1. \$55

- 2. \$AA

The \$55 write must precede the \$AA write. Instructions may be executed between the write operations provided that the COP watchdog does not time out before the second write.

Figure 5-1. Programmable COP Watchdog Diagram

2. COP clear bit (COPC) at address \$1FF0

To clear the non-programmable COP watchdog and start a new COP timeout period, write a logic 0 to bit 0 of address \$1FF0. Reading address \$1FF0 returns the mask option register 1 (MOR1) data at that location. See **9.5.2 Mask Option Register 1**.

**NOTE:** The non-programmable watchdog COP is disabled in bootloader mode, even if the NCOPE bit is programmed.

Figure 5-4 is a diagram of the non-programmable COP.

#### 5.3.4 Clock Monitor Reset

When the CME bit in the COP control register is set, the clock monitor detects the absence of the internal bus clock for a certain period of time. The timeout period depends on processing parameters and varies from 5  $\mu$ s to 100  $\mu$ s, which implies that systems using a bus clock rate of 200 kHz or less should not use the clock monitor function.

If a slow or absent clock is detected, the clock monitor causes a system reset. The reset is issued to the external system for four bus cycles using the bidirectional  $\overrightarrow{\text{RESET}}$  pin.

Special consideration is required when using the STOP instruction with the clock monitor. Since STOP causes the system clocks to halt, the clock monitor issues a system reset when STOP is executed.

**Technical Data**

The clock monitor is a useful backup to the COP watchdog system. Because the watchdog timer requires a clock to function, it cannot indicate a system clock failure. The clock monitor would detect such a condition and force the MCU to a reset state. Clocks are not required for the MCU to reach a reset condition. They are, however, required to bring the MCU through the reset sequence and back to run condition.

Technical Data

# Section 7. Parallel Input/Output (I/O)

## 7.1 Contents

| 7.2   | Introduction                |

|-------|-----------------------------|

| 7.3   | Port A                      |

| 7.3.1 | Port A Data Register78      |

| 7.3.2 | Data Direction Register A79 |

| 7.3.3 | Port A Logic                |

| 7.4   | Port B                      |

| 7.4.1 | Port B Data Register81      |

| 7.4.2 | Data Direction Register B82 |

| 7.4.3 | Port B Logic                |

| 7.5   | Port C                      |

| 7.5.1 | Port C Data Register85      |

| 7.5.2 | Data Direction Register C86 |

| 7.5.3 | Port C Logic                |

| 7.6   | Port D                      |

#### 7.2 Introduction

This section describes the programming of ports A, B, C, and D.

#### 7.6 Port D

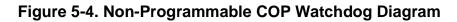

Port D is a 7-bit, special-purpose, input-only port that has no data register. Reading address \$0003 returns the logic states of the port D pins.

Port D shares pins PD5–PD2 with the serial peripheral interface module (SPI). When the SPI is enabled, PD5–PD2 read as logic 0s. When the SPI is disabled, reading address \$0003 returns the logic states of the PD5–PD2 pins.

Port D shares pins PD1 and PD0 with the SCI module. When the SCI is enabled, PD1 and PD0 read as logic 0s. When the SCI is disabled, reading address \$0003 returns the logic states of the PD1 and PD0 pins.

Figure 7-10. Port D Fixed Input Register (PORTD)

Technical Data

# Section 8. Capture/Compare Timer

### 8.1 Contents

| 8.2   | Introduction                |

|-------|-----------------------------|

| 8.3   | Timer Operation             |

| 8.3.1 | Input Capture               |

| 8.3.2 | Output Compare93            |

| 8.4   | Timer I/O Registers         |

| 8.4.1 | Timer Control Register94    |

| 8.4.2 | Timer Status Register96     |

| 8.4.3 | Timer Registers97           |

| 8.4.4 | Alternate Timer Registers   |

| 8.4.5 | Input Capture Registers100  |

| 8.4.6 | Output Compare Registers101 |

|       |                             |

## 8.2 Introduction

This section describes the operation of the 16-bit capture/compare timer. **Figure 8-1** shows the structure of the timer module. **Figure 8-2** is a summary of the timer input/output (I/O) registers.

## 8.3 Timer Operation

The core of the capture/compare timer is a 16-bit free-running counter. The counter is the timing reference for the input capture and output compare functions. The input capture and output compare functions can latch the times at which external events occur, measure input waveforms, and generate output waveforms and timing delays. Software can read the value in the counter at any time without affecting the counter sequence.

MC68HC705C8A — Rev. 3

Technical Data

**Capture/Compare Timer**

#### 8.4 Timer I/O Registers

These registers control and monitor the timer operation:

- Timer control register (TCR)

- Timer status register (TSR)

- Timer registers (TRH and TRL)

- Alternate timer registers (ATRH and ATRL)

- Input capture registers (ICRH and ICRL)

- Output compare registers (OCRH and OCRL)

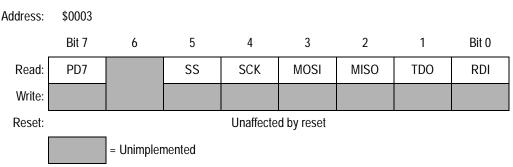

#### 8.4.1 Timer Control Register

The timer control register (TCR) as shown in **Figure 8-5** performs these functions:

- Enables input capture interrupts

- Enables output compare interrupts

- Enables timer overflow interrupts

- Controls the active edge polarity of the TCAP signal

- Controls the active level of the TCMP output

#### Address: \$0012

U = Unaffected

## Figure 8-5. Timer Control Register (TCR)

EPROM/OTPROM (PROM)

**Technical Data**

#### Example:

| LDA | #\$1C | ; MSTR = 1, CPOL = 1, CPHA = 1,          |

|-----|-------|------------------------------------------|

|     |       | ; SPR1 = SPR0 = 0                        |

| STA | SPCR  | ; SPI control register                   |

| LDA | #\$4C | ; MSTR = 0, SPE = 1, CPOL = 1, CPHA = 1, |

|     |       | ; SPR1 = SPR0 = 0                        |

| STA | SPCR  | ; SPI control register                   |

#### 11.5 Multiple-SPI Systems

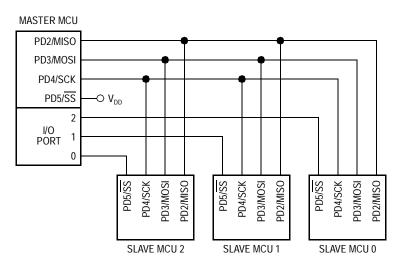

In a multiple-SPI system, all PD4/SCK pins are connected together, all PD3/MOSI pins are connected together, and all PD2/MISO pins are connected together.

Before a transmission, one SPI is configured as master and the rest are configured as slaves. Figure 11-4 is a block diagram showing a single master SPI and three slave SPIs.

**Figure 11-5** is another block diagram with two master/slave SPIs and three slave SPIs.

# Section 12. Instruction Set

## 12.1 Contents

| 12.2 Introduction                     | 154 |

|---------------------------------------|-----|

| 12.3 Addressing Modes                 |     |

| 12.3.1 Inherent                       | 155 |

| 12.3.2 Immediate                      | 155 |

| 12.3.3 Direct                         | 155 |

| 12.3.4 Extended                       | 155 |

| 12.3.5 Indexed, No Offset             |     |

| 12.3.6 Indexed, 8-Bit Offset          |     |

| 12.3.7 Indexed, 16-Bit Offset         | 156 |

| 12.3.8 Relative                       |     |

| 12.4 Instruction Types                |     |

| 12.4.1 Register/Memory Instructions   | 158 |

| 12.4.2 Read-Modify-Write Instructions | 159 |

| 12.4.3 Jump/Branch Instructions       |     |

| 12.4.4 Bit Manipulation Instructions  |     |

| 12.4.5 Control Instructions           |     |

| 12.5 Instruction Set Summary          | 164 |

| 12.6 Opcode Map                       |     |

| Source                                                             | Operation                             | Description                                                                                                                                                                    | I |   | ffect on<br>CCR |   |   | Address<br>Mode                                                                                                      |                                  | Operand                                                                       | Cvcles                                              |

|--------------------------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|-----------------|---|---|----------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------|

| Form                                                               |                                       |                                                                                                                                                                                | Н | I | Ν               | Z | С | Add                                                                                                                  | Opcode                           | Ope                                                                           | Š                                                   |

| BIH rel                                                            | Branch if IRQ Pin High                | $PC \leftarrow (PC) + 2 + rel ? IRQ = 1$                                                                                                                                       | — | — | —               | — | — | REL                                                                                                                  | 2F                               | rr                                                                            | 3                                                   |

| BIL rel                                                            | Branch if IRQ Pin Low                 | $PC \leftarrow (PC) + 2 + rel ? IRQ = 0$                                                                                                                                       |   |   | —               | — | — | REL                                                                                                                  | 2E                               | rr                                                                            | 3                                                   |

| BIT #opr<br>BIT opr<br>BIT opr<br>BIT opr,X<br>BIT opr,X<br>BIT ,X | Bit Test Accumulator with Memory Byte | (A) ∧ (M)                                                                                                                                                                      |   |   | ţ               | ţ |   | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX                                                                                | A5<br>B5<br>C5<br>D5<br>E5<br>F5 | ii<br>dd<br>hh II<br>ee ff<br>ff                                              | 2<br>3<br>4<br>5<br>4<br>3                          |

| BLO rel                                                            | Branch if Lower (Same as BCS)         | PC ← (PC) + 2 + <i>rel</i> ? C = 1                                                                                                                                             | — | — | —               | — | — | REL                                                                                                                  | 25                               | rr                                                                            | 3                                                   |

| BLS rel                                                            | Branch if Lower or Same               | $PC \leftarrow (PC) + 2 + \mathit{rel} ? C \lor Z = 1$                                                                                                                         | — | — | —               |   | — | REL                                                                                                                  | 23                               | rr                                                                            | 3                                                   |

| BMC rel                                                            | Branch if Interrupt Mask Clear        | $PC \leftarrow (PC) + 2 + \mathit{rel} ? I = 0$                                                                                                                                | — | — | —               |   |   | REL                                                                                                                  | 2C                               | rr                                                                            | 3                                                   |

| BMI rel                                                            | Branch if Minus                       | PC ← (PC) + 2 + <i>rel</i> ? N = 1                                                                                                                                             | — | — | —               |   |   | REL                                                                                                                  | 2B                               | rr                                                                            | 3                                                   |

| BMS rel                                                            | Branch if Interrupt Mask Set          | PC ← (PC) + 2 + <i>rel</i> ? I = 1                                                                                                                                             |   | — | —               | — |   | REL                                                                                                                  | 2D                               | rr                                                                            | 3                                                   |

| BNE rel                                                            | Branch if Not Equal                   | $PC \leftarrow (PC) + 2 + \mathit{rel} ? Z = 0$                                                                                                                                | — | — | —               | — | — | REL                                                                                                                  | 26                               | rr                                                                            | 3                                                   |

| BPL rel                                                            | Branch if Plus                        | $PC \leftarrow (PC) + 2 + \mathit{rel} ? N = 0$                                                                                                                                | — | — | —               | — | — | REL                                                                                                                  | 2A                               | rr                                                                            | 3                                                   |

| BRA rel                                                            | Branch Always                         | PC ← (PC) + 2 + <i>rel</i> ? 1 = 1                                                                                                                                             | — | — | —               | — | — | REL                                                                                                                  | 20                               | rr                                                                            | 3                                                   |

| BRCLR n opr rel                                                    | Branch if Bit n Clear                 | PC ← (PC) + 2 + <i>rel</i> ? Mn = 0                                                                                                                                            |   |   |                 |   | ţ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7)             | 03<br>05<br>07<br>09<br>0B<br>0D | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 5<br>5<br>5<br>5<br>5<br>5<br>5                     |

| BRN rel                                                            | Branch Never                          | $PC \leftarrow (PC) + 2 + \mathit{rel} ? 1 = 0$                                                                                                                                | — | — | —               | — | — | REL                                                                                                                  | 21                               | rr                                                                            | 3                                                   |

| BRSET n opr rel                                                    | Branch if Bit n Set                   | PC ← (PC) + 2 + <i>rel</i> ? Mn = 1                                                                                                                                            |   |   |                 |   | ţ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7)             | 02<br>04<br>06<br>08<br>0A<br>0C | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr          | 5<br>5<br>5<br>5<br>5<br>5<br>5                     |

| BSET n opr                                                         | Set Bit n                             | Mn ← 1                                                                                                                                                                         |   |   |                 |   |   | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 12<br>14<br>16<br>18<br>1A<br>1C | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd                                  | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 |

| BSR rel                                                            | Branch to Subroutine                  | $\begin{array}{c} PC \leftarrow (PC) + 2;  push \; (PCL) \\ SP \leftarrow (SP) - 1;  push \; (PCH) \\ SP \leftarrow (SP) - 1 \\ PC \leftarrow (PC) + \mathit{rel} \end{array}$ | _ | _ | _               |   |   | REL                                                                                                                  | AD                               | rr                                                                            | 6                                                   |

| CLC                                                                | Clear Carry Bit                       | $C \leftarrow 0$                                                                                                                                                               | — | — | —               |   | 0 | INH                                                                                                                  | 98                               |                                                                               | 2                                                   |

| CLI                                                                | Clear Interrupt Mask                  | l ← 0                                                                                                                                                                          | — | 0 | —               |   | — | INH                                                                                                                  | 9A                               |                                                                               | 2                                                   |

#### Table 12-6. Instruction Set Summary (Sheet 2 of 6)

MC68HC705C8A — Rev. 3

**Technical Data**

## 13.7 5.0-Volt DC Electrical Characteristics

| Characteristic <sup>(1)</sup>                                                                                                                                                                                                                       | Symbol                              | Min                       | Typ <sup>(2)</sup> | Max                   | Unit       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------------|--------------------|-----------------------|------------|

| Output voltage, $I_{Load} \le 10.0 \ \mu A$                                                                                                                                                                                                         | V <sub>OL</sub><br>V <sub>OH</sub>  | <br>V <sub>DD</sub> – 0.1 |                    | 0.1                   | V          |

| Output high voltage<br>$I_{Load} = -0.8 \text{ mA}, \text{PA7-PA0}, \text{PB7-PB0}, \text{PC6-PC0}, \text{TCMP}$<br>(see Figure 13-2)<br>$I_{Load} = -1.6 \text{ mA}, \text{PD4-PD1}$ (see Figure 13-3)<br>$I_{Load} = -5.0 \text{ mA}, \text{PC7}$ | V <sub>OH</sub>                     | V <sub>DD</sub> – 0.8     |                    |                       | V          |

| Output low voltage (see <b>Figure 13-4</b> )<br>I <sub>Load</sub> = 1.6 mA<br>PA7–PA0, PB7–PB0, PC6–PC0, PD4–PD1<br>I <sub>Load</sub> = 20 mA, PC7                                                                                                  | V <sub>OL</sub>                     |                           |                    | 0.4<br>0.4            | V          |

| Input high voltage<br>PA7–PA0, PB7–PB0, PC7–PC0, PD5–PD0, PD7,<br>TCAP, IRQ, RESET, OSC1                                                                                                                                                            | V <sub>IH</sub>                     | 0.7 x V <sub>DD</sub>     | _                  | V <sub>DD</sub>       | V          |

| Input low voltage<br>PA7–PA0, PB7–PB0, PC7–PC0, PD5–PD0, PD7,<br>TCAP, IRQ, RESET, OSC1                                                                                                                                                             | V <sub>IL</sub>                     | V <sub>SS</sub>           |                    | 0.2 x V <sub>DD</sub> | V          |

| EPROM programming voltage                                                                                                                                                                                                                           | V <sub>PP</sub>                     | 14.5                      | 14.75              | 15.0                  | V          |

| EPROM/OTPROM programming current                                                                                                                                                                                                                    | I <sub>PP</sub>                     | —                         | 5                  | 10                    | mA         |

| User mode current                                                                                                                                                                                                                                   | I <sub>PP</sub>                     | —                         |                    | ± 10                  | mA         |

| Data-retention mode (0°C to 70°C)                                                                                                                                                                                                                   | V <sub>RM</sub>                     | 2.0                       |                    |                       | V          |

| Supply current <sup>(3)</sup><br>Run <sup>(4)</sup><br>Wait <sup>(5)</sup><br>Stop <sup>(6)</sup>                                                                                                                                                   | I <sub>DD</sub>                     |                           | 5.0<br>1.95        | 7.0<br>3.0            | mA<br>mA   |

| 25°C<br>–40°C to +85°C                                                                                                                                                                                                                              |                                     | —                         | 5.0<br>5.0         | 50<br>50              | μμΑ<br>μμΑ |

| I/O ports hi-z leakage current<br>PA7–PA0, PB7–PB0, PC7–PC0, PD4–PD1, PD7, RESET                                                                                                                                                                    | IIL                                 |                           |                    | ± 10                  | μΑ         |

| Input current, IRQ, TCAP, OSC1, PD0, PD5                                                                                                                                                                                                            | l <sub>ln</sub>                     | —                         |                    | ± 1                   | μA         |

| Capacitance<br>Ports (as input or output)<br>RESET, IRQ, TCAP, PD0–PD5, PD7                                                                                                                                                                         | C <sub>Out</sub><br>C <sub>In</sub> |                           |                    | 12<br>8               | pF         |

1.  $V_{DD}$  = 5 V  $\pm$  10%;  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H,$  unless otherwise noted

2. Typical values reflect average measurements at midpoint of voltage range at 25°C.

3. I<sub>DD</sub> measured with port B pullup devices disabled.

4. Run (operating) I<sub>DD</sub> measured using external square wave clock source (f<sub>OSC</sub> = 4.2 MHz). All inputs 0.2 V from rail. No dc loads. Less than 50 pF on all outputs. C<sub>L</sub> = 20 pF on OSC2. OSC2 capacitance linearly affects run I<sub>DD</sub>.

- 5. Wait I<sub>DD</sub> measured using external square wave clock source ( $f_{OSC}$  = 4.2 MHz). All inputs 0.2 V from rail. No dc loads. Less than 50 pF on all outputs. C<sub>L</sub> = 20 pF on OSC2. V<sub>IL</sub> = 0.2 V, V<sub>IH</sub> = V<sub>DD</sub> 0.2 V. All ports configured as inputs. SPI and SCI disabled. If SPI and SCI enabled, add 10% current draw. OSC2 capacitance linearly affects wait I<sub>DD</sub>.

- 6. Stop I<sub>DD</sub> measured with OSC1 = V<sub>DD</sub>. All ports configured as inputs.  $V_{IL}$  = 0.2 V,  $V_{IH}$  =  $V_{DD}$  0.2 V.

| MC68HC705C8A - Rev. 3 | 3 |

|-----------------------|---|

|                       | - |

MOTOROLA

**Technical Data**

Electrical Specifications 3.3-Volt DC Electrical Characteristics

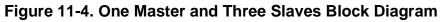

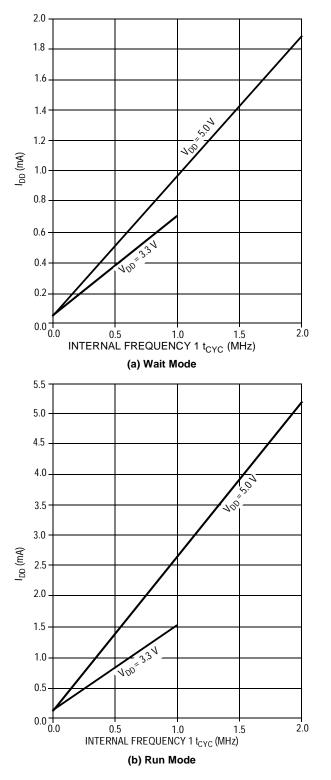

Figure 13-3. Typical Current versus Internal Frequency for Run and Wait Modes

MC68HC705C8A — Rev. 3

**Technical Data**

**Electrical Specifications**

## 13.9 5.0-Volt Control Timing

| Characteristic <sup>(1)</sup>                                                                                                                     | Symbol                                                                      | Min               | Max        | Unit                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------|------------|--------------------------------------------|

| Frequency of operation<br>Crystal option<br>External clock option                                                                                 | fosc                                                                        | <br>dc            | 4.2<br>4.2 | MHz                                        |

| Internal operating frequency<br>Crystal (f <sub>OSC</sub> ÷ 2)<br>External clock (f <sub>OSC</sub> ÷ 2)                                           | f <sub>OP</sub>                                                             | <br>dc            | 2.1<br>2.1 | MHz                                        |

| Cycle time (see Figure 13-7)                                                                                                                      | t <sub>CYC</sub>                                                            | 480               | —          | ns                                         |

| Crystal oscillator startup time (see Figure 13-7)                                                                                                 | t <sub>OXOV</sub>                                                           | _                 | 100        | ms                                         |

| Stop recovery startup time (crystal oscillator)<br>(see Figure 13-6)                                                                              | t <sub>ILCH</sub>                                                           | _                 | 100        | ms                                         |

| RESET pulse width (see Figure 13-7)                                                                                                               | t <sub>RL</sub>                                                             | 8                 | —          | t <sub>CYC</sub>                           |

| Timer<br>Resolution <sup>(2)</sup><br>Input capture pulse width (see <b>Figure 13-5</b> )<br>Input capture pulse period (see <b>Figure 13-5</b> ) | t <sub>RESL</sub><br>t <sub>TH</sub> , t <sub>TL</sub><br>t <sub>TLTL</sub> | 4.0<br>125<br>(3) |            | <sup>t</sup> cyc<br>ns<br><sup>t</sup> cyc |

| Interrupt pulse width low (edge-triggered)<br>(see Figure 4-2. External Interrupt Timing)                                                         | t <sub>ILIH</sub>                                                           | 125               |            | ns                                         |

| Interrupt pulse period<br>(see Figure 4-2. External Interrupt Timing)                                                                             | t <sub>ILIL</sub>                                                           | (4)               | _          | t <sub>CYC</sub>                           |

| OSC1 pulse width                                                                                                                                  | t <sub>OH</sub> , t <sub>OL</sub>                                           | 90                | —          | ns                                         |

1. V<sub>DD</sub> = 5.0 Vdc  $\pm$  10%, V<sub>SS</sub> = 0 Vdc; T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub>

2. Since a 2-bit prescaler in the timer must count four internal cycles (t<sub>CYC</sub>), this is the limiting minimum factor in determining the timer resolution.

3. The minimum period, t<sub>TLTL</sub>, should not be less than the number of cycle times it takes to execute the capture interrupt service routine plus 24 t<sub>CYC</sub>.

4. The minimum period, t<sub>ILIL</sub>, should not be less than the number of cycle times it takes to execute the interrupt service routine plus 19 t<sub>CYC</sub>.

## MC68HSC705C8A

| Diagram<br>Number <sup>(1)</sup> | Characteristic <sup>(2)</sup>                                                                         | Symbol                                   | Min       | Мах       | Unit                      |

|----------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------|-----------|-----------|---------------------------|

| 11                               | Data hold time (outputs)<br>Master (after capture edge)<br>Slave (after enable edge)                  | <sup>t</sup> HO(M)<br><sup>t</sup> HO(S) | 0.25<br>0 |           | t <sub>CYC(M)</sub><br>ns |

| 12                               | Rise time <sup>(7)</sup><br>SPI outputs (SCK, MOSI, MISO <u>)</u><br>SPI inputs (SCK, MOSI, MISO, SS) | t <sub>RM</sub><br>t <sub>RS</sub>       |           | 50<br>2.0 | ns<br>μs                  |

| 13                               | Fall time <sup>(8)</sup><br>SPI outputs (SCK, MOSI, MISO <u>)</u><br>SPI inputs (SCK, MOSI, MISO, SS) | t <sub>FM</sub><br>t <sub>FS</sub>       |           | 50<br>2.0 | ns<br>μs                  |

1. Diagram numbers refer to dimensions in Figure 13-8. SPI Master Timing and Figure 13-9. SPI Slave Timing.

2. V<sub>DD</sub> = 5 V  $\pm$  10%; V<sub>SS</sub> = 0 Vdc, T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub>, unless otherwise noted

3. Signal production depends on software.

4. Time to data active from high-impedance state

5. Hold time to high-impedance state

6. With 200 pF on all SPI pins.

7. 20% of  $V_{DD}$  to 70% of  $V_{DD}$ ;  $C_L$  = 200 pF 8. 70% of  $V_{DD}$  to 20% of  $V_{DD}$ ;  $C_L$  = 200 pF

**Technical Data**

MC68HC705C8A — Rev. 3

MC68HSC705C8A

#### For More Information On This Product, Go to: www.freescale.com

## MC68HSC705C8A

| Diagram<br>Number <sup>(1)</sup> | Characteristic <sup>(2)</sup>                                                                         | Symbol                                   | Min       | Мах        | Unit                      |

|----------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------|-----------|------------|---------------------------|

| 11                               | Data hold time (outputs)<br>Master (after capture edge)<br>Slave (after enable edge)                  | <sup>t</sup> HO(M)<br>t <sub>HO(S)</sub> | 0.25<br>0 |            | t <sub>CYC(M)</sub><br>ns |

| 12                               | Rise time <sup>(7)</sup><br>SPI outputs (SCK, MOSI, MISO <u>)</u><br>SPI inputs (SCK, MOSI, MISO, SS) | t <sub>RM</sub><br>t <sub>RS</sub>       |           | 100<br>2.0 | ns<br>μs                  |

| 13                               | Fall time <sup>(8)</sup><br>SPI outputs (SCK, MOSI, MISO <u>)</u><br>SPI inputs (SCK, MOSI, MISO, SS) | t <sub>FM</sub><br>t <sub>FS</sub>       | _         | 100<br>2.0 | ns<br>μs                  |

1. Diagram numbers refer to dimensions in Figure 13-8. SPI Master Timing and Figure 13-9. SPI Slave Timing.

2.  $V_{DD} = 3.3 \text{ V} \pm 10\%$ ;  $V_{SS} = 0 \text{ Vdc}$ ,  $T_A = T_L$  to  $T_H$ , unless otherwise noted

3. Signal production depends on software.

4. Time to data active from high-impedance state

5. Hold time to high-impedance state

6. With 200 pF on all SPI pins

7. 20% of  $V_{DD}$  to 70% of  $V_{DD}$ ;  $C_L$  = 200 pF 8. 70% of  $V_{DD}$  to 20% of  $V_{DD}$ ;  $C_L$  = 200 pF

MC68HC705C8A — Rev. 3

MC68HSC705C8A

#### For More Information On This Product, Go to: www.freescale.com