# E·XFL

#### NXP USA Inc. - MCHSC705C8ACPE Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | HC05                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 4MHz                                                                   |

| Connectivity               | SCI, SPI                                                               |

| Peripherals                | POR, WDT                                                               |

| Number of I/O              | 24                                                                     |

| Program Memory Size        | 8KB (8K x 8)                                                           |

| Program Memory Type        | OTP                                                                    |

| EEPROM Size                | · ·                                                                    |

| RAM Size                   | 304 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                              |

| Data Converters            | · ·                                                                    |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                               |

| Supplier Device Package    | 40-PDIP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mchsc705c8acpe |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**List of Sections**

**Technical Data**

List of Figures

| Figure | Title                                             | Page |

|--------|---------------------------------------------------|------|

| 14-1   | MC68HC705C8AP Package Dimensions<br>(Case #711)   |      |

| 14-2   | MC68HC705C8AS Package Dimensions<br>(Case #734A)  |      |

| 14-3   | MC68HC705C8AFN Package Dimensions<br>(Case #777)  |      |

| 14-4   | MC68HC705C8AFS Package Dimensions<br>(Case #777B) |      |

| 14-5   | MC68HC705C8AFB Package Dimensions<br>(Case #824A) |      |

| 14-6   | MC68HC705C8AB Package Dimensions<br>(Case #858)   |      |

**Technical Data**

# **General Description**

| RESET    | [ 1  | $\bigcirc$ | 42 🛛 V <sub>DD</sub> |

|----------|------|------------|----------------------|

| IRQ      | 2    |            | 41 ] OSC1            |

| $V_{PP}$ | 3    |            | 40 🛛 OSC2            |

| PA7      | [ 4  |            | 39 🗍 TCAP            |

| PA6      | 5    |            | 38 🗍 PD7             |

| PA5      | 6    |            | 37 🗍 TCMP            |

| PA4      | [ 7  |            | 36 ] PD5/SS          |

| PA3      | 8    |            | 35 🗍 PD4/SCK         |

| PA2      | 9    |            | 34 DD3/MOSI          |

| PA1      | [ 10 |            | 33 PD2/MISO          |

| PA0      | [ 11 |            | 32 ] PD1/TDO         |

| PB0      | [ 12 |            | 31 DD0/RDI           |

| PB1      | [ 13 |            | 30 🗍 PC0             |

| PB2      | [ 14 |            | 29 🗍 PC1             |

| PB3      | [ 15 |            | 28 🗍 PC2             |

| NC       | [ 16 |            | 27 🗍 NC              |

| PB4      | [ 17 |            | 26 🗍 PC3             |

| PB5      | [ 18 |            | 25 🗍 PC4             |

| PB6      | [ 19 |            | 24 🛛 PC5             |

| PB7      | 20   |            | 23 🗍 PC6             |

| $V_{SS}$ | 21   |            | 22 🗍 PC7             |

|          | L    |            |                      |

Figure 1-6. 42-Pin SDIP Pin Assignments

**Freescale Semiconductor, Inc.**

**Technical Data**

Memory

| Addr.  | Register Name                                   |                 | Bit 7 | 6         | 5      | 4           | 3           | 2     | 1     | Bit 0 |

|--------|-------------------------------------------------|-----------------|-------|-----------|--------|-------------|-------------|-------|-------|-------|

| \$000A | SPI Control Register<br>(SPCR)                  | Read:<br>Write: | SPIE  | SPE       |        | MSTR        | CPOL        | СРНА  | SPR1  | SPR0  |

|        | See page 149.                                   | Reset:          | 0     | 0         |        | 0           | U           | U     | U     | U     |

|        | SPI Status Register                             | Read:           | SPIF  | WCOL      |        | MODF        |             |       |       |       |

| \$000B | \$000B (SPSR)                                   | Write:          |       |           |        |             |             |       |       |       |

|        | See page 151.                                   | Reset:          | 0     | 0         |        | 0           |             |       |       |       |

| \$000C | SPI Data Register<br>(SPDR)                     | Read:<br>Write: | Bit 7 | Bit 6     | Bit 5  | Bit 4       | Bit 3       | Blt 2 | Bit 1 | Bit 0 |

|        | See page 149.                                   | Reset:          |       |           |        | Unaffect    | ed by reset |       |       |       |

| \$000D | Baud Rate Register<br>(Baud)                    | Read:<br>Write: |       |           | SCP1   | SCP0        |             | SCR2  | SCR1  | SCR0  |

|        | See page 136.                                   | Reset:          | U     | U         | 0      | 0           | U           | U     | U     | U     |

| \$000E | SCI Control Register 1<br>(SCCR1)               | Read:<br>Write: | R8    | Т8        |        | М           | WAKE        |       |       |       |

|        | See page 130.                                   | Reset:          | U     | U         |        | U           | U           |       |       |       |

| \$000F | SCI Control Register 2<br>(SCCR2)               | Read:<br>Write: | TIE   | TCIE      | RIE    | ILIE        | TE          | RE    | RWU   | SBK   |

|        | See page 131.                                   | Reset:          | 0     | 0         | 0      | 0           | 0           | 0     | 0     | 0     |

|        | SCI Status Register                             | Read:           | TDRE  | TC        | RDRF   | IDLE        | OR          | NF    | FE    |       |

| \$0010 | (SCSR)                                          | Write:          |       |           |        |             |             |       |       |       |

|        | See page 133.                                   | Reset:          | 1     | 1         | 0      | 0           | 0           | 0     | 0     | U     |

| \$0011 | SCI Data Register<br>(SCDR)                     | Read:<br>Write: | Bit 7 | Bit 6     | Bit 5  | Bit 4       | Bit 3       | Bit 2 | Bit 1 | Bit 0 |

|        | See page 129.                                   | Reset:          |       |           |        | Unaffect    | ed by reset |       |       |       |

| \$0012 | Timer Control Register<br>(TCR)<br>See page 94. | Read:<br>Write: | ICIE  | OCIE      | TOIE   | 0           | 0           | 0     | IEDG  | OLVL  |

|        | 300 page 94.                                    | Reset:          | 0     | 0         | 0      | 0           | 0           | 0     | U     | 0     |

|        |                                                 |                 |       | = Unimple | mented | U = Unaffeo | cted        |       |       |       |

# Figure 2-2. I/O Register Summary (Sheet 2 of 4)

**Technical Data**

**Central Processor Unit (CPU)**

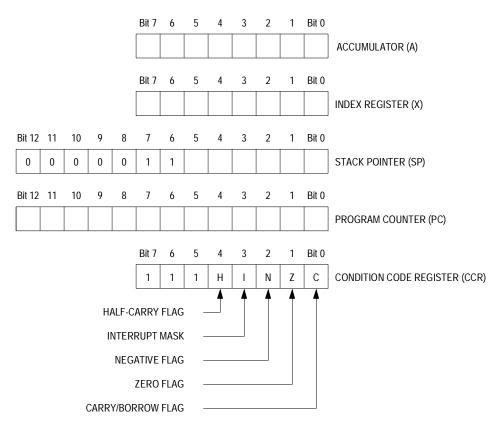

# 3.3 CPU Registers

**Figure 3-1** shows the five CPU registers. These are hard-wired registers within the CPU and are not part of the memory map.

Figure 3-1. Programming Model

- SCI Receiver Overrun Interrupt The overrun bit (OR) indicates that a received byte is lost because software has not read the previously received byte. OR becomes set when a byte shifts into the receive shift register before software reads the word already in the SCI data register. OR generates an interrupt request if the receive interrupt enable bit (RIE) is set also.

- SCI Receiver Input Idle Interrupt The receiver input idle bit (IDLE) indicates that the SCI receiver input is not receiving data.

IDLE becomes set when 10 or 11 consecutive logic 1s appear on the receiver input. IDLE generates an interrupt request if the idle line interrupt enable bit (ILIE) is set also.

#### 4.3.6 SPI Interrupts

The serial peripheral interrupt (SPI) can generate these interrupts:

- SPI transmission complete interrupt

- SPI mode fault interrupt

Setting the I bit in the CCR disables all SPI interrupts.

- SPI Transmission Complete Interrupt The SPI flag bit (SPIF) in the SPI status register indicates the completion of an SPI transmission. SPIF becomes set when a byte shifts into or out of the SPI data register. SPIF generates an interrupt request if the SPIE bit is set also.

- SPI Mode Fault Interrupt The mode fault bit (MODF) in the SPI status register indicates an SPI mode error. MODF becomes set when a logic 0 occurs on the PD5/SS pin while the master bit (MSTR) in the SPI control register is set. MODF generates an interrupt request if the SPIE bit is set also.

\$00C0 (BOTTOM OF STACK) \$00C1 \$00C2 UNSTACKING ORDER . 5 CONDITION CODE REGISTER 1 4 2 ACCUMULATOR 3 3 INDEX REGISTER 4 PROGRAM COUNTER (HIGH BYTE) 2 1 5 PROGRAM COUNTER (LOW BYTE) STACKING ORDER \$00FD \$00FE \$00FF (TOP OF STACK)

Figure 4-4. Interrupt Stacking Order

**NOTE:** If more than one interrupt request is pending, the CPU fetches the vector of the higher priority interrupt first. A higher priority interrupt does not interrupt a lower priority interrupt service routine unless the lower priority interrupt service routine clears the I bit. See **Table 4-1** for a priority listing.

Figure 4-5 shows the sequence of events caused by an interrupt.

**Technical Data**

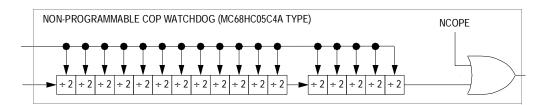

2. COP clear bit (COPC) at address \$1FF0

To clear the non-programmable COP watchdog and start a new COP timeout period, write a logic 0 to bit 0 of address \$1FF0. Reading address \$1FF0 returns the mask option register 1 (MOR1) data at that location. See **9.5.2 Mask Option Register 1**.

**NOTE:** The non-programmable watchdog COP is disabled in bootloader mode, even if the NCOPE bit is programmed.

Figure 5-4 is a diagram of the non-programmable COP.

#### 5.3.4 Clock Monitor Reset

When the CME bit in the COP control register is set, the clock monitor detects the absence of the internal bus clock for a certain period of time. The timeout period depends on processing parameters and varies from 5  $\mu$ s to 100  $\mu$ s, which implies that systems using a bus clock rate of 200 kHz or less should not use the clock monitor function.

If a slow or absent clock is detected, the clock monitor causes a system reset. The reset is issued to the external system for four bus cycles using the bidirectional  $\overrightarrow{\text{RESET}}$  pin.

Special consideration is required when using the STOP instruction with the clock monitor. Since STOP causes the system clocks to halt, the clock monitor issues a system reset when STOP is executed.

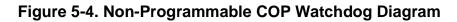

#### 7.3.2 Data Direction Register A

The contents of data direction register A (DDRA) shown in **Figure 7-2** determine whether each port A pin is an input or an output. Writing a logic 1 to a DDRA bit enables the output buffer for the associated port A pin; a logic 0 disables the output buffer. A reset clears all DDRA bits, configuring all port A pins as inputs.

Figure 7-2. Data Direction Register A (DDRA)

DDRA7–DDRA0 — Port A Data Direction Bits

These read/write bits control port A data direction. Reset clears bits DDRA7–DDRA0.

1 = Corresponding port A pin configured as output

0 = Corresponding port A pin configured as input

**NOTE:** Avoid glitches on port A pins by writing to the port A data register before changing DDRA bits from logic 0 to logic 1.

MC68HC705C8A — Rev. 3

## 7.4 Port B

Port B is an 8-bit, general-purpose, bidirectional I/O port. Port B pins can also be configured to function as external interrupts. The port B pullup devices are enabled in mask option register 1 (MOR1). See 9.5.2 Mask Option Register 1 and 4.3.3 Port B Interrupts.

## 7.4.1 Port B Data Register

The port B data register (PORTB) shown in **Figure 7-4** contains a data latch for each of the eight port B pins.

Address: \$0001

|                 | Bit 7 | 6   | 5   | 4         | 3          | 2   | 1   | Bit 0 |

|-----------------|-------|-----|-----|-----------|------------|-----|-----|-------|

| Read:<br>Write: | PB7   | PB6 | PB5 | PB4       | PB3        | PB2 | PB1 | PB0   |

| Reset:          |       |     |     | Unaffecte | d by reset |     |     |       |

#### Figure 7-4. Port B Data Register (PORTB)

PB7-PB0 - Port B Data Bits

These read/write bits are software programmable. Data direction of each bit is under the control of the corresponding bit in data direction register B. Reset has no effect on port B data.

# Freescale Semiconductor, Inc.

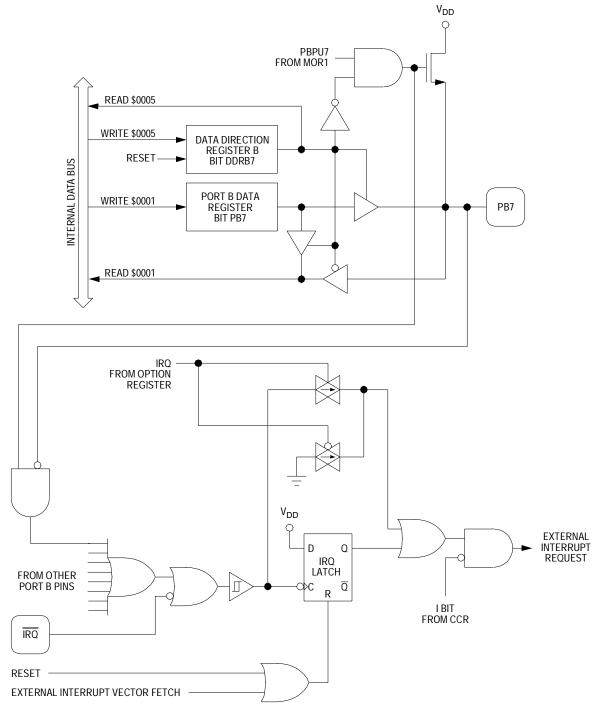

#### 7.4.3 Port B Logic

Figure 7-6 shows the port B I/O logic.

## Figure 7-6. Port B I/O Logic

**Technical Data**

Parallel Input/Output (I/O) For More Information On This Product, Go to: www.freescale.com

**Technical Data**

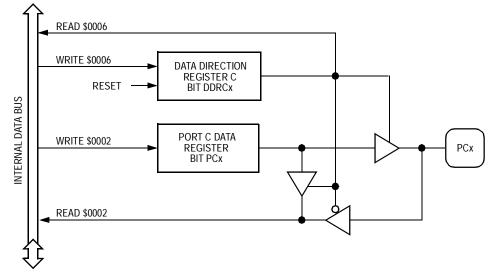

#### 7.5.3 Port C Logic

Figure 7-9 shows port C I/O logic.

Figure 7-9. Port C I/O Logic

When a port C pin is programmed as an output, reading the port bit reads the value of the data latch and not the voltage on the pin. When a port C pin is programmed as an input, reading the port bit reads the voltage level on the pin. The data latch can always be written, regardless of the state of its DDRC bit. **Table 7-3** summarizes the operation of the port C pins.

| Table 7-3 | . Port C Pin | Functions |

|-----------|--------------|-----------|

|-----------|--------------|-----------|

| Ī | DDRC Bit | I/O Pin Mode               | Accesses to DDRC | Accesses to PORTC |                        |  |

|---|----------|----------------------------|------------------|-------------------|------------------------|--|

|   | DDRC BI  |                            | Read/Write       | Read              | Write                  |  |

|   | 0        | Input, Hi-Z <sup>(1)</sup> | DDRC7-DDRC0      | Pin               | PC7-PC0 <sup>(2)</sup> |  |

|   | 1        | Output                     | DDRC7-DDRC0      | PC7–PC0           | PC7-PC0                |  |

1. Hi-Z = high impedance

2. Writing affects data register but does not affect input.

**NOTE:** To avoid excessive current draw, tie all unused input pins to  $V_{DD}$  or  $V_{SS}$  or change I/O pins to outputs by writing to DDRC in user code as early as possible.

MC68HC705C8A — Rev. 3

MOTOROLA

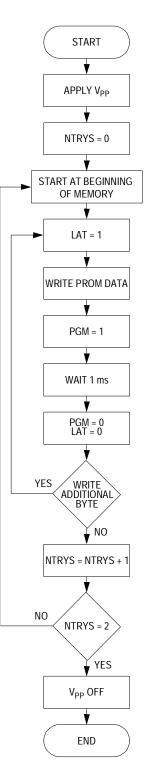

EPROM/OTPROM (PROM) EPROM/OTPROM (PROM) Programming

## Figure 9-1. EPROM/OTPROM Programming Flowchart

**Freescale Semiconductor, Inc.**

MC68HC705C8A — Rev. 3

MOTOROLA

EPROM/OTPROM (PROM)

For More Information On This Product, Go to: www.freescale.com

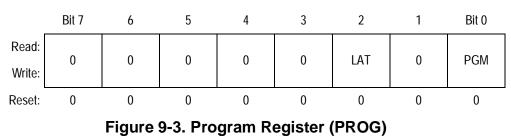

#### 9.3.1 Program Register

The program register (PROG) shown in **Figure 9-3** is used for PROM programming.

Address: \$001C

LAT — Latch Enable Bit

This bit is both readable and writable.

- 1 = Enables PROM data and address bus latches for programming on the next byte write cycle

- 0 = Latch disabled. PROM data and address buses are unlatched for normal CPU operations.

PGM — Program Bit

If LAT is cleared, PGM cannot be set.

- 1 = Enables  $V_{PP}$  power to the PROM for programming

- $0 = V_{PP}$  is disabled.

Bits 1 and 3-7 - Not used; always read 0

## 9.4 **PROM Programming Routines**

This subsection describes the routines necessary to program, verify, and secure the PROM device, and other routines available to the user.

#### 9.4.1 Program and Verify PROM

The program and verify PROM routine copies the contents of the external EPROM into the MCU PROM with direct correspondence between the addresses. Memory addresses in the MCU that are not implemented in PROM are skipped. Unprogrammed addresses in the EPROM being copied should contain \$00 bytes to speed up the programming process.

To run the program and verify the PROM routine on the PROM MCU, take these steps:

- 1. Set switch 1 in the ON position (restores V<sub>DD</sub>).

- 2. Restore the  $V_{PP}$  power source.

- 3. Set switches S3, S4, S5, and S6 in the OFF position (selects proper routine).

- 4. Set switch 2 in the OUT position (routine is activated).

The red light-emitting diode (LED) is illuminated, showing that the programming part of the routine is running. The LED goes out when programming is finished. The verification part of the routine now begins. When the green LED is illuminated, verification is successfully completed and the routine is finished.

5. Set switch 2 in the RESET position.

At this point, if no other MCU is to be programmed or secured, remove  $V_{PP}$  power from the board. If another routine is to be performed on the MCU being programmed, the user can then set switches S3, S4, S5, and S6 to the positions necessary to select the next routine, and begin the routine by setting switch 2 to the OUT position. If no other routine is to be performed, remove  $V_{DD}$  from the board and remove the MCU from the programming socket.

MC68HC705C8A — Rev. 3

# Serial Communications Interface (SCI)

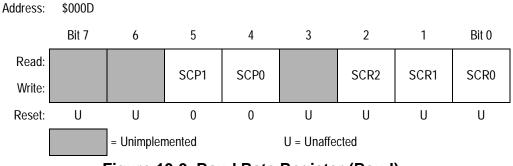

#### 10.6.5 Baud Rate Register

The baud rate register shown in **Figure 10-9** selects the baud rate for both the receiver and the transmitter.

Figure 10-9. Baud Rate Register (Baud)

SCP1 and SCP0 — SCI Prescaler Select Bits

These read/write bits control prescaling of the baud rate generator clock, as shown in **Table 10-1**. Resets clear both SCP1 and SCP0.

| Table 10-1. Baud Rate Generato | or Clock Prescaling |

|--------------------------------|---------------------|

|--------------------------------|---------------------|

| SCP[1:0] | Baud Rate Generator Clock |

|----------|---------------------------|

| 00       | Internal clock ÷ 1        |

| 01       | Internal clock ÷ 3        |

| 10       | Internal clock ÷ 4        |

| 11       | Internal clock ÷ 13       |

MC68HC705C8A — Rev. 3

Serial Peripheral Interface (SPI)

MODF — Mode Fault Bit

This clearable, read-only bit is set when a logic 0 occurs on the PD5/SS pin while the MSTR bit is set. MODF generates an interrupt request if the SPIE bit is also set. Clear the MODF bit by reading the SPSR with MODF set and then writing to the SPCR. Reset clears MODF.

$1 = PD5/\overline{SS}$  pulled low while MSTR bit set

$0 = PD5/\overline{SS}$  not pulled low while MSTR bit set

Technical Data

Instruction Set Addressing Modes

#### 12.3.1 Inherent

Inherent instructions are those that have no operand, such as return from interrupt (RTI) and stop (STOP). Some of the inherent instructions act on data in the CPU registers, such as set carry flag (SEC) and increment accumulator (INCA). Inherent instructions require no operand address and are one byte long.

#### 12.3.2 Immediate

Immediate instructions are those that contain a value to be used in an operation with the value in the accumulator or index register. Immediate instructions require no operand address and are two bytes long. The opcode is the first byte, and the immediate data value is the second byte.

## 12.3.3 Direct

Direct instructions can access any of the first 256 memory locations with two bytes. The first byte is the opcode, and the second is the low byte of the operand address. In direct addressing, the CPU automatically uses \$00 as the high byte of the operand address.

## 12.3.4 Extended

Extended instructions use three bytes and can access any address in memory. The first byte is the opcode; the second and third bytes are the high and low bytes of the operand address.

When using the Motorola assembler, the programmer does not need to specify whether an instruction is direct or extended. The assembler automatically selects the shortest form of the instruction.

# 13.3 Maximum Ratings

Maximum ratings are the extreme limits to which the MCU can be exposed without permanently damaging it.

The MCU contains circuitry to protect the inputs against damage from high static voltages; however, do not apply voltages higher than those shown in the table here. Keep V<sub>In</sub> and V<sub>Out</sub> within the range  $V_{SS} \leq (V_{In} \text{ or } V_{Out}) \leq V_{DD}$ . Connect unused inputs to the appropriate voltage level, either V<sub>SS</sub> or V<sub>DD</sub>.

| Rating <sup>(1)</sup>                                                                       | Symbol           | Value                                           | Unit |

|---------------------------------------------------------------------------------------------|------------------|-------------------------------------------------|------|

| Supply voltage                                                                              | V <sub>DD</sub>  | -0.3 to +7.0                                    | V    |

| Input voltage                                                                               | V <sub>In</sub>  | V <sub>SS</sub> –0.3<br>to V <sub>DD</sub> +0.3 | V    |

| Programming voltage                                                                         | V <sub>PP</sub>  | V <sub>DD</sub> –0.3 to<br>16.0                 |      |

| Bootstrap mode (IRQ pin only)                                                               | V <sub>In</sub>  | $V_{SS} - 0.3$<br>to 2 x $V_{DD}$ + 0.3         | V    |

| Current drain per pin excluding $V_{\mbox{\scriptsize DD}}$ and $V_{\mbox{\scriptsize SS}}$ | Ι                | 25                                              | mA   |

| Storage temperature range                                                                   | T <sub>STG</sub> | –65 to +150                                     | °C   |

1. Voltages referenced to  $\mathrm{V}_{\mathrm{SS}}$

**NOTE:** This device is not guaranteed to operate properly at the maximum ratings. Refer to **13.7 5.0-Volt DC Electrical Characteristics** and **13.8 3.3-Volt DC Electrical Characteristics** for guaranteed operating conditions.

MC68HSC705C8A

# A.7 5.0-Volt High-Speed SPI Timing

| Diagram<br>Number <sup>(1)</sup> | Characteristic <sup>(2)</sup>                                                               | Symbol                                         | Min                        | Max        | Unit                      |

|----------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------|------------|---------------------------|

|                                  | Operating frequency<br>Master<br>Slave                                                      | fop(s)<br>fop(s)                               | dc<br>dc                   | 0.5<br>4.0 | f <sub>OP</sub><br>MHz    |

| 1                                | Cycle time<br>Master<br>Slave                                                               | t <sub>CYC(M)</sub><br>t <sub>CYC(S)</sub>     | 2.0<br>250                 |            | t <sub>CYC</sub><br>ns    |

| 2                                | Enable lead time<br>Master<br>Slave                                                         | t <sub>Lead(M)</sub><br>t <sub>Lead(S)</sub>   | Note <sup>(3)</sup><br>125 |            | ns                        |

| 3                                | Enable lag time<br>Master<br>Slave                                                          | t <sub>Lag(M)</sub><br>t <sub>Lag(S)</sub>     | Note <sup>(2)</sup><br>375 |            | ns                        |

| 4                                | Clock (SCK) high time<br>Master<br>Slave                                                    | <sup>t</sup> w(scкн)м<br><sup>t</sup> w(scкн)s | 170<br>95                  |            | ns                        |

| 5                                | Clock (SCK) low time<br>Master<br>Slave                                                     | t <sub>W(SCKL)M</sub><br>t <sub>W(SCKL)S</sub> | 170<br>95                  |            | ns                        |

| 6                                | Data setup time (inputs)<br>Master<br>Slave                                                 | t <sub>SU(M)</sub><br>t <sub>SU(S)</sub>       | 50<br>50                   |            | ns                        |

| 7                                | Data hold time (inputs)<br>Master<br>Slave                                                  | t <sub>H(M)</sub><br>t <sub>H(S)</sub>         | 50<br>50                   |            | ns                        |

| 8                                | Access time <sup>(4)</sup><br>Slave                                                         | t <sub>A</sub>                                 | 0                          | 60         | ns                        |

| 9                                | Disable time <sup>(5)</sup><br>Slave                                                        | t <sub>DIS</sub>                               | _                          | 120        | ns                        |

| 10                               | Data valid time<br>Master (before capture edge)<br>Slave (after enable edge) <sup>(6)</sup> | t <sub>∨(M)</sub><br>t <sub>V(S)</sub>         | 0.25                       | <br>120    | t <sub>CYC(M)</sub><br>ns |

Continued

**Technical Data**