#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

## Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                      |

|---------------------------------|-------------------------------------------------------------|

| Core Processor                  | PowerPC G4                                                  |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                              |

| Speed                           | 1.0GHz                                                      |

| Co-Processors/DSP               | Multimedia; SIMD                                            |

| RAM Controllers                 | -                                                           |

| Graphics Acceleration           | No                                                          |

| Display & Interface Controllers | -                                                           |

| Ethernet                        | -                                                           |

| SATA                            | -                                                           |

| USB                             | -                                                           |

| Voltage - I/O                   | 1.5V, 1.8V, 2.5V                                            |

| Operating Temperature           | 0°C ~ 105°C (TA)                                            |

| Security Features               | -                                                           |

| Package / Case                  | 483-BCBGA, FCCBGA                                           |

| Supplier Device Package         | 483-FCCBGA (29x29)                                          |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc7457rx1000lc |

|                                 |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

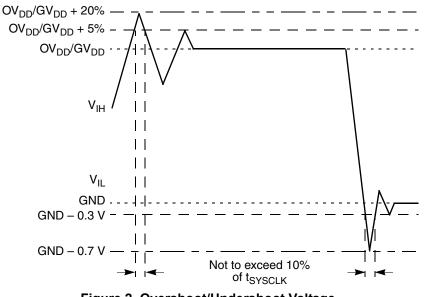

Figure 2. Overshoot/Undershoot Voltage

The MPC7457 provides several I/O voltages to support both compatibility with existing systems and migration to future systems. The MPC7457 core voltage must always be provided at nominal 1.3 V (see Table 4 for actual recommended core voltage). Voltage to the L3 I/Os and processor interface I/Os are provided through separate sets of supply pins and may be provided at the voltages shown in Table 3. The input voltage threshold for each bus is selected by sampling the state of the voltage select pins at the negation of the signal HRESET. The output voltage will swing from GND to the maximum voltage applied to the OV<sub>DD</sub> or GV<sub>DD</sub> power pins.

Table 3. Input Threshold Voltage Setting

| BVSEL Signal | Processor Bus Input Threshold<br>is Relative to: | L3VSEL Signal <sup>1</sup> | L3 Bus Input Threshold is Relative to: | Notes |

|--------------|--------------------------------------------------|----------------------------|----------------------------------------|-------|

| 0            | 1.8 V                                            | 0                          | 1.8 V                                  | 2, 3  |

| HRESET       | Not Available                                    | ¬HRESET                    | 1.5 V                                  | 2, 4  |

| HRESET       | 2.5 V                                            | HRESET                     | 2.5 V                                  | 2     |

| 1            | 2.5 V                                            | 1                          | 2.5 V                                  | 2     |

#### Notes:

1. Not implemented on MPC7447.

2. Caution: The input threshold selection must agree with the OV<sub>DD</sub>/GV<sub>DD</sub> voltages supplied. See notes in Table 2.

3. If used, pull-down resistors should be less than 250  $\boldsymbol{\Omega}.$

4. Applicable to L3 bus interface only. ¬HRESET is the inverse of HRESET.

#### **Electrical and Thermal Characteristics**

## Table 13. L3 Bus Interface AC Timing Specifications for MSUG2 (continued)

At recommended operating conditions. See Table 4.

|                                             |                     | De  | evice Revision                    | (L3 I/O Voltaç | je) <sup>9</sup>                  |      |       |

|---------------------------------------------|---------------------|-----|-----------------------------------|----------------|-----------------------------------|------|-------|

| Parameter                                   | Symbol              |     | .II I/O Modes)<br>5-V I/O Mode)   |                | v 1.2<br>/ I/O Modes)             | Unit | Notes |

|                                             |                     | Min | Max                               | Min            | Max                               |      |       |

| L3_CLK to high impedance: All other outputs | t <sub>L3CHOZ</sub> | —   | (t <sub>L3CLK</sub> /4)<br>+ 0.65 |                | (t <sub>L3CLK</sub> /4)<br>+ 0.65 | ns   |       |

## Notes:

1. Rise and fall times for the L3\_CLK output are measured from 20% to 80% of GV<sub>DD</sub>.

- 2. For DDR, all input specifications are measured from the midpoint of the signal in question to the midpoint voltage of the rising or falling edge of the input L3\_ECHO\_CLK*n* (see Figure 10). Input timings are measured at the pins.

- 3. For DDR, the input data will typically follow the edge of L3\_ECHO\_CLK*n* as shown in Figure 10. For consistency with other input setup time specifications, this will be treated as negative input setup time.

- 4. t<sub>L3\_CLK</sub>/4 is one-fourth the period of L3\_CLK*n*. This parameter indicates that the MPC7457 can latch an input signal that is valid for only a short time before and a short time after the midpoint between the rising and falling (or falling and rising) edges of L3\_ECHO\_CLK*n* at any frequency.

- 5. All output specifications are measured from the midpoint voltage of the rising (or for DDR write data, also the falling) edge of L3\_CLK to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load (see Figure 8).

- 6. For DDR, the output data will typically lead the edge of L3\_CLK*n* as shown in Figure 10. For consistency with other output valid time specifications, this will be treated as negative output valid time.

- 7. t<sub>L3\_CLK</sub>/4 is one-fourth the period of L3\_CLKn. This parameter indicates that the specified output signal is actually launched by an internal clock delayed in phase by 90°. Therefore, there is a frequency component to the output valid and output hold times such that the specified output signal will be valid for approximately one L3\_CLK period starting three-fourths of a clock before the edge on which the SRAM will sample it and ending one-fourth of a clock period after the edge it will be sampled.

- 8. Assumes default value of L3OHCR. See Section 5.2.4.1, "Effects of L3OHCR Settings on L3 Bus AC Specifications," for more information.

- 9. L3 I/O voltage mode must be configured by L3VSEL as described in Table 3, and voltage supplied at GV<sub>DD</sub> must match mode selected as specified in Table 4. See Table 22 for revision level information and part marking.

## **Electrical and Thermal Characteristics**

# Table 15. JTAG AC Timing Specifications (Independent of SYSCLK)<sup>1</sup> (continued)

At recommended operating conditions. See Table 4.

| Parameter                                                  | Symbol                                 | Min      | Мах      | Unit | Notes |

|------------------------------------------------------------|----------------------------------------|----------|----------|------|-------|

| Valid times:<br>Boundary-scan data<br>TDO                  | t <sub>JLDV</sub><br>t <sub>JLOV</sub> | 4<br>4   | 20<br>25 | ns   | 4     |

| Output hold times:<br>Boundary-scan data<br>TDO            | t <sub>JLDX</sub><br>t <sub>JLOX</sub> | 30<br>30 |          | ns   | 4     |

| TCK to output high impedance:<br>Boundary-scan data<br>TDO | t <sub>JLDZ</sub><br>t <sub>JLOZ</sub> | 3<br>3   | 19<br>9  | ns   | 4, 5  |

Notes:

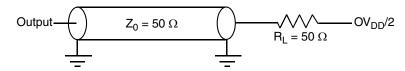

All outputs are measured from the midpoint voltage of the falling/rising edge of TCLK to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load (see Figure 13). Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

2. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

3. Non-JTAG signal input timing with respect to TCK.

4. Non-JTAG signal output timing with respect to TCK.

5. Guaranteed by design and characterization.

Figure 13 provides the AC test load for TDO and the boundary-scan outputs of the MPC7457.

Figure 13. Alternate AC Test Load for the JTAG Interface

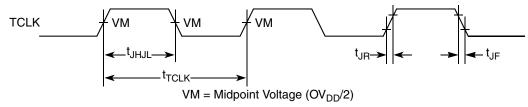

Figure 14 provides the JTAG clock input timing diagram.

Figure 14. JTAG Clock Input Timing Diagram

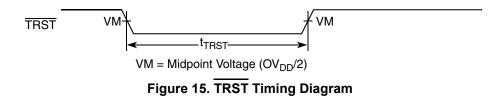

Figure 15 provides the  $\overline{\text{TRST}}$  timing diagram.

**Pin Assignments**

## **Pin Assignments** 6

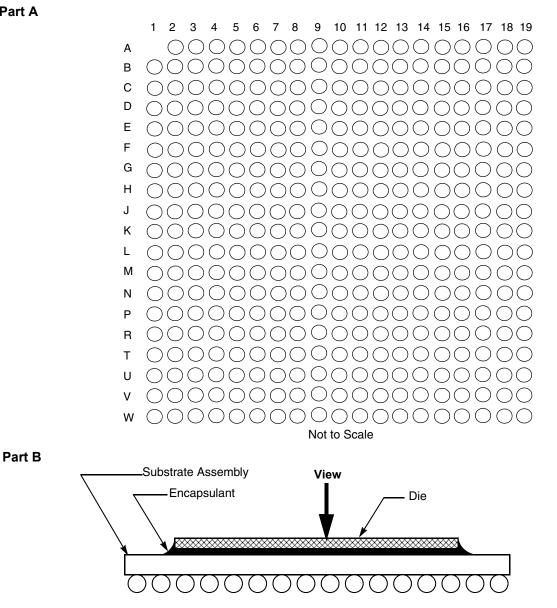

Figure 18 (Part A) shows the pinout of the MPC7447, 360 CBGA package as viewed from the top surface. Part B shows the side profile of the CBGA package to indicate the direction of the top surface view.

Figure 18. Pinout of the MPC7447, 360 CBGA Package as Viewed from the Top Surface

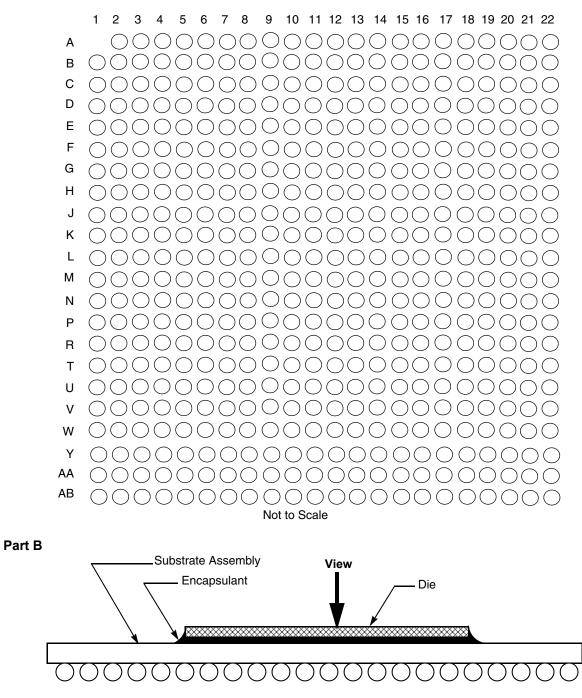

Figure 19 (Part A) shows the pinout of the MPC7457, 483 CBGA package as viewed from the top surface. Part B shows the side profile of the CBGA package to indicate the direction of the top surface view.

Figure 19. Pinout of the MPC7457, 483 CBGA Package as Viewed from the Top Surface

**Pinout Listings**

# 7 Pinout Listings

Table 16 provides the pinout listing for the MPC7447, 360 CBGA package. Table 17 provides the pinout listing for the MPC7457, 483 CBGA package.

# NOTE

This pinout is not compatible with the MPC750, MPC7400, or MPC7410 360 BGA package.

| Signal Name      | Pin Number                                                                                                                                                                                                                                                                                                               | Active | I/O    | I/F Select <sup>1</sup> | Notes |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|-------------------------|-------|

| A[0:35]          | E11, H1, C11, G3, F10, L2, D11, D1, C10, G2, D12, L3,<br>G4, T2, F4, V1, J4, R2, K5, W2, J2, K4, N4, J3, M5, P5,<br>N3, T1, V2, U1, N5, W1, B12, C4, G10, B11                                                                                                                                                            | High   | I/O    | BVSEL                   | 2     |

| AACK             | R1                                                                                                                                                                                                                                                                                                                       | Low    | Input  | BVSEL                   |       |

| AP[0:4]          | C1, E3, H6, F5, G7                                                                                                                                                                                                                                                                                                       | High   | I/O    | BVSEL                   |       |

| ARTRY            | N2                                                                                                                                                                                                                                                                                                                       | Low    | I/O    | BVSEL                   | 3     |

| AV <sub>DD</sub> | A8                                                                                                                                                                                                                                                                                                                       |        | Input  | N/A                     |       |

| BG               | M1                                                                                                                                                                                                                                                                                                                       | Low    | Input  | BVSEL                   |       |

| BMODE0           | G9                                                                                                                                                                                                                                                                                                                       | Low    | Input  | BVSEL                   | 4     |

| BMODE1           | F8                                                                                                                                                                                                                                                                                                                       | Low    | Input  | BVSEL                   | 5     |

| BR               | D2                                                                                                                                                                                                                                                                                                                       | Low    | Output | BVSEL                   |       |

| BVSEL            | В7                                                                                                                                                                                                                                                                                                                       | High   | Input  | BVSEL                   | 1, 6  |

| CI               | J1                                                                                                                                                                                                                                                                                                                       | Low    | Output | BVSEL                   |       |

| CKSTP_IN         | A3                                                                                                                                                                                                                                                                                                                       | Low    | Input  | BVSEL                   |       |

| CKSTP_OUT        | B1                                                                                                                                                                                                                                                                                                                       | Low    | Output | BVSEL                   |       |

| CLK_OUT          | H2                                                                                                                                                                                                                                                                                                                       | High   | Output | BVSEL                   |       |

| D[0:63]          | R15, W15, T14, V16, W16, T15, U15, P14, V13, W13,<br>T13, P13, U14, W14, R12, T12, W12, V12, N11, N10,<br>R11, U11, W11, T11, R10, N9, P10, U10, R9, W10, U9,<br>V9, W5, U6, T5, U5, W7, R6, P7, V6, P17, R19, V18,<br>R18, V19, T19, U19, W19, U18, W17, W18, T16, T18,<br>T17, W3, V17, U4, U8, U7, R7, P6, R8, W8, T8 | High   | I/O    | BVSEL                   |       |

| DBG              | M2                                                                                                                                                                                                                                                                                                                       | Low    | Input  | BVSEL                   |       |

| DP[0:7]          | T3, W4, T4, W9, M6, V3, N8, W6                                                                                                                                                                                                                                                                                           | High   | I/O    | BVSEL                   |       |

| DRDY             | R3                                                                                                                                                                                                                                                                                                                       | Low    | Output | BVSEL                   | 7     |

| DTI[0:3]         | G1, K1, P1, N1                                                                                                                                                                                                                                                                                                           | High   | Input  | BVSEL                   | 8     |

| EXT_QUAL         | A11                                                                                                                                                                                                                                                                                                                      | High   | Input  | BVSEL                   | 9     |

| GBL              | E2                                                                                                                                                                                                                                                                                                                       | Low    | I/O    | BVSEL                   |       |

Table 16. Pinout Listing for the MPC7447, 360 CBGA Package

| Signal Name      | Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Active | I/O    | I/F Select <sup>1</sup> | Notes |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|-------------------------|-------|

| GND              | B5, C3, D6, D13, E17, F3, G17, H4, H7, H9, H11, H13, J6, J8, J10, J12, K7, K3, K9, K11, K13, L6, L8, L10, L12, M4, M7, M9, M11, M13, N7, P3, P9, P12, R5, R14, R17, T7, T10, U3, U13, U17, V5, V8, V11, V15                                                                                                                                                                                                                                                                             | _      | _      | N/A                     |       |

| HIT              | B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Low    | Output | BVSEL                   | 7     |

| HRESET           | D8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Low    | Input  | BVSEL                   |       |

| ĪNT              | D4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Low    | Input  | BVSEL                   |       |

| L1_TSTCLK        | G8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | High   | Input  | BVSEL                   | 9     |

| L2_TSTCLK        | B3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | High   | Input  | BVSEL                   | 10    |

| No Connect       | A6, A13, A14, A15, A16, A17, A18, A19, B13, B14, B15,<br>B16, B17, B18, B19, C13, C14, C15, C16, C17, C18,<br>C19, D14, D15, D16, D17, D18, D19, E12, E13, E14,<br>E15, E16, E19, F12, F13, F14, F15, F16, F17, F18, F19,<br>G11, G12, G13, G14, G15, G16, G19, H14, H15, H16,<br>H17, H18, H19, J14, J15, J16, J17, J18, J19, K15, K16,<br>K17, K18, K19, L14, L15, L16, L17, L18, L19, M14, M15,<br>M16, M17, M18, M19, N12, N13, N14, N15, N16, N17,<br>N18, N19, P15, P16, P18, P19 | _      | _      | _                       | 11    |

| LSSD_MODE        | E8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Low    | Input  | BVSEL                   | 6, 12 |

| MCP              | C9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Low    | Input  | BVSEL                   |       |

| OV <sub>DD</sub> | B4, C2, C12, D5, E18, F2, G18, H3, J5, K2, L5, M3, N6, P2, P8, P11, R4, R13, R16, T6, T9, U2, U12, U16, V4, V7, V10, V14                                                                                                                                                                                                                                                                                                                                                                | _      | _      | N/A                     |       |

| PLL_CFG[0:4]     | B8, C8, C7, D7, A7                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | High   | Input  | BVSEL                   |       |

| PMON_IN          | D9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Low    | Input  | BVSEL                   | 13    |

| PMON_OUT         | А9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Low    | Output | BVSEL                   |       |

| QACK             | G5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Low    | Input  | BVSEL                   |       |

| QREQ             | P4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Low    | Output | BVSEL                   |       |

| SHD[0:1]         | E4, H5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Low    | I/O    | BVSEL                   | 3     |

| SMI              | F9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Low    | Input  | BVSEL                   |       |

| SRESET           | A2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Low    | Input  | BVSEL                   |       |

| SYSCLK           | A10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —      | Input  | BVSEL                   |       |

| TA               | К6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Low    | Input  | BVSEL                   |       |

| TBEN             | E1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | High   | Input  | BVSEL                   |       |

| TBST             | F11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Low    | Output | BVSEL                   |       |

| ТСК              | C6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | High   | Input  | BVSEL                   |       |

| TDI              | В9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | High   | Input  | BVSEL                   | 6     |

| TDO              | A4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | High   | Output | BVSEL                   |       |

# Table 16. Pinout Listing for the MPC7447, 360 CBGA Package (continued)

| Signal Name     | Pin Number                                                                                              | Active | I/O    | I/F Select <sup>1</sup> | Notes |

|-----------------|---------------------------------------------------------------------------------------------------------|--------|--------|-------------------------|-------|

| TDI             | E4                                                                                                      | High   | Input  | BVSEL                   | 7     |

| TDO             | H1                                                                                                      | High   | Output | BVSEL                   |       |

| TEA             | T1                                                                                                      | Low    | Input  | BVSEL                   |       |

| TEST[0:5]       | B10, H6, H10, D8, F9, F8                                                                                | _      | Input  | BVSEL                   | 13    |

| TEST[6]         | A9                                                                                                      | _      | Input  | BVSEL                   | 10    |

| TMS             | К4                                                                                                      | High   | Input  | BVSEL                   | 7     |

| TRST            | C1                                                                                                      | Low    | Input  | BVSEL                   | 7, 16 |

| TS              | P5                                                                                                      | Low    | I/O    | BVSEL                   | 3     |

| TSIZ[0:2]       | L1,H3,D1                                                                                                | High   | Output | BVSEL                   |       |

| TT[0:4]         | F1, F4, K8, A5, E1                                                                                      | High   | I/O    | BVSEL                   |       |

| WT              | L2                                                                                                      | Low    | Output | BVSEL                   |       |

| V <sub>DD</sub> | J9, J11, J13, J15, K10, K12, K14, L9, L11, L13, L15,<br>M10, M12, M14, N9, N11, N13, N15, P10, P12, P14 | _      | —      | N/A                     |       |

| VDD_SENSE[0:1]  | G11, J8                                                                                                 | _      | —      | N/A                     | 17    |

## Table 17. Pinout Listing for the MPC7457, 483 CBGA Package (continued)

Notes:

- 1. OV<sub>DD</sub> supplies power to the processor bus, JTAG, and all control signals except the L3 cache controls (L3CTL[0:1]); GV<sub>DD</sub> supplies power to the L3 cache interface (L3ADDR[0:17], L3DATA[0:63], L3DP[0:7], L3\_ECHO\_CLK[0:3], and L3\_CLK[0:1]) and the L3 control signals L3\_CNTL[0:1]; and V<sub>DD</sub> supplies power to the processor core and the PLL (after filtering to become AV<sub>DD</sub>). For actual recommended value of V<sub>in</sub> or supply voltages, see Table 4.

- 2. Unused address pins must be pulled down to GND.

- 3. These pins require weak pull-up resistors (for example, 4.7 k $\Omega$ ) to maintain the control signals in the negated state after they have been actively negated and released by the MPC7457 and other bus masters.

- 4. This signal selects between MPX bus mode (asserted) and 60x bus mode (negated) and will be sampled at HRESET going high.

- 5. This signal must be negated during reset, by pull up to OV<sub>DD</sub> or negation by ¬HRESET (inverse of HRESET), to ensure proper operation.

- 6. See Table 3 for bus voltage configuration information. If used, pull-down resistors should be less than 250  $\Omega$ .

- 7. Internal pull up on die.

- 8. Ignored in 60x bus mode.

- 9. These signals must be pulled down to GND if unused or if the MPC7457 is in 60x bus mode.

- 10. These input signals for factory use only and must be pulled down to GND for normal machine operation.

- 11. Power must be supplied to GV<sub>DD</sub>, even when the L3 interface is disabled or unused.

- 12. This test signal is recommended to be tied to HRESET; however, other configurations will not adversely affect performance.

- 13. These input signals are for factory use only and must be pulled up to  $OV_{DD}$  for normal machine operation.

- 14. These signals are for factory use only and must be left unconnected for normal machine operation.

- 15. This pin can externally cause a performance monitor event. Counting of the event is enabled via software.

- 16. This signal must be asserted during reset, by pull down to GND or assertion by HRESET, to ensure proper operation.

- 17.These pins are internally connected to V<sub>DD</sub>. They are intended to allow an external device to detect the core voltage level present at the processor core. If unused, they must be connected directly to V<sub>DD</sub> or left unconnected.

Package Description

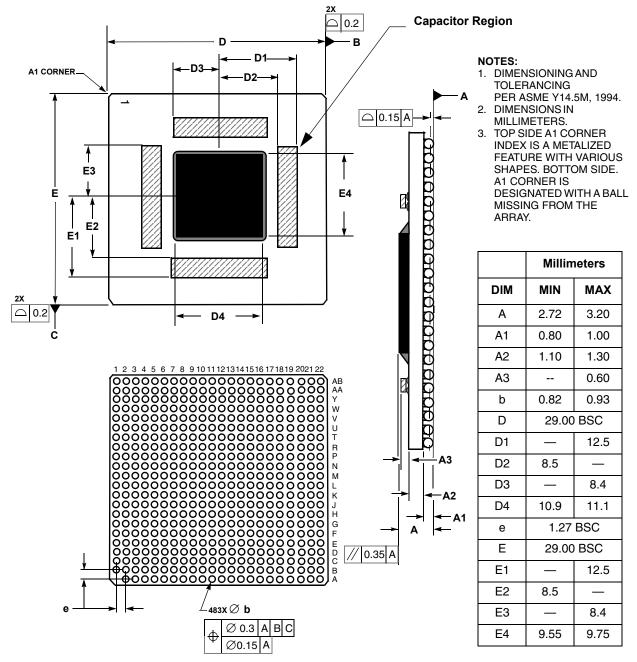

# 8.4 Package Parameters for the MPC7457, 483 CBGA or RoHS BGA

The package parameters are as provided in the following list. The package type is  $29 \times 29$  mm, 483 ceramic ball grid array (CBGA).

| Package outline       | $29 \times 29 \text{ mm}$            |

|-----------------------|--------------------------------------|

| Interconnects         | 483 ( $22 \times 22$ ball array – 1) |

| Pitch                 | 1.27 mm (50 mil)                     |

| Minimum module height | ;                                    |

| Maximum module heigh  | t3.22 mm                             |

| Ball diameter         | 0.89 mm (35 mil)                     |

|                       |                                      |

Package Description

# 8.5 Mechanical Dimensions for the MPC7457, 483 CBGA or RoHS BGA

Figure 22 provides the mechanical dimensions and bottom surface nomenclature for the MPC7457, 483 CBGA package.

Figure 22. Mechanical Dimensions and Bottom Surface Nomenclature for the MPC7457, 483 CBGA or RoHS BGA Package

# System Design Information

|              |                 |                              | Exar          | nple Bus-      | to-Core F      | requency       | in MHz (       | VCO Freq       | uency in l     | MHz)       |

|--------------|-----------------|------------------------------|---------------|----------------|----------------|----------------|----------------|----------------|----------------|------------|

| PLL_CFG[0:4] | Bus-to-<br>Core | Bus-to- Core-to-<br>Core VCO |               |                | Bus            | s (SYSCL       | K) Freque      | ncy            |                |            |

| ·, o[0:4]    | Multiplier      | Multiplier                   | 33.3<br>MHz   | 50<br>MHz      | 66.6<br>MHz    | 75<br>MHz      | 83<br>MHz      | 100<br>MHz     | 133<br>MHz     | 167<br>MHz |

| 01111        | 9x              | 2x                           |               |                | 600<br>(1200)  | 675<br>(1350)  | 747<br>(1494)  | 900<br>(1800)  | 1197<br>(2394) |            |

| 01110        | 9.5x            | 2x                           |               |                | 633<br>(1266)  | 712<br>(1524)  | 789<br>(1578)  | 950<br>(1900)  | 1264<br>(2528) |            |

| 10101        | 10x             | 2x                           |               |                | 667<br>(1333)  | 750<br>(1500)  | 830<br>(1660)  | 1000<br>(2000) |                |            |

| 10001        | 10.5x           | 2x                           |               |                | 700<br>(1400)  | 938<br>(1876)  | 872<br>(1744)  | 1050<br>(2100) |                |            |

| 10011        | 11x             | 2x                           |               |                | 733<br>(1466)  | 825<br>(1650)  | 913<br>(1826)  | 1100<br>(2200) |                |            |

| 00000        | 11.5x           | 2x                           |               |                | 766<br>(532)   | 863<br>(1726)  | 955<br>(1910)  | 1150<br>(2300) |                |            |

| 10111        | 12x             | 2x                           |               | 600<br>(1200)  | 800<br>(1600)  | 900<br>(1800)  | 996<br>(1992)  | 1200<br>(2400) |                |            |

| 11111        | 12.5x           | 2x                           |               | 600<br>(1200)  | 833<br>(1666)  | 938<br>(1876)  | 1038<br>(2076) | 1250<br>(2500) |                |            |

| 01011        | 13x             | 2x                           |               | 650<br>(1300)  | 865<br>(1730)  | 975<br>(1950)  | 1079<br>(2158) |                |                |            |

| 11100        | 13.5x           | 2x                           |               | 675<br>(1350)  | 900<br>(1800)  | 1013<br>(2026) | 1121<br>(2242) |                |                |            |

| 11001        | 14x             | 2x                           |               | 700<br>(1400)  | 933<br>(1866)  | 1050<br>(2100) | 1162<br>(2324) |                |                |            |

| 00011        | 15x             | 2x                           |               | 750<br>(1500)  | 1000<br>(2000) | 1125<br>(2250) | 1245<br>(2490) |                |                |            |

| 11011        | 16x             | 2x                           |               | 800<br>(1600)  | 1066<br>(2132) | 1200<br>(2400) |                |                |                |            |

| 00001        | 17x             | 2x                           |               | 850<br>(1900)  | 1132<br>(2264) |                |                |                |                |            |

| 00101        | 18x             | 2x                           | 600<br>(1200) | 900<br>(1800)  | 1200<br>(2400) |                |                |                |                |            |

| 00111        | 20x             | 2x                           | 667<br>(1334) | 1000<br>(2000) |                |                |                |                |                |            |

| 01001        | 21x             | 2x                           | 700<br>(1400) | 1050<br>(2100) |                |                |                |                |                |            |

| 01101        | 24x             | 2x                           | 800<br>(1600) | 1200<br>(2400) |                |                |                |                |                |            |

| 11101        | 28x             | 2x                           | 933<br>(1866) |                |                |                |                |                |                |            |

| 00110        | PLL b           | ypass                        |               | PLL off,       | SYSCLK         | clocks co      | re circuitry   | directly       |                |            |

# Table 18. MPC7457 Microprocessor PLL Configuration Example for 1267 MHz Parts (continued)

| Core<br>Frequency<br>(MHz) <sup>2</sup> | ÷2  | ÷2.5 | ÷3  | ÷3.5 | ÷4  | ÷4.5 | ÷5  | ÷5.5 | ÷6  | ÷6.5 | ÷7  | ÷7.5 | ÷8  |

|-----------------------------------------|-----|------|-----|------|-----|------|-----|------|-----|------|-----|------|-----|

| 1050                                    | 525 | 420  | 350 | 300  | 263 | 233  | 191 | 191  | 175 | 162  | 150 | 140  | 131 |

| 1100                                    | 550 | 440  | 367 | 314  | 275 | 244  | 200 | 200  | 183 | 169  | 157 | 147  | 138 |

| 1150                                    | 575 | 460  | 383 | 329  | 288 | 256  | 209 | 209  | 192 | 177  | 164 | 153  | 144 |

| 1200                                    | 600 | 480  | 400 | 343  | 300 | 267  | 218 | 218  | 200 | 185  | 171 | 160  | 150 |

| 1250                                    | 638 | 500  | 417 | 357  | 313 | 278  | 227 | 227  | 208 | 192  | 179 | 167  | 156 |

| 1300                                    | 650 | 520  | 433 | 371  | 325 | 289  | 236 | 236  | 217 | 200  | 186 | 173  | 163 |

Notes:

The core and L3 frequencies are for reference only. Note that maximum L3 frequency is design dependent. Some examples

may represent core or L3 frequencies which are not useful, not supported, or not tested for the MPC7457; see Section 5.2.3,

"L3 Clock AC Specifications," for valid L3\_CLK frequencies and for more information regarding the maximum L3 frequency.

2. Not all core frequencies are supported by all speed grades; see Table 8 for minimum and maximum core frequency specifications.

# 9.1.3 System Bus Clock (SYSCLK) and Spread Spectrum Sources

Spread spectrum clock sources are an increasingly popular way to control electromagnetic interference emissions (EMI) by spreading the emitted noise to a wider spectrum and reducing the peak noise magnitude in order to meet industry and government requirements. These clock sources intentionally add long-term jitter in order to diffuse the EMI spectral content. The jitter specification given in Table 8 considers short-term (cycle-to-cycle) jitter only and the clock generator's cycle-to-cycle output jitter should meet the MPC7457 input cycle-to-cycle jitter requirement. Frequency modulation and spread are separate concerns, and the MPC7457 is compatible with spread spectrum sources if the recommendations listed in Table 20 are observed.

# Table 20. Spread Specturm Clock Source Recommendations

At recommended operating conditions. See Table 4.

| Parameter            | Min | Max | Unit | Notes |

|----------------------|-----|-----|------|-------|

| Frequency modulation | —   | 50  | kHz  | 1     |

| Frequency spread     | —   | 1.0 | %    | 1, 2  |

Notes:

1. Guaranteed by design.

2. SYSCLK frequencies resulting from frequency spreading, and the resulting core and VCO frequencies, must meet the minimum and maximum specifications given in Table 8.

It is imperative to note that the processor's minimum and maximum SYSCLK, core, and VCO frequencies must not be exceeded regardless of the type of clock source. Therefore, systems in which the processor is operated at its maximum rated core or bus frequency should avoid violating the stated limits by using down-spreading only.

## **System Design Information**

The  $\overline{QACK}$  signal shown in Figure 26 is usually connected to the PCI bridge chip in a system and is an input to the MPC7457 informing it that it can go into the quiescent state. Under normal operation this occurs during a low-power mode selection. In order for COP to work, the MPC7457 must see this signal asserted (pulled down). While shown on the COP header, not all emulator products drive this signal. If the product does not, a pull-down resistor can be populated to assert this signal. Additionally, some emulator products implement open-drain type outputs and can only drive  $\overline{QACK}$  asserted; for these tools, a pull-up resistor can be implemented to ensure this signal is deasserted when it is not being driven by the tool. Note that the pull-up and pull-down resistors on the  $\overline{QACK}$  signal are mutually exclusive and it is never necessary to populate both in a system. To preserve correct power-down operation,  $\overline{QACK}$  should be merged via logic so that it also can be driven by the PCI bridge.

System Design Information

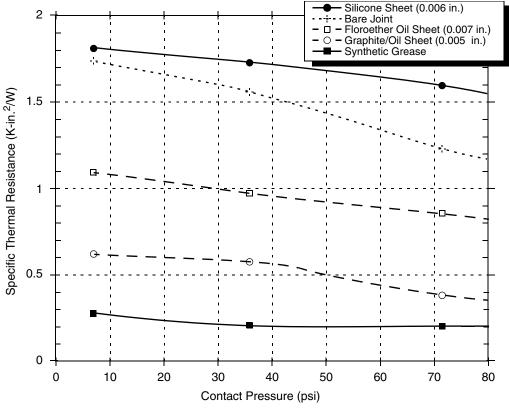

# 9.8.2 Thermal Interface Materials

A thermal interface material is recommended at the package lid-to-heat sink interface to minimize the thermal contact resistance. For those applications where the heat sink is attached by spring clip mechanism, Figure 29 shows the thermal performance of three thin-sheet thermal-interface materials (silicone, graphite/oil, floroether oil), a bare joint, and a joint with thermal grease as a function of contact pressure. As shown, the performance of these thermal interface materials improves with increasing contact pressure. The use of thermal grease significantly reduces the interface thermal resistance. That is, the bare joint results in a thermal resistance approximately seven times greater than the thermal grease joint.

Often, heat sinks are attached to the package by means of a spring clip to holes in the printed-circuit board (see Figure 27). Therefore, the synthetic grease offers the best thermal performance, considering the low interface pressure and is recommended due to the high power dissipation of the MPC7457. Of course, the selection of any thermal interface material depends on many factors—thermal performance requirements, manufacturability, service temperature, dielectric properties, cost, etc.

Figure 29. Thermal Performance of Select Thermal Interface Material

The board designer can choose between several types of thermal interface. Heat sink adhesive materials should be selected based on high conductivity, yet adequate mechanical strength to meet equipment shock/vibration requirements. There are several commercially available thermal interfaces and adhesive materials provided by the following vendors:

| The Bergquist Company<br>18930 West 78 <sup>th</sup> St.<br>Chanhassen, MN 55317<br>Internet: www.bergquistcompany.com                 | 800-347-4572 |

|----------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Chomerics, Inc.<br>77 Dragon Ct.<br>Woburn, MA 01888-4014<br>Internet: www.chomerics.com                                               | 781-935-4850 |

| Dow-Corning Corporation<br>Dow-Corning Electronic Materials<br>2200 W. Salzburg Rd.<br>Midland, MI 48686-0997<br>Internet: www.dow.com | 800-248-2481 |

| Shin-Etsu MicroSi, Inc.<br>10028 S. 51st St.<br>Phoenix, AZ 85044<br>Internet: www.microsi.com                                         | 888-642-7674 |

| Thermagon Inc.<br>4707 Detroit Ave.<br>Cleveland, OH 44102<br>Internet: www.thermagon.com                                              | 888-246-9050 |

The following section provides a heat sink selection example using one of the commercially available heat sinks.

# 9.8.3 Heat Sink Selection Example

For preliminary heat sink sizing, the die-junction temperature can be expressed as follows:

$$T_i = T_I + T_r + (R_{\theta JC} + R_{\theta int} + R_{\theta sa}) \times P_d$$

where:

T<sub>i</sub> is the die-junction temperature

T<sub>I</sub> is the inlet cabinet ambient temperature

$T_r$  is the air temperature rise within the computer cabinet

$R_{\theta JC}$  is the junction-to-case thermal resistance

$R_{\theta int}$  is the adhesive or interface material thermal resistance

$R_{\theta sa}$  is the heat sink base-to-ambient thermal resistance

P<sub>d</sub> is the power dissipated by the device

During operation, the die-junction temperatures  $(T_j)$  should be maintained less than the value specified in Table 4. The temperature of air cooling the component greatly depends on the ambient inlet air temperature and the air temperature rise within the electronic cabinet. An electronic cabinet inlet-air temperature  $(T_a)$  may range from 30° to 40°C. The air temperature rise within a cabinet  $(T_r)$  may be in the range of 5° to 10°C. The thermal resistance of the thermal interface material ( $R_{\theta int}$ ) is typically about 1.5°C/W. For

| MC                     | 74x7               | XX                         | nnnn                                | L                               | X                       |

|------------------------|--------------------|----------------------------|-------------------------------------|---------------------------------|-------------------------|

| Product<br>Code        | Part<br>Identifier | Package                    | Processor<br>Frequency <sup>1</sup> | Application<br>Modifier         | Revision Level          |

| PPC <sup>2</sup><br>MC | 7457<br>7447       | RX = CBGA                  | 867<br>1000<br>1200<br>1267         | L: 1.3 V ± 50 mV<br>0° to 105°C | B: 1.1; PVR = 8002 0101 |

| MC                     | 7457               | RX = CBGA<br>VG = RoHS BGA | 867<br>1000<br>1200<br>1267         |                                 | C: 1.2; PVR = 8002 0102 |

| Table 22 | Part | Numbering | Nomenclature |

|----------|------|-----------|--------------|

|----------|------|-----------|--------------|

Notes:

1. Processor core frequencies supported by parts addressed by this specification only. Parts addressed by a hardware specification addendum may support other maximum core frequencies.

2. The P prefix in a Freescale part number designates a "Pilot Production Prototype" as defined by Freescale SOP 3-13. These parts have only preliminary reliability and characterization data. Before pilot production prototypes may be shipped, written authorization from the customer must be on file in the applicable sales office acknowledging the qualification status and the fact that product changes may still occur while shipping pilot production prototypes.

# 10.2 Part Numbers Not Fully Addressed by This Document

Parts with application modifiers or revision levels not fully addressed are described in a separate addendum, which supplement and supersede this hardware specification. As such parts are released, these specifications will be listed in this section.

# Table 23. Part Numbers Addressed by MPC74x7RXnnnnNx Series Hardware Specifications Addendum (Document Order No. MPC7457ECS01AD)

| MC              | 74x7               | XX                         | nnnn                      | Ν                               | X                       |

|-----------------|--------------------|----------------------------|---------------------------|---------------------------------|-------------------------|

| Product<br>Code | Part<br>Identifier | Package                    | Processor<br>Frequency    | Application<br>Modifier         | Revision Level          |

| PPC             | 7457               | RX = CBGA                  | 1000<br>867<br>733<br>600 | N: 1.1 V ± 50 mV<br>0° to 105°C | B: 1.1; PVR = 8002 0101 |

|                 | 7447               |                            | 1000<br>867               |                                 |                         |

| MC              | 7447               |                            | 1000<br>867<br>733<br>600 |                                 | B: 1.1; PVR = 8002 0101 |

|                 | 7457               | RX = CBGA<br>VG = RoHS BGA | 1000<br>867<br>733<br>600 |                                 | C: 1.2; PVR = 8002 0102 |

**Document Revision History**

# **11** Document Revision History

Table 26 provides a revision history for this hardware specification.

# Table 26. Document Revision History

| Revision<br>Number | Date       | Substantive Change(s)                                                                                                                                                                                                 |  |

|--------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 8                  | 04/09/2013 | Updated template.<br>Updated Table 14 "L3 Bus Interface AC Timing Specifications for PB2 and Late Write SRAMs".<br>Moved Revision History to the end of the document.                                                 |  |

| 7                  | 3/28/2006  | Updated template.<br>Section 2, reworded L1 and L2 cache descriptions.<br>Removed note references for CI and WT in Table 12.<br>Added VG package signifier for 7457 only.                                             |  |

| 6                  | 7/22/2005  | Revised Note in Section 9.2.                                                                                                                                                                                          |  |

|                    |            | Added heat sink vendor to list in Section 9.8.                                                                                                                                                                        |  |

|                    |            | Corrected bump and underfill model dimension in Section 9.8.3.                                                                                                                                                        |  |

| 5                  | 9/9/2004   | Updated document to new Freescale template.                                                                                                                                                                           |  |

|                    |            | Updated section numbering and changed reference from part number specifications to addendums.                                                                                                                         |  |

|                    |            | Added Rev. 1.2 devices, including increased L3 clock max frequency to 250 MHz and improved L3 AC timing.                                                                                                              |  |

|                    |            | Table 5: Added CTE information.                                                                                                                                                                                       |  |

|                    |            | Table 8: Modified jitter specifications to conform to JEDEC standards, changed jitter specification to cycle-to-cycle jitter (instead of long- and short-term jitter); changed jitter bandwidth recommendations.      |  |

|                    |            | Table 13: Deleted note 9 and renumbered.                                                                                                                                                                              |  |

|                    |            | Table 14: Deleted note 5 and renumbered.                                                                                                                                                                              |  |

|                    |            | Table 17: Revised note 6.                                                                                                                                                                                             |  |

|                    |            | Added Section 9.1.3.                                                                                                                                                                                                  |  |

|                    |            | Section 9.2: Changed filter resistor recommendations. Recommend 10 $\Omega$ resistor for all production devices, including production Rev. 1.1 devices. 400 $\Omega$ resistor needed only for early Rev. 1.1 devices. |  |

|                    |            | Table 22: Reversed the order of revision numbers.                                                                                                                                                                     |  |

|                    |            | Added Tables 25 and 26.                                                                                                                                                                                               |  |

| 4.1                |            | Section 9.1.1: Corrected note regarding different PLL configurations for earlier devices; all MPC7457 devices to date conform to this table.                                                                          |  |

|                    |            | Section 9.6: Added information about unused L3_ADDR signals.                                                                                                                                                          |  |

|                    |            | Table 24: Changed title to include document order information for MPC74x7RXnnnnNx series part number specification.                                                                                                   |  |

| Revision<br>Number | Date | Substantive Change(s)                                                                                                                                                                                                  |

|--------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4                  |      | Table 9: Corrected pin lists for input and output AC timing to correctly show HIT as an output-only signal                                                                                                             |

|                    |      | Added specifications for 1267 MHz devices; removed specs for 1300 MHz devices.                                                                                                                                         |

|                    |      | Section 5.2.3: Changed recommendations regarding use of L3 clock jitter in AC timing analysis. The L3 jitter is now fully comprehended in the AC timing specs and does not need to be included in the timing analysis. |

| 3                  |      | Corrected numerous errors in lists of pins associated with $t_{KHOV}$ , $t_{KHOX}$ , $t_{IVKH}$ , and $t_{IXKH}$ in Table 9.                                                                                           |

|                    |      | Added support for 1.5 V L3 interface voltage; issues fixed in Rev. 1.1.                                                                                                                                                |

|                    |      | Corrected typos in Table 12.                                                                                                                                                                                           |

|                    |      | Added data to Table 2.                                                                                                                                                                                                 |

|                    |      | Clarified address bus pull-up resistor recommendations in Section 1.9.6.                                                                                                                                               |

|                    |      | Modified Table 9, Figure 5, and Figure 6 to more accurately show when the mode select inputs (BMODE[0:1], L3VSEL, BVSEL) are sampled and AC timing requirements                                                        |

|                    |      | Table 10: Added skew and jitter values.                                                                                                                                                                                |

|                    |      | Table 14: Added AC timing values.                                                                                                                                                                                      |

|                    |      | Table 24: Updated to reflect past and current part numbers not fully covered by this document.                                                                                                                         |

|                    |      | Table 6: Removed $CV_{IH}$ and $CV_{IL}$ ; $V_{IH}$ and $V_{IL}$ for SYSCLK input is the same as for other input signals, and is now noted accordingly in this table.                                                  |

|                    |      | Table 7: Removed Doze mode power entry (but left footnote 4 for clarity); documentation change only.                                                                                                                   |

|                    |      | Nontechnical formatting                                                                                                                                                                                                |

| 2                  |      | Added substrate capacitor information in Sections 1.8.3 and 1.8.6.                                                                                                                                                     |

|                    |      | Increased minimum processor and VCO frequencies in Table 8 from 500 and 1000 MHz to 600 and 1200 MHz (respectively).                                                                                                   |

|                    |      | Corrected maximum processor frequency for 1300 MHz devices in Table 8 (changed from 1333 to 1300 MHz).                                                                                                                 |

|                    |      | Added value for to t <sub>L3CSKW1</sub> Table 10.                                                                                                                                                                      |

|                    |      | Added L3OHCR information in Section 1.5.2.4.1.                                                                                                                                                                         |

|                    |      | Added values for $t_{CO}$ and $t_{ECI}$ to Table 11.                                                                                                                                                                   |

|                    |      | Added Note 8 to Table 13 and Note 6 to Table 14.                                                                                                                                                                       |

|                    |      | Changed resistor value in PLL filter in Figure 25 from 10 $\Omega$ to 400 $\Omega$ .                                                                                                                                   |

|                    |      | Added 867 MHz speed grade.                                                                                                                                                                                             |

|                    |      | Corrected Product Code in Tables 22 and 23.                                                                                                                                                                            |

|                    |      | Added pull-up/pull-down recommendations for CKSTP_IN and PLL_CFG[0:4] to Section 1.9.6.                                                                                                                                |

| 1.1                |      | Nontechnical reformatting.                                                                                                                                                                                             |

**Document Revision History**

| Revision<br>Number | Date | Substantive Change(s)                                                                                                              |

|--------------------|------|------------------------------------------------------------------------------------------------------------------------------------|

| 1                  |      | Removed support for 1.5 V L3 interface voltage from Tables 3 and 4. 1.5 V I/O voltage is not supported in current MPC7457 devices. |

|                    |      | Added package thermal characteristics values to Table 5, made minor revisions to Section 1.9.8.                                    |

|                    |      | Added preliminary AC timing values to Tables 10 and 12.                                                                            |

|                    |      | Added footnotes to Table 17.                                                                                                       |

| 0                  |      | Initial release.                                                                                                                   |

# Table 26. Document Revision History (continued)

#### How to Reach Us:

Home Page: www.freescale.com Web Support: http://www.freescale.com/support

## USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductors products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claims alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-complaint and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

©2004-2013 Freescale Semiconductor, Inc.

Document Number: MPC7457EC Rev. 8 04/2013