### NXP USA Inc. - MC9S08GB32CFU Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 40MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                            |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 56                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                |                                                                       |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | A/D 8x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08gb32cfu |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **List of Chapters**

| Chapter 1  | Introduction                                 | 17    |

|------------|----------------------------------------------|-------|

| Chapter 2  | Pins and Connections                         | 23    |

| Chapter 3  | Modes of Operation                           | 33    |

| Chapter 4  | Memory                                       | 39    |

| Chapter 5  | Resets, Interrupts, and System Configuration | 61    |

| Chapter 6  | Parallel Input/Output                        | 77    |

| Chapter 7  | Internal Clock Generator (ICG) Module        | 97    |

| Chapter 8  | Central Processor Unit (CPU)                 | .125  |

| Chapter 9  | Keyboard Interrupt (KBI) Module              | .145  |

| Chapter 10 | Timer/PWM (TPM) Module                       | . 151 |

| Chapter 11 | Serial Communications Interface (SCI) Module | . 167 |

| Chapter 12 | Serial Peripheral Interface (SPI) Module     | . 187 |

| Chapter 13 | Inter-Integrated Circuit (IIC) Module        | .203  |

| Chapter 14 | Analog-to-Digital Converter (ATD) Module     | .219  |

| Chapter 15 | Development Support                          | .235  |

| Appendix A | Electrical Characteristics                   | .259  |

| Appendix B | Ordering Information and Mechanical Drawings | .281  |

# **Chapter 1 Introduction**

# 1.1 Overview

The MC9S08GB/GT are members of the low-cost, high-performance HCS08 Family of 8-bit microcontroller units (MCUs). All MCUs in the family use the enhanced HCS08 core and are available with a variety of modules, memory sizes, memory types, and package types.

# 1.2 Features

Features have been organized to reflect:

- Standard features of the HCS08 Family

- Features of the MC9S08GB/GT MCU

## 1.2.1 Standard Features of the HCS08 Family

- 40-MHz HCS08 CPU (central processor unit)

- HC08 instruction set with added BGND instruction

- Background debugging system (see also Chapter 15, "Development Support")

- Breakpoint capability to allow single breakpoint setting during in-circuit debugging (plus two more breakpoints in on-chip debug module)

- Debug module containing two comparators and nine trigger modes. Eight deep FIFO for storing change-of-flow addresses and event-only data. Debug module supports both tag and force breakpoints.

- Support for up to 32 interrupt/reset sources

- Power-saving modes: wait plus three stops

- System protection features:

- Optional computer operating properly (COP) reset

- Low-voltage detection with reset or interrupt

- Illegal opcode detection with reset

- Illegal address detection with reset (some devices don't have illegal addresses)

## 1.2.2 Features of MC9S08GB/GT Series of MCUs

- On-chip in-circuit programmable FLASH memory with block protection and security options (see Table 1-1 for device specific information)

- On-chip random-access memory (RAM) (see Table 1-1 for device specific information)

- 8-channel, 10-bit analog-to-digital converter (ATD)

- Two serial communications interface modules (SCI)

- Serial peripheral interface module (SPI)

MC9S08GB/GT Data Sheet, Rev. 2.3

# NOTE

To avoid extra current drain from floating input pins, the reset initialization routine in the application program should either enable on-chip pullup devices or change the direction of unused pins to outputs so the pins do not float.

For information about controlling these pins as general-purpose I/O pins, see Chapter 6, "Parallel Input/Output." For information about how and when on-chip peripheral systems use these pins, refer to the appropriate section from Table 2-1.

| Port Pins                    | Alternate<br>Function           | Reference <sup>1</sup>                                     |

|------------------------------|---------------------------------|------------------------------------------------------------|

| PTA7-PTA0                    | KBI1P7–KBI1P0                   | Chapter 2, "Pins and Connections"                          |

| PTB7–PTB0                    | AD1P7–AD1P0                     | Chapter 14, "Analog-to-Digital Converter (ATD) Module"     |

| PTC7–PTC4                    | _                               | Chapter 6, "Parallel Input/Output"                         |

| PTC3-PTC2                    | SCL1-SDA1                       | Chapter 13, "Inter-Integrated Circuit (IIC) Module"        |

| PTC1-PTC0                    | RxD2–TxD2                       | Chapter 11, "Serial Communications Interface (SCI) Module" |

| PTD7–PTD3                    | TPM2CH4–<br>TPM2CH0             | Chapter 10, "Timer/PWM (TPM) Module"                       |

| PTD2-PTD0                    | TPM1CH2–<br>TPM1CH0             | Chapter 10, "Timer/PWM (TPM) Module"                       |

| PTE7–PTE6                    | _                               | Chapter 6, "Parallel Input/Output"                         |

| PTE5<br>PTE4<br>PTE3<br>PTE2 | SPSCK1<br>MISO1<br>MOSI1<br>SS1 | Chapter 12, "Serial Peripheral Interface (SPI) Module"     |

| PTE1-PTE0                    | RxD1–TxD1                       | Chapter 11, "Serial Communications Interface (SCI) Module" |

| PTF7–PTF0                    | —                               | Chapter 6, "Parallel Input/Output"                         |

| PTG7–PTG3                    | —                               | Chapter 6, "Parallel Input/Output"                         |

| PTG2-PTG1                    | EXTAL-XTAL                      | Chapter 7, "Internal Clock Generator (ICG) Module"         |

| PTG0                         | BKGD/MS                         | Chapter 15, "Development Support"                          |

<sup>1</sup> See this section for information about modules that share these pins.

When an on-chip peripheral system is controlling a pin, data direction control bits still determine what is read from port data registers even though the peripheral module controls the pin direction by controlling the enable for the pin's output buffer. See Chapter 6, "Parallel Input/Output" for details.

Pullup enable bits for each input pin control whether on-chip pullup devices are enabled whenever the pin is acting as an input even if it is being controlled by an on-chip peripheral module. When the PTA7–PTA4 pins are controlled by the KBI module and are configured for rising-edge/high-level sensitivity, the pullup enable control bits enable pulldown devices rather than pullup devices. Similarly, when IRQ is configured

# **Chapter 4 Memory**

# 4.1 MC9S08GB/GT Memory Map

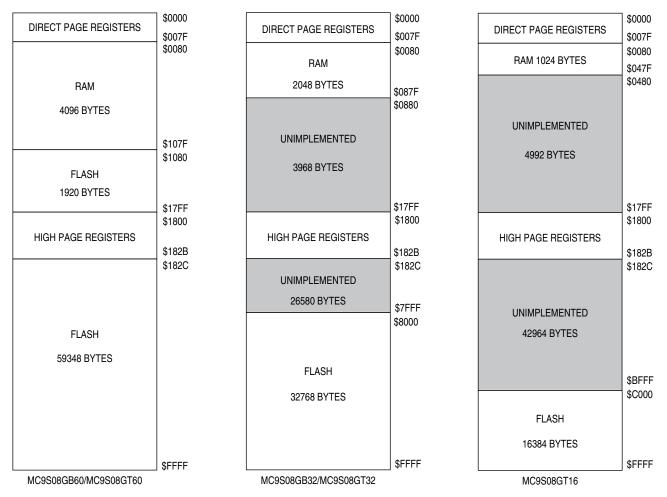

As shown in Figure 4-1, on-chip memory in the MC9S08GB/GT series of MCUs consists of RAM, FLASH program memory for nonvolatile data storage, plus I/O and control/status registers. The registers are divided into three groups:

- Direct-page registers (\$0000 through \$007F)

- High-page registers (\$1800 through \$182B)

- Nonvolatile registers (\$FFB0 through \$FFBF)

Figure 4-1. MC9S08GB/GT Memory Map

# 4.1.1 Reset and Interrupt Vector Assignments

Table 4-1 shows address assignments for reset and interrupt vectors. The vector names shown in this table are the labels used in the Freescale-provided equate file for the MC9S08GB/GT. For more details about

|        | Bit 7                                                                        | 6     | 5    | 4    | 3    | 2 | 1 | Bit 0 |  |  |

|--------|------------------------------------------------------------------------------|-------|------|------|------|---|---|-------|--|--|

| Read:  | FPOPEN                                                                       | FPDIS | FPS2 | FPS1 | FPS0 | 0 | 0 | 0     |  |  |

| Write: | 1                                                                            | (1)   | (1)  | (1)  | (1)  |   |   |       |  |  |

| Reset: | eset: This register is loaded from nonvolatile location NVPROT during reset. |       |      |      |      |   |   |       |  |  |

|        |                                                                              | 1     |      |      |      |   |   |       |  |  |

= Unimplemented or Reserved

<sup>1</sup> Background commands can be used to change the contents of these bits in FPROT.

### Figure 4-7. FLASH Protection Register (FPROT)

FPOPEN — Open Unprotected FLASH for Program/Erase

1 = Any FLASH location, not otherwise block protected or secured, may be erased or programmed. 0 = Entire FLASH memory is block protected (no program or erase allowed).

FPDIS — FLASH Protection Disable

1 = No FLASH block is protected.

0 = FLASH block specified by FPS2:FPS0 is block protected (program and erase not allowed).

FPS2:FPS1:FPS0 — FLASH Protect Size Selects

When FPDIS = 0, this 3-bit field determines the size of a protected block of FLASH locations at the high address end of the FLASH (see Table 4-8). Protected FLASH locations cannot be erased or programmed.

| Table 4-8 | . High | Address | Protected | Block |

|-----------|--------|---------|-----------|-------|

|-----------|--------|---------|-----------|-------|

| FPS2:FPS1:FPS0 | Protected Address Range | Protected Block Size | Redirected Vectors <sup>1</sup> |

|----------------|-------------------------|----------------------|---------------------------------|

| 0:0:0          | \$FE00-\$FFFF           | 512 bytes            | \$FDC0-\$FDFD <sup>2</sup>      |

| 0:0:1          | \$FC00-\$FFFF           | 1024 bytes           | \$FBC0\$FBFD                    |

| 0:1:0          | \$F800-\$FFFF           | 2048 bytes           | \$F7C0-\$F7FD                   |

| 0:1:1          | \$F000-\$FFFF           | 4096 bytes           | \$EFC0-\$EFFD                   |

| 1:0:0          | \$E000-\$FFFF           | 8192 bytes           | \$DFC0\$DFFD                    |

| 1:0:1          | \$C000-\$FFFF           | 16384 bytes          | \$BFC0-\$BFFD <sup>3</sup>      |

| 1:1:0          | \$8000-\$FFFF           | 32768 bytes          | \$7FC0-\$7FFD <sup>4</sup>      |

| 1:1:1          | \$8000-\$FFFF           | 32768 bytes          | \$7FC0-\$7FFD <sup>4</sup>      |

<sup>1</sup> No redirection if FPOPEN = 0, or FNORED = 1.

<sup>2</sup> Reset vector is not redirected.

<sup>3</sup> 32K and 60K devices only.

<sup>4</sup> 60K devices only.

|                    | Bit 7 | 6                                                             | 5   | 4    | 3 | 2   | 1   | Bit 0 |  |  |

|--------------------|-------|---------------------------------------------------------------|-----|------|---|-----|-----|-------|--|--|

| Read:              | POR   | PIN                                                           | COP | ILOP | 0 | ICG | LVD | 0     |  |  |

| Write:             |       | Writing any value to SIMRS address clears COP watchdog timer. |     |      |   |     |     |       |  |  |

| Power-on reset:    | 1     | 0                                                             | 0   | 0    | 0 | 0   | 1   | 0     |  |  |

| Low-voltage reset: | U     | 0                                                             | 0   | 0    | 0 | 0   | 1   | 0     |  |  |

| Any other reset:   | 0     | 1                                                             | (1) | (1)  | 0 | (1) | 0   | 0     |  |  |

U = Unaffected by reset

<sup>1</sup> Any of these reset sources that are active at the time of reset will cause the corresponding bit(s) to be set; bits corresponding to sources that are not active at the time of reset will be cleared.

#### Figure 5-3. System Reset Status (SRS)

POR — Power-On Reset

Reset was caused by the power-on detection logic. Because the internal supply voltage was ramping up at the time, the low-voltage reset (LVD) status bit is also set to indicate that the reset occurred while the internal supply was below the LVD threshold.

1 = POR caused reset.

0 =Reset not caused by POR.

#### PIN — External Reset Pin

Reset was caused by an active-low level on the external reset pin.

1 = Reset came from external reset pin.

0 = Reset not caused by external reset pin.

#### COP — Computer Operating Properly (COP) Watchdog

Reset was caused by the COP watchdog timer timing out. This reset source may be blocked by COPE = 0.

1 = Reset caused by COP timeout.

0 =Reset not caused by COP timeout.

ILOP — Illegal Opcode

Reset was caused by an attempt to execute an unimplemented or illegal opcode. The STOP instruction is considered illegal if stop is disabled by STOPE = 0 in the SOPT register. The BGND instruction is considered illegal if active background mode is disabled by ENBDM = 0 in the BDCSC register.

1 =Reset caused by an illegal opcode.

0 =Reset not caused by an illegal opcode.

ICG — Internal Clock Generation Module Reset

Reset was caused by an ICG module reset.

1 = Reset caused by ICG module.

0 =Reset not caused by ICG module.

#### Chapter 5 Resets, Interrupts, and System Configuration

LVDV — Low-Voltage Detect Voltage Select

The LVDV bit selects the LVD trip point voltage (V<sub>LVD</sub>).

1 = High trip point selected ( $V_{LVD} = V_{LVDH}$ ).

$0 = \text{Low trip point selected } (V_{LVD} = V_{LVDL}).$

LVWV — Low-Voltage Warning Voltage Select

The LVWV bit selects the LVW trip point voltage ( $V_{LVW}$ ).

1 = High trip point selected ( $V_{LVW} = V_{LVWH}$ ).

$0 = \text{Low trip point selected } (V_{LVW} = V_{LVWL}).$

PPDF — Partial Power Down Flag

The PPDF bit indicates that the MCU has exited the stop2 mode.

1 =Stop2 mode recovery.

0 = Not stop2 mode recovery.

PPDACK — Partial Power Down Acknowledge

Writing a 1 to PPDACK clears the PPDF bit.

PDC — Power Down Control

The write-once PDC bit controls entry into the power down (stop2 and stop1) modes.

1 = Power down modes are enabled.

0 = Power down modes are disabled.

PPDC — Partial Power Down Control

The write-once PPDC bit controls which power down mode, stop1 or stop2, is selected.

1 = Stop2, partial power down, mode enabled if PDC set.

0 =Stop1, full power down, mode enabled if PDC set.

**Central Processor Unit (CPU)**

#### 8.3.3 Stack Pointer (SP)

This 16-bit address pointer register points at the next available location on the automatic last-in-first-out (LIFO) stack. The stack may be located anywhere in the 64-Kbyte address space that has RAM and can be any size up to the amount of available RAM. The stack is used to automatically save the return address for subroutine calls, the return address and CPU registers during interrupts, and for local variables. The AIS (add immediate to stack pointer) instruction adds an 8-bit signed immediate value to SP. This is most often used to allocate or deallocate space for local variables on the stack.

SP is forced to \$00FF at reset for compatibility with the earlier M68HC05 Family. HCS08 programs normally change the value in SP to the address of the last location (highest address) in on-chip RAM during reset initialization to free up direct page RAM (from the end of the on-chip registers to \$00FF).

The RSP (reset stack pointer) instruction was included for compatibility with the M68HC05 Family and is seldom used in new HCS08 programs because it only affects the low-order half of the stack pointer.

#### 8.3.4 **Program Counter (PC)**

The program counter is a 16-bit register that contains the address of the next instruction or operand to be fetched.

During normal program execution, the program counter automatically increments to the next sequential memory location every time an instruction or operand is fetched. Jump, branch, interrupt, and return operations load the program counter with an address other than that of the next sequential location. This is called a change-of-flow.

During reset, the program counter is loaded with the reset vector that is located at \$FFFE and \$FFFF. The vector stored there is the address of the first instruction that will be executed after exiting the reset state.

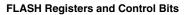

#### 8.3.5 Condition Code Register (CCR)

The 8-bit condition code register contains the interrupt mask (I) and five flags that indicate the results of the instruction just executed. Bits 6 and 5 are set permanently to 1. The following paragraphs describe the functions of the condition code bits in general terms. For a more detailed explanation of how each instruction sets the CCR bits, refer to the HCS08 Family Reference Manual, volume 1, Freescale Semiconductor document order number HCS08RMv1/D.

MC9S08GB/GT Data Sheet, Rev. 2.3

V — Two's Complement Overflow Flag

The CPU sets the overflow flag when a two's complement overflow occurs. The signed branch instructions BGT, BGE, BLE, and BLT use the overflow flag.

1 = Overflow

0 = No overflow

H — Half-Carry Flag

The CPU sets the half-carry flag when a carry occurs between accumulator bits 3 and 4 during an add-without-carry (ADD) or add-with-carry (ADC) operation. The half-carry flag is required for binary-coded decimal (BCD) arithmetic operations. The DAA instruction uses the states of the H and C condition code bits to automatically add a correction value to the result from a previous ADD or ADC on BCD operands to correct the result to a valid BCD value.

1 = Carry between bits 3 and 4

0 =No carry between bits 3 and 4

I — Interrupt Mask Bit

When the interrupt mask is set, all maskable CPU interrupts are disabled. CPU interrupts are enabled when the interrupt mask is cleared. When a CPU interrupt occurs, the interrupt mask is set automatically after the CPU registers are saved on the stack, but before the first instruction of the interrupt service routine is executed.

1 = Interrupts disabled

0 =Interrupts enabled

Interrupts are not recognized at the instruction boundary after any instruction that clears I (CLI or TAP). This ensures that the next instruction after a CLI or TAP will always be executed without the possibility of an intervening interrupt, provided I was set.

### N — Negative Flag

The CPU sets the negative flag when an arithmetic operation, logic operation, or data manipulation produces a negative result, setting bit 7 of the result. Simply loading or storing an 8-bit or 16-bit value causes N to be set if the most significant bit of the loaded or stored value was 1.

1 = Negative result

0 = Non-negative result

### Z — Zero Flag

The CPU sets the zero flag when an arithmetic operation, logic operation, or data manipulation produces a result of \$00 or \$0000. Simply loading or storing an 8-bit or 16-bit value causes Z to be set if the loaded or stored value was all 0s.

1 =Zero result

0 =Non-zero result

C — Carry/Borrow Flag

The CPU sets the carry/borrow flag when an addition operation produces a carry out of bit 7 of the accumulator or when a subtraction operation requires a borrow. Some instructions — such as bit test and branch, shift, and rotate — also clear or set the carry/borrow flag.

1 = Carry out of bit 7

0 =No carry out of bit 7

**Central Processor Unit (CPU)**

*rel* — Any label or expression that refers to an address that is within –128 to +127 locations from the next address after the last byte of object code for the current instruction. The assembler will calculate the 8-bit signed offset and include it in the object code for this instruction.

### **Address modes**

| INH  | = | Inherent (no operands)                                       |

|------|---|--------------------------------------------------------------|

| IMM  | = | 8-bit or 16-bit immediate                                    |

| DIR  | = | 8-bit direct                                                 |

| EXT  | = | 16-bit extended                                              |

| IX   | = | 16-bit indexed no offset                                     |

| IX+  | = | 16-bit indexed no offset, post increment (CBEQ and MOV only) |

| IX1  | = | 16-bit indexed with 8-bit offset from H:X                    |

| IX1+ | = | 16-bit indexed with 8-bit offset, post increment             |

|      |   | (CBEQ only)                                                  |

| IX2  | = | 16-bit indexed with 16-bit offset from H:X                   |

| REL  | = | 8-bit relative offset                                        |

| SP1  | = | Stack pointer with 8-bit offset                              |

SP2 = Stack pointer with 16-bit offset

### Table 8-1. HCS08 Instruction Set Summary (Sheet 1 of 7)

| Source                                                                                                                    | Operation                                                  | Description                                                        |   |   | Effect<br>on CCF |   |   |   | Address<br>Mode                                     | Opcode                                           | Operand                             | Cycles <sup>1</sup>             |

|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------|---|---|------------------|---|---|---|-----------------------------------------------------|--------------------------------------------------|-------------------------------------|---------------------------------|

| Form                                                                                                                      | Operation                                                  |                                                                    |   |   | I                | N | z | с | Add<br>Mo                                           | Opc                                              | Ореі                                | Bus C                           |

| ADC #opr8i<br>ADC opr8a<br>ADC opr16a<br>ADC oprx16,X<br>ADC oprx8,X<br>ADC ,X<br>ADC ,X<br>ADC oprx16,SP<br>ADC oprx8,SP | Add with Carry                                             | A ← (A) + (M) + (C)                                                |   |   | _                |   |   |   | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | C9<br>D9                                         | dd<br>hh II<br>ee ff<br>ff<br>ee ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 |

| ADD #opr8i<br>ADD opr8a<br>ADD opr16a<br>ADD oprx16,X<br>ADD oprx8,X<br>ADD ,X<br>ADD oprx16,SP<br>ADD oprx8,SP           | Add without Carry                                          | A ← (A) + (M)                                                      |   |   | _                |   |   |   | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | AB<br>BB<br>CB<br>DB<br>EB<br>FB<br>9EDB<br>9EEB | dd<br>hh II<br>ee ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>5<br>4 |

| AIS #opr8i                                                                                                                | Add Immediate Value<br>(Signed) to Stack Pointer           | $SP \leftarrow (SP) + (M)$<br>M is sign extended to a 16-bit value | - | - | -                | - | - | - | IMM                                                 | A7                                               | ii                                  | 2                               |

| AIX #opr8i                                                                                                                | Add Immediate Value<br>(Signed) to Index<br>Register (H:X) | H:X ← (H:X) + (M)<br>M is sign extended to a 16-bit value          | - | - | -                | - | - | - | ІММ                                                 | AF                                               | ii                                  | 2                               |

| AND #opr8i<br>AND opr8a<br>AND opr16a<br>AND oprx16,X<br>AND oprx8,X<br>AND ,X<br>AND oprx16,SP<br>AND oprx8,SP           | Logical AND                                                | A ← (A) & (M)                                                      | 0 | _ | _                |   |   | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 |                                                  | dd<br>hh II<br>ee ff<br>ff<br>ee ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 |

|                         |                        |                      |                       |                        |                        | iviap (S              | meet i                | 012)                   |                      |                      |                      |                      |                      |                      |                     |

|-------------------------|------------------------|----------------------|-----------------------|------------------------|------------------------|-----------------------|-----------------------|------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------|

| Bit-Man                 | ipulation              | Branch               |                       |                        |                        |                       |                       | Control Register/Mem   |                      |                      |                      |                      | /Memory              |                      |                     |

| 00 5<br>BRSET0<br>3 DIR | BSET0                  | 20 3<br>BRA<br>2 REL | 30 5<br>NEG<br>2 DIR  | 40 1<br>NEGA<br>1 INH  | 50 1<br>NEGX<br>1 INH  | 60 5<br>NEG<br>2 IX1  | NEG<br>1 IX           | 80 9<br>RTI<br>1 INH   | BGE                  | SUB<br>2 IMM         | SUB<br>2 DIR         | C0 4<br>SUB<br>3 EXT | D0 4<br>SUB<br>3 IX2 | E0 3<br>SUB<br>2 IX1 | F0 3<br>SUB<br>1 IX |

| 01 5<br>BRCLR0<br>3 DIR |                        | 21 3<br>BRN<br>2 REL | 31 5<br>CBEQ<br>3 DIR | 41 4<br>CBEQA<br>3 IMM | 51 4<br>CBEQX<br>3 IMM | CBEQ                  | 71 5<br>CBEQ<br>2 IX+ | RTS<br>1 INH           | BLT<br>2 REL         | CMP<br>2 IMM         | B1 3<br>CMP<br>2 DIR | C1 4<br>CMP<br>3 EXT | D1 4<br>CMP<br>3 IX2 | E1 3<br>CMP<br>2 IX1 | F1 3<br>CMP<br>1 IX |

| 02 5<br>BRSET1<br>3 DIR | 12 5<br>BSET1<br>2 DIR | 22 3<br>BHI<br>2 REL | 32 5<br>LDHX<br>3 EXT | 42 5<br>MUL<br>1 INH   | 52 6<br>DIV<br>1 INH   | NSA                   | 72 1<br>DAA<br>1 INH  | 82 5+<br>BGND<br>1 INH | BGT                  | A2 2<br>SBC<br>2 IMM | B2 3<br>SBC<br>2 DIR | C2 4<br>SBC<br>3 EXT | D2 4<br>SBC<br>3 IX2 | E2 3<br>SBC<br>2 IX1 | F2 3<br>SBC<br>1 IX |

| 03 5                    | 13 5                   | 23 3                 | 33 5                  | 43 1                   | 53 1                   | 63 5                  | 73 4                  | 83 11                  | 93 3                 | A3 2                 | B3 3                 | C3 4                 | D3 4                 | E3 3                 | F3 3                |

| BRCLR1                  | BCLR1                  | BLS                  | COM                   | COMA                   | COMX                   | COM                   | COM                   | SWI                    | BLE                  | CPX                  | CPX                  | CPX                  | CPX                  | CPX                  | CPX                 |

| 3 DIR                   | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH                  | 1 INH                  | 2 IX1                 | 1 IX                  | 1 INH                  | 2 REL                | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 04 5                    | 14 5                   | 24 3                 | 34 5                  | 44 1                   | 54 1                   | 64 5                  | 74 4                  | 84 1                   | TXS                  | A4 2                 | B4 3                 | C4 4                 | D4 4                 | E4 3                 | F4 3                |

| BRSET2                  | BSET2                  | BCC                  | LSR                   | LSRA                   | LSRX                   | LSR                   | LSR                   | TAP                    |                      | AND                  | AND                  | AND                  | AND                  | AND                  | AND                 |

| 3 DIR                   | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH                  | 1 INH                  | 2 IX1                 | 1 IX                  | 1 INH                  |                      | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 05 5                    | 15 5                   | 25 3                 | 35 4                  | 45 3                   | 55 4                   | 65 3                  | 75 5                  | 85 1                   | 95 2                 | A5 2                 | B5 3                 | C5 4                 | D5 4                 | E5 3                 | F5 3                |

| BRCLR2                  | BCLR2                  | BCS                  | STHX                  | LDHX                   | LDHX                   | CPHX                  | CPHX                  | TPA                    | TSX                  | BIT                  | BIT                  | BIT                  | BIT                  | BIT                  | BIT                 |

| 3 DIR                   | 2 DIR                  | 2 REL                | 2 DIR                 | 3 IMM                  | 2 DIR                  | 3 IMM                 | 2 DIR                 | 1 INH                  | 1 INH                | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 06 5                    | BSET3                  | 26 3                 | 36 5                  | 46 1                   | 56 1                   | 66 5                  | 76 4                  | 86 3                   | 96 5                 | A6 2                 | B6 3                 | C6 4                 | D6 4                 | E6 3                 | F6 3                |

| BRSET3                  |                        | BNE                  | ROR                   | RORA                   | RORX                   | ROR                   | ROR                   | PULA                   | STHX                 | LDA                  | LDA                  | LDA                  | LDA                  | LDA                  | LDA                 |

| 3 DIR                   |                        | 2 REL                | 2 DIR                 | 1 INH                  | 1 INH                  | 2 IX1                 | 1 IX                  | 1 INH                  | 3 EXT                | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 07 5                    | 17 5                   | 27 3                 | 37 5                  | 47 1                   | 57 1                   | 67 5                  | 77 4                  | 87 2                   | TAX                  | A7 2                 | B7 3                 | C7 4                 | D7 4                 | E7 3                 | F7 2                |

| BRCLR3                  | BCLR3                  | BEQ                  | ASR                   | ASRA                   | ASRX                   | ASR                   | ASR                   | PSHA                   |                      | AIS                  | STA                  | STA                  | STA                  | STA                  | STA                 |

| 3 DIR                   | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH                  | 1 INH                  | 2 IX1                 | 1 IX                  | 1 INH                  |                      | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 08 5                    |                        | 28 3                 | 38 5                  | 48 1                   | 58 1                   | 68 5                  | 78 4                  | 88 3                   | 98 1                 | A8 2                 | B8 3                 | C8 4                 | D8 4                 | E8 3                 | F8 3                |

| BRSET4                  |                        | BHCC                 | LSL                   | LSLA                   | LSLX                   | LSL                   | LSL                   | PULX                   | CLC                  | EOR                  | EOR                  | EOR                  | EOR                  | EOR                  | EOR                 |

| 3 DIR                   |                        | 2 REL                | 2 DIR                 | 1 INH                  | 1 INH                  | 2 IX1                 | 1 IX                  | 1 INH                  | 1 INH                | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 09 5                    | 19 5                   | 29 3                 | 39 5                  | 49 1                   | 59 1                   | 69 5                  | 79 4                  | 89 2                   | 99 1                 | A9 2                 | B9 3                 | C9 4                 | D9 4                 | E9 3                 | F9 3                |

| BRCLR4                  | BCLR4                  | BHCS                 | ROL                   | ROLA                   | ROLX                   | ROL                   | ROL                   | PSHX                   | SEC                  | ADC                  | ADC                  | ADC                  | ADC                  | ADC                  | ADC                 |

| 3 DIR                   | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH                  | 1 INH                  | 2 IX1                 | 1 IX                  | 1 INH                  | 1 INH                | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0A 5                    | 1A 5                   | 2A 3                 | 3A 5                  | 4A 1                   | 5A 1                   | 6A 5                  | 7A 4                  | 8A 3                   | 9A 1                 | AA 2                 | BA 3                 | CA 4                 | DA 4                 | EA 3                 | FA 3                |

| BRSET5                  | BSET5                  | BPL                  | DEC                   | DECA                   | DECX                   | DEC                   | DEC                   | PULH                   | CLI                  | ORA                  | ORA                  | ORA                  | ORA                  | ORA                  | ORA                 |

| 3 DIR                   | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH                  | 1 INH                  | 2 IX1                 | 1 IX                  | 1 INH                  | 1 INH                | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0B 5<br>BRCLR5<br>3 DIR | BCLR5                  | 2B 3<br>BMI<br>2 REL | 3B 7<br>DBNZ<br>3 DIR | 4B 4<br>DBNZA<br>2 INH | 5B 4<br>DBNZX<br>2 INH | 6B 7<br>DBNZ<br>3 IX1 | 7B 6<br>DBNZ<br>2 IX  | 8B 2<br>PSHH<br>1 INH  | 9B 1<br>SEI<br>1 INH | ADD                  | BB 3<br>ADD<br>2 DIR | CB 4<br>ADD<br>3 EXT | DB 4<br>ADD<br>3 IX2 | EB 3<br>ADD<br>2 IX1 | FB 3<br>ADD<br>1 IX |

| 0C 5                    | 1C 5                   | 2C 3                 | 3C 5                  | 4C 1                   | 5C 1                   | 6C 5                  | 7C 4                  | 8C 1                   | 9C 1                 |                      | BC 3                 | CC 4                 | DC 4                 | EC 3                 | FC 3                |

| BRSET6                  | BSET6                  | BMC                  | INC                   | INCA                   | INCX                   | INC                   | INC                   | CLRH                   | RSP                  |                      | JMP                  | JMP                  | JMP                  | JMP                  | JMP                 |

| 3 DIR                   | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH                  | 1 INH                  | 2 IX1                 | 1 IX                  | 1 INH                  | 1 INH                |                      | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0D 5<br>BRCLR6<br>3 DIR |                        | 2D 3<br>BMS<br>2 REL | 3D 4<br>TST<br>2 DIR  | 4D 1<br>TSTA<br>1 INH  | 5D 1<br>TSTX<br>1 INH  | 6D 4<br>TST<br>2 IX1  | 7D 3<br>TST<br>1 IX   |                        | 9D 1<br>NOP<br>1 INH | AD 5<br>BSR<br>2 REL | BD 5<br>JSR<br>2 DIR | CD 6<br>JSR<br>3 EXT | DD 6<br>JSR<br>3 IX2 | JSR<br>2 IX1         | FD 5<br>JSR<br>1 IX |

| 0E 5<br>BRSET7<br>3 DIR | 1E 5<br>BSET7<br>2 DIR | 2E 3<br>BIL<br>2 REL | 3E 6<br>CPHX<br>3 EXT | 4E 5<br>MOV<br>3 DD    | 5E 5<br>MOV<br>2 DIX+  | MOV<br>3 IMD          | 7E 5<br>MOV<br>2 IX+D | 8E 2+<br>STOP<br>1 INH | 9E<br>Page 2         | LDX<br>2 IMM         |                      |                      | LDX<br>3 IX2         | EE 3<br>LDX<br>2 IX1 | FE 3<br>LDX<br>1 IX |

| 0F 5<br>BRCLR7<br>3 DIR |                        | 2F 3<br>BIH<br>2 REL | 3F 5<br>CLR<br>2 DIR  | 4F 1<br>CLRA<br>1 INH  | 5F 1<br>CLRX<br>1 INH  | 6F 5<br>CLR<br>2 IX1  | 7F 4<br>CLR<br>1 IX   | 8F 2+<br>WAIT<br>1 INH | TXA                  | AIX                  | BF 3<br>STX<br>2 DIR | CF 4<br>STX<br>3 EXT | DF 4<br>STX<br>3 IX2 | EF 3<br>STX<br>2 IX1 | FF 2<br>STX<br>1 IX |

### Table 8-2, Opcode Map (Sheet 1 of 2)

| INH  | Inherent   |

|------|------------|

| IMM  | Immediate  |

| DIR  | Direct     |

| EXT  | Extended   |

| DD   | DIR to DIR |

| IX+D | IX+ to DIR |

REL IX IX1 IX2 IMD DIX+

Relative Indexed, No Offset Indexed, 8-Bit Offset Indexed, 16-Bit Offset IMM to DIR DIR to IX+

Stack Pointer, 8-Bit Offset Stack Pointer, 16-Bit Offset Indexed, No Offset with Post Increment Indexed, 1-Byte Offset with Post Increment

SP1 SP2 IX+

IX1+

MC9S08GB/GT Data Sheet, Rev. 2.3

Opcode in Hexadecimal F0 3 SUB 1 IX HCS08 Cycles Instruction Mnemonic Addressing Mode

Serial Peripheral Interface (SPI) Module

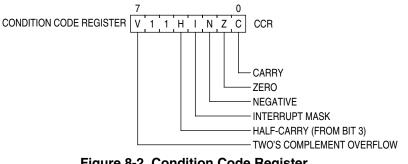

# 12.2.3 SPI Baud Rate Generation

As shown in Figure 12-4, the clock source for the SPI baud rate generator is the bus clock. The three prescale bits (SPPR2:SPPR1:SPPR0) choose a prescale divisor of 1, 2, 3, 4, 5, 6, 7, or 8. The three rate select bits (SPR2:SPR1:SPR0) divide the output of the prescaler stage by 2, 4, 8, 16, 32, 64, 128, or 256 to get the internal SPI master mode bit-rate clock.

# 12.3 Functional Description

An SPI transfer is initiated by checking for the SPI transmit buffer empty flag (SPTEF = 1) and then writing a byte of data to the SPI data register (SPI1D) in the master SPI device. When the SPI shift register is available, this byte of data is moved from the transmit data buffer to the shifter, SPTEF is set to indicate there is room in the buffer to queue another transmit character if desired, and the SPI serial transfer starts.

During the SPI transfer, data is sampled (read) on the MISO1 pin at one SPSCK edge and shifted, changing the bit value on the MOS11 pin, one-half SPSCK cycle later. After eight SPSCK cycles, the data that was in the shift register of the master has been shifted out the MOS11 pin to the slave while eight bits of data were shifted in the MISO1 pin into the master's shift register. At the end of this transfer, the received data byte is moved from the shifter into the receive data buffer and SPRF is set to indicate the data can be read by reading SPI1D. If another byte of data is waiting in the transmit buffer at the end of a transfer, it is moved into the shifter, SPTEF is set, and a new transfer is started.

Normally, SPI data is transferred most significant bit (MSB) first. If the least significant bit first enable (LSBFE) bit is set, SPI data is shifted LSB first.

When the SPI is configured as a slave, its  $\overline{SS1}$  pin must be driven low before a transfer starts and  $\overline{SS1}$  must stay low throughout the transfer. If a clock format where CPHA = 0 is selected,  $\overline{SS1}$  must be driven to a logic 1 between successive transfers. If CPHA = 1,  $\overline{SS1}$  may remain low between successive transfers. See Section 12.3.1, "SPI Clock Formats," for more details.

Because the transmitter and receiver are double buffered, a second byte, in addition to the byte currently being shifted out, can be queued into the transmit data buffer, and a previously received character can be in the receive data buffer while a new character is being shifted in. The SPTEF flag indicates when the transmit buffer has room for a new character. The SPRF flag indicates when a received character is available in the receive data buffer. The received character must be read out of the receive buffer (read SPI1D) before the next transfer is finished or a receive overrun error results.

In the case of a receive overrun, the new data is lost because the receive buffer still held the previous character and was not ready to accept the new data. There is no indication for such an overrun condition so the application system designer must ensure that previous data has been read from the receive buffer before a new transfer is initiated.

When CPHA = 0, the slave begins to drive its MISO output with the first data bit value (MSB or LSB depending on LSBFE) when  $\overline{SS1}$  goes to active low. The first SPSCK edge causes both the master and the slave to sample the data bit values on their MISO and MOSI inputs, respectively. At the second SPSCK edge, the SPI shifter shifts one bit position which shifts in the bit value that was just sampled and shifts the second data bit value out the other end of the shifter to the MOSI and MISO outputs of the master and slave, respectively. When CPHA = 0, the slave's  $\overline{SS}$  input must go to its inactive high level between transfers.

## 12.3.2 SPI Pin Controls

The SPI optionally shares four port pins. The function of these pins depends on the settings of SPI control bits. When the SPI is disabled (SPE = 0), these four pins revert to being general-purpose port I/O pins that are not controlled by the SPI.

## 12.3.2.1 SPSCK1 — SPI Serial Clock

When the SPI is enabled as a slave, this pin is the serial clock input. When the SPI is enabled as a master, this pin is the serial clock output.

## 12.3.2.2 MOSI1 — Master Data Out, Slave Data In

When the SPI is enabled as a master and SPI pin control zero (SPC0) is 0 (not bidirectional mode), this pin is the serial data output. When the SPI is enabled as a slave and SPC0 = 0, this pin is the serial data input. If SPC0 = 1 to select single-wire bidirectional mode, and master mode is selected, this pin becomes the bidirectional data I/O pin (MOMI). Also, the bidirectional mode output enable bit determines whether the pin acts as an input (BIDIROE = 0) or an output (BIDIROE = 1). If SPC0 = 1 and slave mode is selected, this pin is not used by the SPI and reverts to being a general-purpose port I/O pin.

## 12.3.2.3 MISO1 — Master Data In, Slave Data Out

When the SPI is enabled as a master and SPI pin control zero (SPC0) is 0 (not bidirectional mode), this pin is the serial data input. When the SPI is enabled as a slave and SPC0 = 0, this pin is the serial data output. If SPC0 = 1 to select single-wire bidirectional mode, and slave mode is selected, this pin becomes the bidirectional data I/O pin (SISO) and the bidirectional mode output enable bit determines whether the pin acts as an input (BIDIROE = 0) or an output (BIDIROE = 1). If SPC0 = 1 and master mode is selected, this pin is not used by the SPI and reverts to being a general-purpose port I/O pin.

## 12.3.2.4 SS1 — Slave Select

When the SPI is enabled as a slave, this pin is the low-true slave select input. When the SPI is enabled as a master and mode fault enable is off (MODFEN = 0), this pin is not used by the SPI and reverts to being a general-purpose port I/O pin. When the SPI is enabled as a master and MODFEN = 1, the slave select output enable bit determines whether this pin acts as the mode fault input (SSOE = 0) or as the slave select output (SSOE = 1).

Serial Peripheral Interface (SPI) Module

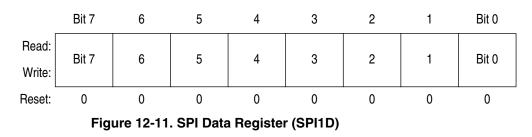

# 12.4.5 SPI Data Register (SPI1D)

Reads of this register return the data read from the receive data buffer. Writes to this register write data to the transmit data buffer. When the SPI is configured as a master, writing data to the transmit data buffer initiates an SPI transfer.

Data should not be written to the transmit data buffer unless the SPI transmit buffer empty flag (SPTEF) is set, indicating there is room in the transmit buffer to queue a new transmit byte.

Data may be read from SPI1D any time after SPRF is set and before another transfer is finished. Failure to read the data out of the receive data buffer before a new transfer ends causes a receive overrun condition and the data from the new transfer is lost.

# 13.1 Introduction

The inter-integrated circuit (IIC) provides a method of communication between a number of devices. The interface is designed to operate up to 100 kbps with maximum bus loading and timing. The device is capable of operating at higher baud rates, up to a maximum of clock/20, with reduced bus loading. The maximum communication length and the number of devices that can be connected are limited by a maximum bus capacitance of 400 pF.

For additional detail, please refer to volume 1 of the *HCS08 Reference Manual*, (Freescale Semiconductor document order number HCS08RMv1/D).

## 13.1.1 Features

The IIC includes these distinctive features:

- Compatible with IIC bus standard

- Multi-master operation

- Software programmable for one of 64 different serial clock frequencies

- Software selectable acknowledge bit

- Interrupt driven byte-by-byte data transfer

- Arbitration lost interrupt with automatic mode switching from master to slave

- Calling address identification interrupt

- START and STOP signal generation/detection

- Repeated START signal generation

- Acknowledge bit generation/detection

- Bus busy detection

# 13.1.2 Modes of Operation

The IIC functions the same in normal and monitor modes. A brief description of the IIC in the various MCU modes is given here.

- Run mode This is the basic mode of operation. To conserve power in this mode, disable the module.

- Wait mode The module will continue to operate while the MCU is in wait mode and can provide a wake-up interrupt.

- Stop mode The IIC is inactive in stop3 mode for reduced power consumption. The STOP instruction does not affect IIC register states. Stop1 and stop2 will reset the register contents.

Analog-to-Digital Converter (ATD) Module

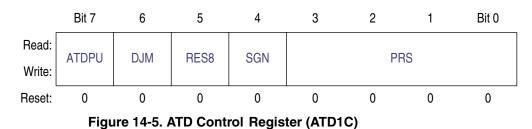

# 14.6.1 ATD Control (ATDC)

Writes to the ATD control register will abort the current conversion, but will not start a new conversion.

### ATDPU — ATD Power Up

This bit provides program on/off control over the ATD, reducing power consumption when the ATD is not being used. When cleared, the ATDPU bit aborts any conversion in progress.

1 = ATD functionality.

0 = Disable the ATD and enter a low-power state.

DJM — Data Justification Mode

This bit determines how the 10-bit conversion result data maps onto the ATD result register bits. When RES8 is set, bit DJM has no effect and the 8-bit result is always located in ATD1RH.

For left-justified mode, result data bits 9–2 map onto bits 7–0 of ATD1RH, result data bits 1 and 0 map onto ATD1RL bits 7 and 6, where bit 7 of ATD1RH is the most significant bit (MSB).

| 7 | 6 | 5 | 4 | 3  | 2      | 1 | 0       | 7 | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|----|--------|---|---------|---|-----|---|---|---|---|---|---|---|

| 9 |   | 1 | I |    | SULT - | ĺ | <b></b> |   | _ 0 |   |   |   |   |   |   |   |

|   |   | 1 | i | 11 | -00L1  | 1 |         |   |     |   |   |   |   |   |   |   |

|   |   |   |   |    |        |   |         |   |     |   |   |   |   |   |   |   |

ATD1RH

ATD1RL

#### Figure 14-6. Left-Justified Mode

For right-justified mode, result data bits 9 and 8 map onto bits 1 and 0 of ATD1RH, result data bits 7–0 map onto ATD1RL bits 7–0, where bit 1 of ATD1RH is the most significant bit (MSB).

| 7 | 6 | 5 | 4 | 3 | 2 | 1              | 0 |  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---|---|---|---|---|---|----------------|---|--|---|---|---|---|---|---|---|---|--|--|

|   |   |   |   |   |   | 9 ← RESULT ▶ 0 |   |  |   |   |   |   |   |   |   |   |  |  |

|   |   |   |   |   |   |                |   |  |   |   |   |   |   |   |   |   |  |  |

ATD1RH

ATD1RL

#### Figure 14-7. Right-Justified Mode

The effect of the DJM bit on the result is shown in Table 14-3.

1 = Result register data is right justified.

0 = Result register data is left justified.

#### Development Support

The SYNC command is unlike other BDC commands because the host does not necessarily know the correct communications speed to use for BDC communications until after it has analyzed the response to the SYNC command.

To issue a SYNC command, the host:

- Drives the BKGD pin low for at least 128 cycles of the slowest possible BDC clock (The slowest clock is normally the reference oscillator/64 or the self-clocked rate/64.)

- Drives BKGD high for a brief speedup pulse to get a fast rise time (This speedup pulse is typically one cycle of the fastest clock in the system.)

- Removes all drive to the BKGD pin so it reverts to high impedance

- Monitors the BKGD pin for the sync response pulse

The target, upon detecting the SYNC request from the host (which is a much longer low time than would ever occur during normal BDC communications):

- Waits for BKGD to return to a logic high

- Delays 16 cycles to allow the host to stop driving the high speedup pulse

- Drives BKGD low for 128 BDC clock cycles

- Drives a 1-cycle high speedup pulse to force a fast rise time on BKGD

- Removes all drive to the BKGD pin so it reverts to high impedance

The host measures the low time of this 128-cycle sync response pulse and determines the correct speed for subsequent BDC communications. Typically, the host can determine the correct communication speed within a few percent of the actual target speed and the communication protocol can easily tolerate speed errors of several percent.

# 15.3.4 BDC Hardware Breakpoint

The BDC includes one relatively simple hardware breakpoint that compares the CPU address bus to a 16-bit match value in the BDCBKPT register. This breakpoint can generate a forced breakpoint or a tagged breakpoint. A forced breakpoint causes the CPU to enter active background mode at the first instruction boundary following any access to the breakpoint address. The tagged breakpoint causes the instruction opcode at the breakpoint address to be tagged so that the CPU will enter active background mode rather than executing that instruction if and when it reaches the end of the instruction queue. This implies that tagged breakpoints can only be placed at the address of an instruction opcode while forced breakpoints can be set at any address.

The breakpoint enable (BKPTEN) control bit in the BDC status and control register (BDCSCR) is used to enable the breakpoint logic (BKPTEN = 1). When BKPTEN = 0, its default value after reset, the breakpoint logic is disabled and no BDC breakpoints are requested regardless of the values in other BDC breakpoint registers and control bits. The force/tag select (FTS) control bit in BDCSCR is used to select forced (FTS = 1) or tagged (FTS = 0) type breakpoints.

The on-chip debug module (DBG) includes circuitry for two additional hardware breakpoints that are more flexible than the simple breakpoint in the BDC module.

**Development Support**

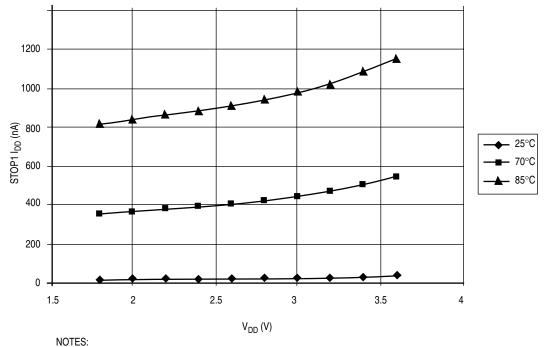

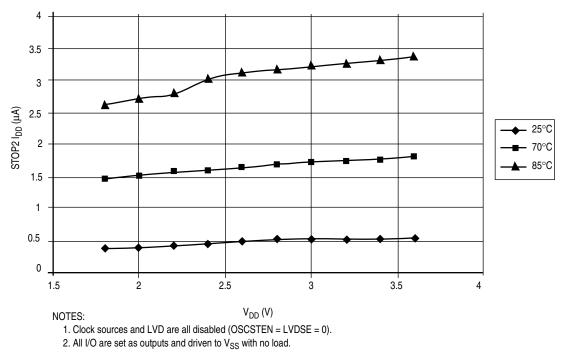

Clock sources and LVD are all disabled (OSCSTEN = LVDSE = 0).

All I/O are set as outputs and driven to V<sub>SS</sub> with no load.

Figure A-7. Typical Stop1 I<sub>DD</sub>

Figure A-8. Typical Stop 2 I<sub>DD</sub>

MC9S08GB/GT Data Sheet, Rev. 2.3

#### Appendix A Electrical Characteristics

- <sup>1</sup> This is the shortest pulse that is guaranteed to be recognized as a reset pin request. Shorter pulses are not guaranteed to override reset requests from internal sources.

- <sup>2</sup> When any reset is initiated, internal circuitry drives the reset pin low for about 34 cycles of f<sub>Self\_reset</sub> and then samples the level on the reset pin about 38 cycles later to distinguish external reset requests from internal requests.

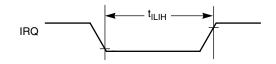

- <sup>3</sup> This is the minimum pulse width that is guaranteed to pass through the pin synchronization circuitry. Shorter pulses may or may not be recognized. In stop mode, the synchronizer is bypassed so shorter pulses can be recognized in that case.

- $^4$  Timing is shown with respect to 20%  $V_{DD}$  and 80%  $V_{DD}$  levels. Temperature range –40°C to 85°C.

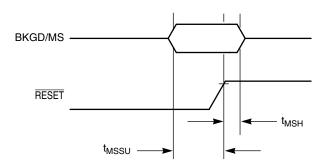

Figure A-11. Reset Timing

Figure A-12. Active Background Debug Mode Latch Timing

## A.9.2 Timer/PWM (TPM) Module Timing

Synchronizer circuits determine the shortest input pulses that can be recognized or the fastest clock that can be used as the optional external source to the timer counter. These synchronizers operate from the current bus rate clock.