Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | S08                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 39                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 2K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-VFQFN Exposed Pad                                                    |

| Supplier Device Package    | 48-QFN-EP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08gt32cfder |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

### http://freescale.com

The following revision history table summarizes changes contained in this document.

| Revision<br>Number | Revision<br>Date | Description of Changes                                                                                                                                                                                                                                                                                                                                                     |

|--------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0                | 4/25/2003        | Initial release                                                                                                                                                                                                                                                                                                                                                            |

| 1.1                |                  | Electricals change, appendix A only                                                                                                                                                                                                                                                                                                                                        |

| 1.2                |                  | Electricals change, appendix A only                                                                                                                                                                                                                                                                                                                                        |

| 1.3                | 10/2/2003        | Added module version table; clarifications                                                                                                                                                                                                                                                                                                                                 |

| 1.4                | 10/29/2003       | Fixed typos and made corrections and clarifications                                                                                                                                                                                                                                                                                                                        |

| 1.5                | 11/12/2003       | Added 1-MHz I <sub>DD</sub> values to Electricals, appendix A                                                                                                                                                                                                                                                                                                              |

| 2                  | 2/10/2004        | Changed format of register names to enable reuse of code (from SCIBD to SCI1BD, even when only one instance of a module on a chip) Added new device: MC9S08GT16 to book. Added new 48-pin QFN package to book. BKGDPE description in Section 5 — changed PTD0 to PTG0. Changed typo in CPU section that listed MOV instruction as being 6 cycles instead of 5 (Table 8-2). |

| 2.2                | 9/2/2004         | Format to Freescale look-and-feel; Clarified RTI clock sources and other changes in Chapter 5; updated ICG initialization examples; expanded descriptions of LOLS and LOCS bits in ICGS1; updated ICG electricals Table A-9 and added a figure                                                                                                                             |

| 2.3                | 12/01/2004       | Minor changes to Table 7-4, Table 7-5, Table A-9;<br>Clarifications in Section 11.10.6, "SCI x Control Register 3 (SCIxC3)", Section 11.7, "Interrupts<br>and Status Flags", Section 11.8.1, "8- and 9-Bit Data Modes", PTG availability in 48-pin<br>package (see Table 2-2)                                                                                              |

This product incorporates SuperFlash® technology licensed from SST.

Freescale, and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

$\ensuremath{\texttt{©}}$  Freescale Semiconductor, Inc., 2004. All rights reserved.

| Section Number |          | umber Title                                              | Page |  |

|----------------|----------|----------------------------------------------------------|------|--|

|                |          | Chapter 8 Central Processor Unit (CPU)                   |      |  |

| 8.1            | Introduc | ction                                                    | 125  |  |

| 8.2            | Feature  | S                                                        | 126  |  |

| 8.3            | Progran  | nmer's Model and CPU Registers                           | 126  |  |

|                | 8.3.1    | Accumulator (A)                                          | 127  |  |

|                | 8.3.2    | Index Register (H:X)                                     | 127  |  |

|                | 8.3.3    | Stack Pointer (SP)                                       | 128  |  |

|                | 8.3.4    | Program Counter (PC)                                     | 128  |  |

|                | 8.3.5    | Condition Code Register (CCR)                            |      |  |

| 8.4            | Address  | sing Modes                                               | 130  |  |

|                | 8.4.1    | Inherent Addressing Mode (INH)                           |      |  |

|                | 8.4.2    | Relative Addressing Mode (REL)                           |      |  |

|                | 8.4.3    | Immediate Addressing Mode (IMM)                          |      |  |

|                | 8.4.4    | Direct Addressing Mode (DIR)                             |      |  |

|                | 8.4.5    | Extended Addressing Mode (EXT)                           |      |  |

|                | 8.4.6    | Indexed Addressing Mode                                  |      |  |

|                |          | 8.4.6.1 Indexed, No Offset (IX)                          |      |  |

|                |          | 8.4.6.2 Indexed, No Offset with Post Increment (IX+)     |      |  |

|                |          | 8.4.6.3 Indexed, 8-Bit Offset (IX1)                      |      |  |

|                |          | 8.4.6.4 Indexed, 8-Bit Offset with Post Increment (IX1+) |      |  |

|                |          | 8.4.6.5 Indexed, 16-Bit Offset (IX2)                     |      |  |

|                |          | 8.4.6.6 SP-Relative, 8-Bit Offset (SP1)                  |      |  |

|                |          | 8.4.6.7 SP-Relative, 16-Bit Offset (SP2)                 |      |  |

| 8.5            |          | Operations                                               |      |  |

|                | 8.5.1    | Reset Sequence                                           |      |  |

|                | 8.5.2    | Interrupt Sequence                                       |      |  |

|                | 8.5.3    | Wait Mode Operation                                      |      |  |

|                | 8.5.4    | Stop Mode Operation                                      |      |  |

| 0.6            | 8.5.5    | BGND Instruction                                         |      |  |

| 8.6            | HCS08    | Instruction Set Summary                                  | 134  |  |

|                |          | Chapter 9                                                |      |  |

| 9.1            | Introduc | Keyboard Interrupt (KBI) Module                          | 145  |  |

| <b>7.1</b>     | 9.1.1    | Port A and Keyboard Interrupt Pins                       |      |  |

| 9.2            |          | S                                                        |      |  |

| 9.3            |          | ock Diagram                                              |      |  |

| 9.4            |          | rd Interrupt (KBI) Module                                |      |  |

| <i>7</i> .1    | 9.4.1    | Pin Enables                                              |      |  |

|                | 9.4.2    | Edge and Level Sensitivity                               |      |  |

|                | 9.4.3    | KBI Interrupt Controls                                   |      |  |

| 9.5            |          | gisters and Control Bits                                 |      |  |

|                | 9.5.1    | KBI Status and Control Register (KBI1SC)                 |      |  |

|                | 9.5.2    | KBI Pin Enable Register (KBI1PE)                         |      |  |

|                |          | MC9S08GB/GT Data Sheet, Rev. 2.3                         |      |  |

#### **Chapter 1 Introduction**

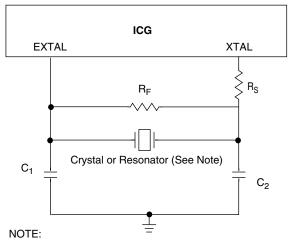

- Multiple clock source options:

- Internally generated clock with  $\pm 0.2\%$  trimming resolution and  $\pm 0.5\%$  deviation across voltage.

- Crystal

- Resonator, or

- External clock

- Inter-integrated circuit bus module to operate up to 100 kbps (IIC)

- One 3-channel and one 5-channel 16-bit timer/pulse width modulator (TPM) modules with selectable input capture, output compare, and edge-aligned PWM capability on each channel. Each timer module may be configured for buffered, centered PWM (CPWM) on all channels (TPMx).

- 8-pin keyboard interrupt module (KBI)

- 16 high-current pins (limited by package dissipation)

- Software selectable pullups on ports when used as input. Selection is on an individual port bit basis. During output mode, pullups are disengaged.

- Internal pullup on RESET and IRQ pin to reduce customer system cost

- Up to 56 general-purpose input/output (I/O) pins, depending on package selection

- 64-pin low-profile quad flat package (LQFP) MC9S08GBxx

- 48-pin quad flat package, no lead (QFN) MC9S08GTxx

- 44-pin quad flat package (QFP) MC9S08GTxx

- 42-pin shrink dual in-line package (SDIP) MC9S08GTxx

## 1.2.3 Devices in the MC9S08GB/GT Series

Table 1-1 lists the devices available in the MC9S08GB/GT series and summarizes the differences among them.

Table 1-1. Devices in the MC9S08GB/GT Series

| Device     | FLASH | RAM | TPM                                           | I/O            | Packages                                   |

|------------|-------|-----|-----------------------------------------------|----------------|--------------------------------------------|

| MC9S08GB60 | 60K   | 4K  | One 3-channel and one 5-channel, 16-bit timer | 56             | 64 LQFP                                    |

| MC9S08GB32 | 32K   | 2K  | One 3-channel and one 5-channel, 16-bit timer | 56             | 64 LQFP                                    |

| MC9S08GT60 | 60K   | 4K  | Two 2-channel,<br>16-bit timers               | 39<br>36<br>34 | 48 QFN <sup>1</sup><br>44 QFP<br>42 SDIP   |

| MC9S08GT32 | 32K   | 2K  | Two 2-channel,<br>16-bit timers               | 39<br>36<br>34 | 48 QFN <sup>(1)</sup><br>44 QFP<br>42 SDIP |

| MC9S08GT16 | 16K   | 1K  | Two 2-channel,<br>16-bit timers               | 39<br>36<br>34 | 48 QFN <sup>(1)</sup><br>44 QFP<br>42 SDIP |

<sup>&</sup>lt;sup>1</sup> The 48-pin QFN package has one 3-channel and one 2-channel 16-bit TPM.

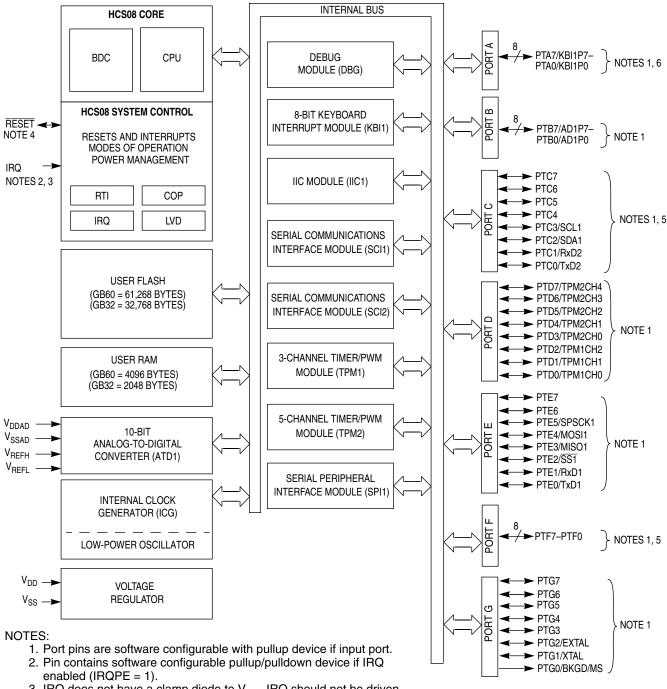

## 1.3 MCU Block Diagrams

These block diagrams show the structure of the MC9S08GB/GT MCUs.

- 3. IRQ does not have a clamp diode to  $V_{DD}$ . IRQ should not be driven above  $V_{DD}$ .

- 4. Pin contains integrated pullup device.

- 5. High current drive

- 6. Pins PTA[7:4] contain both pullup and pulldown devices. Pulldown available when KBI enabled (KBIPn = 1).

Figure 1-1. MC9S08GBxx Block Diagram

MC9S08GB/GT Data Sheet, Rev. 2.3

#### **Chapter 2 Pins and Connections**

#### **NOTE**

To avoid extra current drain from floating input pins, the reset initialization routine in the application program should either enable on-chip pullup devices or change the direction of unused pins to outputs so the pins do not float.

For information about controlling these pins as general-purpose I/O pins, see Chapter 6, "Parallel Input/Output." For information about how and when on-chip peripheral systems use these pins, refer to the appropriate section from Table 2-1.

**Table 2-1. Pin Sharing References**

| Port Pins                    | Alternate<br>Function           | Reference <sup>1</sup>                                     |  |

|------------------------------|---------------------------------|------------------------------------------------------------|--|

| PTA7-PTA0                    | KBI1P7-KBI1P0                   | Chapter 2, "Pins and Connections"                          |  |

| PTB7-PTB0                    | AD1P7–AD1P0                     | Chapter 14, "Analog-to-Digital Converter (ATD) Module"     |  |

| PTC7-PTC4                    | _                               | Chapter 6, "Parallel Input/Output"                         |  |

| PTC3-PTC2                    | SCL1-SDA1                       | Chapter 13, "Inter-Integrated Circuit (IIC) Module"        |  |

| PTC1-PTC0                    | RxD2–TxD2                       | Chapter 11, "Serial Communications Interface (SCI) Module" |  |

| PTD7-PTD3                    | TPM2CH4-<br>TPM2CH0             | Chapter 10, "Timer/PWM (TPM) Module"                       |  |

| PTD2-PTD0                    | TPM1CH2-<br>TPM1CH0             | Chapter 10, "Timer/PWM (TPM) Module"                       |  |

| PTE7-PTE6                    | _                               | Chapter 6, "Parallel Input/Output"                         |  |

| PTE5<br>PTE4<br>PTE3<br>PTE2 | SPSCK1<br>MISO1<br>MOSI1<br>SST | Chapter 12, "Serial Peripheral Interface (SPI) Module"     |  |

| PTE1-PTE0                    | RxD1–TxD1                       | Chapter 11, "Serial Communications Interface (SCI) Module" |  |

| PTF7-PTF0                    | _                               | Chapter 6, "Parallel Input/Output"                         |  |

| PTG7-PTG3                    | _                               | Chapter 6, "Parallel Input/Output"                         |  |

| PTG2-PTG1                    | EXTAL-XTAL                      | Chapter 7, "Internal Clock Generator (ICG) Module"         |  |

| PTG0                         | BKGD/MS                         | Chapter 15, "Development Support"                          |  |

<sup>&</sup>lt;sup>1</sup> See this section for information about modules that share these pins.

When an on-chip peripheral system is controlling a pin, data direction control bits still determine what is read from port data registers even though the peripheral module controls the pin direction by controlling the enable for the pin's output buffer. See Chapter 6, "Parallel Input/Output" for details.

Pullup enable bits for each input pin control whether on-chip pullup devices are enabled whenever the pin is acting as an input even if it is being controlled by an on-chip peripheral module. When the PTA7–PTA4 pins are controlled by the KBI module and are configured for rising-edge/high-level sensitivity, the pullup enable control bits enable pulldown devices rather than pullup devices. Similarly, when IRQ is configured

MC9S08GB/GT Data Sheet, Rev. 2.3

as the IRQ input and is set to detect rising edges, the pullup enable control bit enables a pulldown device rather than a pullup device.

# 2.3.6 Signal Properties Summary

Table 2-2 summarizes I/O pin characteristics. These characteristics are determined by the way the common pin interfaces are hardwired to internal circuits.

**Table 2-2. Signal Properties**

| Pin<br>Name         | Dir | High Current<br>Pin | Output<br>Slew <sup>1</sup> | Pull-Up <sup>2</sup> | Comments                                                                                                                                                                                                                                                                                           |

|---------------------|-----|---------------------|-----------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{DD}$            |     | _                   | _                           | _                    |                                                                                                                                                                                                                                                                                                    |

| V <sub>SS</sub>     |     | _                   | _                           | _                    | The 48-pin QFN package has two $V_{SS}$ pins — $V_{SS1}$ and $V_{SS2}$ .                                                                                                                                                                                                                           |

| $V_{\mathrm{DDAD}}$ |     | _                   | _                           | _                    |                                                                                                                                                                                                                                                                                                    |

| V <sub>SSAD</sub>   |     | _                   | _                           | _                    |                                                                                                                                                                                                                                                                                                    |

| V <sub>REFH</sub>   |     | _                   | _                           | _                    |                                                                                                                                                                                                                                                                                                    |

| V <sub>REFL</sub>   |     | _                   | _                           | _                    |                                                                                                                                                                                                                                                                                                    |

| RESET               | I/O | Y                   | N                           | Y                    | Pin contains integrated pullup.                                                                                                                                                                                                                                                                    |

| IRQ                 | I   | _                   | _                           | Y                    | IRQPE must be set to enable IRQ function. IRQ does not have a clamp diode to $V_{DD}$ . IRQ should not be driven above $V_{DD}$ . Pullup/pulldown active when IRQ pin function enabled. Pullup forced on when IRQ enabled for falling edges; pulldown forced on when IRQ enabled for rising edges. |

| PTA0/KBI1P0         | I/O | N                   | SWC                         | SWC                  |                                                                                                                                                                                                                                                                                                    |

| PTA1/KBI1P1         | I/O | N                   | SWC                         | SWC                  |                                                                                                                                                                                                                                                                                                    |

| PTA2/KBI1P2         | I/O | N                   | SWC                         | SWC                  |                                                                                                                                                                                                                                                                                                    |

| PTA3/KBI1P3         | I/O | N                   | SWC                         | SWC                  |                                                                                                                                                                                                                                                                                                    |

| PTA4/KBI1P4         | I/O | N                   | SWC                         | SWC                  | Pullup/pulldown active when KBI pin function                                                                                                                                                                                                                                                       |

| PTA5/KBI1P5         | I/O | N                   | SWC                         | SWC                  | enabled. Pullup forced on when KBI1Px enabled for                                                                                                                                                                                                                                                  |

| PTA6/KBI1P6         | I/O | N                   | SWC                         | SWC                  | falling edges; pulldown forced on when KBI1Px                                                                                                                                                                                                                                                      |

| PTA7/KBI1P7         | I/O | N                   | SWC                         | SWC                  | enabled for rising edges.                                                                                                                                                                                                                                                                          |

| PTB0/AD1P0          | I/O | N                   | SWC                         | SWC                  |                                                                                                                                                                                                                                                                                                    |

| PTB1/AD1P1          | I/O | N                   | SWC                         | SWC                  |                                                                                                                                                                                                                                                                                                    |

| PTB2/AD1P2          | I/O | N                   | SWC                         | SWC                  |                                                                                                                                                                                                                                                                                                    |

| PTB3/AD1P3          | I/O | N                   | SWC                         | SWC                  |                                                                                                                                                                                                                                                                                                    |

| PTB4/AD1P4          | I/O | N                   | SWC                         | SWC                  |                                                                                                                                                                                                                                                                                                    |

| PTB5/AD1P5          | I/O | N                   | SWC                         | SWC                  |                                                                                                                                                                                                                                                                                                    |

| PTB6/AD1P6          | I/O | N                   | SWC                         | SWC                  |                                                                                                                                                                                                                                                                                                    |

| PTB7/AD1P7          | I/O | N                   | SWC                         | SWC                  |                                                                                                                                                                                                                                                                                                    |

| PTC0/TxD2           | I/O | Y                   | SWC                         | SWC                  | When pin is configured for SCI function, pin is                                                                                                                                                                                                                                                    |

| PTC1/RxD2           | I/O | Y                   | SWC                         | SWC                  | configured for partial output drive.                                                                                                                                                                                                                                                               |

| PTC2/SDA1           | I/O | Y                   | SWC                         | SWC                  |                                                                                                                                                                                                                                                                                                    |

| PTC3/SCL1           | I/O | Y                   | SWC                         | SWC                  |                                                                                                                                                                                                                                                                                                    |

**Chapter 4 Memory**

#### Chapter 6 Parallel Input/Output

Port A can be configured to be keyboard interrupt input pins. Refer to Chapter 9, "Keyboard Interrupt (KBI) Module," for more information about using port A pins as keyboard interrupts pins.

## 6.3.2 Port B and Analog to Digital Converter Inputs

| Port B |             | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

|--------|-------------|-------|-------|-------|-------|-------|-------|-------|-------|

|        | MCU Pin:    | PTB7/ | PTB6/ | PTB5/ | PTB4/ | PTB3/ | PTB2/ | PTB1/ | PTB0/ |

|        | IVICU FIII. | AD1P7 | AD1P6 | AD1P5 | AD1P4 | AD1P3 | AD1P2 | AD1P1 | AD1P0 |

Figure 6-3. Port B Pin Names

Port B is an 8-bit port shared among the ATD inputs and general-purpose I/O. Any pin enabled as an ATD input will be forced to act as an input.

Port B pins are available as general-purpose I/O pins controlled by the port B data (PTBD), data direction (PTBDD), pullup enable (PTBPE), and slew rate control (PTBSE) registers. Refer to Section 6.4, "Parallel I/O Controls," for more information about general-purpose I/O control.

When the ATD module is enabled, analog pin enables are used to specify which pins on port B will be used as ATD inputs. Refer to Chapter 14, "Analog-to-Digital Converter (ATD) Module," for more information about using port B pins as ATD pins.

## 6.3.3 Port C and SCI2, IIC, and High-Current Drivers

| Port C |          | Bit 7 | 6    | 5    | 3    | 3             | 2             | 1             | Bit 0         |

|--------|----------|-------|------|------|------|---------------|---------------|---------------|---------------|

|        | MCU Pin: | PTC7  | PTC6 | PTC5 | PTC4 | PTC3/<br>SCL1 | PTC2/<br>SDA1 | PTC1/<br>RxD2 | PTC0/<br>TxD2 |

Figure 6-4. Port C Pin Names

Port C is an 8-bit port which is shared among the SCI2 and IIC1 modules, and general-purpose I/O. When SCI2 or IIC1 modules are enabled, the pin direction will be controlled by the module or function. Port C has high current output drivers.

Port C pins are available as general-purpose I/O pins controlled by the port C data (PTCD), data direction (PTCDD), pullup enable (PTCPE), and slew rate control (PTCSE) registers. Refer to Section 6.4, "Parallel I/O Controls," for more information about general-purpose I/O control.

When the SCI2 module is enabled, PTC0 serves as the SCI2 module's transmit pin (TxD2) and PTC1 serves as the receive pin (RxD2). Refer to Chapter 11, "Serial Communications Interface (SCI) Module," for more information about using PTC0 and PTC1 as SCI pins

When the IIC module is enabled, PTC2 serves as the IIC modules's serial data input/output pin (SDA1) and PTC3 serves as the clock pin (SCL1). Refer to Chapter 13, "Inter-Integrated Circuit (IIC) Module," for more information about using PTC2 and PTC3 as IIC pins.

**Chapter 6 Parallel Input/Output**

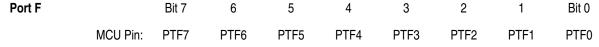

## 6.3.6 Port F and High-Current Drivers

Figure 6-7. Port F Pin Names

Port F is an 8-bit port general-purpose I/O that is not shared with any peripheral module. Port F has high current output drivers.

Port F pins are available as general-purpose I/O pins controlled by the port F data (PTFD), data direction (PTFDD), pullup enable (PTFPE), and slew rate control (PTFSE) registers. Refer to Section 6.4, "Parallel I/O Controls" for more information about general-purpose I/O control.

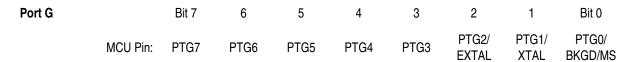

## 6.3.7 Port G, BKGD/MS, and Oscillator

Figure 6-8. Port G Pin Names

Port G is an 8-bit port which is shared among the background/mode select function, oscillator, and general-purpose I/O. When the background/mode select function or oscillator is enabled, the pin direction will be controlled by the module function.

Port G pins are available as general-purpose I/O pins controlled by the port G data (PTGD), data direction (PTGDD), pullup enable (PTGPE), and slew rate control (PTGSE) registers. Refer to Section 6.4, "Parallel I/O Controls" for more information about general-purpose I/O control.

The internal pullup for PTG0 is enabled when the background/mode select function is enabled, regardless of the state of PTGPE0. During reset, the BKGD/MS pin functions as a mode select pin. After the MCU is out of reset, the BKGD/MS pin becomes the background communications input/output pin. The PTG0 can be configured to be a general-purpose output pin. Refer to Chapter 3, "Modes of Operation", Chapter 5, "Resets, Interrupts, and System Configuration", and Chapter 15, "Development Support" for more information about using this pin.

The ICG module can be configured to use PTG2–PTG1 ports as crystal oscillator or external clock pins.

Refer to Chapter 13, "Inter-Integrated Circuit (IIC) Module" for more information about using these pins as oscillator pins.

## 6.4 Parallel I/O Controls

Provided no on-chip peripheral is controlling a port pin, the pins operate as general-purpose I/O pins that are accessed and controlled by a data register (PTxD), a data direction register (PTxDD), a pullup enable register (PTxPE), and a slew rate control register (PTxSE) where x is A, B, C, D, E, F, or G.

The clock scheme will be FLL engaged, internal (FEI). So

$$f_{ICGOUT} = (f_{IRG} / 7) * P * N / R ; P = 64, f_{IRG} = 243 \text{ kHz}$$

Eqn. 7-5

Solving for N / R gives:

$$N/R = 10.8 \text{ MHz}/(243/7 \text{ kHz} * 64) = 4.86$$

; We can choose  $N = 10$  and  $R = 2$ .

A trim procedure will be required to hone the frequency to exactly 5.4 MHz. An example of the trim procedure is shown in example #4.

The values needed in each register to set up the desired operation are:

### ICGC1 = \$28 (%00101000)

| Bit 7    |         | 0  | Unimplemented or reserved, always reads zero                         |

|----------|---------|----|----------------------------------------------------------------------|

| Bit 6    | RANGE   | 0  | Configures oscillator for low-frequency range; (don't care)          |

| Bit 5    | REFS    | 1  | Oscillator using crystal or resonator requested (don't care)         |

| Bits 4:3 | CLKS    | 01 | FLL engaged, internal reference clock mode                           |

| Bit 2    | OSCSTEN | 0  | Disables the oscillator in stop modes                                |

| Bit 1    |         | 0  | Reserved for Freescale Semiconductor internal use; always write zero |

| Bit 0    |         | 0  | Unimplemented or reserved, always reads zero                         |

|          |         |    |                                                                      |

## ICGC2 = \$31 (%00110001)

| Bit 7   | LOLRE | 0   | Generates an interrupt request on loss of lock  |

|---------|-------|-----|-------------------------------------------------|

| Bit 6:4 | MFD   | 011 | Sets the MFD multiplication factor to 10        |

| Bit 3   | LOCRE | 0   | Generates an interrupt request on loss of clock |

| Bit 2:0 | RFD   | 001 | Sets the RFD division factor to ÷2              |

### ICGS1 = \$xx

This is read only except for clearing interrupt flag

### ICGS2 = \$xx

This is read only; good idea to read this before performing time critical operations

### ICGFLTLU/L = \$xx

Not used in this example

### ICGTRM = \$xx

Bit 7:0 TRIM Only need to write when trimming internal oscillator; done in separate operation (see example #4)

**Central Processor Unit (CPU)**

## 8.3.3 Stack Pointer (SP)

This 16-bit address pointer register points at the next available location on the automatic last-in-first-out (LIFO) stack. The stack may be located anywhere in the 64-Kbyte address space that has RAM and can be any size up to the amount of available RAM. The stack is used to automatically save the return address for subroutine calls, the return address and CPU registers during interrupts, and for local variables. The AIS (add immediate to stack pointer) instruction adds an 8-bit signed immediate value to SP. This is most often used to allocate or deallocate space for local variables on the stack.

SP is forced to \$00FF at reset for compatibility with the earlier M68HC05 Family. HCS08 programs normally change the value in SP to the address of the last location (highest address) in on-chip RAM during reset initialization to free up direct page RAM (from the end of the on-chip registers to \$00FF).

The RSP (reset stack pointer) instruction was included for compatibility with the M68HC05 Family and is seldom used in new HCS08 programs because it only affects the low-order half of the stack pointer.

## 8.3.4 Program Counter (PC)

The program counter is a 16-bit register that contains the address of the next instruction or operand to be fetched.

During normal program execution, the program counter automatically increments to the next sequential memory location every time an instruction or operand is fetched. Jump, branch, interrupt, and return operations load the program counter with an address other than that of the next sequential location. This is called a change-of-flow.

During reset, the program counter is loaded with the reset vector that is located at \$FFFE and \$FFFF. The vector stored there is the address of the first instruction that will be executed after exiting the reset state.

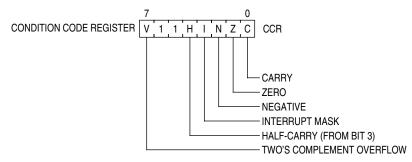

## 8.3.5 Condition Code Register (CCR)

The 8-bit condition code register contains the interrupt mask (I) and five flags that indicate the results of the instruction just executed. Bits 6 and 5 are set permanently to 1. The following paragraphs describe the functions of the condition code bits in general terms. For a more detailed explanation of how each instruction sets the CCR bits, refer to the *HCS08 Family Reference Manual*, *volume 1*, Freescale Semiconductor document order number HCS08RMv1/D.

Figure 8-2. Condition Code Register

**Central Processor Unit (CPU)**

### 8.5.5 BGND Instruction

The BGND instruction is new to the HCS08 compared to the M68HC08. BGND would not be used in normal user programs because it forces the CPU to stop processing user instructions and enter the active background mode. The only way to resume execution of the user program is through reset or by a host debug system issuing a GO, TRACE1, or TAGGO serial command through the background debug interface.

Software-based breakpoints can be set by replacing an opcode at the desired breakpoint address with the BGND opcode. When the program reaches this breakpoint address, the CPU is forced to active background mode rather than continuing the user program.

## 8.6 HCS08 Instruction Set Summary

### **Instruction Set Summary Nomenclature**

The nomenclature listed here is used in the instruction descriptions in Table 8-1.

### **Operators**

() = Contents of register or memory location shown inside parentheses

$\leftarrow$  = Is loaded with (read: "gets")

& = Boolean AND

= Boolean OR

$\oplus$  = Boolean exclusive-OR

$\times$  = Multiply

$\div$  = Divide

: = Concatenate

+ = Add

– = Negate (two's complement)

#### **CPU** registers

A = Accumulator

CCR = Condition code register

H = Index register, higher order (most significant) 8 bits

X = Index register, lower order (least significant) 8 bits

PC = Program counter

PCH = Program counter, higher order (most significant) 8 bits PCL = Program counter, lower order (least significant) 8 bits

SP = Stack pointer

### Memory and addressing

M = A memory location or absolute data, depending on addressing mode

M:M + \$0001= A 16-bit value in two consecutive memory locations. The higher-order (most significant) 8 bits are located at the address of M, and the lower-order (least

significant) 8 bits are located at the next higher sequential address.

MC9S08GB/GT Data Sheet, Rev. 2.3

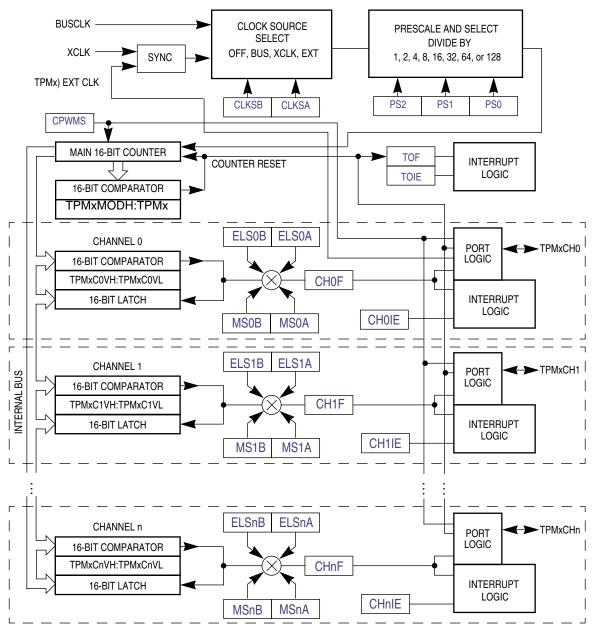

#### **TPM Block Diagram** 10.3

The TPM uses one input/output (I/O) pin per channel, TPMxCHn where x is the TPM number (for example, 1 or 2) and n is the channel number (for example, 0-4). The TPM shares its I/O pins with general-purpose I/O port pins (refer to the Pins and Connections chapter for more information). Figure 10-2 shows the structure of a TPM. Some MCUs include more than one TPM, with various numbers of channels.

Figure 10-2. TPM Block Diagram

The central component of the TPM is the 16-bit counter that can operate as a free-running counter, a modulo counter, or an up-/down-counter when the TPM is configured for center-aligned PWM. The TPM

MC9S08GB/GT Data Sheet, Rev. 2.3 Freescale Semiconductor 153

#### Timer/PWM (TPM) Module

### CHnF — Channel n Flag

When channel n is configured for input capture, this flag bit is set when an active edge occurs on the channel n pin. When channel n is an output compare or edge-aligned PWM channel, CHnF is set when the value in the TPM counter registers matches the value in the TPM channel n value registers. This flag is seldom used with center-aligned PWMs because it is set every time the counter matches the channel value register, which correspond to both edges of the active duty cycle period.

A corresponding interrupt is requested when CHnF is set and interrupts are enabled (CHnIE = 1). Clear CHnF by reading TPMxCnSC while CHnF is set and then writing a 0 to CHnF. If another interrupt request occurs before the clearing sequence is complete, the sequence is reset so CHnF would remain set after the clear sequence was completed for the earlier CHnF. This is done so a CHnF interrupt request cannot be lost by clearing a previous CHnF.

Reset clears the CHnF bit. Writing a 1 to CHnF has no effect.

- 1 = Input capture or output compare event occurred on channel n.

- 0 = No input capture or output compare event occurred on channel n.

### CHnIE — Channel n Interrupt Enable

This read/write bit enables interrupts from channel n. Reset clears the CHnIE bit.

- 1 = Channel n interrupt requests enabled.

- 0 = Channel n interrupt requests disabled (use software polling).

#### MSnB — Mode Select B for TPM Channel n

When CPWMS = 0, MSnB = 1 configures TPM channel n for edge-aligned PWM mode. For a summary of channel mode and setup controls, refer to Table 10-3.

#### MSnA — Mode Select A for TPM Channel n

When CPWMS = 0 and MSnB = 0, MSnA configures TPM channel n for input capture mode or output compare mode. Refer to Table 10-3 for a summary of channel mode and setup controls.

#### Serial Communications Interface (SCI) Module

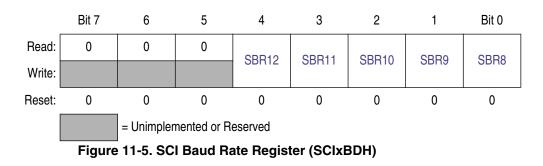

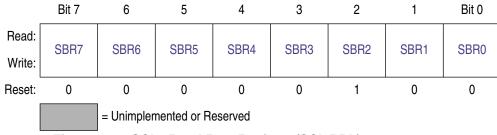

Figure 11-6. SCI x Baud Rate Register (SCIxBDL)

#### SBR12:SBR0 — Baud Rate Modulo Divisor

These 13 bits are referred to collectively as BR, and they set the modulo divide rate for the SCI baud rate generator. When BR = 0, the SCI baud rate generator is disabled to reduce supply current. When BR = 1 to 8191, the SCI baud rate =  $BUSCLK/(16 \times BR)$ .

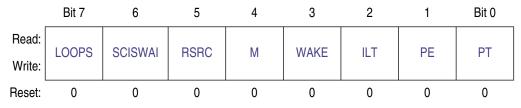

## 11.10.2 SCI x Control Register 1 (SCIxC1)

This read/write register is used to control various optional features of the SCI system.

Figure 11-7. SCI x Control Register 1 (SCIxC1)

### LOOPS — Loop Mode Select

Selects between loop back modes and normal 2-pin full-duplex modes. When LOOPS = 1, the transmitter output is internally connected to the receiver input.

- 1 = Loop mode or single-wire mode where transmitter outputs are internally connected to receiver input. (See RSRC bit.) RxD1 pin is not used by SCI.

- 0 = Normal operation RxD1 and TxD1 use separate pins.

Inter-Integrated Circuit (IIC) Module

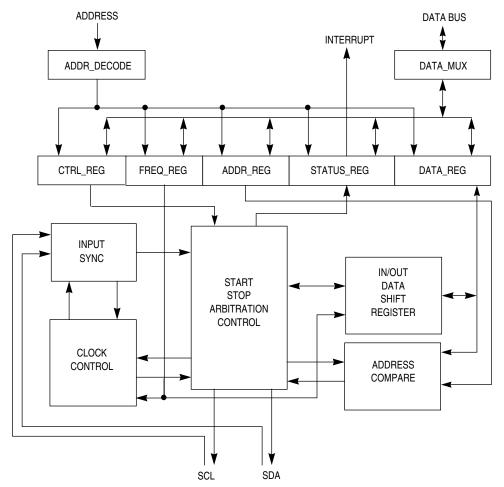

## 13.1.3 Block Diagram

Figure 13-2 is a block diagram of the IIC.

Figure 13-2. IIC Functional Block Diagram

## 13.1.4 Detailed Signal Descriptions

This section describes each user-accessible pin signal.

## 13.1.4.1 SCL1 — Serial Clock Line

The bidirectional SCL1 is the serial clock line of the IIC system.

## 13.1.4.2 SDA1 — Serial Data Line

The bidirectional SDA1 is the serial data line of the IIC system

### Inter-Integrated Circuit (IIC) Module

Table 13-3. IIC Divider and Hold Values

| 00         20         7           01         22         7           02         24         8           03         26         8           04         28         9           05         30         9           06         34         10           07         40         10           08         28         7           09         32         7           0A         36         9           0B         40         9           0C         44         11           0D         48         11           0E         56         13           0F         68         13           10         48         9           11         56         9           12         64         13           13         72         13           14         80         17           15         88         17           16         104         21           17         128         21           18         80         9           19         96         9 | ICR<br>(hex) | SCL Divider | SDA Hold<br>Value |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------|-------------------|

| 01       22       7         02       24       8         03       26       8         04       28       9         05       30       9         06       34       10         07       40       10         08       28       7         09       32       7         0A       36       9         0B       40       9         0C       44       11         0D       48       11         0E       56       13         0F       68       13         10       48       9         11       56       9         12       64       13         13       72       13         14       80       17         15       88       17         16       104       21         17       128       21         18       80       9         19       96       9         1A       112       17         1B       128       17                                                                                                                           |              | 20          |                   |

| 02       24       8         03       26       8         04       28       9         05       30       9         06       34       10         07       40       10         08       28       7         09       32       7         0A       36       9         0B       40       9         0C       44       11         0D       48       11         0E       56       13         0F       68       13         10       48       9         11       56       9         12       64       13         13       72       13         14       80       17         15       88       17         16       104       21         17       128       21         18       80       9         19       96       9         1A       112       17         1B       128       17                                                                                                                                                       |              |             |                   |

| 03       26       8         04       28       9         05       30       9         06       34       10         07       40       10         08       28       7         09       32       7         0A       36       9         0B       40       9         0C       44       11         0D       48       11         0E       56       13         0F       68       13         10       48       9         11       56       9         12       64       13         13       72       13         14       80       17         15       88       17         16       104       21         17       128       21         18       80       9         19       96       9         1A       112       17         1B       128       17                                                                                                                                                                                   |              |             | -                 |

| 04       28       9         05       30       9         06       34       10         07       40       10         08       28       7         09       32       7         0A       36       9         0B       40       9         0C       44       11         0D       48       11         0E       56       13         0F       68       13         10       48       9         11       56       9         12       64       13         13       72       13         14       80       17         15       88       17         16       104       21         17       128       21         18       80       9         19       96       9         1A       112       17         1B       128       17                                                                                                                                                                                                               |              |             | _                 |

| 05       30       9         06       34       10         07       40       10         08       28       7         09       32       7         0A       36       9         0B       40       9         0C       44       11         0D       48       11         0E       56       13         0F       68       13         10       48       9         11       56       9         12       64       13         13       72       13         14       80       17         15       88       17         16       104       21         17       128       21         18       80       9         19       96       9         1A       112       17         1B       128       17                                                                                                                                                                                                                                           |              |             |                   |

| 06       34       10         07       40       10         08       28       7         09       32       7         0A       36       9         0B       40       9         0C       44       11         0D       48       11         0E       56       13         0F       68       13         10       48       9         11       56       9         12       64       13         13       72       13         14       80       17         15       88       17         16       104       21         17       128       21         18       80       9         19       96       9         1A       112       17         1B       128       17                                                                                                                                                                                                                                                                       | _            | _           |                   |

| 07       40       10         08       28       7         09       32       7         0A       36       9         0B       40       9         0C       44       11         0D       48       11         0E       56       13         0F       68       13         10       48       9         11       56       9         12       64       13         13       72       13         14       80       17         15       88       17         16       104       21         17       128       21         18       80       9         19       96       9         1A       112       17         1B       128       17                                                                                                                                                                                                                                                                                                    |              |             | _                 |

| 08       28       7         09       32       7         0A       36       9         0B       40       9         0C       44       11         0D       48       11         0E       56       13         0F       68       13         10       48       9         11       56       9         12       64       13         13       72       13         14       80       17         15       88       17         16       104       21         17       128       21         18       80       9         19       96       9         1A       112       17         1B       128       17                                                                                                                                                                                                                                                                                                                                 |              |             |                   |

| 09       32       7         0A       36       9         0B       40       9         0C       44       11         0D       48       11         0E       56       13         0F       68       13         10       48       9         11       56       9         12       64       13         13       72       13         14       80       17         15       88       17         16       104       21         17       128       21         18       80       9         19       96       9         1A       112       17         1B       128       17                                                                                                                                                                                                                                                                                                                                                             |              | _           |                   |

| 0A       36       9         0B       40       9         0C       44       11         0D       48       11         0E       56       13         0F       68       13         10       48       9         11       56       9         12       64       13         13       72       13         14       80       17         15       88       17         16       104       21         17       128       21         18       80       9         19       96       9         1A       112       17         1B       128       17                                                                                                                                                                                                                                                                                                                                                                                         | 08           | 28          |                   |

| 0B       40       9         0C       44       11         0D       48       11         0E       56       13         0F       68       13         10       48       9         11       56       9         12       64       13         13       72       13         14       80       17         15       88       17         16       104       21         17       128       21         18       80       9         19       96       9         1A       112       17         1B       128       17                                                                                                                                                                                                                                                                                                                                                                                                                     |              | 32          | 7                 |

| 0C     44     11       0D     48     11       0E     56     13       0F     68     13       10     48     9       11     56     9       12     64     13       13     72     13       14     80     17       15     88     17       16     104     21       17     128     21       18     80     9       19     96     9       1A     112     17       1B     128     17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0A           | 36          | 9                 |

| 0D       48       11         0E       56       13         0F       68       13         10       48       9         11       56       9         12       64       13         13       72       13         14       80       17         15       88       17         16       104       21         17       128       21         18       80       9         19       96       9         1A       112       17         1B       128       17                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0B           | 40          | 9                 |

| 0E     56     13       0F     68     13       10     48     9       11     56     9       12     64     13       13     72     13       14     80     17       15     88     17       16     104     21       17     128     21       18     80     9       19     96     9       1A     112     17       1B     128     17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0C           | 44          | 11                |

| 0F     68     13       10     48     9       11     56     9       12     64     13       13     72     13       14     80     17       15     88     17       16     104     21       17     128     21       18     80     9       19     96     9       1A     112     17       1B     128     17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0D           | 48          | 11                |

| 10     48     9       11     56     9       12     64     13       13     72     13       14     80     17       15     88     17       16     104     21       17     128     21       18     80     9       19     96     9       1A     112     17       1B     128     17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0E           | 56          | 13                |

| 11     56     9       12     64     13       13     72     13       14     80     17       15     88     17       16     104     21       17     128     21       18     80     9       19     96     9       1A     112     17       1B     128     17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0F           | 68          | 13                |

| 12     64     13       13     72     13       14     80     17       15     88     17       16     104     21       17     128     21       18     80     9       19     96     9       1A     112     17       1B     128     17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10           | 48          | 9                 |

| 13     72     13       14     80     17       15     88     17       16     104     21       17     128     21       18     80     9       19     96     9       1A     112     17       1B     128     17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11           | 56          | 9                 |

| 14     80     17       15     88     17       16     104     21       17     128     21       18     80     9       19     96     9       1A     112     17       1B     128     17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12           | 64          | 13                |

| 15     88     17       16     104     21       17     128     21       18     80     9       19     96     9       1A     112     17       1B     128     17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13           | 72          | 13                |

| 16     104     21       17     128     21       18     80     9       19     96     9       1A     112     17       1B     128     17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 14           | 80          | 17                |

| 17     128     21       18     80     9       19     96     9       1A     112     17       1B     128     17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15           | 88          | 17                |

| 18     80     9       19     96     9       1A     112     17       1B     128     17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16           | 104         | 21                |

| 19     96     9       1A     112     17       1B     128     17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17           | 128         | 21                |

| 1A 112 17<br>1B 128 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18           | 80          | 9                 |

| 1B 128 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 19           | 96          | 9                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1A           | 112         | 17                |

| 1C 144 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1B           | 128         | 17                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1C           | 144         | 25                |

| 1D 160 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              | 160         | 25                |