Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Obsolete                                                             |

| Core Processor             | S08                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 40MHz                                                                |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                           |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 34                                                                   |

| Program Memory Size        | 60KB (60K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 4K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                          |

| Data Converters            | A/D 8x10b                                                            |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Through Hole                                                         |

| Package / Case             | 42-SDIP (0.600", 15.24mm)                                            |

| Supplier Device Package    | 42-PDIP                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08gt60cb |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Section Number **Title Page Chapter 7 Internal Clock Generator (ICG) Module** 7.1 Introduction ......99 Features 100 7.1.2 Modes of Operation ......101 7.2 7.2.1 7.2.2 7.2.2.1 7.2.2.2 7.2.3 7.2.4 7.3.1 7.3.1.1 7.3.1.2 7.3.1.3 7.3.2 7.3.3 FLL Bypassed, External Clock (FBE) Mode ......106 7.3.4 7.3.5 7.3.5.2 7.3.6 7.3.7 7.3.8 7.3.9 7.4 7.4.1 7.4.2 Example #1: External Crystal = 32 kHz, Bus Frequency = 4.19 MHz ......112 7.4.3 Example #3: No External Crystal Connection, 5.4 MHz Bus Frequency .......114 7.4.4 7.4.5 7.5 7.5.1 ICG Control Register 2 (ICGC2) ......119 7.5.2 7.5.3 7.5.4 ICG Filter Registers (ICGFLTU, ICGFLTL) ......122 7.5.5 7.5.6

#### **Chapter 4 Memory**

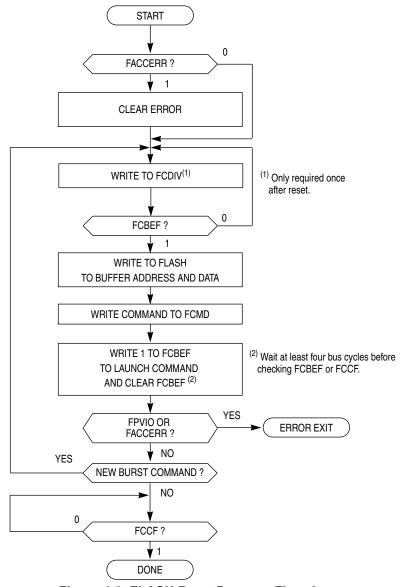

program time provided that the conditions above are met. In the case the next sequential address is the beginning of a new row, the program time for that byte will be the standard time instead of the burst time. This is because the high voltage to the array must be disabled and then enabled again. If a new burst command has not been queued before the current command completes, then the charge pump will be disabled and high voltage removed from the array.

Figure 4-3. FLASH Burst Program Flowchart

### 4.4.5 Access Errors

An access error occurs whenever the command execution protocol is violated.

• Any of the following specific actions will cause the access error flag (FACCERR) in FSTAT to be set. FACCERR must be cleared by writing a 1 to FACCERR in FSTAT before any command can be processed.

|        | Bit 7  | 6     | 5    | 4    | 3    | 2 | 1 | Bit 0 |

|--------|--------|-------|------|------|------|---|---|-------|

| Read:  | FPOPEN | FPDIS | FPS2 | FPS1 | FPS0 | 0 | 0 | 0     |

| Write: | 1      | (1)   | (1)  | (1)  | (1)  |   |   |       |

Reset:

This register is loaded from nonvolatile location NVPROT during reset.

= Unimplemented or Reserved

### Figure 4-7. FLASH Protection Register (FPROT)

### FPOPEN — Open Unprotected FLASH for Program/Erase

- 1 = Any FLASH location, not otherwise block protected or secured, may be erased or programmed.

- 0 = Entire FLASH memory is block protected (no program or erase allowed).

#### FPDIS — FLASH Protection Disable

- 1 = No FLASH block is protected.

- 0 = FLASH block specified by FPS2:FPS0 is block protected (program and erase not allowed).

### FPS2:FPS1:FPS0 — FLASH Protect Size Selects

When FPDIS = 0, this 3-bit field determines the size of a protected block of FLASH locations at the high address end of the FLASH (see Table 4-8). Protected FLASH locations cannot be erased or programmed.

**Table 4-8. High Address Protected Block**

| FPS2:FPS1:FPS0 | Protected Address Range | Protected Block Size | Redirected Vectors <sup>1</sup> |

|----------------|-------------------------|----------------------|---------------------------------|

| 0:0:0          | \$FE00-\$FFFF           | 512 bytes            | \$FDC0-\$FDFD <sup>2</sup>      |

| 0:0:1          | \$FC00-\$FFFF           | 1024 bytes           | \$FBC0-\$FBFD                   |

| 0:1:0          | \$F800-\$FFFF           | 2048 bytes           | \$F7C0-\$F7FD                   |

| 0:1:1          | \$F000-\$FFFF           | 4096 bytes           | \$EFC0-\$EFFD                   |

| 1:0:0          | \$E000-\$FFFF           | 8192 bytes           | \$DFC0-\$DFFD                   |

| 1:0:1          | \$C000-\$FFFF           | 16384 bytes          | \$BFC0-\$BFFD <sup>3</sup>      |

| 1:1:0          | \$8000-\$FFFF           | 32768 bytes          | \$7FC0-\$7FFD <sup>4</sup>      |

| 1:1:1          | \$8000-\$FFFF           | 32768 bytes          | \$7FC0-\$7FFD <sup>4</sup>      |

<sup>&</sup>lt;sup>1</sup> No redirection if FPOPEN = 0, or FNORED = 1.

Background commands can be used to change the contents of these bits in FPROT.

<sup>&</sup>lt;sup>2</sup> Reset vector is not redirected.

<sup>3 32</sup>K and 60K devices only.

<sup>&</sup>lt;sup>4</sup> 60K devices only.

#### Chapter 6 Parallel Input/Output

| PTCD  |                 | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

|-------|-----------------|--------|--------|--------|--------|--------|--------|--------|--------|

|       | Read:<br>Write: | PTCD7  | PTCD6  | PTCD5  | PTCD4  | PTCD3  | PTCD2  | PTCD1  | PTCD0  |

|       | Reset:          | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| PTCPE |                 |        |        |        |        |        |        |        |        |

|       | Read:<br>Write: | PTCPE7 | PTCPE6 | PTCPE5 | PTCPE4 | PTCPE3 | PTCPE2 | PTCPE1 | PTCPE0 |

|       | Reset:          | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| PTCSE |                 |        |        |        |        |        |        |        |        |

|       | Read:<br>Write: | PTCSE7 | PTCSE6 | PTCSE5 | PTCSE4 | PTCSE3 | PTCSE2 | PTCSE1 | PTCSE0 |

|       | Reset:          | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| PTCDD |                 |        |        |        |        |        |        |        |        |

|       | Read:<br>Write: | PTCDD7 | PTCDD6 | PTCDD5 | PTCDD4 | PTCDD3 | PTCDD2 | PTCDD1 | PTCDD0 |

|       | Reset:          | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

Figure 6-11. Port C Registers

### PTCDn — Port C Data Register Bit n (n = 0-7)

For port C pins that are inputs, reads return the logic level on the pin. For port C pins that are configured as outputs, reads return the last value written to this register.

Writes are latched into all bits of this register. For port C pins that are configured as outputs, the logic level is driven out the corresponding MCU pin.

Reset forces PTCD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled.

### PTCPEn — Pullup Enable for Port C Bit n (n = 0-7)

For port C pins that are inputs, these read/write control bits determine whether internal pullup devices are enabled. For port C pins that are configured as outputs, these bits are ignored and the internal pullup devices are disabled.

- 1 = Internal pullup device enabled.

- 0 = Internal pullup device disabled.

### PTCSEn — Slew Rate Control Enable for Port C Bit n (n = 0-7)

For port C pins that are outputs, these read/write control bits determine whether the slew rate controlled outputs are enabled. For port B pins that are configured as inputs, these bits are ignored.

- 1 = Slew rate control enabled.

- 0 =Slew rate control disabled.

#### MC9S08GB/GT Data Sheet, Rev. 2.3

#### KBEDGn — Keyboard Edge Select for KBI Port Bit n (n = 7-4)

Each of these read/write bits selects the polarity of the edges and/or levels that are recognized as trigger events on the corresponding KBI port pin when it is configured as a keyboard interrupt input (KBIPEn = 1). Also see the KBIMOD control bit, which determines whether the pin is sensitive to edges-only or edges and levels.

- 1 = Rising edges/high levels.

- 0 = Falling edges/low levels.

### KBF — Keyboard Interrupt Flag

This read-only status flag is set whenever the selected edge event has been detected on any of the enabled KBI port pins. This flag is cleared by writing a 1 to the KBACK control bit. The flag will remain set if KBIMOD = 1 to select edge-and-level operation and any enabled KBI port pin remains at the asserted level.

- 1 = KBI interrupt pending.

- 0 = No KBI interrupt pending.

KBF can be used as a software pollable flag (KBIE = 0) or it can generate a hardware interrupt request to the CPU (KBIE = 1).

### KBACK — Keyboard Interrupt Acknowledge

This write-only bit (reads always return 0) is used to clear the KBF status flag by writing a 1 to KBACK. When KBIMOD = 1 to select edge-and-level operation and any enabled KBI port pin remains at the asserted level, KBF is being continuously set so writing 1 to KBACK does not clear the KBF flag.

### KBIE — Keyboard Interrupt Enable

This read/write control bit determines whether hardware interrupts are generated when the KBF status flag equals 1. When KBIE = 0, no hardware interrupts are generated, but KBF can still be used for software polling.

- 1 = KBI hardware interrupt requested when KBF = 1.

- 0 = KBF does not generate hardware interrupts (use polling).

### KBIMOD — Keyboard Detection Mode

This read/write control bit selects either edge-only detection or edge-and-level detection. KBI port bits 3 through 0 can detect falling edges-only or falling edges and low levels.

KBI port bits 7 through 4 can be configured to detect either:

- Rising edges-only or rising edges and high levels (KBEDGn = 1)

- Falling edges-only or falling edges and low levels (KBEDGn = 0)

- 1 = Edge-and-level detection.

- 0 = Edge-only detection.

associated TPM act as center-aligned PWM channels. When CPWMS = 0, each channel can independently be configured to operate in input capture, output compare, or buffered edge-aligned PWM mode.

The following sections describe the main 16-bit counter and each of the timer operating modes (input capture, output compare, edge-aligned PWM, and center-aligned PWM). Because details of pin operation and interrupt activity depend on the operating mode, these topics are covered in the associated mode sections.

#### 10.5.1 Counter

All timer functions are based on the main 16-bit counter (TPMxCNTH:TPMxCNTL). This section discusses selection of the clock source, up-counting vs. up-/down-counting, end-of-count overflow, and manual counter reset.

After any MCU reset, CLKSB:CLKSA = 0:0 so no clock source is selected and the TPM is inactive. Normally, CLKSB:CLKSA would be set to 0:1 so the bus clock drives the timer counter. The clock source for each of the TPM can be independently selected to be off, the bus clock (BUSCLK), the fixed system clock (XCLK), or an external input through the TPMxCH0 pin. The maximum frequency allowed for the external clock option is one-fourth the bus rate. Refer to Section 10.7.1, "Timer x Status and Control Register (TPMxSC)," and Table 10-1 for more information about clock source selection.

When the microcontroller is in active background mode, the TPM temporarily suspends all counting until the microcontroller returns to normal user operating mode. During stop mode, all TPM clocks are stopped; therefore, the TPM is effectively disabled until clocks resume. During wait mode, the TPM continues to operate normally.

The main 16-bit counter has two counting modes. When center-aligned PWM is selected (CPWMS = 1), the counter operates in up-/down-counting mode. Otherwise, the counter operates as a simple up-counter. As an up-counter, the main 16-bit counter counts from \$0000 through its terminal count and then continues with \$0000. The terminal count is \$FFFF or a modulus value in TPMxMODH:TPMxMODL.

When center-aligned PWM operation is specified, the counter counts upward from \$0000 through its terminal count and then counts downward to \$0000 where it returns to up-counting. Both \$0000 and the terminal count value (value in TPMxMODH:TPMxMODL) are normal length counts (one timer clock period long).

An interrupt flag and enable are associated with the main 16-bit counter. The timer overflow flag (TOF) is a software-accessible indication that the timer counter has overflowed. The enable signal selects between software polling (TOIE = 0) where no hardware interrupt is generated, or interrupt-driven operation (TOIE = 1) where a static hardware interrupt is automatically generated whenever the TOF flag is 1.

The conditions that cause TOF to become set depend on the counting mode (up or up/down). In up-counting mode, the main 16-bit counter counts from \$0000 through \$FFFF and overflows to \$0000 on the next counting clock. TOF becomes set at the transition from \$FFFF to \$0000. When a modulus limit is set, TOF becomes set at the transition from the value set in the modulus register to \$0000. When the main 16-bit counter is operating in up-/down-counting mode, the TOF flag gets set as the counter changes direction at the transition from the value set in the modulus register and the next lower count value. This corresponds to the end of a PWM period. (The \$0000 count value corresponds to the center of a period.)

#### Serial Communications Interface (SCI) Module

When polling is used, this sequence is naturally satisfied in the normal course of the user program. If hardware interrupts are used, SCIxS1 must be read in the interrupt service routine (ISR). Normally, this is done in the ISR anyway to check for receive errors, so the sequence is automatically satisfied.

The IDLE status flag includes logic that prevents it from getting set repeatedly when the RxD1 line remains idle for an extended period of time. IDLE is cleared by reading SCIxS1 while IDLE = 1 and then reading SCIxD. After IDLE has been cleared, it cannot become set again until the receiver has received at least one new character and has set RDRF.

If the associated error was detected in the received character that caused RDRF to be set, the error flags — noise flag (NF), framing error (FE), and parity error flag (PF) — get set at the same time as RDRF. These flags are not set in overrun cases.

If RDRF was already set when a new character is ready to be transferred from the receive shifter to the receive data buffer, the overrun (OR) flag gets set instead and the data and any associated NF, FE, or PF condition is lost.

### 11.8 Additional SCI Functions

The following sections describe additional SCI functions.

### 11.8.1 8- and 9-Bit Data Modes

The SCI system (transmitter and receiver) can be configured to operate in 9-bit data mode by setting the M control bit in SCIxC1. In 9-bit mode, there is a ninth data bit to the left of the MSB of the SCI data register. For the transmit data buffer, this bit is stored in T8 in SCIxC3. For the receiver, the ninth bit is held in R8 in SCIxC3.

When transmitting 9-bit data, write to the T8 bit before writing to SCIxD for coherent writes to the transmit data buffer. If the bit value to be transmitted as the ninth bit of a new character is the same as for the previous character, it is not necessary to write to T8 again. When data is transferred from the transmit data buffer to the transmit shifter, the value in T8 is copied at the same time data is transferred from SCIxD to the shifter.

When receiving 9-bit data, clear the RDRF bit by reading both R8 and SCIxD. R8 and SCIxD can be read in either order.

9-bit data mode typically is used in conjunction with parity to allow eight bits of data plus the parity in the ninth bit. Or it is used with address-mark wakeup so the ninth data bit can serve as the wakeup bit. In custom protocols, the ninth bit can also serve as a software-controlled marker.

# 11.9 Stop Mode Operation

During all stop modes, clocks to the SCI module are halted.

In stop1 and stop2 modes, all SCI register data is lost and must be re-initialized upon recovery from these two stop modes.

No SCI module registers are affected in stop3 mode.

#### Serial Communications Interface (SCI) Module

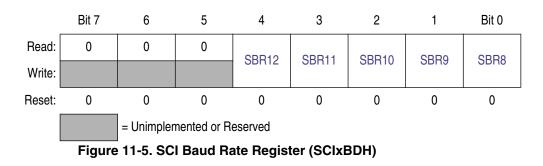

Figure 11-6. SCI x Baud Rate Register (SCIxBDL)

#### SBR12:SBR0 — Baud Rate Modulo Divisor

These 13 bits are referred to collectively as BR, and they set the modulo divide rate for the SCI baud rate generator. When BR = 0, the SCI baud rate generator is disabled to reduce supply current. When BR = 1 to 8191, the SCI baud rate =  $BUSCLK/(16 \times BR)$ .

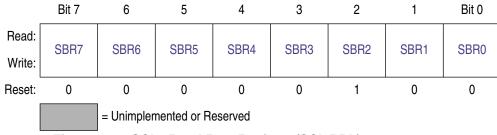

## 11.10.2 SCI x Control Register 1 (SCIxC1)

This read/write register is used to control various optional features of the SCI system.

Figure 11-7. SCI x Control Register 1 (SCIxC1)

### LOOPS — Loop Mode Select

Selects between loop back modes and normal 2-pin full-duplex modes. When LOOPS = 1, the transmitter output is internally connected to the receiver input.

- 1 = Loop mode or single-wire mode where transmitter outputs are internally connected to receiver input. (See RSRC bit.) RxD1 pin is not used by SCI.

- 0 = Normal operation RxD1 and TxD1 use separate pins.

#### RE — Receiver Enable

When the SCI receiver is off, the RxD1 pin reverts to being a general-purpose port I/O pin.

- 1 =Receiver on.

- 0 = Receiver off.

#### RWU — Receiver Wakeup Control

This bit can be written to 1 to place the SCI receiver in a standby state where it waits for automatic hardware detection of a selected wakeup condition. The wakeup condition is either an idle line between messages (WAKE = 0, idle-line wakeup), or a logic 1 in the most significant data bit in a character (WAKE = 1, address-mark wakeup). Application software sets RWU and (normally) a selected hardware condition automatically clears RWU. Refer to Section 11.6.3, "Receiver Wakeup Operation," for more details.

- 1 = SCI receiver in standby waiting for wakeup condition.

- 0 = Normal SCI receiver operation.

#### SBK — Send Break

Writing a 1 and then a 0 to SBK queues a break character in the transmit data stream. Additional break characters of 10 or 11 bit times of logic 0 are queued as long as SBK = 1. Depending on the timing of the set and clear of SBK relative to the information currently being transmitted, a second break character may be queued before software clears SBK. Refer to Section 11.5.2, "Send Break and Queued Idle," for more details.

- 1 = Queue break character(s) to be sent.

- 0 = Normal transmitter operation.

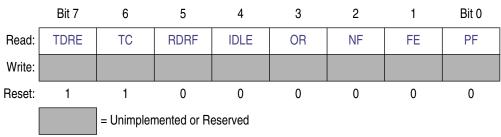

# 11.10.4 SCI x Status Register 1 (SCIxS1)

This register has eight read-only status flags. Writes have no effect. Special software sequences (that do not involve writing to this register) are used to clear these status flags.

Figure 11-9. SCI x Status Register 1 (SCIxS1)

#### TDRE — Transmit Data Register Empty Flag

TDRE is set out of reset and when a transmit data value transfers from the transmit data buffer to the transmit shifter, leaving room for a new character in the buffer. To clear TDRE, read SCIxS1 with TDRE = 1 and then write to the SCI data register (SCIxD).

- 1 = Transmit data register (buffer) empty.

- 0 = Transmit data register (buffer) full.

MC9S08GB/GT Data Sheet, Rev. 2.3

#### OR — Receiver Overrun Flag

OR is set when a new serial character is ready to be transferred to the receive data register (buffer), but the previously received character has not been read from SCIxD yet. In this case, the new character (and all associated error information) is lost because there is no room to move it into SCIxD. To clear OR, read SCIxS1 with OR = 1 and then read the SCI data register (SCIxD).

- 1 = Receive overrun (new SCI data lost).

- 0 = No overrun.

#### NF — Noise Flag

The advanced sampling technique used in the receiver takes seven samples during the start bit and three samples in each data bit and the stop bit. If any of these samples disagrees with the rest of the samples within any bit time in the frame, the flag NF will be set at the same time as the flag RDRF gets set for the character. To clear NF, read SCIxS1 and then read the SCI data register (SCIxD).

- 1 = Noise detected in the received character in SCIxD.

- 0 = No noise detected.

#### FE — Framing Error Flag

FE is set at the same time as RDRF when the receiver detects a logic 0 where the stop bit was expected. This suggests the receiver was not properly aligned to a character frame. To clear FE, read SCIxS1 with FE = 1 and then read the SCI data register (SCIxD).

- 1 = Framing error.

- 0 = No framing error detected. This does not guarantee the framing is correct.

#### PF — Parity Error Flag

PF is set at the same time as RDRF when parity is enabled (PE = 1) and the parity bit in the received character does not agree with the expected parity value. To clear PF, read SCIxS1 and then read the SCI data register (SCIxD).

- 1 = Parity error.

- 0 = No parity error.

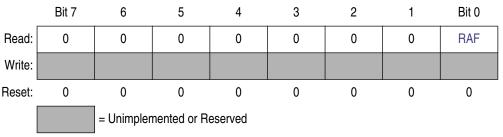

# 11.10.5 SCI x Status Register 2 (SCIxS2)

This register has one read-only status flag. Writes have no effect.

Figure 11-10. SCI x Status Register 2 (SCIxS2)

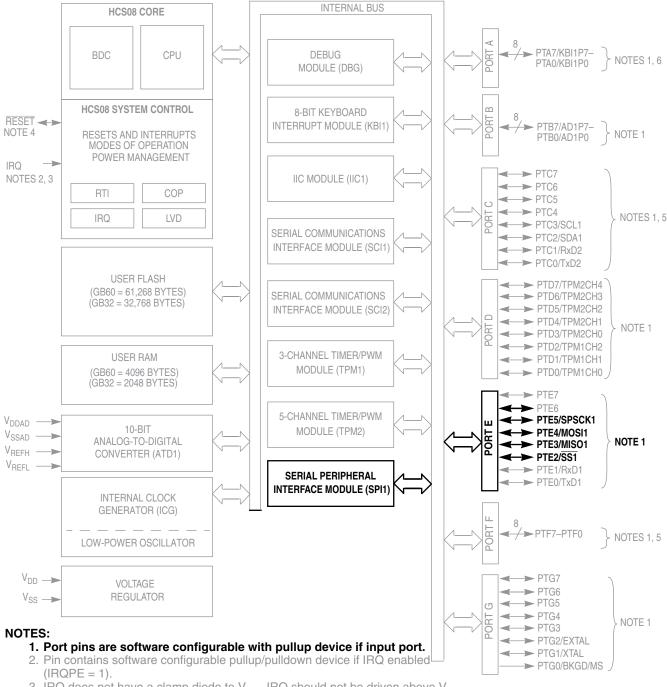

#### Chapter 12 Serial Peripheral Interface (SPI) Module

- 3. IRQ does not have a clamp diode to  $V_{DD}$ . IRQ should not be driven above  $V_{DD}$ .

- 4. Pin contains integrated pullup device.

- 5. High current drive

- 6. Pins PTA[7:4] contain both pullup and pulldown devices. Pulldown available when KBI enabled (KBIPn = 1).

Figure 12-1. Block Diagram Highlighting the SPI Module

Serial Peripheral Interface (SPI) Module

### 12.3.3 SPI Interrupts

There are three flag bits, two interrupt mask bits, and one interrupt vector associated with the SPI system. The SPI interrupt enable mask (SPIE) enables interrupts from the SPI receiver full flag (SPRF) and mode fault flag (MODF). The SPI transmit interrupt enable mask (SPTIE) enables interrupts from the SPI transmit buffer empty flag (SPTEF). When one of the flag bits is set, and the associated interrupt mask bit is set, a hardware interrupt request is sent to the CPU. If the interrupt mask bits are cleared, software can poll the associated flag bits instead of using interrupts. The SPI interrupt service routine (ISR) should check the flag bits to determine what event caused the interrupt. The service routine should also clear the flag bit(s) before returning from the ISR (usually near the beginning of the ISR).

#### 12.3.4 Mode Fault Detection

A mode fault occurs and the mode fault flag (MODF) becomes set when a master SPI device detects an error on the  $\overline{SS1}$  pin (provided the  $\overline{SS1}$  pin is configured as the mode fault input signal). The  $\overline{SS1}$  pin is configured to be the mode fault input signal when MSTR = 1, mode fault enable is set (MODFEN = 1), and slave select output enable is clear (SSOE = 0).

The mode fault detection feature can be used in a system where more than one SPI device might become a master at the same time. The error is detected when a master's  $\overline{SS1}$  pin is low, indicating that some other SPI device is trying to address this master as if it were a slave. This could indicate a harmful output driver conflict, so the mode fault logic is designed to disable all SPI output drivers when such an error is detected.

When a mode fault is detected, MODF is set and MSTR is cleared to change the SPI configuration back to slave mode. The output drivers on the SPSCK1, MOSI1, and MISO1 (if not bidirectional mode) are disabled.

MODF is cleared by reading it while it is set, then writing to the SPI control register 1 (SPI1C1). User software should verify the error condition has been corrected before changing the SPI back to master mode.

# 12.4 SPI Registers and Control Bits

The SPI has five 8-bit registers to select SPI options, control baud rate, report SPI status, and for transmit/receive data.

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all SPI registers. This section refers to registers and control bits only by their names, and a Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

### Inter-Integrated Circuit (IIC) Module

Table 13-3. IIC Divider and Hold Values

| 00 20 7 01 22 7 02 24 8 03 26 8 04 28 9 05 30 9 06 34 10 07 40 10 08 28 7 09 32 7 0A 36 9 0B 40 9 0C 44 11 0D 48 11 0D 48 11 0E 56 13 0F 68 13 10 48 9 11 56 9 12 64 13 13 72 13 14 80 17 15 88 17 16 104 21 17 128 21 18 80 9 19 96 9 11 18 128 17 16 114 12 17 18 128 17 16 114 128 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ICR<br>(hex) | SCL Divider | SDA Hold<br>Value |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------|-------------------|

| 01       22       7         02       24       8         03       26       8         04       28       9         05       30       9         06       34       10         07       40       10         08       28       7         09       32       7         0A       36       9         0B       40       9         0C       44       11         0D       48       11         0E       56       13         0F       68       13         10       48       9         11       56       9         12       64       13         13       72       13         14       80       17         15       88       17         16       104       21         17       128       21         18       80       9         19       96       9         1A       112       17         1B       128       17 |              | 20          |                   |

| 02       24       8         03       26       8         04       28       9         05       30       9         06       34       10         07       40       10         08       28       7         09       32       7         0A       36       9         0B       40       9         0C       44       11         0D       48       11         0E       56       13         0F       68       13         10       48       9         11       56       9         12       64       13         13       72       13         14       80       17         15       88       17         16       104       21         17       128       21         18       80       9         19       96       9         1A       112       17         1B       128       17                             |              |             |                   |

| 03       26       8         04       28       9         05       30       9         06       34       10         07       40       10         08       28       7         09       32       7         0A       36       9         0B       40       9         0C       44       11         0D       48       11         0E       56       13         0F       68       13         10       48       9         11       56       9         12       64       13         13       72       13         14       80       17         15       88       17         16       104       21         17       128       21         18       80       9         19       96       9         1A       112       17         1B       128       17                                                         |              |             | -                 |

| 04       28       9         05       30       9         06       34       10         07       40       10         08       28       7         09       32       7         0A       36       9         0B       40       9         0C       44       11         0D       48       11         0E       56       13         0F       68       13         10       48       9         11       56       9         12       64       13         13       72       13         14       80       17         15       88       17         16       104       21         17       128       21         18       80       9         19       96       9         1A       112       17         1B       128       17                                                                                     |              |             | _                 |

| 05       30       9         06       34       10         07       40       10         08       28       7         09       32       7         0A       36       9         0B       40       9         0C       44       11         0D       48       11         0E       56       13         0F       68       13         10       48       9         11       56       9         12       64       13         13       72       13         14       80       17         15       88       17         16       104       21         17       128       21         18       80       9         19       96       9         1A       112       17         1B       128       17                                                                                                                 |              |             |                   |

| 06       34       10         07       40       10         08       28       7         09       32       7         0A       36       9         0B       40       9         0C       44       11         0D       48       11         0E       56       13         0F       68       13         10       48       9         11       56       9         12       64       13         13       72       13         14       80       17         15       88       17         16       104       21         17       128       21         18       80       9         19       96       9         1A       112       17         1B       128       17                                                                                                                                             | _            | _           |                   |

| 07       40       10         08       28       7         09       32       7         0A       36       9         0B       40       9         0C       44       11         0D       48       11         0E       56       13         0F       68       13         10       48       9         11       56       9         12       64       13         13       72       13         14       80       17         15       88       17         16       104       21         17       128       21         18       80       9         19       96       9         1A       112       17         1B       128       17                                                                                                                                                                          |              |             | _                 |

| 08       28       7         09       32       7         0A       36       9         0B       40       9         0C       44       11         0D       48       11         0E       56       13         0F       68       13         10       48       9         11       56       9         12       64       13         13       72       13         14       80       17         15       88       17         16       104       21         17       128       21         18       80       9         19       96       9         1A       112       17         1B       128       17                                                                                                                                                                                                       |              |             |                   |

| 09       32       7         0A       36       9         0B       40       9         0C       44       11         0D       48       11         0E       56       13         0F       68       13         10       48       9         11       56       9         12       64       13         13       72       13         14       80       17         15       88       17         16       104       21         17       128       21         18       80       9         19       96       9         1A       112       17         1B       128       17                                                                                                                                                                                                                                   |              | _           |                   |

| 0A       36       9         0B       40       9         0C       44       11         0D       48       11         0E       56       13         0F       68       13         10       48       9         11       56       9         12       64       13         13       72       13         14       80       17         15       88       17         16       104       21         17       128       21         18       80       9         19       96       9         1A       112       17         1B       128       17                                                                                                                                                                                                                                                               | 08           | 28          |                   |

| 0B       40       9         0C       44       11         0D       48       11         0E       56       13         0F       68       13         10       48       9         11       56       9         12       64       13         13       72       13         14       80       17         15       88       17         16       104       21         17       128       21         18       80       9         19       96       9         1A       112       17         1B       128       17                                                                                                                                                                                                                                                                                           |              | 32          | 7                 |

| 0C     44     11       0D     48     11       0E     56     13       0F     68     13       10     48     9       11     56     9       12     64     13       13     72     13       14     80     17       15     88     17       16     104     21       17     128     21       18     80     9       19     96     9       1A     112     17       1B     128     17                                                                                                                                                                                                                                                                                                                                                                                                                     | 0A           | 36          | 9                 |

| 0D       48       11         0E       56       13         0F       68       13         10       48       9         11       56       9         12       64       13         13       72       13         14       80       17         15       88       17         16       104       21         17       128       21         18       80       9         19       96       9         1A       112       17         1B       128       17                                                                                                                                                                                                                                                                                                                                                    | 0B           | 40          | 9                 |

| 0E     56     13       0F     68     13       10     48     9       11     56     9       12     64     13       13     72     13       14     80     17       15     88     17       16     104     21       17     128     21       18     80     9       19     96     9       1A     112     17       1B     128     17                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0C           | 44          | 11                |

| 0F     68     13       10     48     9       11     56     9       12     64     13       13     72     13       14     80     17       15     88     17       16     104     21       17     128     21       18     80     9       19     96     9       1A     112     17       1B     128     17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0D           | 48          | 11                |

| 10     48     9       11     56     9       12     64     13       13     72     13       14     80     17       15     88     17       16     104     21       17     128     21       18     80     9       19     96     9       1A     112     17       1B     128     17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0E           | 56          | 13                |

| 11     56     9       12     64     13       13     72     13       14     80     17       15     88     17       16     104     21       17     128     21       18     80     9       19     96     9       1A     112     17       1B     128     17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0F           | 68          | 13                |

| 12     64     13       13     72     13       14     80     17       15     88     17       16     104     21       17     128     21       18     80     9       19     96     9       1A     112     17       1B     128     17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10           | 48          | 9                 |

| 13     72     13       14     80     17       15     88     17       16     104     21       17     128     21       18     80     9       19     96     9       1A     112     17       1B     128     17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11           | 56          | 9                 |

| 14     80     17       15     88     17       16     104     21       17     128     21       18     80     9       19     96     9       1A     112     17       1B     128     17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12           | 64          | 13                |

| 15     88     17       16     104     21       17     128     21       18     80     9       19     96     9       1A     112     17       1B     128     17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 13           | 72          | 13                |

| 16     104     21       17     128     21       18     80     9       19     96     9       1A     112     17       1B     128     17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14           | 80          | 17                |

| 17     128     21       18     80     9       19     96     9       1A     112     17       1B     128     17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15           | 88          | 17                |

| 18     80     9       19     96     9       1A     112     17       1B     128     17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16           | 104         | 21                |

| 19     96     9       1A     112     17       1B     128     17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17           | 128         | 21                |

| 1A 112 17<br>1B 128 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 18           | 80          | 9                 |

| 1B 128 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19           | 96          | 9                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1A           | 112         | 17                |

| 1C 144 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1B           | 128         | 17                |

| , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1C           | 144         | 25                |

| 1D 160 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              | 160         | 25                |

| 1E 192 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1E           | 192         | 33                |

| 1F 240 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |             |                   |

| ICR<br>(hex) | SCL Divider | SDA Hold<br>Value |

|--------------|-------------|-------------------|

| 20           | 160         | 17                |

| 21           | 192         | 17                |

| 22           | 224         | 33                |

| 23           | 256         | 33                |

| 24           | 288         | 49                |

| 25           | 320         | 49                |

| 26           | 384         | 65                |

| 27           | 480         | 65                |

| 28           | 320         | 33                |

| 29           | 384         | 33                |

| 2A           | 448         | 65                |

| 2B           | 512         | 65                |

| 2C           | 576         | 97                |

| 2D           | 640         | 97                |

| 2E           | 768         | 129               |

| 2F           | 960         | 129               |

| 30           | 640         | 65                |

| 31           | 768         | 65                |

| 32           | 896         | 129               |

| 33           | 1024        | 129               |

| 34           | 1152        | 193               |

| 35           | 1280        | 193               |

| 36           | 1536        | 257               |

| 37           | 1920        | 257               |

| 38           | 1280        | 129               |

| 39           | 1536        | 129               |

| 3A           | 1792        | 257               |

| 3B           | 2048        | 257               |

| 3C           | 2304        | 385               |

| 3D           | 2560        | 385               |

| 3E           | 3072        | 513               |

| 3F           | 3840        | 513               |

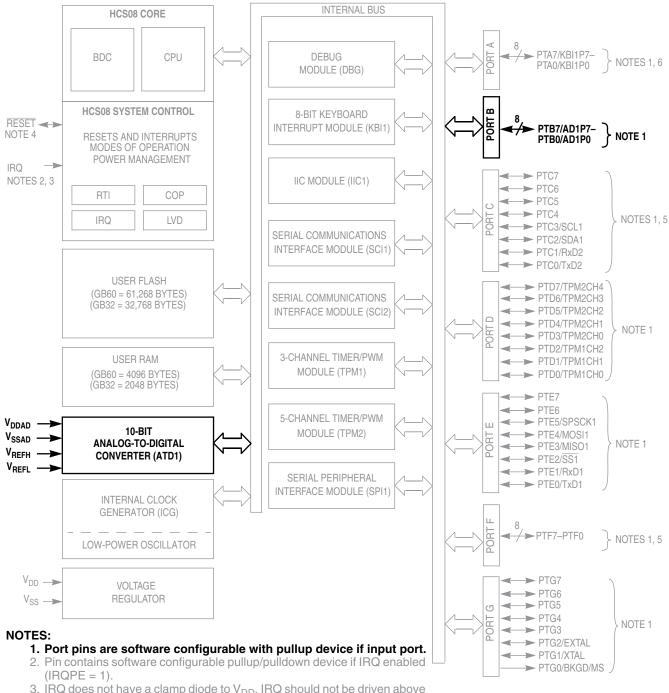

#### Chapter 14 Analog-to-Digital Converter (ATD) Module

- 3. IRQ does not have a clamp diode to  $\ensuremath{V_{DD}}.$  IRQ should not be driven above

- $V_{DD}$ .

- 4. Pin contains integrated pullup device.

- 5. High current drive

- 6. Pins PTA[7:4] contain both pullup and pulldown devices. Pulldown available when KBI enabled (KBIPn = 1).

Figure 14-1. MC9S08GBxx Block Diagram Highlighting ATD Block and Pins

| <b>Table</b> | 14-1. | Signal | Properties | ; |

|--------------|-------|--------|------------|---|

|--------------|-------|--------|------------|---|

| Name              | Function                                 |

|-------------------|------------------------------------------|

| AD7–AD0           | Channel input pins                       |

| V <sub>REFH</sub> | High reference voltage for ATD converter |

| V <sub>REFL</sub> | Low reference voltage for ATD converter  |

| V <sub>DDAD</sub> | ATD power supply voltage                 |

| V <sub>SSAD</sub> | ATD ground supply voltage                |

#### Channel Input Pins — AD1P7–AD1P0 14.2.1.1

The channel pins are used as the analog input pins of the ATD. Each pin is connected to an analog switch which serves as the signal gate into the sample submodule.

## 14.2.1.2 ATD Reference Pins — V<sub>RFFH</sub>, V<sub>RFFI</sub>

These pins serve as the source for the high and low reference potentials for the converter. Separation from the power supply pins accommodates the filtering necessary to achieve the accuracy of which the system is capable.

#### ATD Supply Pins — V<sub>DDAD</sub>, V<sub>SSAD</sub> 14.2.1.3

These two pins are used to supply power and ground to the analog section of the ATD. Dedicated power is required to isolate the sensitive analog circuitry from the normal levels of noise present on digital power supplies.

#### NOTE

$V_{DDAD1}$  and  $V_{DD}$  must be at the same potential. Likewise,  $V_{SSAD1}$  and  $V_{SS}$ must be at the same potential.

#### 14.3 **Functional Description**

The ATD uses a successive approximation register (SAR) architecture. The ATD contains all the necessary elements to perform a single analog-to-digital conversion.

A write to the ATD1SC register initiates a new conversion. A write to the ATD1C register will interrupt the current conversion but it will not initiate a new conversion. A write to the ATD1PE register will also abort the current conversion but will not initiate a new conversion. If a conversion is already running when a write to the ATD1SC register is made, it will be aborted and a new one will be started.

#### 14.3.1 **Mode Control**

The ATD has a mode control unit to communicate with the sample and hold (S/H) machine and the SAR machine when necessary to collect samples and perform conversions. The mode control unit signals the S/H machine to begin collecting a sample and for the SAR machine to begin receiving a sample. At the end of the sample period, the S/H machine signals the SAR machine to begin the analog-to-digital conversion process. The conversion process is terminated when the SAR machine signals the end of

## 15.4 On-Chip Debug System (DBG)

Because HCS08 devices do not have external address and data buses, the most important functions of an in-circuit emulator have been built onto the chip with the MCU. The debug system consists of an 8-stage FIFO that can store address or data bus information, and a flexible trigger system to decide when to capture bus information and what information to capture. The system relies on the single-wire background debug system to access debug control registers and to read results out of the eight stage FIFO.

The debug module includes control and status registers that are accessible in the user's memory map. These registers are located in the high register space to avoid using valuable direct page memory space.

Most of the debug module's functions are used during development, and user programs rarely access any of the control and status registers for the debug module. The one exception is that the debug system can provide the means to implement a form of ROM patching. This topic is discussed in greater detail in Section 15.4.6, "Hardware Breakpoints."

## 15.4.1 Comparators A and B

Two 16-bit comparators (A and B) can optionally be qualified with the R/W signal and an opcode tracking circuit. Separate control bits allow you to ignore R/W for each comparator. The opcode tracking circuitry optionally allows you to specify that a trigger will occur only if the opcode at the specified address is actually executed as opposed to only being read from memory into the instruction queue. The comparators are also capable of magnitude comparisons to support the inside range and outside range trigger modes. Comparators are disabled temporarily during all BDC accesses.

The A comparator is always associated with the 16-bit CPU address. The B comparator compares to the CPU address or the 8-bit CPU data bus, depending on the trigger mode selected. Because the CPU data bus is separated into a read data bus and a write data bus, the RWAEN and RWA control bits have an additional purpose, in full address plus data comparisons they are used to decide which of these buses to use in the comparator B data bus comparisons. If RWAEN = 1 (enabled) and RWA = 0 (write), the CPU's write data bus is used. Otherwise, the CPU's read data bus is used.

The currently selected trigger mode determines what the debugger logic does when a comparator detects a qualified match condition. A match can cause:

- Generation of a breakpoint to the CPU

- Storage of data bus values into the FIFO

- Starting to store change-of-flow addresses into the FIFO (begin type trace)

- Stopping the storage of change-of-flow addresses into the FIFO (end type trace)

## 15.4.2 Bus Capture Information and FIFO Operation

The usual way to use the FIFO is to setup the trigger mode and other control options, then arm the debugger. When the FIFO has filled or the debugger has stopped storing data into the FIFO, you would read the information out of it in the order it was stored into the FIFO. Status bits indicate the number of words of valid information that are in the FIFO as data is stored into it. If a trace run is manually halted by writing 0 to ARM before the FIFO is full (CNT = 1:0:0:0), the information is shifted by one position and

Freescale Semiconductor 245

MC9S08GB/GT Data Sheet, Rev. 2.3

#### **Development Support**

the host must perform ((8 - CNT) - 1) dummy reads of the FIFO to advance it to the first significant entry in the FIFO.

In most trigger modes, the information stored in the FIFO consists of 16-bit change-of-flow addresses. In these cases, read DBGFH then DBGFL to get one coherent word of information out of the FIFO. Reading DBGFL (the low-order byte of the FIFO data port) causes the FIFO to shift so the next word of information is available at the FIFO data port. In the event-only trigger modes (see Section 15.4.5, "Trigger Modes"), 8-bit data information is stored into the FIFO. In these cases, the high-order half of the FIFO (DBGFH) is not used and data is read out of the FIFO by simply reading DBGFL. Each time DBGFL is read, the FIFO is shifted so the next data value is available through the FIFO data port at DBGFL.

In trigger modes where the FIFO is storing change-of-flow addresses, there is a delay between CPU addresses and the input side of the FIFO. Because of this delay, if the trigger event itself is a change-of-flow address or a change-of-flow address appears during the next two bus cycles after a trigger event starts the FIFO, it will not be saved into the FIFO. In the case of an end-trace, if the trigger event is a change-of-flow, it will be saved as the last change-of-flow entry for that debug run.

The FIFO can also be used to generate a profile of executed instruction addresses when the debugger is not armed. When ARM = 0, reading DBGFL causes the address of the most-recently fetched opcode to be saved in the FIFO. To use the profiling feature, a host debugger would read addresses out of the FIFO by reading DBGFH then DBGFL at regular periodic intervals. The first eight values would be discarded because they correspond to the eight DBGFL reads needed to initially fill the FIFO. Additional periodic reads of DBGFH and DBGFL return delayed information about executed instructions so the host debugger can develop a profile of executed instruction addresses.

## 15.4.3 Change-of-Flow Information

To minimize the amount of information stored in the FIFO, only information related to instructions that cause a change to the normal sequential execution of instructions is stored. With knowledge of the source and object code program stored in the target system, an external debugger system can reconstruct the path of execution through many instructions from the change-of-flow information stored in the FIFO.

For conditional branch instructions where the branch is taken (branch condition was true), the source address is stored (the address of the conditional branch opcode). Because BRA and BRN instructions are not conditional, these events do not cause change-of-flow information to be stored in the FIFO.

Indirect JMP and JSR instructions use the current contents of the H:X index register pair to determine the destination address, so the debug system stores the run-time destination address for any indirect JMP or JSR. For interrupts, RTI, or RTS, the destination address is stored in the FIFO as change-of-flow information.

## 15.4.4 Tag vs. Force Breakpoints and Triggers

Tagging is a term that refers to identifying an instruction opcode as it is fetched into the instruction queue, but not taking any other action until and unless that instruction is actually executed by the CPU. This distinction is important because any change-of-flow from a jump, branch, subroutine call, or interrupt causes some instructions that have been fetched into the instruction queue to be thrown away without being executed.

MC9S08GB/GT Data Sheet, Rev. 2.3

#### CLKSW — Select Source for BDC Communications Clock

CLKSW defaults to 0, which selects the alternate BDC clock source.

- 1 = MCU bus clock.

- 0 = Alternate BDC clock source.

#### WS — Wait or Stop Status

When the target CPU is in wait or stop mode, most BDC commands cannot function. However, the BACKGROUND command can be used to force the target CPU out of wait or stop and into active background mode where all BDC commands work. Whenever the host forces the target MCU into active background mode, the host should issue a READ\_STATUS command to check that BDMACT = 1 before attempting other BDC commands.

- 1 = Target CPU is in wait or stop mode, or a BACKGROUND command was used to change from wait or stop to active background mode.

- 0 = Target CPU is running user application code or in active background mode (was not in wait or stop mode when background became active).

#### WSF — Wait or Stop Failure Status

This status bit is set if a memory access command failed due to the target CPU executing a wait or stop instruction at or about the same time. The usual recovery strategy is to issue a BACKGROUND command to get out of wait or stop mode into active background mode, repeat the command that failed, then return to the user program. (Typically, the host would restore CPU registers and stack values and re-execute the wait or stop instruction.)

- 1 = Memory access command failed because the CPU entered wait or stop mode.

- 0 = Memory access did not conflict with a wait or stop instruction.

#### DVF — Data Valid Failure Status

This status bit is not used in the MC9S08GB/GT because it does not have any slow access memory.

- 1 = Memory access command failed because CPU was not finished with a slow memory access.

- 0 = Memory access did not conflict with a slow memory access.

## 15.5.1.2 BDC Breakpoint Match Register (BDCBKPT)

This 16-bit register holds the address for the hardware breakpoint in the BDC. The BKPTEN and FTS control bits in BDCSCR are used to enable and configure the breakpoint logic. Dedicated serial BDC commands (READ\_BKPT and WRITE\_BKPT) are used to read and write the BDCBKPT register but is not accessible to user programs because it is not located in the normal memory map of the MCU. Breakpoints are normally set while the target MCU is in active background mode before running the user application program. For additional information about setup and use of the hardware breakpoint logic in the BDC, refer to Section 15.3.4, "BDC Hardware Breakpoint."

## 15.5.2 System Background Debug Force Reset Register (SBDFR)

This register contains a single write-only control bit. A serial active background mode command such as WRITE\_BYTE must be used to write to SBDFR. Attempts to write this register from a user program are ignored. Reads always return \$00.

MC9S08GB/GT Data Sheet, Rev. 2.3

# A.4 Electrostatic Discharge (ESD) Protection Characteristics

Although damage from static discharge is much less common on these devices than on early CMOS circuits, normal handling precautions should be used to avoid exposure to static discharge. Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage. All ESD testing is in conformity with CDF-AEC-Q00 Stress Test Qualification for Automotive Grade Integrated Circuits. (http://www.aecouncil.com/) This device was qualified to AEC-Q100 Rev E. A device is considered to have failed if, after exposure to ESD pulses, the device no longer meets the device specification requirements. Complete dc parametric and functional testing is performed per the applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

Parameter

Symbol

Value

Unit

ESD Target for Machine Model (MM) MM circuit description

V<sub>THMM</sub>

200

V

ESD Target for Human Body Model (HBM) HBM circuit description

V<sub>THHBM</sub>

2000

V

**Table A-3. ESD Protection Characteristics**

### A.5 DC Characteristics

This section includes information about power supply requirements, I/O pin characteristics, and power supply current in various operating modes.

Table A-4. DC Characteristics (Sheet 1 of 2) (Temperature Range = -40 to 85°C Ambient)

| Parameter                                                                                               | Symbol            | Min              | Typical <sup>1</sup> | Max          | Unit |

|---------------------------------------------------------------------------------------------------------|-------------------|------------------|----------------------|--------------|------|

| Supply voltage (run, wait and stop modes.) $0 < f_{Bus} < 8 \text{ MHz}$ $0 < f_{Bus} < 20 \text{ MHz}$ | V <sub>DD</sub>   | 1.8<br>2.08      |                      | 3.6<br>3.6   | V    |

| Minimum RAM retention supply voltage applied to $V_{\text{DD}}$                                         | V <sub>RAM</sub>  | 1.0 <sup>2</sup> |                      | _            | V    |

|                                                                                                         | V <sub>LVDH</sub> | 2.08<br>2.16     | 2.1<br>2.19          | 2.2<br>2.27  | V    |

|                                                                                                         | V <sub>LVDL</sub> | 1.80<br>1.88     | 1.82<br>1.90         | 1.91<br>1.99 | V    |

| Low-voltage warning threshold — high range (V <sub>DD</sub> falling) (V <sub>DD</sub> rising)           | V <sub>LVWH</sub> | 2.35<br>2.35     | 2.40<br>2.40         | 2.5          | V    |

| Low-voltage warning threshold — low range (V <sub>DD</sub> falling) (V <sub>DD</sub> rising)            | V <sub>LVWL</sub> | 2.08<br>2.16     | 2.1<br>2.19          | 2.2<br>2.27  | V    |

#### **Appendix A Electrical Characteristics**

1. Not defined but normally MSB of character just received

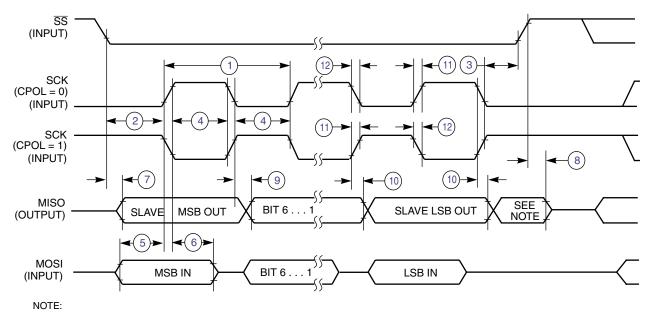

Figure A-18. SPI Slave Timing (CPHA = 0)

NOTE:

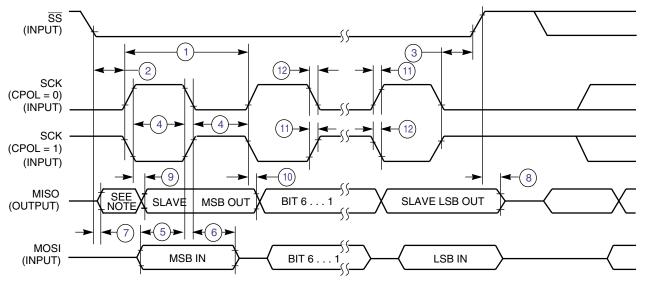

1. Not defined but normally LSB of character just received

Figure A-19. SPI Slave Timing (CPHA = 1)