Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | S08                                                        |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 40MHz                                                      |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                 |

| Peripherals                | LVD, POR, PWM, WDT                                         |

| Number of I/O              | 39                                                         |

| Program Memory Size        | 60KB (60K x 8)                                             |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 4K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                |

| Data Converters            | A/D 8x10b                                                  |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                          |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 48-VFQFN Exposed Pad                                       |

| Supplier Device Package    | 48-QFN (7x7)                                               |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08gt60cfd |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Section Number**

# Title

### Page

# Chapter 8 Central Processor Unit (CPU)

| 8.1 | Introduct | tion       |                                                  |     |

|-----|-----------|------------|--------------------------------------------------|-----|

| 8.2 | Features  |            |                                                  | 126 |

| 8.3 | Program   | mer's Moo  | del and CPU Registers                            |     |

|     | 8.3.1     | Accumul    | ator (A)                                         | 127 |

|     | 8.3.2     | Index Re   | gister (H:X)                                     | 127 |

|     | 8.3.3     | Stack Po   | inter (SP)                                       |     |

|     | 8.3.4     | Program    | Counter (PC)                                     |     |

|     | 8.3.5     | Condition  | n Code Register (CCR)                            |     |

| 8.4 | Addressi  | ng Modes   |                                                  | 130 |

|     | 8.4.1     | Inherent   | Addressing Mode (INH)                            | 130 |

|     | 8.4.2     | Relative   | Addressing Mode (REL)                            | 130 |

|     | 8.4.3     | Immedia    | te Addressing Mode (IMM)                         | 130 |

|     | 8.4.4     | Direct A   | ddressing Mode (DIR)                             | 130 |

|     | 8.4.5     | Extended   | Addressing Mode (EXT)                            | 131 |

|     | 8.4.6     | Indexed A  | Addressing Mode                                  | 131 |

|     |           | 8.4.6.1    | Indexed, No Offset (IX)                          | 131 |

|     |           | 8.4.6.2    | Indexed, No Offset with Post Increment (IX+)     | 131 |

|     |           | 8.4.6.3    | Indexed, 8-Bit Offset (IX1)                      | 131 |

|     |           | 8.4.6.4    | Indexed, 8-Bit Offset with Post Increment (IX1+) | 131 |

|     |           | 8.4.6.5    | Indexed, 16-Bit Offset (IX2)                     | 131 |

|     |           | 8.4.6.6    | SP-Relative, 8-Bit Offset (SP1)                  | 131 |

|     |           | 8.4.6.7    | SP-Relative, 16-Bit Offset (SP2)                 | 132 |

| 8.5 | Special C | Operations |                                                  |     |

|     | 8.5.1     | Reset See  | quence                                           | 132 |

|     | 8.5.2     | Interrupt  | Sequence                                         | 132 |

|     | 8.5.3     | Wait Mo    | de Operation                                     |     |

|     | 8.5.4     | Stop Mo    | de Operation                                     |     |

|     | 8.5.5     | BGND II    | nstruction                                       | 134 |

| 8.6 | HCS08 I   | nstruction | Set Summary                                      |     |

# Chapter 9 Keyboard Interrupt (KBI) Module

| 9.1 | Introduc | tion                                     | 145 |

|-----|----------|------------------------------------------|-----|

|     | 9.1.1    | Port A and Keyboard Interrupt Pins       | 145 |

| 9.2 | Features |                                          | 145 |

| 9.3 | KBI Blo  | ck Diagram                               | 147 |

| 9.4 | Keyboar  | d Interrupt (KBI) Module                 | 147 |

|     | -        | Pin Enables                              |     |

|     | 9.4.2    | Edge and Level Sensitivity               | 147 |

|     | 9.4.3    | KBI Interrupt Controls                   |     |

| 9.5 |          | gisters and Control Bits                 |     |

|     | 9.5.1    | KBI Status and Control Register (KBI1SC) |     |

|     | 9.5.2    | KBI Pin Enable Register (KBI1PE)         |     |

|     |          |                                          |     |

### **Section Number**

# Page

|      |           | 14.2.1.2 ATD Reference Pins — V <sub>REFH</sub> , V <sub>REFL</sub> | 223 |

|------|-----------|---------------------------------------------------------------------|-----|

|      |           | 14.2.1.3 ATD Supply Pins — V <sub>DDAD</sub> , V <sub>SSAD</sub>    | 223 |

| 14.3 | Function  | al Description                                                      | 223 |

|      | 14.3.1    | Mode Control                                                        | 223 |

|      | 14.3.2    | Sample and Hold                                                     | 224 |

|      | 14.3.3    | Analog Input Multiplexer                                            | 226 |

|      |           | ATD Module Accuracy Definitions                                     |     |

| 14.4 |           | -<br>                                                               |     |

| 14.5 | Interrupt | S                                                                   | 229 |

|      |           | gisters and Control Bits                                            |     |

|      | 14.6.1    | ATD Control (ATDC)                                                  | 230 |

|      | 14.6.2    | ATD Status and Control (ATD1SC)                                     | 232 |

|      |           | ATD Result Data (ATD1RH, ATD1RL)                                    |     |

|      |           | ATD Pin Enable (ATD1PE)                                             |     |

# Chapter 15 Development Support

| 15.1 | Introduct | tion                                                 | 235 |

|------|-----------|------------------------------------------------------|-----|

| 15.2 | Features  |                                                      | 236 |

| 15.3 | Backgrou  | und Debug Controller (BDC)                           | 237 |

|      | 15.3.1    | BKGD Pin Description                                 | 237 |

|      | 15.3.2    | Communication Details                                | 238 |

|      | 15.3.3    | BDC Commands                                         | 242 |

|      | 15.3.4    | BDC Hardware Breakpoint                              | 244 |

| 15.4 | On-Chip   | Debug System (DBG)                                   | 245 |

|      | 15.4.1    | Comparators A and B                                  | 245 |

|      | 15.4.2    | Bus Capture Information and FIFO Operation           | 245 |

|      | 15.4.3    | Change-of-Flow Information                           | 246 |

|      | 15.4.4    | Tag vs. Force Breakpoints and Triggers               | 246 |

|      | 15.4.5    | Trigger Modes                                        | 247 |

|      | 15.4.6    | Hardware Breakpoints                                 | 249 |

| 15.5 | Registers | s and Control Bits                                   | 249 |

|      | 15.5.1    | BDC Registers and Control Bits                       | 249 |

|      |           | 15.5.1.1 BDC Status and Control Register (BDCSCR)    | 250 |

|      |           | 15.5.1.2 BDC Breakpoint Match Register (BDCBKPT)     | 251 |

|      | 15.5.2    | System Background Debug Force Reset Register (SBDFR) | 251 |

|      | 15.5.3    | DBG Registers and Control Bits                       | 252 |

|      |           | 15.5.3.1 Debug Comparator A High Register (DBGCAH)   | 252 |

|      |           | 15.5.3.2 Debug Comparator A Low Register (DBGCAL)    | 252 |

|      |           | 15.5.3.3 Debug Comparator B High Register (DBGCBH)   | 252 |

|      |           | 15.5.3.4 Debug Comparator B Low Register (DBGCBL)    | 252 |

|      |           |                                                      |     |

| Address                            | Register Name | Bit 7  | 6      | 5      | 4      | 3       | 2       | 1       | Bit 0  |  |  |  |

|------------------------------------|---------------|--------|--------|--------|--------|---------|---------|---------|--------|--|--|--|

| \$00 <b>28</b>                     | SPI1C1        | SPIE   | SPE    | SPTIE  | MSTR   | CPOL    | CPHA    | SSOE    | LSBFE  |  |  |  |

| \$00 <b>29</b>                     | SPI1C2        | 0      | 0      | 0      | MODFEN | BIDIROE | 0       | SPISWAI | SPC0   |  |  |  |

| \$00 <b>2A</b>                     | SPI1BR        | 0      | SPPR2  | SPPR1  | SPPR0  | 0       | SPR2    | SPR1    | SPR0   |  |  |  |

| \$00 <b>2B</b>                     | SPI1S         | SPRF   | 0      | SPTEF  | MODF   | 0       | 0       | 0       | 0      |  |  |  |

| \$00 <b>2C</b>                     | Reserved      | 0      | 0      | 0      | 0      | 0       | 0       | 0       | 0      |  |  |  |

| \$00 <b>2D</b>                     | SPI1D         | Bit 7  | 6      | 5      | 4      | 3       | 2       | 1       | Bit 0  |  |  |  |

| \$00 <b>2E</b>                     | Reserved      | 0      | 0      | 0      | 0      | 0       | 0       | 0       | 0      |  |  |  |

| \$00 <b>2F</b>                     | Reserved      | 0      | 0      | 0      | 0      | 0       | 0       | 0       | 0      |  |  |  |

| \$00 <b>30</b>                     | TPM1SC        | TOF    | TOIE   | CPWMS  | CLKSB  | CLKSA   | PS2     | PS1     | PS0    |  |  |  |

| \$00 <b>31</b>                     | TPM1CNTH      | Bit 15 | 14     | 13     | 12     | 11      | 10      | 9       | Bit 8  |  |  |  |

| \$00 <b>32</b>                     | TPM1CNTL      | Bit 7  | 6      | 5      | 4      | 3       | 2       | 1       | Bit 0  |  |  |  |

| \$00 <b>33</b>                     | TPM1MODH      | Bit 15 | 14     | 13     | 12     | 11      | 10      | 9       | Bit 8  |  |  |  |

| \$00 <b>34</b>                     | TPM1MODL      | Bit 7  | 6      | 5      | 4      | 3       | 2       | 1       | Bit 0  |  |  |  |

| \$00 <b>35</b>                     | TPM1C0SC      | CH0F   | CH0IE  | MS0B   | MS0A   | ELS0B   | ELS0A   | 0       | 0      |  |  |  |

| \$00 <b>36</b>                     | TPM1C0VH      | Bit 15 | 14     | 13     | 12     | 11      | 10      | 9       | Bit 8  |  |  |  |

| \$00 <b>37</b>                     | TPM1C0VL      | Bit 7  | 6      | 5      | 4      | 3       | 2       | 1       | Bit 0  |  |  |  |

| \$00 <b>38</b>                     | TPM1C1SC      | CH1F   | CH1IE  | MS1B   | MS1A   | ELS1B   | ELS1A   | 0       | 0      |  |  |  |

| \$00 <b>39</b>                     | TPM1C1VH      | Bit 15 | 14     | 13     | 12     | 11      | 10      | 9       | Bit 8  |  |  |  |

| \$00 <b>3A</b>                     | TPM1C1VL      | Bit 7  | 6      | 5      | 4      | 3       | 2       | 1       | Bit 0  |  |  |  |

| \$00 <b>3B</b>                     | TPM1C2SC      | CH2F   | CH2IE  | MS2B   | MS2A   | ELS2B   | ELS2A   | 0       | 0      |  |  |  |

| \$00 <b>3C</b>                     | TPM1C2VH      | Bit 15 | 14     | 13     | 12     | 11      | 10      | 9       | Bit 8  |  |  |  |

| \$00 <b>3D</b>                     | TPM1C2VL      | Bit 7  | 6      | 5      | 4      | 3       | 2       | 1       | Bit 0  |  |  |  |

| \$00 <b>3E</b> –<br>\$00 <b>3F</b> | Reserved      | _      |        | _      | _      | _       | _       | _       | _      |  |  |  |

| \$00 <b>40</b>                     | PTFD          | PTFD7  | PTFD6  | PTFD5  | PTFD4  | PTFD3   | PTFD2   | PTFD1   | PTFD0  |  |  |  |

| \$00 <b>41</b>                     | PTFPE         | PTFPE7 | PTFPE6 | PTFPE5 | PTFPE4 | PTFPE3  | PTFPE2  | PTFPE1  | PTFPE0 |  |  |  |

| \$00 <b>42</b>                     | PTFSE         | PTFSE7 | PTFSE6 | PTFSE5 | PTFSE4 | PTFSE3  | PTFSE2  | PTFSE1  | PTFSE0 |  |  |  |

| \$00 <b>43</b>                     | PTFDD         | PTFDD7 | PTFDD6 | PTFDD5 | PTFDD4 | PTFDD3  | PTFDD2  | PTFDD1  | PTFDD0 |  |  |  |

| \$0044                             | PTGD          | PTGD7  | PTGD6  | PTGD5  | PTGD4  | PTGD3   | PTGD2   | PTGD1   | PTGD0  |  |  |  |

| \$00 <b>45</b>                     | PTGPE         | PTGPE7 | PTGPE6 | PTGPE5 | PTGPE4 | PTGPE3  | PTGPE2  | PTGPE1  | PTGPE0 |  |  |  |

| \$00 <b>46</b>                     | PTGSE         | PTGSE7 | PTGSE6 | PTGSE5 | PTGSE4 | PTGSE3  | PTGSE2  | PTGSE1  | PTGSE0 |  |  |  |

| \$00 <b>47</b>                     | PTGDD         | PTGDD7 | PTGDD6 | PTGDD5 | PTGDD4 | PTGDD3  | PTGDD2  | PTGDD1  | PTGDD0 |  |  |  |

| \$00 <b>48</b>                     | ICGC1         | 0      | RANGE  | REFS   | CL     | KS      | OSCSTEN | 0*      | 0      |  |  |  |

| \$00 <b>49</b>                     | ICGC2         | LOLRE  |        | MFD    |        | LOCRE   |         | RFD     |        |  |  |  |

| \$00 <b>4A</b>                     | ICGS1         | CL     | KST    | REFST  | LOLS   | LOCK    | LOCS    | ERCS    | ICGIF  |  |  |  |

| \$00 <b>4B</b>                     | ICGS2         | 0      | 0      | 0      | 0      | 0       | 0       | 0       | DCOS   |  |  |  |

| \$00 <b>4C</b>                     | ICGFLTU       | 0      | 0      | 0      | 0      |         | FL      | T       |        |  |  |  |

| \$00 <b>4D</b>                     | ICGFLTL       |        |        |        | FI     | L<br>LT |         |         |        |  |  |  |

| \$00 <b>4E</b>                     | ICGTRM        |        |        |        | TF     | RIM     |         |         |        |  |  |  |

|                                    |               | TRIM   |        |        |        |         |         |         |        |  |  |  |

\* This bit is reserved for Freescale Semiconductor internal use only. Always write a 0 to this bit.

Chapter 4 Memory

Table 4-2. Direct-Page Register Summary (Sheet 3 of 3)

| Address                            | Register Name | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1                                                                                                                                                                                                                                                                                                                                                                                      | Bit 0  |  |  |  |  |  |  |

|------------------------------------|---------------|--------|--------|--------|--------|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|--|--|--|--|--|

| \$00 <b>4F</b>                     | Reserved      | 0      | 0      | 0      | 0      | 0      | 0      | 0                                                                                                                                                                                                                                                                                                                                                                                      | 0      |  |  |  |  |  |  |

|                                    |               |        |        |        |        |        |        |                                                                                                                                                                                                                                                                                                                                                                                        |        |  |  |  |  |  |  |

| \$00 <b>50</b>                     | ATD1C         | ATDPU  | DJM    | RES8   | SGN    |        | PF     | RS                                                                                                                                                                                                                                                                                                                                                                                     |        |  |  |  |  |  |  |

| \$00 <b>51</b>                     | ATD1SC        | CCF    | ATDIE  | ATDCO  |        |        | ATDCH  |                                                                                                                                                                                                                                                                                                                                                                                        |        |  |  |  |  |  |  |

| \$00 <b>52</b>                     | ATD1RH        | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1                                                                                                                                                                                                                                                                                                                                                                                      | Bit 0  |  |  |  |  |  |  |

| \$00 <b>53</b>                     | ATD1RL        | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1                                                                                                                                                                                                                                                                                                                                                                                      | Bit 0  |  |  |  |  |  |  |

| \$00 <b>54</b>                     | ATD1PE        | ATDPE7 | ATDPE6 | ATDPE5 | ATDPE4 | ATDPE3 | ATDPE2 | ATDPE1                                                                                                                                                                                                                                                                                                                                                                                 | ATDPE0 |  |  |  |  |  |  |

| \$00 <b>55</b> –<br>\$00 <b>57</b> | Reserved      | _      | _      |        |        | _      |        |                                                                                                                                                                                                                                                                                                                                                                                        | _      |  |  |  |  |  |  |

| \$00 <b>58</b>                     | IIC1A         |        |        |        | ADDR   |        |        |                                                                                                                                                                                                                                                                                                                                                                                        | 0      |  |  |  |  |  |  |

| \$00 <b>59</b>                     | IIC1F         | MU     | ILT    |        |        | IC     | R      | 0   0     PRS     ATDCH     2   1     2   1     2   1     2   1     2   1     2   1     2   ATDPE1     ATDPE2   ATDPE1     ATDPE2   ATDPE1     ATDPE2   ATDPE1             RSTA   0     SRW   IICIF     R          PS2   PS1     PS2   PS1     PS2   PS1     10   9     2   1     ELS0A   0     10   9     2   1     ELS1A   0     10   9     2   1     2   1     ELS2A   0     10   9 |        |  |  |  |  |  |  |

| \$00 <b>5A</b>                     | IIC1C         | IICEN  | IICIE  | MST    | ΤX     | TXAK   | RSTA   | 0                                                                                                                                                                                                                                                                                                                                                                                      | 0      |  |  |  |  |  |  |

| \$00 <b>5B</b>                     | IIC1S         | TCF    | IAAS   | BUSY   | ARBL   | 0      | SRW    | IICIF                                                                                                                                                                                                                                                                                                                                                                                  | RXAK   |  |  |  |  |  |  |

| \$00 <b>5C</b>                     | IIC1D         |        |        |        | DA     | TA     |        | PRS   ATDCH   2 1 Bit 0   2 1 Bit 0   2 1 Bit 0   2 1 ATDPE0                                 PS2 PS1 PS0   10 9 Bit 8   2 1 Bit 0   10 9 Bit 8   2 1 Bit 0   ELS0A 0 0   10 9 Bit 8   2 1 Bit 0   ELS1A 0 0   10 9 Bit 8   2 1 Bit 0   ELS2A 0 0   10 9 Bit 8   2 1 Bit 0   ELS2A 0 0   10 9 Bit 8                                                                                     |        |  |  |  |  |  |  |

| \$00 <b>5D</b> –<br>\$00 <b>5F</b> | Reserved      | _      | _      | _      | _      | _      | _      | _                                                                                                                                                                                                                                                                                                                                                                                      | _      |  |  |  |  |  |  |

| \$00 <b>60</b>                     | TPM2SC        | TOF    | TOIE   | CPWMS  | CLKSB  | CLKSA  | PS2    | PS1                                                                                                                                                                                                                                                                                                                                                                                    | PS0    |  |  |  |  |  |  |

| \$00 <b>61</b>                     | TPM2CNTH      | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9                                                                                                                                                                                                                                                                                                                                                                                      | Bit 8  |  |  |  |  |  |  |

| \$00 <b>62</b>                     | TPM2CNTL      | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1                                                                                                                                                                                                                                                                                                                                                                                      | Bit 0  |  |  |  |  |  |  |

| \$00 <b>63</b>                     | TPM2MODH      | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9                                                                                                                                                                                                                                                                                                                                                                                      | Bit 8  |  |  |  |  |  |  |

| \$00 <b>64</b>                     | TPM2MODL      | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1                                                                                                                                                                                                                                                                                                                                                                                      | Bit 0  |  |  |  |  |  |  |

| \$00 <b>65</b>                     | TPM2C0SC      | CH0F   | CH0IE  | MS0B   | MS0A   | ELS0B  | ELS0A  | 0                                                                                                                                                                                                                                                                                                                                                                                      | 0      |  |  |  |  |  |  |

| \$00 <b>66</b>                     | TPM2C0VH      | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9                                                                                                                                                                                                                                                                                                                                                                                      | Bit 8  |  |  |  |  |  |  |

| \$00 <b>67</b>                     | TPM2C0VL      | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1                                                                                                                                                                                                                                                                                                                                                                                      | Bit 0  |  |  |  |  |  |  |

| \$00 <b>68</b>                     | TPM2C1SC      | CH1F   | CH1IE  | MS1B   | MS1A   | ELS1B  | ELS1A  | 0                                                                                                                                                                                                                                                                                                                                                                                      | 0      |  |  |  |  |  |  |

| \$00 <b>69</b>                     | TPM2C1VH      | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9                                                                                                                                                                                                                                                                                                                                                                                      | Bit 8  |  |  |  |  |  |  |

| \$00 <b>6A</b>                     | TPM2C1VL      | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1                                                                                                                                                                                                                                                                                                                                                                                      | Bit 0  |  |  |  |  |  |  |

| \$00 <b>6B</b>                     | TPM2C2SC      | CH2F   | CH2IE  | MS2B   | MS2A   | ELS2B  | ELS2A  | 0                                                                                                                                                                                                                                                                                                                                                                                      | 0      |  |  |  |  |  |  |

| \$00 <b>6C</b>                     | TPM2C2VH      | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9                                                                                                                                                                                                                                                                                                                                                                                      | Bit 8  |  |  |  |  |  |  |

| \$00 <b>6D</b>                     | TPM2C2VL      | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1                                                                                                                                                                                                                                                                                                                                                                                      | Bit 0  |  |  |  |  |  |  |

| \$00 <b>6E</b>                     | TPM2C3SC      | CH3F   | CH3IE  | MS3B   | MS3A   | ELS3B  | ELS3A  | 0                                                                                                                                                                                                                                                                                                                                                                                      | 0      |  |  |  |  |  |  |

| \$00 <b>6F</b>                     | TPM2C3VH      | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9                                                                                                                                                                                                                                                                                                                                                                                      | Bit 8  |  |  |  |  |  |  |

| \$00 <b>70</b>                     | TPM2C3VL      | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1                                                                                                                                                                                                                                                                                                                                                                                      | Bit 0  |  |  |  |  |  |  |

| \$00 <b>71</b>                     | TPM2C4SC      | CH4F   | CH4IE  | MS4B   | MS4A   | ELS4B  | ELS4A  | 0                                                                                                                                                                                                                                                                                                                                                                                      | 0      |  |  |  |  |  |  |

| \$00 <b>72</b>                     | TPM2C4VH      | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9                                                                                                                                                                                                                                                                                                                                                                                      | Bit 8  |  |  |  |  |  |  |

| \$00 <b>73</b>                     | TPM2C4VL      | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1                                                                                                                                                                                                                                                                                                                                                                                      | Bit 0  |  |  |  |  |  |  |

| \$00 <b>74</b> –<br>\$00 <b>7F</b> | Reserved      | —      |        | —      | —      |        | —      | —                                                                                                                                                                                                                                                                                                                                                                                      | _      |  |  |  |  |  |  |

Chapter 5 Resets, Interrupts, and System Configuration

Each of these sources, with the exception of the background debug forced reset, has an associated bit in the system reset status register. Whenever the MCU enters reset, the internal clock generator (ICG) module switches to self-clocked mode with the frequency of  $f_{Self\_reset}$  selected. The reset pin is driven low for 34 internal bus cycles where the internal bus frequency is half the ICG frequency. After the 34 cycles are completed, the pin is released and will be pulled up by the internal pullup resistor, unless it is held low externally. After the pin is released, it is sampled after another 38 cycles to determine whether the reset pin is the cause of the MCU reset.

# 5.4 Computer Operating Properly (COP) Watchdog

The COP watchdog is intended to force a system reset when the application software fails to execute as expected. To prevent a system reset from the COP timer (when it is enabled), application software must reset the COP timer periodically. If the application program gets lost and fails to reset the COP before it times out, a system reset is generated to force the system back to a known starting point. The COP watchdog is enabled by the COPE bit in SOPT (see Section 5.8.4, "System Options Register (SOPT)" for additional information). The COP timer is reset by writing any value to the address of SRS. This write does not affect the data in the read-only SRS. Instead, the act of writing to this address is decoded and sends a reset signal to the COP timer.

After any reset, the COP timer is enabled. This provides a reliable way to detect code that is not executing as intended. If the COP watchdog is not used in an application, it can be disabled by clearing the COPE bit in the write-once SOPT register. Also, the COPT bit can be used to choose one of two timeout periods (2<sup>18</sup> or 2<sup>13</sup> cycles of the bus rate clock). Even if the application will use the reset default settings in COPE and COPT, the user should still write to write-once SOPT during reset initialization to lock in the settings. That way, they cannot be changed accidentally if the application program gets lost.

The write to SRS that services (clears) the COP timer should not be placed in an interrupt service routine (ISR) because the ISR could continue to be executed periodically even if the main application program fails.

When the MCU is in active background mode, the COP timer is temporarily disabled.

# 5.5 Interrupts

Interrupts provide a way to save the current CPU status and registers, execute an interrupt service routine (ISR), and then restore the CPU status so processing resumes where it left off before the interrupt. Other than the software interrupt (SWI), which is a program instruction, interrupts are caused by hardware events such as an edge on the IRQ pin or a timer-overflow event. The debug module can also generate an SWI under certain circumstances.

If an event occurs in an enabled interrupt source, an associated read-only status flag will become set. The CPU will not respond until and unless the local interrupt enable is set to 1 to enable the interrupt. The I bit in the CCR is 0 to allow interrupts. The global interrupt mask (I bit) in the CCR is initially set after reset which masks (prevents) all maskable interrupt sources. The user program initializes the stack pointer and performs other system setup before clearing the I bit to allow the CPU to respond to interrupts.

Chapter 6 Parallel Input/Output

| PTCD  |                 | Bit 7  | 6      | 5       | 4          | 3      | 2      | 1      | Bit 0  |

|-------|-----------------|--------|--------|---------|------------|--------|--------|--------|--------|

|       | Read:<br>Write: | PTCD7  | PTCD6  | PTCD5   | PTCD4      | PTCD3  | PTCD2  | PTCD1  | PTCD0  |

|       | Reset:          | 0      | 0      | 0       | 0          | 0      | 0      | 0      | 0      |

| PTCPE |                 |        |        |         |            |        |        |        |        |

|       | Read:<br>Write: | PTCPE7 | PTCPE6 | PTCPE5  | PTCPE4     | PTCPE3 | PTCPE2 | PTCPE1 | PTCPE0 |

|       | Reset:          | 0      | 0      | 0       | 0          | 0      | 0      | 0      | 0      |

| PTCSE |                 |        |        |         |            |        |        |        |        |

|       | Read:<br>Write: | PTCSE7 | PTCSE6 | PTCSE5  | PTCSE4     | PTCSE3 | PTCSE2 | PTCSE1 | PTCSE0 |

|       | Reset:          | 0      | 0      | 0       | 0          | 0      | 0      | 0      | 0      |

| PTCDD |                 |        |        |         |            |        |        |        |        |

|       | Read:<br>Write: | PTCDD7 | PTCDD6 | PTCDD5  | PTCDD4     | PTCDD3 | PTCDD2 | PTCDD1 | PTCDD0 |

|       | Reset:          | 0      | 0      | 0       | 0          | 0      | 0      | 0      | 0      |

|       |                 |        | Figure | 6-11 Po | rt C Regis | sters  |        |        |        |

Figure 6-11. Port C Registers

PTCDn — Port C Data Register Bit n (n = 0-7)

For port C pins that are inputs, reads return the logic level on the pin. For port C pins that are configured as outputs, reads return the last value written to this register.

Writes are latched into all bits of this register. For port C pins that are configured as outputs, the logic level is driven out the corresponding MCU pin.

Reset forces PTCD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled.

PTCPEn — Pullup Enable for Port C Bit n (n = 0-7)

For port C pins that are inputs, these read/write control bits determine whether internal pullup devices are enabled. For port C pins that are configured as outputs, these bits are ignored and the internal pullup devices are disabled.

1 = Internal pullup device enabled.

0 = Internal pullup device disabled.

PTCSEn — Slew Rate Control Enable for Port C Bit n (n = 0-7)

For port C pins that are outputs, these read/write control bits determine whether the slew rate controlled outputs are enabled. For port B pins that are configured as inputs, these bits are ignored.

1 = Slew rate control enabled.

0 = Slew rate control disabled.

**Chapter 6 Parallel Input/Output**

### PTEDDn — Data Direction for Port E Bit n (n = 0-7)

These read/write bits control the direction of port E pins and what is read for PTED reads.

- 1 = Output driver enabled for port E bit n and PTED reads return the contents of PTEDn.

- 0 = Input (output driver disabled) and reads return the pin value.

# 6.6.6 Port F Registers (PTFD, PTFPE, PTFSE, and PTFDD)

Port F includes eight general-purpose I/O pins that are not shared with any peripheral module. Port F pins used as general-purpose I/O pins are controlled by the port F data (PTFD), data direction (PTFDD), pullup enable (PTFPE), and slew rate control (PTFSE) registers.

| PTFD  |                 | Bit 7  | 6      | 5          | 4          | 3      | 2      | 1      | Bit 0  |

|-------|-----------------|--------|--------|------------|------------|--------|--------|--------|--------|

|       | Read:<br>Write: | PTFD7  | PTFD6  | PTFD5      | PTFD4      | PTFD3  | PTFD2  | PTFD1  | PTFD0  |

|       | Reset:          | 0      | 0      | 0          | 0          | 0      | 0      | 0      | 0      |

| PTFPE |                 |        |        |            |            |        |        |        |        |

|       | Read:<br>Write: | PTFPE7 | PTFPE6 | PTFPE5     | PTFPE4     | PTFPE3 | PTFPE2 | PTFPE1 | PTFPE0 |

|       | Reset:          | 0      | 0      | 0          | 0          | 0      | 0      | 0      | 0      |

| PTFSE |                 |        |        |            |            |        |        |        |        |

|       | Read:<br>Write: | PTFSE7 | PTFSE6 | PTFSE5     | PTFSE4     | PTFSE3 | PTFSE2 | PTFSE1 | PTFSE0 |

|       | Reset:          | 0      | 0      | 0          | 0          | 0      | 0      | 0      | 0      |

| PTFDD |                 |        |        |            |            |        |        |        |        |

|       | Read:<br>Write: | PTFDD7 | PTFDD6 | PTFDD5     | PTFDD4     | PTFDD3 | PTFDD2 | PTFDD1 | PTFDD0 |

|       | Reset:          | 0      | 0      | 0          | 0          | 0      | 0      | 0      | 0      |

|       |                 |        | Figure | e 6-14. Po | rt F Regis | sters  |        |        |        |

PTFDn — Port PTF Data Register Bit n (n = 0-7)

For port F pins that are inputs, reads return the logic level on the pin. For port F pins that are configured as outputs, reads return the last value written to this register.

Writes are latched into all bits of this register. For port F pins that are configured as outputs, the logic level is driven out the corresponding MCU pin.

Reset forces PTFD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled.

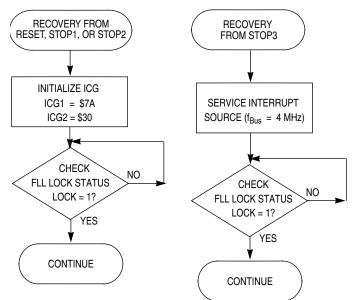

Internal Clock Generator (ICG) Module

### ICGC2 = \$30 (%00110000)

| Bit 7   | LOLRE | 0   | Generates an interrupt request on loss of lock  |

|---------|-------|-----|-------------------------------------------------|

| Bit 6:4 | MFD   | 011 | Sets the MFD multiplication factor to 10        |

| Bit 3   | LOCRE | 0   | Generates an interrupt request on loss of clock |

| Bit 2:0 | RFD   | 000 | Sets the RFD division factor to ÷1              |

### ICGS1 = \$xx

This is read only except for clearing interrupt flag

### ICGS2 = \$xx

This is read only. Should read DCOS before performing any time critical tasks

### ICGFLTLU/L =\$xx

Not used in this example

### ICGTRM

Not used in this example

Figure 7-9. ICG Initialization and Stop Recovery for Example #2

### 7.4.4 Example #3: No External Crystal Connection, 5.4 MHz Bus Frequency

In this example, the FLL will be used (in FEI mode) to multiply the internal 243 kHz (approximate) reference clock up to 10.8 MHz to achieve 5.4 MHz bus frequency. This system will also use the trim function to fine tune the frequency based on an external reference signal.

After the MCU is released from reset, the ICG is in self-clocked mode (SCM) and supplies approximately 8 MHz on ICGOUT which corresponds to a 4 MHz bus frequency (f<sub>Bus</sub>).

**Central Processor Unit (CPU)**

| Source                                                                                                          |                                            |                                                                                                                                                                                                                                               |   |   |   | eci<br>CC |   |   | ess<br>de<br>ode                                    |                                                  | and                                 | cles                            |

|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|-----------|---|---|-----------------------------------------------------|--------------------------------------------------|-------------------------------------|---------------------------------|

| Form                                                                                                            | Operation                                  | Description                                                                                                                                                                                                                                   | v | н | I | N         | z | с | Address<br>Mode                                     | Opcode                                           | Operand                             | Bus Cycles <sup>1</sup>         |

| LDA #opr8i<br>LDA opr8a<br>LDA opr16a<br>LDA oprx16,X<br>LDA oprx8,X<br>LDA ,X<br>LDA ,X<br>LDA oprx8,SP        | Load Accumulator from<br>Memory            | A ← (M)                                                                                                                                                                                                                                       | 0 | _ | _ |           |   | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 |                                                  | dd<br>hh II<br>ee ff<br>ff<br>ee ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 |

| LDHX #opr16i<br>LDHX opr8a<br>LDHX opr16a<br>LDHX ,X<br>LDHX oprx16,X<br>LDHX oprx8,X<br>LDHX oprx8,SP          | Load Index Register (H:X)<br>from Memory   | H:X ← (M:M + \$0001)                                                                                                                                                                                                                          | 0 | _ | _ |           |   | _ | IMM<br>DIR<br>EXT<br>IX<br>IX2<br>IX1<br>SP1        | 9EAE<br>9EBE<br>9ECE<br>9EFE                     | dd<br>hh II<br>ee ff<br>ff          | 3455655                         |

| LDX #opr8i<br>LDX opr8a<br>LDX opr16a<br>LDX oprx16,X<br>LDX oprx8,X<br>LDX x<br>LDX oprx16,SP<br>LDX oprx8,SP  | Load X (Index Register<br>Low) from Memory | $X \gets (M)$                                                                                                                                                                                                                                 | 0 | _ | _ |           |   | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 |                                                  | dd<br>hh II<br>ee ff<br>ff<br>ee ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 |

| LSL opr8a<br>LSLA<br>LSLX<br>LSL oprx8,X<br>LSL ,X<br>LSL oprx8,SP                                              | Logical Shift Left<br>(Same as ASL)        | C - 0<br>b7 b0                                                                                                                                                                                                                                |   | _ | _ |           |   |   | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 38<br>48<br>58<br>68<br>78<br>9E68               | ff                                  | 5<br>1<br>1<br>5<br>4<br>6      |

| LSR opr8a<br>LSRA<br>LSRX<br>LSR oprx8,X<br>LSR ,X<br>LSR oprx8,SP                                              | Logical Shift Right                        | $0 \rightarrow \boxed[b7]{b0} \hline C$                                                                                                                                                                                                       |   | _ | _ | 0         |   |   | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 34<br>44<br>54<br>64<br>74<br>9E64               | ff                                  | 5<br>1<br>5<br>4<br>6           |

| MOV opr8a,opr8a<br>MOV opr8a,X+<br>MOV #opr8i,opr8a<br>MOV ,X+,opr8a                                            | Move                                       | $(M)_{destination} \leftarrow (M)_{source}$<br>H:X $\leftarrow$ (H:X) + \$0001 in<br>IX+/DIR and DIR/IX+ Modes                                                                                                                                | 0 | _ | _ |           |   | _ | DIR/DIR<br>DIR/IX+<br>IMM/DIR<br>IX+/DIR            | 5E<br>6E                                         | dd dd<br>dd<br>ii dd<br>dd          | 5<br>5<br>4<br>5                |

| MUL                                                                                                             | Unsigned multiply                          | $X:A \leftarrow (X) \times (A)$                                                                                                                                                                                                               | - | 0 | - | -         | - | 0 | INH                                                 | 42                                               |                                     | 5                               |

| NEG opr8a<br>NEGA<br>NEG oprx8,X<br>NEG oprx8,X<br>NEG oprx8,SP                                                 | Negate<br>(Two's Complement)               | $\begin{array}{l} M \leftarrow - (M) = \$00 - (M) \\ A \leftarrow - (A) = \$00 - (A) \\ X \leftarrow - (X) = \$00 - (X) \\ M \leftarrow - (M) = \$00 - (M) \\ M \leftarrow - (M) = \$00 - (M) \\ M \leftarrow - (M) = \$00 - (M) \end{array}$ |   | _ | _ |           |   |   | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 30<br>40<br>50<br>60<br>70<br>9E60               |                                     | 5<br>1<br>5<br>4<br>6           |

| NOP                                                                                                             | No Operation                               | Uses 1 Bus Cycle                                                                                                                                                                                                                              | - | - | - | -         | - | - | INH                                                 | 9D                                               |                                     | 1                               |

| NSA                                                                                                             | Nibble Swap<br>Accumulator                 | $A \leftarrow (A[3:0]:A[7:4])$                                                                                                                                                                                                                | - | - | - | -         | - | - | INH                                                 | 62                                               |                                     | 1                               |

| ORA #opr8i<br>ORA opr8a<br>ORA opr16a<br>ORA oprx16,X<br>ORA oprx8,X<br>ORA ,X<br>ORA oprx16,SP<br>ORA oprx8,SP | Inclusive OR Accumulator<br>and Memory     | $A \gets (A) \mid (M)$                                                                                                                                                                                                                        | 0 | _ | _ |           |   | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | AA<br>BA<br>CA<br>DA<br>EA<br>FA<br>9EDA<br>9EEA | dd<br>hh II<br>ee ff<br>ff<br>ee ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 |

| PSHA                                                                                                            | Push Accumulator onto Stack                | Push (A); SP ← (SP) – \$0001                                                                                                                                                                                                                  | - | - | _ | -         | _ | _ | INH                                                 | 87                                               |                                     | 2                               |

| PSHH                                                                                                            | Push H (Index Register<br>High) onto Stack | Push (H); SP ← (SP) – \$0001                                                                                                                                                                                                                  | - | - | - | -         | - | - | INH                                                 | 8B                                               |                                     | 2                               |

| PSHX                                                                                                            | Push X (Index Register<br>Low) onto Stack  | $Push\ (X); SP \leftarrow (SP) - \$0001$                                                                                                                                                                                                      | - | - | - | -         | - | - | INH                                                 | 89                                               |                                     | 2                               |

#### Central Processor Unit (CPU)

| Bit-Manipulation Branch Read-Modify-Write |        |  |  |  |                         | Control Register/Memory |  |  |                        |        |                         |                                  |                        |                         |

|-------------------------------------------|--------|--|--|--|-------------------------|-------------------------|--|--|------------------------|--------|-------------------------|----------------------------------|------------------------|-------------------------|

| Dit-Manipulation                          | 9E60 6 |  |  |  | 001                     |                         |  |  | negister               | 9ED0 5 |                         |                                  |                        |                         |

|                                           |        |  |  |  | NEG<br>3 SP1            |                         |  |  |                        |        |                         | 4 SUB                            | SUB<br>3 SP1           |                         |

|                                           |        |  |  |  | 9E61 6<br>CBEQ<br>4 SP1 |                         |  |  |                        |        |                         | 9ED1 5<br>CMP<br>4 SP2           | CMP<br>3 SP1           |                         |

|                                           |        |  |  |  |                         |                         |  |  |                        |        |                         |                                  | 9EE2 4<br>SBC<br>3 SP1 |                         |

|                                           |        |  |  |  | 9E63 6<br>COM<br>3 SP1  |                         |  |  |                        |        |                         | 4 SP2<br>9ED3 5<br>CPX<br>4 SP2  | 13 SP1                 | 9EF3 6<br>CPHX<br>3 SP1 |

|                                           |        |  |  |  | 9E64 6<br>LSR<br>3 SP1  |                         |  |  |                        |        |                         | AND                              | 9EE4 4<br>AND<br>3 SP1 |                         |

|                                           |        |  |  |  |                         |                         |  |  |                        |        |                         | 9ED5 5<br>BIT<br>4 SP2           | BIT<br>3 SP1           |                         |

|                                           |        |  |  |  | 9E66 6<br>ROR<br>3 SP1  |                         |  |  |                        |        |                         | 9ED6 5<br>LDA<br>4 SP2           | 9EE6 4<br>LDA<br>3 SP1 |                         |

|                                           |        |  |  |  | 9E67 6<br>ASR<br>3 SP1  |                         |  |  |                        |        |                         | 9ED7 5<br>STA<br>4 SP2           | STA<br>3 SP1           |                         |

|                                           |        |  |  |  | 9E68 6<br>LSL<br>3 SP1  |                         |  |  |                        |        |                         | 9ED8 5<br>EOR<br>4 SP2<br>9ED9 5 | 9EE8 4<br>EOR<br>3 SP1 |                         |

|                                           |        |  |  |  | 9E69 6<br>ROL<br>3 SP1  |                         |  |  |                        |        |                         | ADC                              | 3 SP1                  |                         |

|                                           |        |  |  |  | 9E6A 6<br>DEC<br>3 SP1  |                         |  |  |                        |        |                         | 9EDA 5<br>ORA<br>4 SP2           | 3 SP1                  |                         |

|                                           |        |  |  |  | 9E6B 8<br>DBNZ<br>4 SP1 |                         |  |  |                        |        |                         | 9EDB 5<br>ADD<br>4 SP2           | ADD                    |                         |

|                                           |        |  |  |  | 9E6C 6<br>INC<br>3 SP1  |                         |  |  |                        |        |                         |                                  |                        |                         |

|                                           |        |  |  |  | 9E6D 5<br>TST<br>3 SP1  |                         |  |  |                        |        |                         |                                  |                        |                         |

|                                           |        |  |  |  |                         |                         |  |  | 9EAE 5<br>LDHX<br>2 IX | LDHX   | 9ECE 5<br>LDHX<br>3 IX1 | 9EDE 5<br>LDX<br>4 SP2<br>9EDF 5 | 9EEE 4<br>LDX<br>3 SP1 | 9EFE 5<br>LDHX<br>3 SP1 |

|                                           |        |  |  |  | 9E6F 6<br>CLR<br>3 SP1  |                         |  |  |                        |        |                         | 9EDF 5<br>STX<br>4 SP2           | 9EEF 4<br>STX<br>3 SP1 | 9EFF 5<br>STHX<br>3 SP1 |

### Table 8-2. Opcode Map (Sheet 2 of 2)

Inherent Immediate Direct Extended DIR to DIR IX+ to DIR REL IX IX1 IX2 IMD DIX+ INH IMM DIR EXT DD IX+D

Relative Indexed, No Offset Indexed, 8-Bit Offset Indexed, 16-Bit Offset IMM to DIR DIR to IX+

Stack Pointer, 8-Bit Offset Stack Pointer, 16-Bit Offset Indexed, No Offset with Post Increment Indexed, 1-Byte Offset with Post Increment

SP1 SP2 IX+

IX1+

Note: All Sheet 2 Opcodes are Preceded by the Page 2 Prebyte (9E)

Prebyte (9E) and Opcode in Hexadecimal 9E60 6 NEG Number of Bytes 3 SP1 Addressing Mode

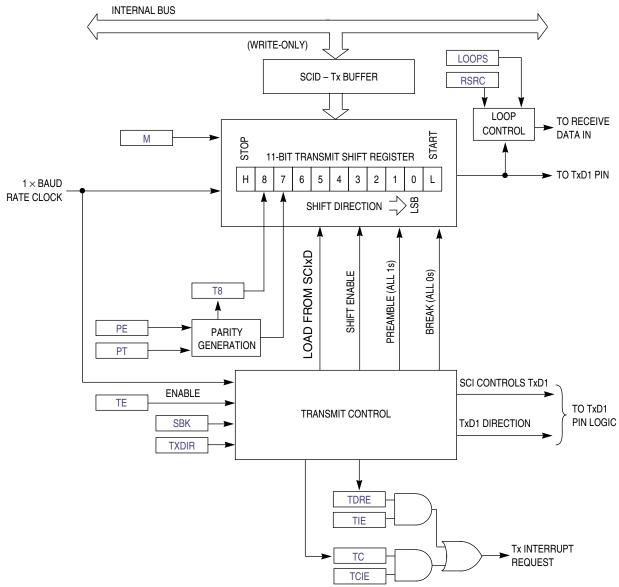

**Transmitter Functional Description**

Figure 11-3. SCI Transmitter Block Diagram

The transmitter is enabled by setting the TE bit in SCIxC2. This queues a preamble character that is one full character frame of logic high. The transmitter then remains idle (TxD1 pin remains high) until data is available in the transmit data buffer. Programs store data into the transmit data buffer by writing to the SCI data register (SCIxD).

The central element of the SCI transmitter is the transmit shift register that is either 10 or 11 bits long depending on the setting in the M control bit. For the remainder of this section, we will assume M = 0, selecting the normal 8-bit data mode. In 8-bit data mode, the shift register holds a start bit, eight data bits, and a stop bit. When the transmit shift register is available for a new SCI character, the value waiting in the transmit data register is transferred to the shift register (synchronized with the baud rate clock) and the transmit data register empty (TDRE) status flag is set to indicate another character may be written to the transmit data buffer at SCIxD.

#### Serial Peripheral Interface (SPI) Module

The most common uses of the SPI system include connecting simple shift registers for adding input or output ports or connecting small peripheral devices such as serial A/D or D/A converters. Although Figure 12-2 shows a system where data is exchanged between two MCUs, many practical systems involve simpler connections where data is unidirectionally transferred from the master MCU to a slave or from a slave to the master MCU.

### 12.2.2 SPI Module Block Diagram

Figure 12-3 is a block diagram of the SPI module. The central element of the SPI is the SPI shift register. Data is written to the double-buffered transmitter (write to SPI1D) and gets transferred to the SPI shift register at the start of a data transfer. After shifting in a byte of data, the data is transferred into the double-buffered receiver where it can be read (read from SPI1D). Pin multiplexing logic controls connections between MCU pins and the SPI module.

When the SPI is configured as a master, the clock output is routed to the SPSCK1 pin, the shifter output is routed to MOSI1, and the shifter input is routed from the MISO1 pin.

When the SPI is configured as a slave, the SPSCK1 pin is routed to the clock input of the SPI, the shifter output is routed to MISO1, and the shifter input is routed from the MOSI1 pin.

In the external SPI system, simply connect all SPSCK pins to each other, all MISO pins together, and all MOSI pins together. Peripheral devices often use slightly different names for these pins.

Serial Peripheral Interface (SPI) Module

| SPPR2:SPPR1:SPPR0 | Prescaler Divisor |

|-------------------|-------------------|

| 0:0:0             | 1                 |

| 0:0:1             | 2                 |

| 0:1:0             | 3                 |

| 0:1:1             | 4                 |

| 1:0:0             | 5                 |

| 1:0:1             | 6                 |

| 1:1:0             | 7                 |

| 1:1:1             | 8                 |

#### Table 12-2. SPI Baud Rate Prescaler Divisor

### SPR2:SPR1:SPR0 - SPI Baud Rate Divisor

This 3-bit field selects one of eight divisors for the SPI baud rate divider as shown in Figure 12-3. The input to this divider comes from the SPI baud rate prescaler (see Figure 12-4). The output of this divider is the SPI bit rate clock for master mode.

| SPR2:SPR1:SPR0 | Rate Divisor |

|----------------|--------------|

| 0:0:0          | 2            |

| 0:0:1          | 4            |

| 0:1:0          | 8            |

| 0:1:1          | 16           |

| 1:0:0          | 32           |

| 1:0:1          | 64           |

| 1:1:0          | 128          |

| 1:1:1          | 256          |

Table 12-3. SPI Baud Rate Divisor

Inter-Integrated Circuit (IIC) Module

### 13.2.1.1 START Signal

When the bus is free; i.e., no master device is engaging the bus (both SCL and SDA lines are at logical high), a master may initiate communication by sending a START signal. As shown in Figure 13-3, a START signal is defined as a high-to-low transition of SDA while SCL is high. This signal denotes the beginning of a new data transfer (each data transfer may contain several bytes of data) and brings all slaves out of their idle states.

### 13.2.1.2 Slave Address Transmission

The first byte of data transferred immediately after the START signal is the slave address transmitted by the master. This is a seven-bit calling address followed by a R/W bit. The R/W bit tells the slave the desired direction of data transfer.

- 1 =Read transfer, the slave transmits data to the master.

- 0 = Write transfer, the master transmits data to the slave.

Only the slave with a calling address that matches the one transmitted by the master will respond by sending back an acknowledge bit. This is done by pulling the SDA low at the 9th clock (see Figure 13-3).

No two slaves in the system may have the same address. If the IIC module is the master, it must not transmit an address that is equal to its own slave address. The IIC cannot be master and slave at the same time. However, if arbitration is lost during an address cycle, the IIC will revert to slave mode and operate correctly even if it is being addressed by another master.

### 13.2.1.3 Data Transfer

Before successful slave addressing is achieved, the data transfer can proceed byte-by-byte in a direction specified by the R/W bit sent by the calling master.

All transfers that come after an address cycle are referred to as data transfers, even if they carry sub-address information for the slave device

Each data byte is 8 bits long. Data may be changed only while SCL is low and must be held stable while SCL is high as shown in Figure 13-3. There is one clock pulse on SCL for each data bit, the MSB being transferred first. Each data byte is followed by a 9th (acknowledge) bit, which is signalled from the receiving device. An acknowledge is signalled by pulling the SDA low at the ninth clock. In summary, one complete data transfer needs nine clock pulses.

If the slave receiver does not acknowledge the master in the 9th bit time, the SDA line must be left high by the slave. The master interprets the failed acknowledge as an unsuccessful data transfer.

If the master receiver does not acknowledge the slave transmitter after a data byte transmission, the slave interprets this as an end of data transfer and releases the SDA line.

In either case, the data transfer is aborted and the master does one of two things:

- Relinquishes the bus by generating a STOP signal.

- Commences a new calling by generating a repeated START signal.

#### Inter-Integrated Circuit (IIC) Module

Note that the TX bit in IIC1C must correctly reflect the desired direction of transfer in master and slave modes for the transmission to begin. For instance, if the IIC is configured for master transmit but a master receive is desired, then reading the IIC1D will not initiate the receive.

Reading the IIC1D will return the last byte received while the IIC is configured in either master receive or slave receive modes. The IIC1D does not reflect every byte that is transmitted on the IIC bus, nor can software verify that a byte has been written to the IIC1D correctly by reading it back.

In master transmit mode, the first byte of data written to IIC1D following assertion of MST is used for the address transfer and should comprise of the calling address (in bit 7–bit 1) concatenated with the required R/W bit (in position bit 0).

# Chapter 14 Analog-to-Digital Converter (ATD) Module

The MC9S08GB/GT provides one 8-channel analog-to-digital (ATD) module. The eight ATD channels share port B. Each channel individually can be configured for general-purpose I/O or for ATD functionality. All features of the ATD module as described in this section are available on the MC9S08GB/GT. Electrical parametric information for the ATD may be found in Appendix A, "Electrical Characteristics."

# 15.4 On-Chip Debug System (DBG)

Because HCS08 devices do not have external address and data buses, the most important functions of an in-circuit emulator have been built onto the chip with the MCU. The debug system consists of an 8-stage FIFO that can store address or data bus information, and a flexible trigger system to decide when to capture bus information and what information to capture. The system relies on the single-wire background debug system to access debug control registers and to read results out of the eight stage FIFO.

The debug module includes control and status registers that are accessible in the user's memory map. These registers are located in the high register space to avoid using valuable direct page memory space.

Most of the debug module's functions are used during development, and user programs rarely access any of the control and status registers for the debug module. The one exception is that the debug system can provide the means to implement a form of ROM patching. This topic is discussed in greater detail in Section 15.4.6, "Hardware Breakpoints."

## 15.4.1 Comparators A and B

Two 16-bit comparators (A and B) can optionally be qualified with the R/W signal and an opcode tracking circuit. Separate control bits allow you to ignore R/W for each comparator. The opcode tracking circuitry optionally allows you to specify that a trigger will occur only if the opcode at the specified address is actually executed as opposed to only being read from memory into the instruction queue. The comparators are also capable of magnitude comparisons to support the inside range and outside range trigger modes. Comparators are disabled temporarily during all BDC accesses.

The A comparator is always associated with the 16-bit CPU address. The B comparator compares to the CPU address or the 8-bit CPU data bus, depending on the trigger mode selected. Because the CPU data bus is separated into a read data bus and a write data bus, the RWAEN and RWA control bits have an additional purpose, in full address plus data comparisons they are used to decide which of these buses to use in the comparator B data bus comparisons. If RWAEN = 1 (enabled) and RWA = 0 (write), the CPU's write data bus is used. Otherwise, the CPU's read data bus is used.

The currently selected trigger mode determines what the debugger logic does when a comparator detects a qualified match condition. A match can cause:

- Generation of a breakpoint to the CPU

- Storage of data bus values into the FIFO

- Starting to store change-of-flow addresses into the FIFO (begin type trace)

- Stopping the storage of change-of-flow addresses into the FIFO (end type trace)

# 15.4.2 Bus Capture Information and FIFO Operation

The usual way to use the FIFO is to setup the trigger mode and other control options, then arm the debugger. When the FIFO has filled or the debugger has stopped storing data into the FIFO, you would read the information out of it in the order it was stored into the FIFO. Status bits indicate the number of words of valid information that are in the FIFO as data is stored into it. If a trace run is manually halted by writing 0 to ARM before the FIFO is full (CNT = 1:0:0:0), the information is shifted by one position and

Appendix A Electrical Characteristics

# A.3 Thermal Characteristics

This section provides information about operating temperature range, power dissipation, and package thermal resistance. Power dissipation on I/O pins is usually small compared to the power dissipation in on-chip logic and voltage regulator circuits and it is user-determined rather than being controlled by the MCU design. In order to take  $P_{I/O}$  into account in power calculations, determine the difference between actual pin voltage and  $V_{SS}$  or  $V_{DD}$  and multiply by the pin current for each I/O pin. Except in cases of unusually high pin current (heavy loads), the difference between pin voltage and  $V_{SS}$  or  $V_{DD}$  will be very small.

Table A-2. Thermal Characteristics

| Rating                                                                                                   | Symbol                          | Value                 | Unit | Temp.<br>Code |

|----------------------------------------------------------------------------------------------------------|---------------------------------|-----------------------|------|---------------|

| Operating temperature range (packaged)                                                                   | T <sub>A</sub>                  | -40 to 85             | °C   | С             |

| Thermal resistance<br>64-pin LQFP (GB60)<br>48-pin QFN (GT60)<br>42-pin SDIP (GT60)<br>44-pin QFP (GT60) | θ <sub>JA</sub> <sup>1, 2</sup> | 65<br>82<br>57<br>118 | °C/W | _             |

<sup>1</sup> Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, airflow, power dissipation of other components on the board, and board thermal resistance.

<sup>2</sup> Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal. Single layer board is designed per JEDEC JESD51-3.

The average chip-junction temperature  $(T_J)$  in °C can be obtained from:

$$T_J = T_A + (P_D \times \theta_{JA})$$

Eqn. A-2

where:

$T_A$  = Ambient temperature, °C

$\theta_{IA}$  = Package thermal resistance, junction-to-ambient, °C/W

$P_D = P_{int} + P_{I/O}$

$P_{int} = I_{DD} \times V_{DD}$ , Watts — chip internal power

$P_{I/O}$  = Power dissipation on input and output pins — user determined

For most applications,  $P_{I/O} \ll P_{int}$  and can be neglected. An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is:

$$P_{D} = K \div (T_{J} + 273^{\circ}C) \qquad \qquad Eqn. A-2$$

Solving equations 1 and 2 for K gives:

$$K = P_D \times (T_A + 273^{\circ}C) + \theta_{JA} \times (P_D)^2$$

Eqn. A-3

where K is a constant pertaining to the particular part. K can be determined from equation 3 by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  can be obtained by solving equations 1 and 2 iteratively for any value of  $T_A$ .

#### Appendix A Electrical Characteristics

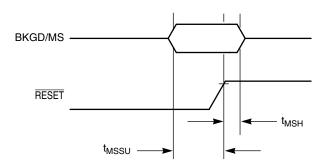

- <sup>1</sup> This is the shortest pulse that is guaranteed to be recognized as a reset pin request. Shorter pulses are not guaranteed to override reset requests from internal sources.

- <sup>2</sup> When any reset is initiated, internal circuitry drives the reset pin low for about 34 cycles of f<sub>Self\_reset</sub> and then samples the level on the reset pin about 38 cycles later to distinguish external reset requests from internal requests.

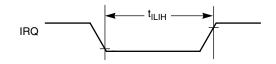

- <sup>3</sup> This is the minimum pulse width that is guaranteed to pass through the pin synchronization circuitry. Shorter pulses may or may not be recognized. In stop mode, the synchronizer is bypassed so shorter pulses can be recognized in that case.

- $^4$  Timing is shown with respect to 20%  $V_{DD}$  and 80%  $V_{DD}$  levels. Temperature range –40°C to 85°C.

Figure A-11. Reset Timing

Figure A-12. Active Background Debug Mode Latch Timing

### A.9.2 Timer/PWM (TPM) Module Timing

Synchronizer circuits determine the shortest input pulses that can be recognized or the fastest clock that can be used as the optional external source to the timer counter. These synchronizers operate from the current bus rate clock.

B.4 48-Pin QFN Package Drawing