Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                       |                                                                                                                                 |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Product Status                | Active                                                                                                                          |

| Core Processor                | ARM® Cortex®-M7                                                                                                                 |

| Core Size                     | 32-Bit Single-Core                                                                                                              |

| Speed                         | 480MHz                                                                                                                          |

| Connectivity                  | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MDIO, MMC/SD/SDIO, QSPI, SAI, SPDIF, SPI, SWPMI, UART/USART, USB OTG |

| Peripherals                   | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                                               |

| Number of I/O                 | 140                                                                                                                             |

| Program Memory Size           | 2MB (2M x 8)                                                                                                                    |

| Program Memory Type           | FLASH                                                                                                                           |

| EEPROM Size                   | -                                                                                                                               |

| RAM Size                      | 1M x 8                                                                                                                          |

| Voltage - Supply<br>(Vcc/Vdd) | 1.62V ~ 3.6V                                                                                                                    |

| Data Converters               | A/D 36x16b; D/A 2x12b                                                                                                           |

| Oscillator Type               | Internal                                                                                                                        |

| Operating<br>Temperature      | -40°C ~ 85°C (TA)                                                                                                               |

| Mounting Type                 | Surface Mount                                                                                                                   |

| Package / Case                | 201-UFBGA                                                                                                                       |

| Supplier Device<br>Package    | 176+25UFBGA (10x10)                                                                                                             |

| Purchase URL                  | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32h753iik6                                                           |

STM32H753xI Functional overview

### 3.3 Memories

# 3.3.1 Embedded Flash memory

The STM32H753xl devices embed up to 2 Mbytes of Flash memory that can be used for storing programs and data.

The Flash memory is organized as 266-bit Flash words memory that can be used for storing both code and data constants. Each word consists of:

- One Flash word (8 words, 32 bytes or 256 bits)

- 10 ECC bits.

The Flash memory is divided into two independent banks. Each bank is organized as follows:

- A 1-Mbyte user Flash memory block containing eight user sectors of 128 Kbytes(4 K Flash words)

- 128 Kbytes of System Flash memory from which the device can boot

- 2 Kbytes (64 Flash words) of user option bytes for user configuration

### 3.3.2 Secure access mode

In addition to other typical memory protection mechanism (RDP, PCROP), STM32H753xl devices introduce the Secure access mode, a new enhanced security feature. This mode allows developing user-defined secure services by ensuring, on the one hand code and data protection and on the other hand code safe execution.

Two types of secure services are available:

- STMicroelectronics Root Secure Services:

- These services are embedded in System memory. They provide a secure solution for firmware and third-party modules installation. These services rely on cryptographic algorithms based on a device unique private key.

- User-defined secure services:

- These services are embedded in user Flash memory. Examples of user secure services are proprietary user firmware update solution, secure Flash integrity check or any other sensitive applications that require a high level of protection.

- The secure firmware is embedded in specific user Flash memory areas configured through option bytes.

Secure services are executed just after a reset and preempt all other applications to guarantee protected and safe execution. Once executed, the corresponding code and data are no more accessible.

The above secure services are available only for Cortex<sup>®</sup>-M7 core operating in Secure access mode. The other masters cannot access the option bytes involved in Secure access mode settings or the Flash secured areas.

57

DS12117 Rev 5 19/232

STM32H753xI Functional overview

The boot loader is located in non-user System memory. It is used to reprogram the Flash memory through a serial interface (USART, I2C, SPI, USB-DFU). Refer to *STM32* microcontroller System memory Boot mode application note (AN2606) for details.

# 3.5 Power supply management

### 3.5.1 Power supply scheme

STM32H53xl power supply voltages are the following:

- V<sub>DD</sub> = 1.62 to 3.6 V: external power supply for I/Os, provided externally through V<sub>DD</sub> pins.

- V<sub>DDLDO</sub> = 1.62 to 3.6 V: supply voltage for the internal regulator supplying V<sub>CORE</sub>

- V<sub>DDA</sub> = 1.62 to 3.6 V: external analog power supplies for ADC, DAC, COMP and OPAMP.

- V<sub>DD33USB</sub> and V<sub>DD50USB</sub>:

- $V_{DD50USB}$  can be supplied through the USB cable to generate the  $V_{DD33USB}$  via the USB internal regulator. This allows supporting a  $V_{DD}$  supply different from 3.3 V.

- The USB regulator can be bypassed to supply directly  $V_{DD33USB}$  if  $V_{DD}$  = 3.3 V.

- V<sub>BAT</sub> = 1.2 to 3.6 V: power supply for the V<sub>SW</sub> domain when V<sub>DD</sub> is not present.

- V<sub>CAP</sub>: V<sub>CORE</sub> supply voltage, which values depend on voltage scaling (0.7 V, 0.9 V, 1.0 V, 1.1 V or 1.2 V). They are configured through VOS bits in PWR\_D3CR register. The V<sub>CORE</sub> domain is split into the following power domains that can be independently switch off.

- D1 domain containing some peripherals and the Cortex<sup>®</sup>-M7 core.

- D2 domain containing a large part of the peripherals.

- D3 domain containing some peripherals and the system control.

During power-up and power-down phases, the following power sequence requirements must be respected (see *Figure 2*):

- When  $V_{DD}$  is below 1 V, other power supplies ( $V_{DDA}$ ,  $V_{DD33USB}$ ,  $V_{DD50USB}$ ) must remain below  $V_{DD}$  + 300 mV.

- When V<sub>DD</sub> is above 1 V, all power supplies are independent.

During the power-down phase,  $V_{DD}$  can temporarily become lower than other supplies only if the energy provided to the microcontroller remains below 1 mJ. This allows external decoupling capacitors to be discharged with different time constants during the power-down transient phase.

DS12117 Rev 5 21/232

STM32H753xl Functional overview

# 3.28 Cryptographic acceleration (CRYPT and HASH)

The devices embed a cryptographic processor that supports the advanced cryptographic algorithms usually required to ensure confidentiality, authentication, data integrity and non-repudiation when exchanging messages with a peer:

- Encryption/Decryption

- DES/TDES (data encryption standard/triple data encryption standard): ECB (electronic codebook) and CBC (cipher block chaining) chaining algorithms, 64-, 128- or 192-bit key

- AES (advanced encryption standard): ECB, CBC, GCM, CCM, and CTR (Counter mode) chaining algorithms, 128, 192 or 256-bit key

- Universal HASH

- SHA-1 and SHA-2 (secure HASH algorithms)

- MD5

- HMAC

The cryptographic accelerator supports DMA request generation.

# 3.29 Timers and watchdogs

The devices include one high-resolution timer, two advanced-control timers, ten general-purpose timers, two basic timers, five low-power timers, two watchdogs and a SysTick timer.

All timer counters can be frozen in Debug mode.

*Table 5* compares the features of the advanced-control, general-purpose and basic timers.

Max Max **DMA** Capture/ timer Comple-Timer Counter Counter **Prescaler** interface Timer request compare mentary clock type resolution type factor clock (MHz) (1) generation channels output (MHz) /1 /2 /4 High-(x2 x4 x8 HRTIM1 400 400 resolution 16-bit Up Yes 10 Yes x16 x32, timer with DLL) Any Up, integer TIM1, Advanced 16-bit between 1 100 200 Down, Yes Yes 4 -control TIM8 Up/down and 65536

Table 5. Timer feature comparison

STM32H753xl Functional overview

# 3.31 Inter-integrated circuit interface (I2C)

STM32H753xI devices embed four I<sup>2</sup>C interfaces.

The I<sup>2</sup>C bus interface handles communications between the microcontroller and the serial I<sup>2</sup>C bus. It controls all I<sup>2</sup>C bus-specific sequencing, protocol, arbitration and timing.

The I2C peripheral supports:

- I<sup>2</sup>C-bus specification and user manual rev. 5 compatibility:

- Slave and Master modes, multimaster capability

- Standard-mode (Sm), with a bitrate up to 100 kbit/s

- Fast-mode (Fm), with a bitrate up to 400 kbit/s

- Fast-mode Plus (Fm+), with a bitrate up to 1 Mbit/s and 20 mA output drive I/Os

- 7-bit and 10-bit addressing mode, multiple 7-bit slave addresses

- Programmable setup and hold times

- Optional clock stretching

- System Management Bus (SMBus) specification rev 2.0 compatibility:

- Hardware PEC (Packet Error Checking) generation and verification with ACK control

- Address resolution protocol (ARP) support

- SMBus alert

- Power System Management Protocol (PMBus<sup>TM</sup>) specification rev 1.1 compatibility

- Independent clock: a choice of independent clock sources allowing the I2C communication speed to be independent from the PCLK reprogramming.

- Wakeup from Stop mode on address match

- Programmable analog and digital noise filters

- 1-byte buffer with DMA capability

# 3.32 Universal synchronous/asynchronous receiver transmitter (USART)

STM32H753xl devices have four embedded universal synchronous receiver transmitters (USART1, USART2, USART3 and USART6) and four universal asynchronous receiver transmitters (UART4, UART5, UART7 and UART8). Refer to *Table 6* for a summary of USARTx and UARTx features.

These interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire Half-duplex communication mode and have LIN Master/Slave capability. They provide hardware management of the CTS and RTS signals, and RS485 Driver Enable. They are able to communicate at speeds of up to 12.5 Mbit/s.

USART1, USART2, USART3 and USART6 also provide Smartcard mode (ISO 7816 compliant) and SPI-like communication capability.

The USARTs embed a Transmit FIFO (TXFIFO) and a Receive FIFO (RXFIFO). FIFO mode is enabled by software and is disabled by default.

577

DS12117 Rev 5 41/232

Functional overview STM32H753xI

# 3.41 Universal serial bus on-the-go high-speed (OTG\_HS)

The devices embed two USB OTG high-speed (up to 480 Mbit/s) device/host/OTG peripheral. OTG-HS1 supports both full-speed and high-speed operations, while OTG-HS2 supports only full-speed operations. They both integrate the transceivers for full-speed operation (12 Mbit/s) and are able to operate from the internal HSI48 oscillator. OTG-HS1 features a UTMI low-pin interface (ULPI) for high-speed operation (480 Mbit/s). When using the USB OTG-HS1 in HS mode, an external PHY device connected to the ULPI is required.

The USB OTG HS peripherals are compliant with the USB 2.0 specification and with the OTG 2.0 specification. They have software-configurable endpoint setting and supports suspend/resume. The USB OTG controllers require a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator.

### The main features are:

- Combined Rx and Tx FIFO size of 4 Kbytes with dynamic FIFO sizing

- Supports the session request protocol (SRP) and host negotiation protocol (HNP)

- 9 bidirectional endpoints (including EP0)

- 16 host channels with periodic OUT support

- Software configurable to OTG1.3 and OTG2.0 modes of operation

- USB 2.0 LPM (Link Power Management) support

- Battery Charging Specification Revision 1.2 support

- Internal FS OTG PHY support

- External HS or HS OTG operation supporting ULPI in SDR mode (OTG\_HS1 only)

The OTG PHY is connected to the microcontroller ULPI port through 12 signals. It can be clocked using the 60 MHz output.

- Internal USB DMA

- HNP/SNP/IP inside (no need for any external resistor)

- For OTG/Host modes, a power switch is needed in case bus-powered devices are connected

# 3.42 Ethernet MAC interface with dedicated DMA controller (ETH)

The devices provide an IEEE-802.3-2002-compliant media access controller (MAC) for ethernet LAN communications through an industry-standard medium-independent interface (MII) or a reduced medium-independent interface (RMII). The microcontroller requires an external physical interface device (PHY) to connect to the physical LAN bus (twisted-pair, fiber, etc.). The PHY is connected to the device MII port using 17 signals for MII or 9 signals for RMII, and can be clocked using the 25 MHz (MII) from the microcontroller.

STM32H753xI Functional overview

The devices include the following features:

- Supports 10 and 100 Mbit/s rates

- Dedicated DMA controller allowing high-speed transfers between the dedicated SRAM and the descriptors

- Tagged MAC frame support (VLAN support)

- Half-duplex (CSMA/CD) and full-duplex operation

- MAC control sublayer (control frames) support

- 32-bit CRC generation and removal

- Several address filtering modes for physical and multicast address (multicast and group addresses)

- 32-bit status code for each transmitted or received frame

- Internal FIFOs to buffer transmit and receive frames. The transmit FIFO and the receive FIFO are both 2 Kbytes.

- Supports hardware PTP (precision time protocol) in accordance with IEEE 1588 2008 (PTP V2) with the time stamp comparator connected to the TIM2 input

- Triggers interrupt when system time becomes greater than target time

# 3.43 High-definition multimedia interface (HDMI) - consumer electronics control (CEC)

The devices embed a HDMI-CEC controller that provides hardware support for the Consumer Electronics Control (CEC) protocol (Supplement 1 to the HDMI standard).

This protocol provides high-level control functions between all audiovisual products in an environment. It is specified to operate at low speeds with minimum processing and memory overhead. It has a clock domain independent from the CPU clock, allowing the HDMI-CEC controller to wakeup the MCU from Stop mode on data reception.

# 3.44 Debug infrastructure

The devices offer a comprehensive set of debug and trace features to support software development and system integration.

- Breakpoint debugging

- Code execution tracing

- Software instrumentation

- JTAG debug port

- Serial-wire debug port

- Trigger input and output

- Serial-wire trace port

- Trace port

- Arm<sup>®</sup> CoreSight<sup>™</sup> debug and trace components

The debug can be controlled via a JTAG/Serial-wire debug access port, using industry standard debugging tools.

The trace port performs data capture for logging and analysis.

DS12117 Rev 5 47/232

Memory mapping STM32H753xI

# 4 Memory mapping

Refer to the product line reference manual for details on the memory mapping as well as the boundary addresses for all peripherals.

STM32H753xl Pin descriptions

Table 7. Legend/abbreviations used in the pinout table

| Nar           | ne                   | Abbreviation                    | Definition                                                                                  |

|---------------|----------------------|---------------------------------|---------------------------------------------------------------------------------------------|

| Pin na        | ame                  |                                 | ecified in brackets below the pin name, the pin function during same as the actual pin name |

|               |                      | S                               | Supply pin                                                                                  |

| Pin t         | VIDO                 | I                               | Input only pin                                                                              |

| FIII (        | ype                  | I/O                             | Input / output pin                                                                          |

|               |                      | ANA                             | Analog-only Input                                                                           |

|               |                      | FT                              | 5 V tolerant I/O                                                                            |

|               |                      | TT                              | 3.3 V tolerant I/O                                                                          |

|               |                      | В                               | Dedicated BOOT0 pin                                                                         |

|               |                      | RST                             | Bidirectional reset pin with embedded weak pull-up resistor                                 |

| I/O stru      | ıcture               |                                 | Option for TT and FT I/Os                                                                   |

|               |                      | _f                              | I2C FM+ option                                                                              |

|               |                      | _a                              | analog option (supplied by V <sub>DDA</sub> )                                               |

|               |                      | _u                              | USB option (supplied by V <sub>DD33USB</sub> )                                              |

|               |                      | _h                              | High Speed Low Voltage                                                                      |

| Not           | es                   | Unless otherwise spafter reset. | ecified by a note, all I/Os are set as floating inputs during and                           |

| Pin functions | Alternate functions  | Functions selected the          | hrough GPIOx_AFR registers                                                                  |

| FILLIULICUOUS | Additional functions | Functions directly se           | elected/enabled through peripheral registers                                                |

Pin descriptions STM32H753xI

Table 8. STM32H753xl pin/ball definition (continued)

|         |          |         | Pin/ba   | all nam     |         |         |                   |                                          |          |               |       | continued)                                                                                                                                        |                           |

|---------|----------|---------|----------|-------------|---------|---------|-------------------|------------------------------------------|----------|---------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| LQFP100 | TFBGA100 | LQFP144 | UFBGA169 | UFBGA176+25 | LQFP176 | LQFP208 | TFBGA240 +25      | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                                               | Additional<br>functions   |

| 22      | G2       | 34      | J5       | N3          | 40      | 43      | N5 <sup>(5)</sup> | PA0                                      | I/O      | FT_a          | -     | TIM2_CH1/TIM2_ETR, TIM5_CH1, TIM8_ETR, TIM15_BKIN, USART2_CTS_NSS, UART4_TX, SDMMC2_CMD, SAI2_SD_B, ETH_MII_CRS, EVENTOUT                         | ADC1_INP16,<br>WKUP0      |

| -       | -        | -       | -        | -           | -       | -       | T1 <sup>(5)</sup> | PA0_C                                    | ANA      | TT_a          | -     | -                                                                                                                                                 | ADC12_INN1,<br>ADC12_INP0 |

| 23      | H2       | 35      | K4       | N2          | 41      | 44      | N4 <sup>(5)</sup> | PA1                                      | I/O      | FT_<br>ha     | -     | TIM2_CH2, TIM5_CH2, LPTIM3_OUT, TIM15_CH1N, USART2_RTS, UART4_RX, QUADSPI_BK1_IO3, SAI2_MCK_B, ETH_MII_RX_CLK/ETH_ RMII_REF_CLK, LCD_R2, EVENTOUT | ADC1_INN16,<br>ADC1_INP17 |

| -       | -        | -       | -        | -           | -       | -       | T2 <sup>(5)</sup> | PA1_C                                    | ANA      | TT_a          | -     | -                                                                                                                                                 | ADC12_INP1                |

| 24      | J2       | 36      | N1       | P2          | 42      | 45      | N3                | PA2                                      | I/O      | FT_a          | -     | TIM2_CH3, TIM5_CH3,<br>LPTIM4_OUT,<br>TIM15_CH1,<br>USART2_TX,<br>SAI2_SCK_B,<br>ETH_MDIO,<br>MDIOS_MDIO, LCD_R1,<br>EVENTOUT                     | ADC12_INP14,<br>WKUP1     |

| -       | 1        | -       | N2       | F4          | 43      | 46      | N2                | PH2                                      | I/O      | FT_<br>ha     | -     | LPTIM1_IN2, QUADSPI_BK2_IO0, SAI2_SCK_B, ETH_MII_CRS, FMC_SDCKE0, LCD_R0, EVENTOUT                                                                | ADC3_INP13                |

| -       | K1       | -       | M1       | -           | -       | -       | F5                | VDD                                      | S        | -             | -     | -                                                                                                                                                 | -                         |

| -       | J1       | -       | M7       | J8          | -       | -       | C16               | VSS                                      | S        | -             | -     | -                                                                                                                                                 | -                         |

| -       | -        | -       | M3       | G4          | 44      | 47      | P2                | PH3                                      | I/O      | FT_<br>ha     | -     | QUADSPI_BK2_IO1,<br>SAI2_MCK_B,<br>ETH_MII_COL,<br>FMC_SDNE0, LCD_R1,<br>EVENTOUT                                                                 | ADC3_INN13,<br>ADC3_INP14 |

STM32H753xl Pin descriptions

Table 8. STM32H753xl pin/ball definition (continued)

|         |          |         | Pin/ba   | all nam     |         |         |              | •                                        |          |               |       | continuea)                                                                                                        |                         |

|---------|----------|---------|----------|-------------|---------|---------|--------------|------------------------------------------|----------|---------------|-------|-------------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | TFBGA100 | LQFP144 | UFBGA169 | UFBGA176+25 | LQFP176 | LQFP208 | TFBGA240 +25 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                               | Additional<br>functions |

| 97      | D4       | 141     | D5       | A4          | 169     | 200     | C4           | PE0                                      | I/O      | FT_h          | -     | LPTIM1_ETR, TIM4_ETR, HRTIM_SCIN, LPTIM2_ETR, UART8_RX, FDCAN1_RXFD_MODE, SAI2_MCK_A, FMC_NBL0, DCMI_D2, EVENTOUT | -                       |

| 98      | C4       | 142     | D4       | А3          | 170     | 201     | В4           | PE1                                      | I/O      | FT_h          | -     | LPTIM1_IN2, HRTIM_SCOUT, UART8_TX, FDCAN1_TXFD_MODE, FMC_NBL1, DCMI_D3, EVENTOUT                                  | -                       |

| -       | -        | -       | -        | -           | -       | -       | A7           | VCAP                                     | S        | -             | -     | -                                                                                                                 | -                       |

| 99      | -        | -       | -        | D5          | -       | 202     | -            | VSS                                      | S        | -             | -     | -                                                                                                                 | -                       |

| -       | F7       | 143     | C4       | C6          | 171     | 203     | E7           | PDR_ON                                   | S        | -             | -     | -                                                                                                                 | -                       |

| -       | F4       | -       | B4       | -           | -       | -       | A6           | VDDLDO                                   | S        | -             | -     | -                                                                                                                 | -                       |

| 100     | -        | 144     | 1        | C5          | 172     | 204     | -            | VDD                                      | S        | -             | -     | -                                                                                                                 | -                       |

| -       | 1        | 1       | 1        | D4          | 173     | 205     | A4           | Pl4                                      | I/O      | FT_h          | -     | TIM8_BKIN, SAI2_MCK_A, TIM8_BKIN_COMP12, FMC_NBL2, DCMI_D5, LCD_B4, EVENTOUT                                      | ı                       |

| -       | -        | -       | -        | C4          | 174     | 206     | А3           | PI5                                      | I/O      | FT_h          | -     | TIM8_CH1,<br>SAI2_SCK_A,<br>FMC_NBL3,<br>DCMI_VSYNC, LCD_B5,<br>EVENTOUT                                          | -                       |

| -       | -        | -       | A4       | C3          | 175     | 207     | A2           | PI6                                      | I/O      | FT_h          | -     | TIM8_CH2, SAI2_SD_A,<br>FMC_D28, DCMI_D6,<br>LCD_B6, EVENTOUT                                                     | -                       |

| -       | -        | -       | E2       | C2          | 176     | 208     | В3           | PI7                                      | I/O      | FT_h          | -     | TIM8_CH3, SAI2_FS_A,<br>FMC_D29, DCMI_D7,<br>LCD_B7, EVENTOUT                                                     | -                       |

| -       | -        | -       | 1        | Н9          | 1       | -       | 1            | VSS                                      | S        | -             | -     | -                                                                                                                 | -                       |

| -       | -        | -       | -        | K9          | -       | -       | -            | VSS                                      | S        | -             | -     | -                                                                                                                 | -                       |

| -       | -        | -       | •        | K10         | -       | -       | -            | VSS                                      | S        | -             | -     | -                                                                                                                 | -                       |

<sup>1.</sup> When this pin/ball was previously configured as an oscillator, the oscillator function is kept during and after a reset. This is valid for all resets except for power-on reset.

<sup>2.</sup> This ball should remain floating.

DS12117 Rev 5 81/232

### **Table 12. Port D alternate functions**

| Г   |      |         |                                    |                                 |                                                       |                                                          |                            |                                            |                                                |                                                             |                                                                                   |                                                                        |                                                                             |                                                     |                            |               | I I           |

|-----|------|---------|------------------------------------|---------------------------------|-------------------------------------------------------|----------------------------------------------------------|----------------------------|--------------------------------------------|------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------|----------------------------|---------------|---------------|

|     |      | AF0     | AF1                                | AF2                             | AF3                                                   | AF4                                                      | AF5                        | AF6                                        | AF7                                            | AF8                                                         | AF9                                                                               | AF10                                                                   | AF11                                                                        | AF12                                                | AF13                       | AF14          | AF15          |

|     | Port | SYS     | TIM1/2/16/1<br>7/LPTIM1/<br>HRTIM1 | SAI1/TIM3/<br>4/5/12/<br>HRTIM1 | LPUART/<br>TIM8/<br>LPTIM2/3/4<br>/5/HRTIM1/<br>DFSDM | I2C1/2/3/4/<br>USART1/<br>TIM15/<br>LPTIM2/<br>DFSDM/CEC | SPI1/2/3/4/<br>5/6/CEC     | SPI2/3/SAI1<br>/3/I2C4/<br>UART4/<br>DFSDM | SPI2/3/6/<br>USART1/2/<br>3/6/UART7/<br>SDMMC1 | SPI6/SAI2/<br>4/UART4/5/<br>8/LPUART/<br>SDMMC1/<br>SPDIFRX | SAI4/<br>FDCAN1/2/<br>TIM13/14/Q<br>UADSPI/FM<br>C/<br>SDMMC2/<br>LCD/<br>SPDIFRX | SAI2/4/<br>TIM8/<br>QUADSPI/<br>SDMMC2/<br>OTG1_HS/<br>OTG2_FS/<br>LCD | I2C4/<br>UART7/<br>SWPMI1/<br>TIM1/8/<br>DFSDM/<br>SDMMC2/<br>MDIOS/<br>ETH | TIM1/8/FMC<br>/SDMMC1/<br>MDIOS/<br>OTG1_FS/<br>LCD | TIM1/DCMI<br>/LCD/<br>COMP | UART5/<br>LCD | SYS           |

|     | PD0  | -       | =                                  | ·                               | DFSDM_<br>CKIN6                                       | -                                                        | -                          | SAI3_SCK_<br>A                             | -                                              | UART4_RX                                                    | FDCAN1_<br>RX                                                                     | -                                                                      | -                                                                           | FMC_D2/<br>FMC_DA2                                  | -                          | -             | EVENT-<br>OUT |

|     | PD1  | -       | -                                  | 1                               | DFSDM_<br>DATIN6                                      | -                                                        | -                          | SAI3_SD_A                                  | -                                              | UART4_TX                                                    | FDCAN1_<br>TX                                                                     | 1                                                                      | 1                                                                           | FMC_D3/<br>FMC_DA3                                  | -                          | 1             | EVENT-<br>OUT |

|     | PD2  | TRACED2 | -                                  | TIM3_ETR                        | -                                                     | -                                                        | -                          | 1                                          | -                                              | UART5_RX                                                    | -                                                                                 | 1                                                                      | 1                                                                           | SDMMC1_<br>CMD                                      | DCMI_D11                   | 1             | EVENT-<br>OUT |

|     | PD3  | -       | -                                  | -                               | DFSDM_<br>CKOUT                                       | -                                                        | SPI2_SCK/<br>I2S2_CK       | -                                          | USART2_<br>CTS_NSS                             | -                                                           | -                                                                                 | -                                                                      | -                                                                           | FMC_CLK                                             | DCMI_D5                    | LCD_G7        | EVENT-<br>OUT |

|     | PD4  | -       | -                                  | HRTIM_<br>FLT3                  | -                                                     | -                                                        | -                          | SAI3_FS_A                                  | USART2_<br>RTS                                 | -                                                           | FDCAN1_R<br>XFD_MODE                                                              | -                                                                      | -                                                                           | FMC_NOE                                             | -                          | -             | EVENT-<br>OUT |

|     | PD5  | -       | -                                  | HRTIM_<br>EEV3                  | -                                                     | -                                                        | -                          | 1                                          | USART2_<br>TX                                  | -                                                           | FDCAN1_T<br>XFD_MODE                                                              | 1                                                                      | 1                                                                           | FMC_NWE                                             | -                          | 1             | EVENT-<br>OUT |

|     | PD6  | -       | -                                  | SAI1_D1                         | DFSDM_<br>CKIN4                                       | DFSDM_<br>DATIN1                                         | SPI3_<br>MOSI/I2S3<br>_SDO | SAI1_SD_A                                  | USART2_<br>RX                                  | SAI4_SD_<br>A                                               | FDCAN2_R<br>XFD_MODE                                                              | SAI4_D1                                                                | SDMMC2_<br>CK                                                               | FMC_<br>NWAIT                                       | DCMI_D10                   | LCD_B2        | EVENT-<br>OUT |

| Out |      | -       | -                                  | -                               | DFSDM_<br>DATIN4                                      | -                                                        | SPI1_<br>MOSI/I2S1<br>_SDO | DFSDM_CK<br>IN1                            | USART2_<br>CK                                  | -                                                           | SPDIFRX_<br>IN0                                                                   | -                                                                      | SDMMC2_<br>CMD                                                              | FMC_NE1                                             | -                          | 1             | EVENT-<br>OUT |

|     | PD8  | -       | -                                  | 1                               | DFSDM_<br>CKIN3                                       | -                                                        | -                          | SAI3_SCK_<br>B                             | USART3_<br>TX                                  | -                                                           | SPDIFRX_<br>IN1                                                                   | 1                                                                      | 1                                                                           | FMC_D13/<br>FMC_DA13                                | -                          | 1             | EVENT-<br>OUT |

|     | PD9  | -       | -                                  | 1                               | DFSDM_<br>DATIN3                                      | -                                                        | -                          | SAI3_SD_B                                  | USART3_<br>RX                                  | -                                                           | FDCAN2_R<br>XFD_MODE                                                              | 1                                                                      | ı                                                                           | FMC_D14/<br>FMC_DA14                                | -                          | ı             | EVENT-<br>OUT |

|     | PD10 | -       | -                                  | 1                               | DFSDM_<br>CKOUT                                       | -                                                        | -                          | SAI3_FS_B                                  | USART3_<br>CK                                  | -                                                           | FDCAN2_T<br>XFD_MODE                                                              | 1                                                                      | 1                                                                           | FMC_D15/<br>FMC_DA15                                | -                          | LCD_B3        | EVENT-<br>OUT |

|     | PD11 | -       | -                                  | 1                               | LPTIM2_IN 2                                           | I2C4_SMBA                                                | -                          | 1                                          | USART3_<br>CTS_NSS                             | -                                                           | QUADSPI_<br>BK1_IO0                                                               | SAI2_SD_A                                                              | 1                                                                           | FMC_A16                                             | -                          | 1             | EVENT-<br>OUT |

|     | PD12 | -       | LPTIM1_IN1                         | TIM4_CH1                        | LPTIM2_IN<br>1                                        | I2C4_SCL                                                 | -                          | -                                          | USART3_<br>RTS                                 | -                                                           | QUADSPI_<br>BK1_IO1                                                               | SAI2_FS_A                                                              | -                                                                           | FMC_A17                                             | -                          | -             | EVENT-<br>OUT |

|     | PD13 | -       | LPTIM1_<br>OUT                     | TIM4_CH2                        | -                                                     | I2C4_SDA                                                 | -                          | -                                          |                                                | -                                                           | QUADSPI_<br>BK1_IO3                                                               | SAI2_SCK_<br>A                                                         | -                                                                           | FMC_A18                                             | -                          | -             | EVENT-<br>OUT |

|     | PD14 | -       | -                                  | TIM4_CH3                        | -                                                     | -                                                        | -                          | SAI3_MCLK<br>_B                            | -                                              | UART8_<br>CTS                                               | -                                                                                 | -                                                                      | -                                                                           | FMC_D0/<br>FMC_DA0                                  | -                          | -             | EVENT-<br>OUT |

|     | PD15 | -       | -                                  | TIM4_CH4                        | -                                                     | -                                                        | -                          | SAI3_MCLK<br>_A                            | -                                              | UART8_<br>RTS                                               | -                                                                                 | -                                                                      | -                                                                           | FMC_D1/<br>FMC_DA1                                  | -                          | -             | EVENT-<br>OUT |

## 6 Electrical characteristics

### 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

### 6.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of junction temperature, supply voltage and frequencies by tests in production on 100% of the devices with an junction temperature at  $T_J = 25$  °C and  $T_J = T_{Jmax}$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean±3 $\sigma$ ).

### 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_J$  = 25 °C,  $V_{DD}$  = 3.3 V (for the 1.7 V  $\leq$   $V_{DD}$   $\leq$  3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean±2σ).

### 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

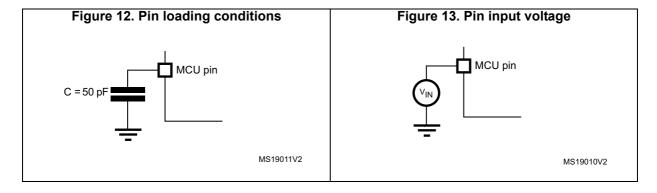

## 6.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in Figure 12.

### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 13*.

DS12117 Rev 5 97/232

**Electrical characteristics** STM32H753xI

| Parameter                 | Conditions                   | Min        | Typ      |  |

|---------------------------|------------------------------|------------|----------|--|

| Table 26. Reset and power | er control block characteris | itics (con | itinued) |  |

| Symbol                 | Parameter                                                       | Conditions      | Min  | Тур  | Max  | Unit |

|------------------------|-----------------------------------------------------------------|-----------------|------|------|------|------|

| V                      | Analog voltage detector for                                     | Rising edge     | 1.66 | 1.71 | 1.76 |      |

| V <sub>AVM_0</sub>     | V <sub>DDA</sub> threshold 0                                    | Falling edge    | 1.56 | 1.61 | 1.66 |      |

| V                      | Analog voltage detector for                                     | Rising edge     | 2.06 | 2.12 | 2.19 |      |

| V <sub>AVM_1</sub>     | V <sub>DDA</sub> threshold 1                                    | Falling edge    | 1.96 | 2.02 | 2.08 | V    |

| V                      | Analog voltage detector for                                     | Rising edge     | 2.42 | 2.50 | 2.58 | V    |

| V <sub>AVM_2</sub>     | V <sub>DDA</sub> threshold 2                                    | Falling edge    | 2.35 | 2.42 | 2.49 |      |

| V                      | Analog voltage detector for                                     | Rising edge     | 2.74 | 2.83 | 2.91 |      |

| V <sub>AVM_3</sub>     | V <sub>DDA</sub> threshold 3                                    | Falling edge    | 2.64 | 2.72 | 2.80 |      |

| V <sub>hyst_VDDA</sub> | Hysteresis of V <sub>DDA</sub> voltage detector                 | -               | -    | 100  | -    | mV   |

| I <sub>DD_PVM</sub>    | PVM consumption from V <sub>DD(1)</sub>                         | -               | -    | -    | 0.25 | μΑ   |

| I <sub>DD_VDDA</sub>   | Voltage detector consumption on V <sub>DDA</sub> <sup>(1)</sup> | Resistor bridge | -    | -    | 2.5  | μΑ   |

<sup>1.</sup> Guaranteed by design.

#### 6.3.5 **Embedded reference voltage**

The parameters given in *Table 27* are derived from tests performed under ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in *Table 23: General operating* conditions.

Table 27. Embedded reference voltage

| Symbol                                | Parameter                                                           | Conditions                                     | Min   | Тур   | Max   | Unit   |

|---------------------------------------|---------------------------------------------------------------------|------------------------------------------------|-------|-------|-------|--------|

| V <sub>REFINT</sub>                   | Internal reference voltages                                         | -40°C < TJ < 105°C,<br>V <sub>DD</sub> = 3.3 V | 1.180 | 1.216 | 1.255 | V      |

| t <sub>S_vrefint</sub> (1)(2)         | ADC sampling time when reading the internal reference voltage       | -                                              | 4.3   | -     | -     | 116    |

| t <sub>S_vbat</sub> <sup>(1)(2)</sup> | VBAT sampling time when reading the internal VBAT reference voltage | -                                              | 9     | -     | -     | μs     |

| I <sub>refbuf</sub> <sup>(2)</sup>    | Reference Buffer consumption for ADC                                | V <sub>DDA</sub> =3.3 V                        | 9     | 13.5  | 23    | μA     |

| ΔV <sub>REFINT</sub> <sup>(2)</sup>   | Internal reference voltage spread over the temperature range        | -40°C < T <sub>J</sub> < 105°C                 | -     | 5     | 15    | mV     |

| T <sub>coeff</sub> <sup>(2)</sup>     | Average temperature coefficient                                     | Average temperature coefficient                | -     | 20    | 70    | ppm/°C |

| V <sub>DDcoeff</sub> <sup>(2)</sup>   | Average Voltage coefficient                                         | 3.0V < V <sub>DD</sub> < 3.6V                  | -     | 10    | 1370  | ppm/V  |

<sup>2.</sup> BOR0 is enabled in all modes and its consumption is therefore included in the supply current characteristics tables (refer to Section 6.3.6: Supply current characteristics).

Table 38. Peripheral current consumption in Run mode (continued)

| D.               | eripheral                             |      | I <sub>DD</sub> (Typ) |      | Unit   |

|------------------|---------------------------------------|------|-----------------------|------|--------|

| Pe               | eripheral                             | VOS1 | VOS2                  | VOS3 | - Unit |

|                  | UART5 registers                       | 1.4  | 1.4                   | 1    |        |

|                  | UART5 kernel                          | 3.6  | 3.2                   | 3.1  |        |

|                  | I2C1 registers                        | 0.8  | 0.8                   | 0.6  |        |

|                  | I2C1 kernel                           | 2    | 1.8                   | 1.7  |        |

|                  | I2C2 registers                        | 0.7  | 0.7                   | 0.4  |        |

|                  | I2C2 kernel                           | 1.9  | 1.7                   | 1.6  |        |

|                  | I2C3 registers                        | 0.9  | 0.7                   | 0.6  |        |

|                  | I2C3 kernel                           | 2.1  | 1.9                   | 1.9  |        |

|                  | HDMI-CEC registers                    | 0.5  | 0.3                   | 0.3  |        |

|                  | DAC1/2 USART7 registers USART7 kernel | 1.4  | 1.1                   | 0.9  |        |

| APB1 (continued) |                                       | 1.9  | 1.8                   | 1.3  | μΑ/MHz |

| (continueu)      |                                       | 4    | 3.5                   | 3.3  |        |

|                  | USART8 registers                      | 1.6  | 1.5                   | 1.2  |        |

|                  | USART8 kernel                         | 4    | 3.6                   | 3.3  |        |

|                  | CRS                                   | 3.4  | 3.1                   | 2.9  |        |

|                  | SWPMI registers                       | 2.3  | 2                     | 2    |        |

|                  | SWPMI kernel                          | 0.1  | 0.1                   | 0.1  |        |

|                  | OPAMP                                 | 0.5  | 0.4                   | 0.4  |        |

|                  | MDIO                                  | 2.7  | 2.4                   | 2.3  | 1      |

|                  | FDCAN registers                       | 16   | 15                    | 14   |        |

|                  | FDCAN kernel                          | 7.8  | 7.6                   | 7.1  |        |

|                  | Bridge APB1                           | 0.1  | 0.1                   | 0.1  |        |

### Output buffer timing characteristics (HSLV option enabled)

Table 62. Output timing characteristics (HSLV ON)<sup>(1)</sup>

| Speed | Symbol                          | Parameter                | conditions                                            | Min | Max | Unit |

|-------|---------------------------------|--------------------------|-------------------------------------------------------|-----|-----|------|

|       |                                 |                          | C=50 pF, 1.62 V≤V <sub>DD</sub> ≤2.7 V                | -   | 10  |      |

|       | F <sub>max</sub> <sup>(2)</sup> | Maximum frequency        | C=30 pF, 1.62 V≤V <sub>DD</sub> ≤2.7 V                | -   | 10  | MHz  |

| 00    |                                 |                          | C=10 pF, 1.62 V≤V <sub>DD</sub> ≤2.7 V                | -   | 10  |      |

| 00    |                                 | Output high to low level | C=50 pF, 1.62 V≤V <sub>DD</sub> ≤2.7 V                | -   | 11  |      |

|       | $t_r/t_f^{(3)}$                 | fall time and output low | C=30 pF, 1.62 V≤V <sub>DD</sub> ≤2.7 V                | -   | 9   | ns   |

|       |                                 | to high level rise time  | C=10 pF, 1.62 V≤V <sub>DD</sub> ≤2.7 V                | -   | 6.6 |      |

|       |                                 |                          | C=50 pF, 1.62 V≤V <sub>DD</sub> ≤2.7 V                | -   | 50  |      |

|       | F <sub>max</sub> <sup>(2)</sup> | Maximum frequency        | C=30 pF, 1.62 V≤V <sub>DD</sub> ≤2.7 V                | -   | 58  | MHz  |

| 01    |                                 |                          | C=10 pF, 1.62 V≤V <sub>DD</sub> ≤2.7 V                | -   | 66  |      |

| 01    |                                 | Output high to low level | C=50 pF, 1.62 V≤V <sub>DD</sub> ≤2.7 V                | -   | 6.6 |      |

|       | $t_r/t_f^{(3)}$                 | fall time and output low | C=30 pF, 1.62 V≤V <sub>DD</sub> ≤2.7 V                | -   | 4.8 | ns   |

|       |                                 | to high level rise time  | C=10 pF, 1.62 V≤V <sub>DD</sub> ≤2.7 V                | -   | 3   |      |

|       |                                 |                          | C=50 pF, 1.62 V≤V <sub>DD</sub> ≤2.7 V <sup>(4)</sup> | -   | 55  |      |

|       | F <sub>max</sub> <sup>(2)</sup> | Maximum frequency        | C=30 pF, 1.62 V≤V <sub>DD</sub> ≤2.7 V <sup>(4)</sup> | -   | 80  | MHz  |

| 10    |                                 |                          | C=10 pF, 1.62 V≤V <sub>DD</sub> ≤2.7 V <sup>(4)</sup> | -   | 133 |      |

| 10    |                                 | Output high to low level | C=50 pF, 1.62 V≤V <sub>DD</sub> ≤2.7 V <sup>(4)</sup> | -   | 5.8 |      |

|       | $t_r/t_f^{(3)}$                 | fall time and output low | C=30 pF, 1.62 V≤V <sub>DD</sub> ≤2.7 V <sup>(4)</sup> | -   | 4   | ns   |

|       |                                 | to high level rise time  | C=10 pF, 1.62 V≤V <sub>DD</sub> ≤2.7 V <sup>(4)</sup> | -   | 2.4 |      |

|       |                                 |                          | C=50 pF, 1.62 V≤V <sub>DD</sub> ≤2.7 V <sup>(4)</sup> | -   | 60  |      |

|       | F <sub>max</sub> <sup>(2)</sup> | Maximum frequency        | C=30 pF, 1.62 V≤V <sub>DD</sub> ≤2.7 V <sup>(4)</sup> | -   | 90  | MHz  |

| 11    |                                 |                          | C=10 pF, 1.62 V≤V <sub>DD</sub> ≤2.7 V <sup>(4)</sup> | -   | 175 |      |

| ''    |                                 | Output high to low level | C=50 pF, 1.62 V≤V <sub>DD</sub> ≤2.7 V <sup>(4)</sup> | -   | 5.3 |      |

|       | $t_r/t_f^{(3)}$                 | fall time and output low | C=30 pF, 1.62 V≤V <sub>DD</sub> ≤2.7 V <sup>(4)</sup> | -   | 3.6 | ns   |

|       |                                 | to high level rise time  | C=10 pF, 1.62 V≤V <sub>DD</sub> ≤2.7 V <sup>(4)</sup> | -   | 1.9 |      |

<sup>1.</sup> Guaranteed by design.

- 3. The fall and rise times are defined between 90% and 10% and between 10% and 90% of the output waveform, respectively.

- 4. Compensation system enabled.

<sup>2.</sup> The maximum frequency is defined with the following conditions:  $(t_r + t_f) \le 2/3$  T Skew  $\le 1/20$  T 45%<Duty cycle<55%

Electrical characteristics STM32H753xl

Table 87. DAC characteristics<sup>(1)</sup> (continued)

| Symbol                 | Parameter                              | Cond                     | itions                                   | Min | Тур                                                           | Max | Unit |

|------------------------|----------------------------------------|--------------------------|------------------------------------------|-----|---------------------------------------------------------------|-----|------|

|                        |                                        | DAC output               | No load, middle code (0x800)             | -   | 360                                                           | -   |      |

|                        | DAC quiescent                          | buffer ON                | No load, worst code (0xF1C)              | ı   | 490                                                           | -   |      |

| I <sub>DDA(DAC)</sub>  | consumption from V <sub>DDA</sub>      | DAC output<br>buffer OFF | No load,<br>middle/worst<br>code (0x800) | -   | 20                                                            | -   |      |

|                        |                                        |                          | Hold mode,<br>100 nF                     | -   | 360*T <sub>ON</sub> /<br>(T <sub>ON</sub> +T <sub>OFF</sub> ) | -   |      |

|                        |                                        | DAC output               | No load, middle code (0x800)             | -   | 170                                                           | -   | μΑ   |

|                        |                                        | buffer ON                | No load, worst code (0xF1C)              | -   | 170                                                           | -   |      |

| I <sub>DDV</sub> (DAC) | DAC consumption from V <sub>REF+</sub> | DAC output<br>buffer OFF | No load,<br>middle/worst<br>code (0x800) | -   | 160                                                           | -   |      |

|                        |                                        |                          | old mode, Buffer<br>nF (worst code)      | ı   | 170*T <sub>ON</sub> /<br>(T <sub>ON</sub> +T <sub>OFF</sub> ) | -   |      |

|                        |                                        |                          | old mode, Buffer<br>nF (worst code)      | -   | 160*T <sub>ON</sub> /<br>(T <sub>ON</sub> +T <sub>OFF</sub> ) | -   |      |

- 1. Guaranteed by characterization results.

- 2. Guaranteed by design.

- 3. In buffered mode, the output can overshoot above the final value for low input code (starting from the minimum value).

Table 88. DAC accuracy<sup>(1)</sup>

| Symbol  | Parameter                                 | Conditions                                           |                                                          | Min | Тур | Max | Unit |

|---------|-------------------------------------------|------------------------------------------------------|----------------------------------------------------------|-----|-----|-----|------|

| DNL     | Differential non                          | DAC output buffer ON                                 |                                                          | -   | ±2  | -   | LSB  |

| DINL    | linearity <sup>(2)</sup>                  | DAC output buffer OFF                                |                                                          | -   | ±2  | -   | LOD  |

| INL     | Integral non linearity <sup>(3)</sup>     |                                                      | DAC output buffer ON, $C_L \le 50$ pF,<br>$R_L \ge 5$ kΩ |     | ±4  | -   | LSB  |

| IINL    | integral non lineality (**)               |                                                      | buffer OFF,<br>pF, no R <sub>L</sub>                     | -   | ±4  | -   | LOD  |

|         |                                           | DAC output buffer ON,                                | V <sub>REF+</sub> = 3.6 V                                | -   | -   | ±12 |      |

| Offset  | Offset error at code 0x800 (3)            | $C_L \le 50 \text{ pF},$ $R_L \ge 5 \text{ k}\Omega$ | V <sub>REF+</sub> = 1.8 V                                | -   | -   | ±25 | LSB  |

|         |                                           |                                                      | buffer OFF,<br>pF, no R <sub>L</sub>                     | -   | -   | ±8  |      |

| Offset1 | Offset error at code 0x001 <sup>(4)</sup> |                                                      | buffer OFF,<br>pF, no R <sub>L</sub>                     | -   | -   | ±5  | LSB  |

Table 96. OPAMP characteristics<sup>(1)</sup> (continued)

| Symbol               | Parameter                                                                 | Conditions                                                                                     |                                                                                         | Min                         | Тур    | Max | Unit      |

|----------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------|--------|-----|-----------|

| V <sub>OHSAT</sub>   | High saturation voltage                                                   | I <sub>load</sub> =max or R <sub>LOAD</sub> =min <sup>(2)</sup> ,<br>Input at V <sub>DDA</sub> |                                                                                         | V <sub>DDA</sub><br>−100 mV | -      | -   | mV        |

| V <sub>OLSAT</sub>   | Low saturation voltage                                                    | I <sub>load</sub> =max or R <sub>LOAD</sub> =min <sup>(2)</sup> ,<br>Input at 0 V              |                                                                                         | -                           | -      | 100 |           |

| t <sub>WAKEUP</sub>  | Wake up time from OFF                                                     | Normal<br>mode                                                                                 | $C_{LOAD} \le 50 pf$ ,<br>$R_{LOAD} \ge 4 k\Omega^{(2)}$ ,<br>follower<br>configuration | -                           | 0.8    | 3.2 | - µs      |

|                      | state                                                                     | High<br>speed                                                                                  | $C_{LOAD} \le 50 pf$ ,<br>$R_{LOAD} \ge 4 k\Omega^{(2)}$ ,<br>follower<br>configuration | -                           | 0.9    | 2.8 |           |

|                      |                                                                           | -                                                                                              |                                                                                         | -                           | 2      | -   | -         |

|                      | Non inverting gain value                                                  | -                                                                                              |                                                                                         | -                           | 4      | -   | -         |

|                      | Non inverting gain value                                                  | -                                                                                              |                                                                                         | -                           | 8      | -   | -         |

| PGA gain             |                                                                           | -                                                                                              |                                                                                         | -                           | 16     | -   | -         |

| 1 O/t gain           | Inverting gain value                                                      | -                                                                                              |                                                                                         | -                           | -1     | -   | -         |

|                      |                                                                           | -                                                                                              |                                                                                         | -                           | -3     | -   | -         |

|                      |                                                                           | -                                                                                              |                                                                                         | -                           | -7     | -   | -         |

|                      |                                                                           | -                                                                                              |                                                                                         | -                           | -15    | -   | -         |

|                      | R2/R1 internal resistance values in non-inverting PGA mode <sup>(3)</sup> | PGA Gain=2                                                                                     |                                                                                         | -                           | 10/10  | -   | kΩ/<br>kΩ |

|                      |                                                                           | PGA Gain=4                                                                                     |                                                                                         | -                           | 30/10  | -   |           |

| R <sub>network</sub> |                                                                           | PGA Gain=8                                                                                     |                                                                                         | -                           | 70/10  | -   |           |

|                      |                                                                           | PGA Gain=16                                                                                    |                                                                                         | -                           | 150/10 | -   |           |

|                      | R2/R1 internal resistance values in inverting PGA mode <sup>(3)</sup>     | PGA Gain=-1                                                                                    |                                                                                         | -                           | 10/10  | -   |           |

|                      |                                                                           | PGA Gain=-3                                                                                    |                                                                                         | -                           | 30/10  | _   |           |

|                      |                                                                           | PGA Gain=-7                                                                                    |                                                                                         | _                           | 70/10  |     |           |

|                      |                                                                           | PGA Gain=-15                                                                                   |                                                                                         | -                           | 150/10 | -   |           |

| Delta R              | Resistance variation (R1 or R2)                                           | -                                                                                              |                                                                                         | -15                         | -      | 15  | %         |

| PGA BW               |                                                                           | Gain=2                                                                                         |                                                                                         | -                           | GBW/2  | -   | - MHz     |

|                      | PGA bandwidth for different non inverting gain                            | Gain=4                                                                                         |                                                                                         | -                           | GBW/4  | -   |           |

|                      |                                                                           | Gain=8                                                                                         |                                                                                         | -                           | GBW/8  | -   |           |

|                      |                                                                           | Gain=16                                                                                        |                                                                                         | -                           | GBW/16 | -   |           |

Electrical characteristics STM32H753xl

Table 97. DFSDM measured timing 1.62-3.6 V<sup>(1)</sup> (continued)

| Symbol                  | Parameter                                       | Conditions                                                                                                         | Min                                   | Тур                  | Max                                     | Unit |

|-------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------|-----------------------------------------|------|

| t <sub>wh(CKIN)</sub>   | Input clock high and low time                   | SPI mode (SITP[1:0]=0,1),<br>External clock mode<br>(SPICKSEL[1:0]=0),<br>1.62 < V <sub>DD</sub> < 3.6 V           | TCKIN/2 - 0.5                         | T <sub>CKIN</sub> /2 | -                                       |      |

| t <sub>su</sub>         | Data input setup<br>time                        | SPI mode (SITP[1:0]=0,1),<br>External clock mode<br>(SPICKSEL[1:0]=0),<br>1.62 < V <sub>DD</sub> < 3.6 V           | 4                                     | -                    | -                                       |      |

| t <sub>h</sub>          | Data input hold time                            | SPI mode (SITP[1:0]=0,1),<br>External clock mode<br>(SPICKSEL[1:0]=0),<br>1.62 < V <sub>DD</sub> < 3.6 V           | 0.5                                   | -                    | -                                       | ns   |

| T <sub>Manchester</sub> | Manchester data period (recovered clock period) | Manchester mode<br>(SITP[1:0]=2,3),<br>Internal clock mode<br>(SPICKSEL[1:0]≠0),<br>1.62 < V <sub>DD</sub> < 3.6 V | (CKOUTDIV+1)  * T <sub>DFSDMCLK</sub> | -                    | (2*CKOUTDIV)<br>* T <sub>DFSDMCLK</sub> |      |

<sup>1.</sup> Guaranteed by characterization results.

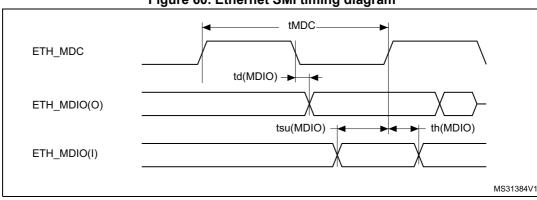

Figure 60. Ethernet SMI timing diagram

Table 112 gives the list of Ethernet MAC signals for the RMII and Figure 61 shows the corresponding timing diagram.

Table 112. Dynamics characteristics: Ethernet MAC signals for RMII<sup>(1)</sup>

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                        |                      |                                  |     |     |      |      |

|------------------------------------------------------------------------------------------------|----------------------|----------------------------------|-----|-----|------|------|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                          | Symbol               | Parameter                        | Min | Тур | Max  | Unit |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                          | t <sub>su(RXD)</sub> | Receive data setup time          | 2   | -   | -    |      |

| $t_{ih(CRS)}$ Carrier sense hold time 2 $t_{d(TXEN)}$ Transmit enable valid delay time 4 4.5 7 | t <sub>ih(RXD)</sub> | Receive data hold time           | 3   | -   | -    |      |

| $t_{ih(CRS)}$ Carrier sense hold time 2 $t_{d(TXEN)}$ Transmit enable valid delay time 4 4.5 7 | t <sub>su(CRS)</sub> | Carrier sense setup time         | 2.5 | -   | -    | 20   |

| Transport data valid dalay time                                                                | t <sub>ih(CRS)</sub> | Carrier sense hold time          | 2   | -   | -    | 115  |

| t <sub>d(TXD)</sub> Transmit data valid delay time 7 7.5 11.5                                  | t <sub>d(TXEN)</sub> | Transmit enable valid delay time | 4   | 4.5 | 7    |      |

|                                                                                                | t <sub>d(TXD)</sub>  | Transmit data valid delay time   | 7   | 7.5 | 11.5 |      |

<sup>1.</sup> Guaranteed by characterization results.

RMII\_REF\_CLK  $t_{d(TXEN)}$ t<sub>d</sub>(TXD) RMII TX EN RMII\_TXD[1:0] t<sub>su(RXD)</sub> tih(RXD) t<sub>su(CRS)</sub> tih(CRS) RMII\_RXD[1:0] RMII\_CRS\_DV ai15667b

Figure 61. Ethernet RMII timing diagram

Table 113 gives the list of Ethernet MAC signals for MII and Figure 62 shows the corresponding timing diagram.

Package information STM32H753xI

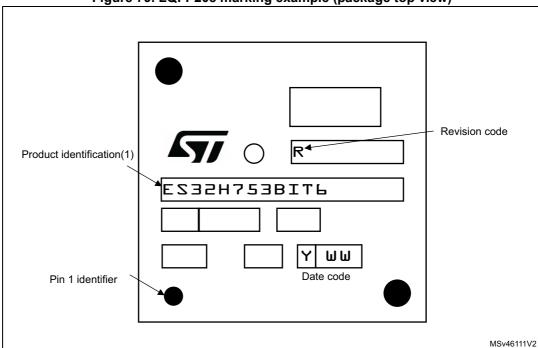

### **Device marking for LQFP208**

The following figure gives an example of topside marking versus pin 1 position identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Figure 79. LQFP208 marking example (package top view)

<sup>1.</sup> Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's Quality department must be contacted prior to any decision to use these engineering samples to run a qualification activity.