Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 72MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB            |

| Peripherals                | DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT            |

| Number of I/O              | 51                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | - ·                                                                     |

| RAM Size                   | 48K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f103rct6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 8 | Revi | sion his | tory                                    |

|---|------|----------|-----------------------------------------|

| 7 | Part | number   | ing                                     |

|   |      | 6.7.2    | Selecting the product temperature range |

|   |      | 6.7.1    | Reference document                      |

|   | 6.7  | Therma   | al characteristics                      |

|   | 6.6  | LQFP6    | 4 package information 130               |

|   | 6.5  | LQFP1    | 00 package information                  |

|   | 6.4  | LQFP1    | 44 package information                  |

|   | 6.3  | WLCS     | P64 package information 121             |

|   | 6.2  | LFBGA    | 100 package information 118             |

|   | 6.1  | LFBGA    | 144 package information 115             |

| 6 | Pack | age info | ormation                                |

|   |      | 5.3.21   | Temperature sensor characteristics      |

|   |      | 5.3.20   | DAC electrical specifications           |

## 2.3 Overview

# 2.3.1 ARM<sup>®</sup> Cortex<sup>®</sup>-M3 core with embedded Flash and SRAM

The ARM Cortex<sup>®</sup>-M3 processor is the latest generation of ARM processors for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM Cortex<sup>®</sup>-M3 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

With its embedded ARM core, STM32F103xC, STM32F103xD and STM32F103xE performance line family is compatible with all ARM tools and software.

*Figure 1* shows the general block diagram of the device family.

### 2.3.2 Embedded Flash memory

Up to 512 Kbytes of embedded Flash is available for storing programs and data.

#### 2.3.3 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

#### 2.3.4 Embedded SRAM

Up to 64 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states.

#### 2.3.5 FSMC (flexible static memory controller)

The FSMC is embedded in the STM32F103xC, STM32F103xD and STM32F103xE performance line family. It has four Chip Select outputs supporting the following modes: PC Card/Compact Flash, SRAM, PSRAM, NOR and NAND.

Functionality overview:

- The three FSMC interrupt lines are ORed in order to be connected to the NVIC

- Write FIFO

- Code execution from external memory except for NAND Flash and PC Card

- The targeted frequency, f<sub>CLK</sub>, is HCLK/2, so external access is at 36 MHz when HCLK is at 72 MHz and external access is at 24 MHz when HCLK is at 48 MHz

#### 2.3.10 Boot modes

At startup, boot pins are used to select one of three boot options:

- Boot from user Flash: you have an option to boot from any of two memory banks. By default, boot from Flash memory bank 1 is selected. You can choose to boot from Flash memory bank 2 by setting a bit in the option bytes.

- Boot from system memory

- Boot from embedded SRAM

The boot loader is located in system memory. It is used to reprogram the Flash memory by using USART1.

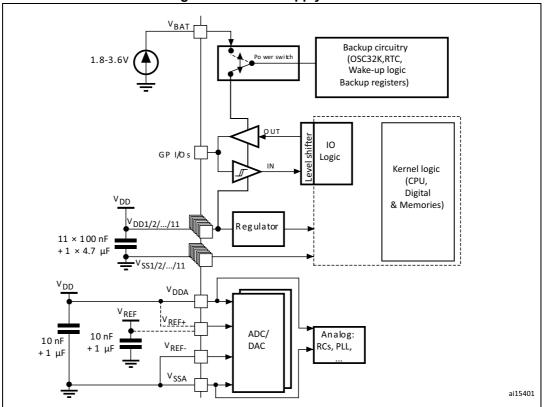

#### 2.3.11 **Power supply schemes**

- $V_{DD}$  = 2.0 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through V<sub>DD</sub> pins.

- $V_{SSA}$ ,  $V_{DDA} = 2.0$  to 3.6 V: external analog power supplies for ADC, DAC, Reset blocks, RCs and PLL (minimum voltage to be applied to VDDA is 2.4 V when the ADC or DAC is used).  $V_{DDA}$  and  $V_{SSA}$  must be connected to  $V_{DD}$  and  $V_{SS}$ , respectively.

- V<sub>BAT</sub> = 1.8 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

For more details on how to connect power pins, refer to *Figure 12: Power supply scheme*.

#### 2.3.12 Power supply supervisor

The device has an integrated power-on reset (POR)/power-down reset (PDR) circuitry. It is always active, and ensures proper operation starting from/down to 2 V. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$ , without the need for an external reset circuit.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software. Refer to *Table 12: Embedded reset and power control block characteristics* for the values of  $V_{POR/PDR}$  and  $V_{PVD}$ .

#### 2.3.13 Voltage regulator

The regulator has three operation modes: main (MR), low-power (LPR) and power down.

- MR is used in the nominal regulation mode (Run)

- LPR is used in the Stop modes.

- Power down is used in Standby mode: the regulator output is in high impedance: the kernel circuitry is powered down, inducing zero consumption (but the contents of the registers and SRAM are lost)

This regulator is always enabled after reset. It is disabled in Standby mode.

|          |          | Pir     | IS     |         |         |                                    |                     |                            |                                                  | Alternate funct     | tions <sup>(4)</sup> |

|----------|----------|---------|--------|---------|---------|------------------------------------|---------------------|----------------------------|--------------------------------------------------|---------------------|----------------------|

| LFBGA144 | LFBGA100 | WLCSP64 | LQFP64 | LQFP100 | LQFP144 | Pin name                           | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default             | Remap                |

| A3       | A3       | -       | -      | 1       | 1       | PE2                                | I/O                 | FT                         | PE2                                              | TRACECK/ FSMC_A23   | -                    |

| A2       | B3       | -       | -      | 2       | 2       | PE3                                | I/O                 | FT                         | PE3                                              | TRACED0/FSMC_A19    | -                    |

| B2       | C3       | -       | -      | 3       | 3       | PE4                                | I/O                 | FT                         | PE4                                              | TRACED1/FSMC_A20    | -                    |

| B3       | D3       | -       | -      | 4       | 4       | PE5                                | I/O                 | FT                         | PE5                                              | TRACED2/FSMC_A21    | -                    |

| B4       | E3       | -       | -      | 5       | 5       | PE6                                | I/O                 | FT                         | PE6                                              | TRACED3/FSMC_A22    | -                    |

| C2       | B2       | C6      | 1      | 6       | 6       | V <sub>BAT</sub>                   | S                   | -                          | V <sub>BAT</sub>                                 | -                   | -                    |

| A1       | A2       | C8      | 2      | 7       | 7       | PC13-TAMPER-<br>RTC <sup>(5)</sup> | I/O                 | -                          | PC13 <sup>(6)</sup>                              | TAMPER-RTC          | -                    |

| B1       | A1       | B8      | 3      | 8       | 8       | PC14-<br>OSC32_IN <sup>(5)</sup>   | I/O                 | -                          | PC14 <sup>(6)</sup>                              | OSC32_IN            | -                    |

| C1       | B1       | B7      | 4      | 9       | 9       | PC15-<br>OSC32_OUT <sup>(5)</sup>  | I/O                 | -                          | PC15 <sup>(6)</sup>                              | OSC32_OUT           | -                    |

| C3       | -        | -       | -      | -       | 10      | PF0                                | I/O                 | FT                         | PF0                                              | FSMC_A0             | -                    |

| C4       | -        | -       | -      | -       | 11      | PF1                                | I/O                 | FT                         | PF1                                              | FSMC_A1             | -                    |

| D4       | -        | -       | -      | -       | 12      | PF2                                | I/O                 | FT                         | PF2                                              | FSMC_A2             | -                    |

| E2       | -        | -       | -      | -       | 13      | PF3                                | I/O                 | FT                         | PF3                                              | FSMC_A3             | -                    |

| E3       | -        | -       | -      | -       | 14      | PF4                                | I/O                 | FT                         | PF4                                              | FSMC_A4             | -                    |

| E4       | -        | -       | -      | -       | 15      | PF5                                | I/O                 | FT                         | PF5                                              | FSMC_A5             | -                    |

| D2       | C2       | -       | -      | 10      | 16      | V <sub>SS_5</sub>                  | S                   | -                          | V <sub>SS_5</sub>                                | -                   | -                    |

| D3       | D2       | -       | -      | 11      | 17      | $V_{DD_5}$                         | S                   | -                          | V <sub>DD_5</sub>                                | -                   | -                    |

| F3       | -        | -       | -      | -       | 18      | PF6                                | I/O                 | -                          | PF6                                              | ADC3_IN4/FSMC_NIORD | -                    |

| F2       | -        | -       | -      | -       | 19      | PF7                                | I/O                 | -                          | PF7                                              | ADC3_IN5/FSMC_NREG  | -                    |

| G3       | -        | -       | -      | -       | 20      | PF8                                | I/O                 | -                          | PF8                                              | ADC3_IN6/FSMC_NIOWR | -                    |

| G2       | -        | -       | -      | -       | 21      | PF9                                | I/O                 | -                          | PF9                                              | ADC3_IN7/FSMC_CD    | -                    |

| G1       | -        | -       | -      | -       | 22      | PF10                               | I/O                 | -                          | PF10                                             | ADC3_IN8/FSMC_INTR  | -                    |

| D1       | C1       | D8      | 5      | 12      | 23      | OSC_IN                             | Ι                   | -                          | OSC_IN                                           | -                   | -                    |

| E1       | D1       | D7      | 6      | 13      | 24      | OSC_OUT                            | 0                   | -                          | OSC_OUT                                          | -                   | -                    |

| F1       | E1       | C7      | 7      | 14      | 25      | NRST                               | I/O                 | -                          | NRST                                             | -                   | -                    |

| H1       | F1       | E8      | 8      | 15      | 26      | PC0                                | I/O                 | -                          | PC0                                              | ADC123_IN10         | _                    |

| H2       | F2       | F8      | 9      | 16      | 27      | PC1                                | I/O                 | -                          | PC1                                              | ADC123_IN11         | -                    |

Table 5. High-density STM32F103xC/D/E pin definitions

|          |          | Pir     |        |         |         |                   |                     |                            | · · ·                                            | Alternate functions <sup>(4)</sup>             |           |

|----------|----------|---------|--------|---------|---------|-------------------|---------------------|----------------------------|--------------------------------------------------|------------------------------------------------|-----------|

| LFBGA144 | LFBGA100 | WLCSP64 | LQFP64 | LQFP100 | LQFP144 | Pin name          | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                        | Remap     |

| L4       | J4       | H4      | 26     | 35      | 46      | PB0               | I/O                 | -                          | PB0                                              | ADC12_IN8/TIM3_CH3<br>TIM8_CH2N                | TIM1_CH2N |

| M4       | K4       | F4      | 27     | 36      | 47      | PB1               | I/O                 | -                          | PB1                                              | ADC12_IN9/TIM3_CH4 <sup>(9)</sup><br>TIM8_CH3N | TIM1_CH3N |

| J5       | G5       | H3      | 28     | 37      | 48      | PB2               | I/O                 | FT                         | PB2/BOOT1                                        | -                                              | -         |

| M5       | -        | -       | -      | -       | 49      | PF11              | I/O                 | FT                         | PF11                                             | FSMC_NIOS16                                    | -         |

| L5       | -        | -       | I      | -       | 50      | PF12              | I/O                 | FT                         | PF12                                             | FSMC_A6                                        | -         |

| H5       | -        | -       | I      | -       | 51      | $V_{SS_6}$        | S                   | -                          | $V_{SS_6}$                                       | -                                              | -         |

| G5       | -        | -       | -      | -       | 52      | $V_{DD_6}$        | S                   | -                          | $V_{DD_6}$                                       | V <sub>DD_6</sub> -                            |           |

| K5       | -        | -       | I      | -       | 53      | PF13              | I/O                 | FT                         | PF13 FSMC_A7                                     |                                                | -         |

| M6       | -        | -       | I      | -       | 54      | PF14              | I/O                 | FT                         | PF14                                             | FSMC_A8                                        | -         |

| L6       | -        | -       | -      | -       | 55      | PF15              | I/O                 | FT                         | PF15                                             | FSMC_A9                                        | -         |

| K6       | -        | -       | -      | -       | 56      | PG0               | I/O                 | FT                         | PG0                                              | FSMC_A10                                       | -         |

| J6       | -        | -       | -      | -       | 57      | PG1               | I/O                 | FT                         | PG1                                              | FSMC_A11                                       | -         |

| M7       | H5       | -       | -      | 38      | 58      | PE7               | I/O                 | FT                         | PE7                                              | FSMC_D4                                        | TIM1_ETR  |

| L7       | J5       | -       | -      | 39      | 59      | PE8               | I/O                 | FT                         | PE8                                              | FSMC_D5                                        | TIM1_CH1N |

| K7       | K5       | -       | -      | 40      | 60      | PE9               | I/O                 | FT                         | PE9                                              | FSMC_D6                                        | TIM1_CH1  |

| H6       | -        | -       | -      | -       | 61      | V <sub>SS_7</sub> | S                   | -                          | V <sub>SS_7</sub>                                | -                                              | -         |

| G6       | -        | -       | -      | -       | 62      | V <sub>DD_7</sub> | S                   | -                          | V <sub>DD_7</sub>                                | -                                              | -         |

| J7       | G6       | -       | -      | 41      | 63      | PE10              | I/O                 | FT                         | PE10                                             | FSMC_D7                                        | TIM1_CH2N |

| H8       | H6       | -       | -      | 42      | 64      | PE11              | I/O                 | FT                         | PE11                                             | FSMC_D8                                        | TIM1_CH2  |

| J8       | J6       | -       | -      | 43      | 65      | PE12              | I/O                 | FT                         | PE12                                             | FSMC_D9                                        | TIM1_CH3N |

| K8       | K6       | -       | -      | 44      | 66      | PE13              | I/O                 | FT                         | PE13                                             | FSMC_D10                                       | TIM1_CH3  |

| L8       | G7       | -       | -      | 45      | 67      | PE14              | I/O                 | FT                         | PE14                                             | FSMC_D11                                       | TIM1_CH4  |

| M8       | H7       | -       | -      | 46      | 68      | PE15              | I/O                 | FT                         | PE15                                             | FSMC_D12                                       | TIM1_BKIN |

| M9       | J7       | G3      | 29     | 47      | 69      | PB10              | I/O                 | FT                         | PB10                                             | I2C2_SCL/USART3_TX <sup>(9)</sup>              | TIM2_CH3  |

| M10      | K7       | F3      | 30     | 48      | 70      | PB11              | I/O                 | FT                         | PB11                                             | I2C2_SDA/USART3_RX <sup>(9)</sup>              | TIM2_CH4  |

| H7       | E7       | H2      | 31     | 49      | 71      | V <sub>SS_1</sub> | S                   | -                          | V <sub>SS_1</sub>                                | -                                              | -         |

| G7       | F7       | H1      | 32     | 50      | 72      | $V_{DD_1}$        | S                   | -                          | V <sub>DD_1</sub>                                | -                                              | -         |

Table 5. High-density STM32F103xC/D/E pin definitions (continued)

# 5 Electrical characteristics

## 5.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

#### 5.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

#### 5.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 3.3$  V (for the 2 V  $\leq V_{DD} \leq 3.6$  V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\Sigma$ ).

#### 5.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

#### 5.1.4 Loading capacitor

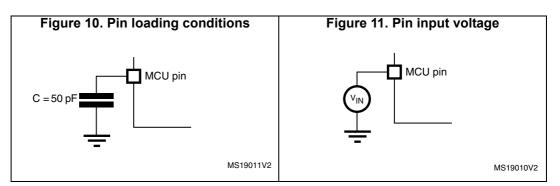

The loading conditions used for pin parameter measurement are shown in *Figure 10*.

#### 5.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 11*.

## 5.1.6 Power supply scheme

Figure 12. Power supply scheme

Caution: In Figure 12, the 4.7 µF capacitor must be connected to V<sub>DD3</sub>.

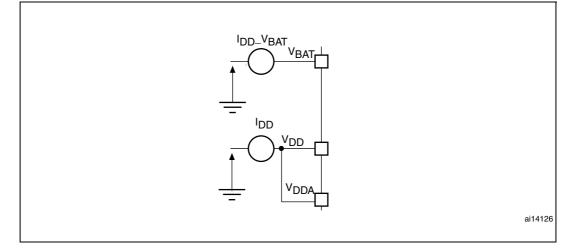

#### 5.1.7 Current consumption measurement

#### Figure 13. Current consumption measurement scheme

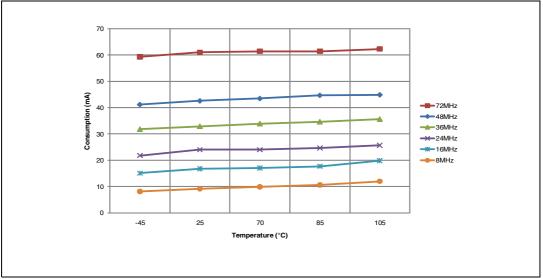

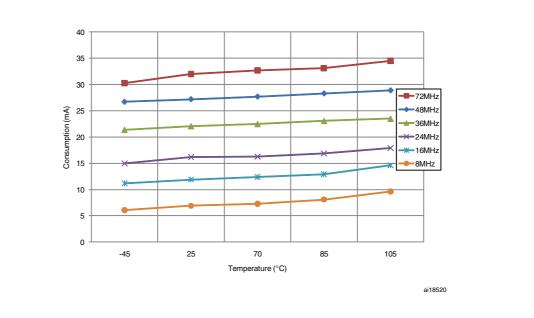

Figure 14. Typical current consumption in Run mode versus frequency (at 3.6 V) - code with data processing running from RAM, peripherals enabled

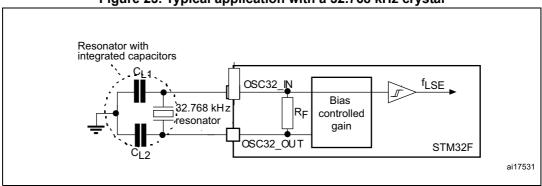

Figure 23. Typical application with a 32.768 kHz crystal

### 5.3.7 Internal clock source characteristics

The parameters given in *Table 25* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 10*.

#### High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                        | Co                                   | Min                            | Тур  | Max | Unit             |     |

|-------------------------------------|----------------------------------|--------------------------------------|--------------------------------|------|-----|------------------|-----|

| f <sub>HSI</sub>                    | Frequency                        | -                                    |                                | -    | 8   | -                | MHz |

| DuCy <sub>(HSI)</sub>               | Duty cycle                       | -                                    |                                | 45   | -   | 55               | %   |

|                                     |                                  | User-trimmed register <sup>(2)</sup> | with the RCC_CR                | -    | -   | 1 <sup>(3)</sup> | %   |

|                                     | Accuracy of the HSI              |                                      | T <sub>A</sub> = -40 to 105 °C | -2   | -   | 2.5              | %   |

| ACC <sub>HSI</sub>                  | oscillator                       | Factory-                             | T <sub>A</sub> = −10 to 85 °C  | -1.5 | -   | 2.2              | %   |

|                                     |                                  | calibrated <sup>(4)</sup>            | T <sub>A</sub> = 0 to 70 °C    | -1.3 | -   | 2                | %   |

|                                     |                                  |                                      | T <sub>A</sub> = 25 °C         | -1.1 | -   | 1.8              | %   |

| t <sub>su(HSI)</sub> <sup>(4)</sup> | HSI oscillator<br>startup time   | -                                    |                                | 1    | -   | 2                | μs  |

| I <sub>DD(HSI)</sub> <sup>(4)</sup> | HSI oscillator power consumption | -                                    | -                              | 80   | 100 | μA               |     |

Table 25. HSI oscillator characteristics<sup>(1)</sup>

1.  $V_{DD}$  = 3.3 V,  $T_A$  = –40 to 105  $^\circ C$  unless otherwise specified.

Refer to application note AN2868 "STM32F10xxx internal RC oscillator (HSI) calibration" available from the ST website <u>www.st.com</u>.

3. Guaranteed by design.

4. Guaranteed by characterization results.

| Symbol                   | Parameter                               | Min                     | Мах                     | Unit |

|--------------------------|-----------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>       | FSMC_NE low time                        | 3t <sub>HCLK</sub> – 1  | 3t <sub>HCLK</sub> + 2  | ns   |

| t <sub>v(NWE_NE)</sub>   | FSMC_NEx low to FSMC_NWE low            | t <sub>HCLK</sub> – 0.5 | t <sub>HCLK</sub> + 1.5 | ns   |

| t <sub>w(NWE)</sub>      | FSMC_NWE low time                       | t <sub>HCLK</sub> – 0.5 | t <sub>HCLK</sub> + 1.5 | ns   |

| t <sub>h(NE_NWE)</sub>   | FSMC_NWE high to FSMC_NE high hold time | t <sub>HCLK</sub>       | -                       | ns   |

| t <sub>v(A_NE)</sub>     | FSMC_NEx low to FSMC_A valid            | -                       | 7.5                     | ns   |

| t <sub>h(A_NWE)</sub>    | Address hold time after FSMC_NWE high   | t <sub>HCLK</sub>       | -                       | ns   |

| t <sub>v(BL_NE)</sub>    | FSMC_NEx low to FSMC_BL valid           | -                       | 0                       | ns   |

| t <sub>h(BL_NWE)</sub>   | FSMC_BL hold time after FSMC_NWE high   | t <sub>HCLK</sub> – 0.5 | -                       | ns   |

| t <sub>v(Data_NE)</sub>  | FSMC_NEx low to Data valid              | -                       | t <sub>HCLK</sub> + 7   | ns   |

| t <sub>h(Data_NWE)</sub> | Data hold time after FSMC_NWE high      | t <sub>HCLK</sub>       | -                       | ns   |

| t <sub>v(NADV_NE)</sub>  | FSMC_NEx low to FSMC_NADV low           | -                       | 5.5                     | ns   |

| t <sub>w(NADV)</sub>     | FSMC_NADV low time                      | -                       | t <sub>HCLK</sub> + 1.5 | ns   |

Table 32. Asynchronous non-multiplexed SRAM/PSRAM/NOR write timings<sup>(1)(2)</sup>

1. C<sub>L</sub> = 15 pF.

2. Guaranteed by characterization results.

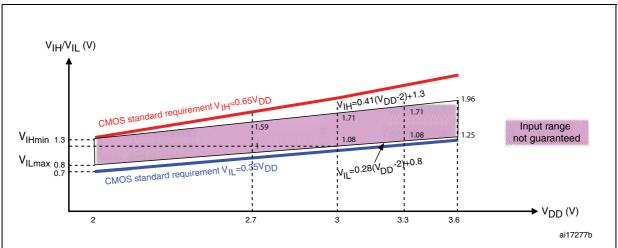

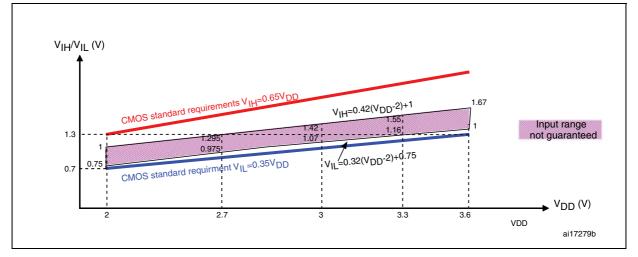

Figure 42. Standard I/O input characteristics - CMOS port

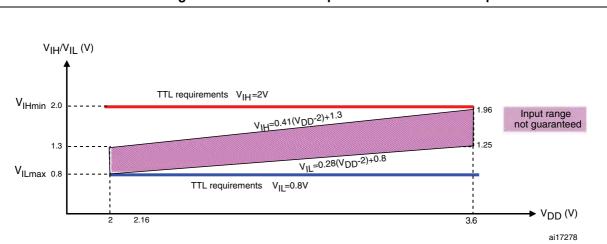

Figure 43. Standard I/O input characteristics - TTL port

Figure 44. 5 V tolerant I/O input characteristics - CMOS port

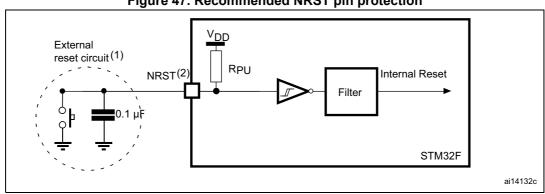

Figure 47. Recommended NRST pin protection

- 1. The reset network protects the device against parasitic resets.

- The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 49. Otherwise the reset will not be taken into account by the device.

#### 5.3.16 TIM timer characteristics

The parameters given in Table 50 are guaranteed by design.

Refer to *Section 5.3.14: I/O port characteristics* for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                       | Parameter Conditions Min      |        | Max                     | Unit                 |

|------------------------|---------------------------------|-------------------------------|--------|-------------------------|----------------------|

| +                      | Timer resolution time           | -                             | 1      | -                       | t <sub>TIMxCLK</sub> |

| t <sub>res(TIM)</sub>  |                                 | f <sub>TIMxCLK</sub> = 72 MHz | 13.9   | -                       | ns                   |

| f                      | Timer external clock            | -                             | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |

| f <sub>EXT</sub>       | frequency on CH1 to CH4         | f <sub>TIMxCLK</sub> = 72 MHz | 0      | 36                      | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution                | -                             | -      | 16                      | bit                  |

|                        | 16-bit counter clock period     | -                             | 1      | 65536                   | t <sub>TIMxCLK</sub> |

| <sup>t</sup> COUNTER   | when internal clock is selected | f <sub>TIMxCLK</sub> = 72 MHz | 0.0139 | 910                     | μs                   |

| t <sub>MAX_COUNT</sub> | Maximum possible count          | -                             | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |

|                        |                                 | f <sub>TIMxCLK</sub> = 72 MHz | -      | 59.6                    | s                    |

Table 50. TIMx<sup>(1)</sup> characteristics

1. TIMx is used as a general term to refer to the TIM1, TIM2, TIM3 and TIM4 timers.

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}.}$

| Symbol                               | Parameter                                                                                                                                                          | Min | Тур | Мах  | Unit | Comments                                                                                                                |  |  |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|-------------------------------------------------------------------------------------------------------------------------|--|--|

|                                      | Offset error                                                                                                                                                       | -   | -   | ±10  | mV   | -                                                                                                                       |  |  |

| Offset <sup>(3)</sup>                | (difference between<br>measured value at Code                                                                                                                      | -   | -   | ±3   | LSB  | Given for the DAC in 10-bit at V <sub>REF+</sub><br>= 3.6 V                                                             |  |  |

|                                      | (0x800) and the ideal value =<br>V <sub>REF+</sub> /2)                                                                                                             | -   | -   | ±12  | LSB  | Given for the DAC in 12-bit at V <sub>REF+</sub><br>= 3.6 V                                                             |  |  |

| Gain<br>error <sup>(3)</sup>         | Gain error                                                                                                                                                         | -   | -   | ±0.5 | %    | Given for the DAC in 12bit configuration                                                                                |  |  |

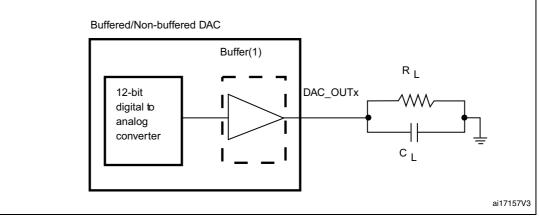

| t <sub>SETTLING</sub> <sup>(3)</sup> | Settling time (full scale: for a<br>10-bit input code transition<br>between the lowest and the<br>highest input codes when<br>DAC_OUT reaches final<br>value ±1LSB | -   | 3   | 4    | μs   | $C_{LOAD} \le 50 \text{ pF, } R_{LOAD} \ge 5 \text{ k}\Omega$                                                           |  |  |

| Update<br>rate <sup>(3)</sup>        | Max frequency for a correct<br>DAC_OUT change when<br>small variation in the input<br>code (from code i to i+1LSB)                                                 | -   | -   | 1    | MS/s | $C_{LOAD} \le 50 \text{ pF, } R_{LOAD} \ge 5 \text{ k}\Omega$                                                           |  |  |

| t <sub>wakeup</sub> (3)              | Wakeup time from off state<br>(Setting the ENx bit in the<br>DAC Control register)                                                                                 | -   | 6.5 | 10   | μs   | $C_{LOAD} \le 50 \text{ pF}, R_{LOAD} \ge 5 \text{ k}\Omega$<br>input code between lowest and<br>highest possible ones. |  |  |

| PSRR+ <sup>(1)</sup>                 | Power supply rejection ratio<br>(to V <sub>DDA</sub> ) (static DC<br>measurement                                                                                   | -   | -67 | -40  | dB   | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                                        |  |  |

Table 63. DAC characteristics (continued)

1. Guaranteed by design.

2. Guaranteed by characterization.

3. The quiescent mode corresponds to a state where the DAC maintains a stable output level to ensure that no dynamic consumption occurs.

4. Guaranteed by characterization results.

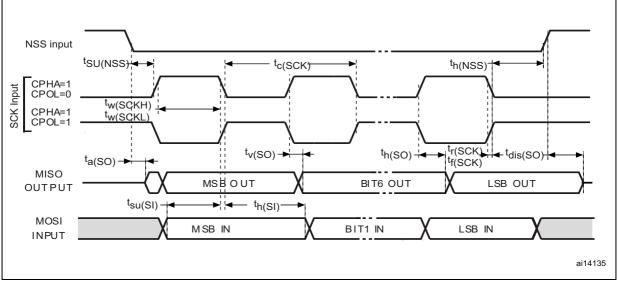

1. The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

# 6 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

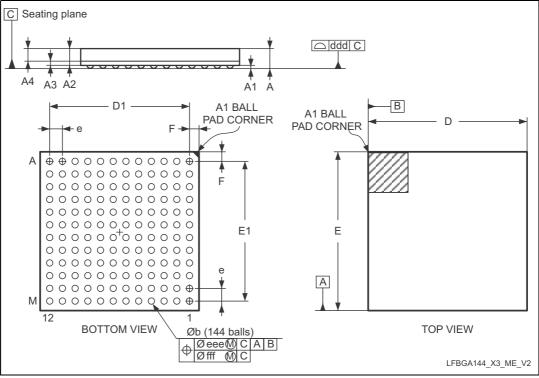

## 6.1 LFBGA144 package information

Figure 62. LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm, 0.8 mm pitch, package outline

1. Drawing is not to scale.

| Table 65. LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm, |

|-----------------------------------------------------------------------------------|

| 0.8 mm pitch, package mechanical data                                             |

| Symbol           |       | millimeters |       |        | inches <sup>(1)</sup> |        |  |

|------------------|-------|-------------|-------|--------|-----------------------|--------|--|

| Symbol           | Min   | Тур         | Мах   | Тур    | Min                   | Max    |  |

| A <sup>(2)</sup> | -     | -           | 1.700 | -      | -                     | 0.0669 |  |

| A1               | 0.250 | 0.300       | 0.350 | 0.098  | 0.0118                | 0.0138 |  |

| A2               | 0.810 | 0.910       | 1.010 | 0.0319 | 0.0358                | 0.0398 |  |

| A3               | 0.225 | 0.26        | 0.295 | 0.0089 | 0.0102                | 0.0116 |  |

| A4               | 0.585 | 0.650       | 0.715 | 0.0230 | 0.0256                | 0.0281 |  |

| mechanical data |     |             |       |                       |     |        |  |  |  |  |

|-----------------|-----|-------------|-------|-----------------------|-----|--------|--|--|--|--|

| Symbol          |     | millimeters |       | inches <sup>(1)</sup> |     |        |  |  |  |  |

| Symbol          | Min | Тур         | Мах   | Min                   | Тур | Мах    |  |  |  |  |

| eee             | -   | -           | 0.150 | -                     | -   | 0.0059 |  |  |  |  |

| fff             | -   | -           | 0.080 | -                     | -   | 0.0031 |  |  |  |  |

# Table 67. LFBGA100 - 10 x 10 mm low profile fine pitch ball grid array package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

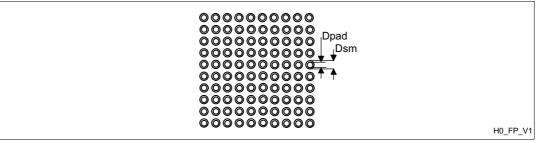

# Figure 66. LFBGA100 – 100-ball low profile fine pitch ball grid array, 10 x 10 mm, 0.8 mm pitch, package recommended footprintoutline

#### Table 68. LFBGA100 recommended PCB design rules (0.8 mm pitch BGA)

| Dimension         | Recommended values                                                    |

|-------------------|-----------------------------------------------------------------------|

| Pitch             | 0.8                                                                   |

| Dpad              | 0.500 mm                                                              |

| Dsm               | 0.570 mm typ. (depends on the soldermask reg-<br>istration tolerance) |

| Stencil opening   | 0.500 mm                                                              |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                         |

| Pad trace width   | 0.120 mm                                                              |

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|--------|-----------------------|--------|--------|

|        | Min         | Тур    | Мах    | Min                   | Тур    | Max    |

| А      | -           | -      | 1.600  | -                     | -      | 0.0630 |

| A1     | 0.050       | -      | 0.150  | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |

| с      | 0.090       | -      | 0.200  | 0.0035                | -      | 0.0079 |

| D      | 21.800      | 22.000 | 22.200 | 0.8583                | 0.8661 | 0.8740 |

| D1     | 19.800      | 20.000 | 20.200 | 0.7795                | 0.7874 | 0.7953 |

| D3     | -           | 17.500 | -      | -                     | 0.6890 | -      |

| E      | 21.800      | 22.000 | 22.200 | 0.8583                | 0.8661 | 0.8740 |

| E1     | 19.800      | 20.000 | 20.200 | 0.7795                | 0.7874 | 0.7953 |

| E3     | -           | 17.500 | -      | -                     | 0.6890 | -      |

| е      | -           | 0.500  | -      | -                     | 0.0197 | -      |

| L      | 0.450       | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000  | -      | -                     | 0.0394 | -      |

| k      | 0°          | 3.5°   | 7°     | 0°                    | 3.5°   | 7°     |

| CCC    | -           | -      | 0.080  | -                     | -      | 0.0031 |

| Table 71. LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package |

|-----------------------------------------------------------------------|

| mechanical data                                                       |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

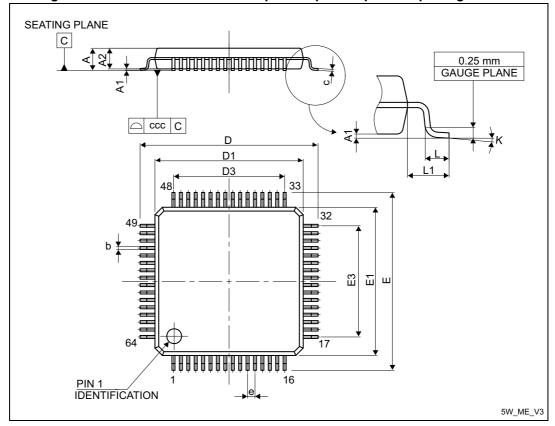

# 6.6 LQFP64 package information

Figure 76. LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package outline

#### Table 73. LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package mechanical data

| Symbol | millimeters |        |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|-------|-----------------------|--------|--------|

|        | Min         | Тур    | Мах   | Min                   | Тур    | Max    |

| А      | -           | -      | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050       | -      | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400  | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220  | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090       | -      | 0.200 | 0.0035                | -      | 0.0079 |

| D      | -           | 12.000 | -     | -                     | 0.4724 | -      |

| D1     | -           | 10.000 | -     | -                     | 0.3937 | -      |

| D3     | -           | 7.500  | -     | -                     | 0.2953 | -      |

| E      | -           | 12.000 | -     | -                     | 0.4724 | -      |

| E1     | -           | 10.000 | -     | -                     | 0.3937 | -      |

<sup>1.</sup> Drawing is not in scale.

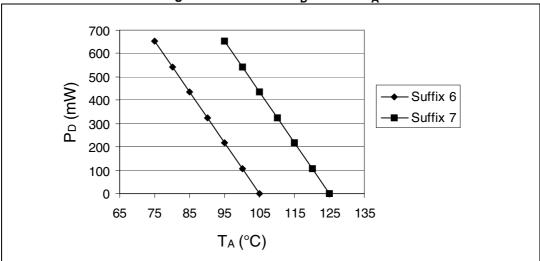

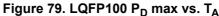

Using the values obtained in *Table 74*  $T_{Jmax}$  is calculated as follows:

- For LQFP100, 46 °C/W

- $T_{Jmax}$  = 115 °C + (46 °C/W × 134 mW) = 115 °C + 6.2 °C = 121.2 °C

This is within the range of the suffix 7 version parts (–40 <  $T_J$  < 125 °C).

In this case, parts must be ordered at least with the temperature range suffix 7 (see *Table 75: Ordering information scheme*).

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 12-Dec-2008 | 4        | Timers specified on page 1 (motor control capability mentioned).<br>Section 2.2: Full compatibility throughout the family updated.<br>Table 6: High-density timer feature comparison added.<br>General-purpose timers (TIMx) and Advanced-control timers (TIM1 and<br>TIM8) on page 27 updated.<br>Figure 1: STM32F103xF, STM32F103xD and<br>STM32F103xGSTM32F103xF and STM32F103xG performance line<br>block diagram modified.<br>Note 10 added, main function after reset and Note 5 on page 44<br>updated in Table 8: High-density STM32F103xx pin definitions.<br>Note 2 modified below Table 11: Voltage characteristics on page 58,<br>$ DV_{DDx} $ min and $ DV_{DDx} $ min removed.<br>Note 2 and P <sub>D</sub> values for LQFP144 and LFBGA144 packages added to<br>Table 14: General operating conditions on page 59.<br>Measurement conditions specified in Section 5.3.5: Supply current<br>characteristics on page 62.<br>Max values at T <sub>A</sub> = 85 °C and T <sub>A</sub> = 105 °C updated in Table 21: Typical<br>and maximum current consumptions in Stop and Standby modes on<br>page 68.<br>Section 5.3.10: FSMC characteristics on page 110.<br>I <sub>VREF</sub> added to Table 67: ADC characteristics on page 130.<br>Table 81: Package thermal characteristics on page 146 updated.<br>Small text changes. |  |  |

## Table 76.Document revision history