Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2010                       |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 72MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB            |

| Peripherals                | DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT            |

| Number of I/O              | 51                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | - ·                                                                     |

| RAM Size                   | 48K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f103rct7tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   |        | 2.3.29    | Serial wire JTAG debug port (SWJ-DP)                   |

|---|--------|-----------|--------------------------------------------------------|

|   |        | 2.3.30    | Embedded Trace Macrocell™24                            |

|   |        |           |                                                        |

| 3 | Pinou  | its and   | pin descriptions 25                                    |

| 4 | Memo   | ory map   | ping                                                   |

| 5 | Electi | rical cha | aracteristics                                          |

|   | 5.1    | Parame    | ter conditions                                         |

|   |        | 5.1.1     | Minimum and maximum values41                           |

|   |        | 5.1.2     | Typical values                                         |

|   |        | 5.1.3     | Typical curves                                         |

|   |        | 5.1.4     | Loading capacitor                                      |

|   |        | 5.1.5     | Pin input voltage                                      |

|   |        | 5.1.6     | Power supply scheme                                    |

|   |        | 5.1.7     | Current consumption measurement                        |

|   | 5.2    | Absolut   | e maximum ratings 43                                   |

|   | 5.3    | Operati   | ng conditions                                          |

|   |        | 5.3.1     | General operating conditions                           |

|   |        | 5.3.2     | Operating conditions at power-up / power-down          |

|   |        | 5.3.3     | Embedded reset and power control block characteristics |

|   |        | 5.3.4     | Embedded reference voltage                             |

|   |        | 5.3.5     | Supply current characteristics                         |

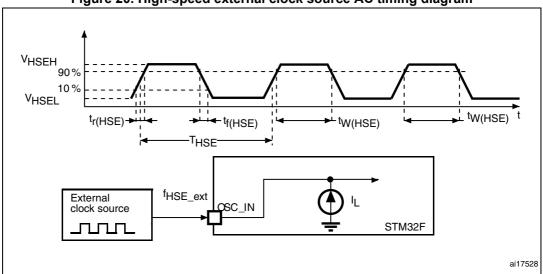

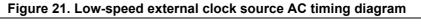

|   |        | 5.3.6     | External clock source characteristics                  |

|   |        | 5.3.7     | Internal clock source characteristics                  |

|   |        | 5.3.8     | PLL characteristics64                                  |

|   |        | 5.3.9     | Memory characteristics64                               |

|   |        | 5.3.10    | FSMC characteristics                                   |

|   |        | 5.3.11    | EMC characteristics                                    |

|   |        | 5.3.12    | Absolute maximum ratings (electrical sensitivity)      |

|   |        | 5.3.13    | I/O current injection characteristics                  |

|   |        | 5.3.14    | I/O port characteristics                               |

|   |        | 5.3.15    | NRST pin characteristics95                             |

|   |        | 5.3.16    | TIM timer characteristics                              |

|   |        | 5.3.17    | Communications interfaces                              |

|   |        | 5.3.18    | CAN (controller area network) interface                |

|   |        | 5.3.19    | 12-bit ADC characteristics                             |

# 2.3 Overview

# 2.3.1 ARM<sup>®</sup> Cortex<sup>®</sup>-M3 core with embedded Flash and SRAM

The ARM Cortex<sup>®</sup>-M3 processor is the latest generation of ARM processors for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM Cortex<sup>®</sup>-M3 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

With its embedded ARM core, STM32F103xC, STM32F103xD and STM32F103xE performance line family is compatible with all ARM tools and software.

*Figure 1* shows the general block diagram of the device family.

# 2.3.2 Embedded Flash memory

Up to 512 Kbytes of embedded Flash is available for storing programs and data.

#### 2.3.3 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

#### 2.3.4 Embedded SRAM

Up to 64 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states.

#### 2.3.5 FSMC (flexible static memory controller)

The FSMC is embedded in the STM32F103xC, STM32F103xD and STM32F103xE performance line family. It has four Chip Select outputs supporting the following modes: PC Card/Compact Flash, SRAM, PSRAM, NOR and NAND.

Functionality overview:

- The three FSMC interrupt lines are ORed in order to be connected to the NVIC

- Write FIFO

- Code execution from external memory except for NAND Flash and PC Card

- The targeted frequency, f<sub>CLK</sub>, is HCLK/2, so external access is at 36 MHz when HCLK is at 72 MHz and external access is at 24 MHz when HCLK is at 48 MHz

# 2.3.14 Low-power modes

The STM32F103xC, STM32F103xD and STM32F103xE performance line supports three low-power modes to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

• Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

• Stop mode

Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.

The device can be woken up from Stop mode by any of the EXTI line. The EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm or the USB wakeup.

• Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.8 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, SRAM and register contents are lost except for registers in the Backup domain and Standby circuitry.

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped by entering Stop or Standby mode.

# 2.3.15 DMA

The flexible 12-channel general-purpose DMAs (7 channels for DMA1 and 5 channels for DMA2) are able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The two DMA controllers support circular buffer management, removing the need for user code intervention when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with support for software trigger on each channel. Configuration is made by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: SPI, I<sup>2</sup>C, USART, general-purpose, basic and advanced-control timers TIMx, DAC, I<sup>2</sup>S, SDIO and ADC.

## 2.3.16 RTC (real-time clock) and backup registers

The RTC and the backup registers are supplied through a switch that takes power either on  $V_{DD}$  supply when present or through the  $V_{BAT}$  pin. The backup registers are forty-two 16-bit registers used to store 84 bytes of user application data when  $V_{DD}$  power is not present. They are not reset by a system or power reset, and they are not reset when the device wakes up from the Standby mode.

The real-time clock provides a set of continuously running counters which can be used with suitable software to provide a clock calendar function, and provides an alarm interrupt and a

#### Advanced-control timers (TIM1 and TIM8)

The two advanced-control timers (TIM1 and TIM8) can each be seen as a three-phase PWM multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead-times. They can also be seen as a complete general-purpose timer. The 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge or center-aligned modes)

- One-pulse mode output

If configured as a standard 16-bit timer, it has the same features as the TIMx timer. If configured as the 16-bit PWM generator, it has full modulation capability (0-100%).

In debug mode, the advanced-control timer counter can be frozen and the PWM outputs disabled to turn off any power switch driven by these outputs.

Many features are shared with those of the general-purpose TIM timers which have the same architecture. The advanced-control timer can therefore work together with the TIM timers via the Timer Link feature for synchronization or event chaining.

#### General-purpose timers (TIMx)

There are up to 4 synchronizable general-purpose timers (TIM2, TIM3, TIM4 and TIM5) embedded in the STM32F103xC, STM32F103xD and STM32F103xE performance line devices. These timers are based on a 16-bit auto-reload up/down counter, a 16-bit prescaler and feature 4 independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input captures / output compares / PWMs on the largest packages.

The general-purpose timers can work together with the advanced-control timer via the Timer Link feature for synchronization or event chaining. Their counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs. They all have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

#### Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger generation. They can also be used as a generic 16-bit time base.

#### Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

#### Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from

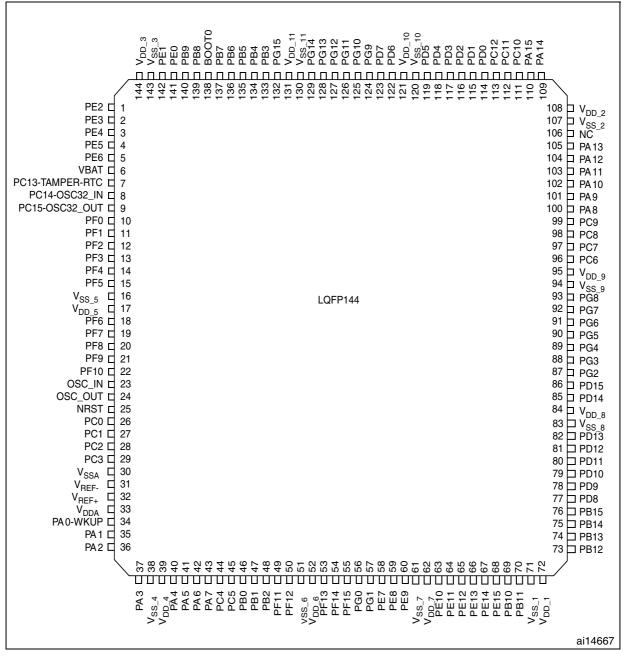

Figure 5. STM32F103xC/D/E performance line LQFP144 pinout

1. The above figure shows the package top view.

|          |          | Pir     |        |         |         |                   |                     |                            | · · ·                                            | Alternate functions <sup>(4)</sup>             |           |  |

|----------|----------|---------|--------|---------|---------|-------------------|---------------------|----------------------------|--------------------------------------------------|------------------------------------------------|-----------|--|

| LFBGA144 | LFBGA100 | WLCSP64 | LQFP64 | LQFP100 | LQFP144 | Pin name          | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                        | Remap     |  |

| L4       | J4       | H4      | 26     | 35      | 46      | PB0               | I/O                 | -                          | PB0                                              | ADC12_IN8/TIM3_CH3<br>TIM8_CH2N                | TIM1_CH2N |  |

| M4       | K4       | F4      | 27     | 36      | 47      | PB1               | I/O                 | -                          | PB1                                              | ADC12_IN9/TIM3_CH4 <sup>(9)</sup><br>TIM8_CH3N | TIM1_CH3N |  |

| J5       | G5       | H3      | 28     | 37      | 48      | PB2               | I/O                 | FT                         | PB2/BOOT1                                        | -                                              | -         |  |

| M5       | -        | -       | -      | -       | 49      | PF11              | I/O                 | FT                         | PF11                                             | FSMC_NIOS16                                    | -         |  |

| L5       | -        | -       | I      | -       | 50      | PF12              | I/O                 | FT                         | PF12                                             | FSMC_A6                                        | -         |  |

| H5       | -        | -       | I      | -       | 51      | $V_{SS_6}$        | S                   | -                          | $V_{SS_6}$                                       | -                                              | -         |  |

| G5       | -        | -       | -      | -       | 52      | $V_{DD_6}$        | S                   | -                          | $V_{DD_6}$                                       | -                                              | -         |  |

| K5       | -        | -       | I      | -       | 53      | PF13              | I/O                 | FT                         | PF13                                             | FSMC_A7                                        | -         |  |

| M6       | -        | -       | I      | -       | 54      | PF14              | I/O                 | FT                         | PF14                                             | FSMC_A8                                        | -         |  |

| L6       | -        | -       | -      | -       | 55      | PF15              | I/O                 | FT                         | PF15                                             | FSMC_A9                                        | -         |  |

| K6       | -        | -       | -      | -       | 56      | PG0               | I/O                 | FT                         | PG0                                              | FSMC_A10                                       | -         |  |

| J6       | -        | -       | -      | -       | 57      | PG1               | I/O                 | FT                         | PG1                                              | FSMC_A11                                       | -         |  |

| M7       | H5       | -       | -      | 38      | 58      | PE7               | I/O                 | FT                         | PE7                                              | FSMC_D4                                        | TIM1_ETR  |  |

| L7       | J5       | -       | -      | 39      | 59      | PE8               | I/O                 | FT                         | PE8                                              | FSMC_D5                                        | TIM1_CH1N |  |

| K7       | K5       | -       | -      | 40      | 60      | PE9               | I/O                 | FT                         | PE9                                              | FSMC_D6                                        | TIM1_CH1  |  |

| H6       | -        | -       | -      | -       | 61      | V <sub>SS_7</sub> | S                   | -                          | V <sub>SS_7</sub>                                | -                                              | -         |  |

| G6       | -        | -       | -      | -       | 62      | V <sub>DD_7</sub> | S                   | -                          | V <sub>DD_7</sub>                                | -                                              | -         |  |

| J7       | G6       | -       | -      | 41      | 63      | PE10              | I/O                 | FT                         | PE10                                             | FSMC_D7                                        | TIM1_CH2N |  |

| H8       | H6       | -       | -      | 42      | 64      | PE11              | I/O                 | FT                         | PE11                                             | FSMC_D8                                        | TIM1_CH2  |  |

| J8       | J6       | -       | -      | 43      | 65      | PE12              | I/O                 | FT                         | PE12                                             | FSMC_D9                                        | TIM1_CH3N |  |

| K8       | K6       | -       | -      | 44      | 66      | PE13              | I/O                 | FT                         | PE13                                             | FSMC_D10                                       | TIM1_CH3  |  |

| L8       | G7       | -       | -      | 45      | 67      | PE14              | I/O                 | FT                         | PE14                                             | FSMC_D11                                       | TIM1_CH4  |  |

| M8       | H7       | -       | -      | 46      | 68      | PE15              | I/O                 | FT                         | PE15                                             | FSMC_D12                                       | TIM1_BKIN |  |

| M9       | J7       | G3      | 29     | 47      | 69      | PB10              | I/O                 | FT                         | PB10                                             | I2C2_SCL/USART3_TX <sup>(9)</sup>              | TIM2_CH3  |  |

| M10      | K7       | F3      | 30     | 48      | 70      | PB11              | I/O                 | FT                         | PB11                                             | I2C2_SDA/USART3_RX <sup>(9)</sup>              | TIM2_CH4  |  |

| H7       | E7       | H2      | 31     | 49      | 71      | V <sub>SS_1</sub> | S                   | -                          | V <sub>SS_1</sub>                                | -                                              | -         |  |

| G7       | F7       | H1      | 32     | 50      | 72      | $V_{DD_1}$        | S                   | -                          | V <sub>DD_1</sub>                                | -                                              | -         |  |

Table 5. High-density STM32F103xC/D/E pin definitions (continued)

|          |          | Pir     | IS     |         |         |                   |                     |    |                   | Alternate functions <sup>(4)</sup> |       |  |

|----------|----------|---------|--------|---------|---------|-------------------|---------------------|----|-------------------|------------------------------------|-------|--|

| LFBGA144 | LFBGA100 | WLCSP64 | LQFP64 | LQFP100 | LQFP144 | Pin name          | Type <sup>(1)</sup> | 2  |                   | Default                            | Remap |  |

| A5       | D4       | -       | -      | 97      | 141     | PE0               | I/O                 | FT | PE0               | TIM4_ETR / FSMC_NBL0               | -     |  |

| A4       | C4       | -       | -      | 98      | 142     | PE1               | I/O                 | FT | PE1               | FSMC_NBL1                          | -     |  |

| E5       | E5       | A7      | 63     | 99      | 143     | V <sub>SS_3</sub> | S                   | -  | V <sub>SS_3</sub> | -                                  | -     |  |

| F5       | F5       | A8      | 64     | 100     | 144     | $V_{DD_3}$        | S                   | -  | V <sub>DD_3</sub> | -                                  | _     |  |

Table 5. High-density STM32F103xC/D/E pin definitions (continued)

1. I = input, O = output, S = supply.

2. FT = 5 V tolerant.

3. Function availability depends on the chosen device.

- 4. If several peripherals share the same I/O pin, to avoid conflict between these alternate functions only one peripheral should be enabled at a time through the peripheral clock enable bit (in the corresponding RCC peripheral clock enable register).

- PC13, PC14 and PC15 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 in output mode is limited: the speed should not exceed 2 MHz with a maximum load of 30 pF and these IOs must not be used as a current source (e.g. to drive an LED).

- 6. Main function after the first backup domain power-up. Later on, it depends on the contents of the Backup registers even after reset (because these registers are not reset by the main reset). For details on how to manage these IOs, refer to the Battery backup domain and BKP register description sections in the STM32F10xxx reference manual, available from the STMicroelectronics website: www.st.com.

- 7. In the WCLSP64 package, the PC3 I/O pin is not bonded and it must be configured by software to output mode (Push-pull) and writing 0 to the data register in order to avoid an extra consumption during low-power modes.

- 8. Unlike in the LQFP64 package, there is no PC3 in the WLCSP package. The V<sub>REF+</sub> functionality is provided instead.

- This alternate function can be remapped by software to some other port pins (if available on the used package). For more

details, refer to the Alternate function I/O and debug configuration section in the STM32F10xxx reference manual,

available from the STMicroelectronics website: www.st.com.

- 10. For the WCLSP64/LQFP64 package, the pins number 5 and 6 are configured as OSC\_IN/OSC\_OUT after reset, however the functionality of PD0 and PD1 can be remapped by software on these pins. For the LQFP100/BGA100 and LQFP144/BGA144 packages, PD0 and PD1 are available by default, so there is no need for remapping. For more details, refer to Alternate function I/O and debug configuration section in the STM32F10xxx reference manual.

- 11. For devices delivered in LQFP64 packages, the FSMC function is not available.

|      |        |        | FSM                | C             | ,           |                                  |

|------|--------|--------|--------------------|---------------|-------------|----------------------------------|

| Pins | CF     | CF/IDE | NOR/PSRAM/<br>SRAM | NOR/PSRAM Mux | NAND 16 bit | LQFP100<br>BGA100 <sup>(1)</sup> |

| PD9  | D14    | D14    | D14                | DA14          | D14         | Yes                              |

| PD10 | D15    | D15    | D15                | DA15          | D15         | Yes                              |

| PD11 | -      | -      | A16                | A16           | CLE         | Yes                              |

| PD12 | -      | -      | A17                | A17           | ALE         | Yes                              |

| PD13 | -      | -      | A18                | A18           | -           | Yes                              |

| PD14 | D0     | D0     | D0                 | DA0           | D0          | Yes                              |

| PD15 | D1     | D1     | D1                 | DA1           | D1          | Yes                              |

| PG2  | -      | -      | A12                | -             | -           | -                                |

| PG3  | -      | -      | A13                | -             | -           | -                                |

| PG4  | -      | -      | A14                | -             | -           | -                                |

| PG5  | -      | -      | A15                | -             | -           | -                                |

| PG6  | -      | -      | -                  | -             | INT2        | -                                |

| PG7  | -      | -      | -                  | -             | INT3        | -                                |

| PD0  | D2     | D2     | D2                 | DA2           | D2          | Yes                              |

| PD1  | D3     | D3     | D3                 | DA3           | D3          | Yes                              |

| PD3  | -      | -      | CLK                | CLK           | -           | Yes                              |

| PD4  | NOE    | NOE    | NOE                | NOE           | NOE         | Yes                              |

| PD5  | NWE    | NWE    | NWE                | NWE           | NWE         | Yes                              |

| PD6  | NWAIT  | NWAIT  | NWAIT              | NWAIT         | NWAIT       | Yes                              |

| PD7  | -      | -      | NE1                | NE1           | NCE2        | Yes                              |

| PG9  | -      | -      | NE2                | NE2           | NCE3        | -                                |

| PG10 | NCE4_1 | NCE4_1 | NE3                | NE3           | -           | -                                |

| PG11 | NCE4_2 | NCE4_2 | -                  | -             | -           | -                                |

| PG12 | -      | -      | NE4                | NE4           | -           | -                                |

| PG13 | -      | -      | A24                | A24           | -           | -                                |

| PG14 | -      | -      | A25                | A25           | -           | -                                |

| PB7  | -      | -      | NADV               | NADV          | -           | Yes                              |

| PE0  | -      | -      | NBL0               | NBL0          | -           | Yes                              |

| PE1  | -      | -      | NBL1               | NBL1          | -           | Yes                              |

Table 6. FSMC pin definition (continued)

1. Ports F and G are not available in devices delivered in 100-pin packages.

| Symbol          | Parameter      | Conditions                          | 4      | Ма                     | ax <sup>(1)</sup>       | Unit |

|-----------------|----------------|-------------------------------------|--------|------------------------|-------------------------|------|

| Symbol          | Farameter      | Conditions                          | fhclk  | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |

|                 |                |                                     | 72 MHz | 45                     | 46                      |      |

|                 |                |                                     | 48 MHz | 31                     | 32                      |      |

|                 |                | External clock <sup>(2)</sup> , all | 36 MHz | 24                     | 25                      |      |

|                 |                | peripherals enabled                 | 24 MHz | 17                     | 17.5                    |      |

|                 |                |                                     | 16 MHz | 12.5                   | 13                      |      |

|                 | Supply current |                                     | 8 MHz  | 8                      | 8                       | mA   |

| I <sub>DD</sub> | in Sleep mode  |                                     | 72 MHz | 8.5                    | 9                       |      |

|                 |                |                                     | 48 MHz | 7                      | 7.5                     |      |

|                 |                | External clock <sup>(2)</sup> , all | 36 MHz | 6                      | 6.5                     |      |

|                 |                | peripherals disabled                | 24 MHz | 5                      | 5.5                     |      |

|                 |                |                                     | 16 MHz | 4.5                    | 5                       |      |

|                 |                |                                     | 8 MHz  | 4                      | 4                       |      |

# Table 16. Maximum current consumption in Sleep mode, code running from Flash or RAM

1. Guaranteed by characterization results at  $V_{\text{DD}}$  max,  $f_{\text{HCLK}}$  max with peripherals enabled.

2. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

| Peri                | pheral              | Current<br>consumption   | Unit   |

|---------------------|---------------------|--------------------------|--------|

|                     | APB2-Bridge         | 4,17                     |        |

|                     | GPIOA               | 8,47                     |        |

|                     | GPIOB               | 8,47                     |        |

|                     | GPIOC               | 6,53                     |        |

|                     | GPIOD               | 8,47                     |        |

|                     | GPIOE               | 6,53                     |        |

|                     | GPIOF               | 6,53                     |        |

| APB2 (up to 72 MHz) | GPIOG               | 6,11                     | µA/MHz |

|                     | SPI1                | 4,72                     |        |

|                     | USART1              | 12,50                    |        |

|                     | TIM1                | 22,92                    |        |

|                     | TIM8                | 22,92                    |        |

|                     | ADC1 <sup>(4)</sup> | 17,32                    |        |

|                     | ADC2 <sup>(4)</sup> | DC2 <sup>(4)</sup> 15,18 |        |

|                     | ADC3 <sup>(4)</sup> | 14,82                    |        |

| Table 20. | Peripheral cur | rent consumpt | ion (continued) |

|-----------|----------------|---------------|-----------------|

|-----------|----------------|---------------|-----------------|

1. The BusMatrix is automatically active when at least one master is ON. (CPU, DMA1 or DMA2).

2. When the I2S is enabled, a current consumption equal to 0.02 mA must be added.

3. When DAC\_OU1 or DAC\_OUT2 is enabled, a current consumption equal to 0.36 mA must be added.

Specific conditions for measuring ADC current consumption: f<sub>HCLK</sub> = 56 MHz, f<sub>APB1</sub> = f<sub>HCLK</sub>/2, f<sub>APB2</sub> = f<sub>HCLK</sub>, f<sub>ADCCLK</sub> = f<sub>APB2</sub>/4. When ADON bit in the ADCx\_CR2 register is set to 1, a current consumption of analog part equal to 0.54 mA must be added for each ADC.

Figure 20. High-speed external clock source AC timing diagram

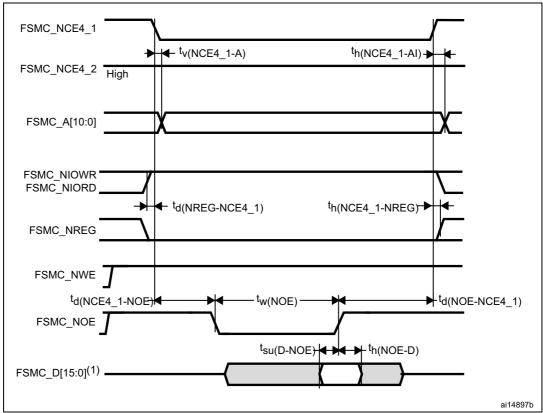

Figure 34. PC Card/CompactFlash controller waveforms for attribute memory read access

1. Only data bits 0...7 are read (bits 8...15 are disregarded).

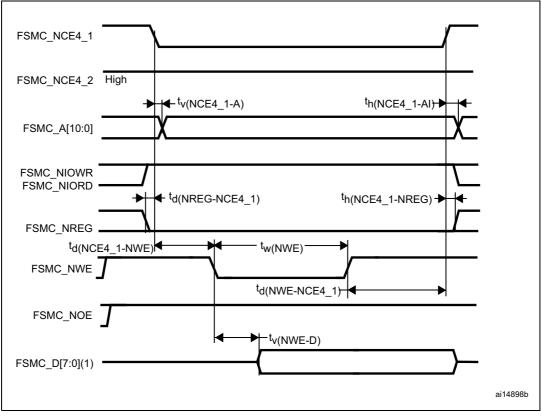

Figure 35. PC Card/CompactFlash controller waveforms for attribute memory write access

1. Only data bits 0...7 are driven (bits 8...15 remains HiZ).

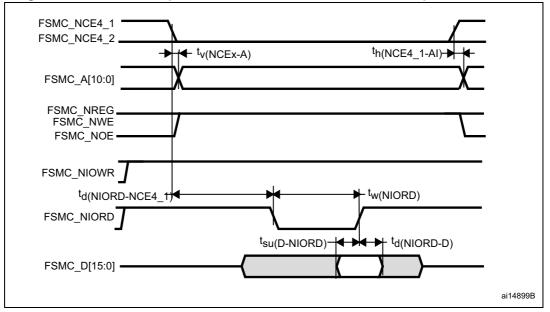

#### Figure 36. PC Card/CompactFlash controller waveforms for I/O space read access

| Symbol | Parameter             | Conditions                            | Class      |  |  |  |

|--------|-----------------------|---------------------------------------|------------|--|--|--|

| LU     | Static latch-up class | $T_A = +105$ °C conforming to JESD78A | II level A |  |  |  |

#### Table 44. Electrical sensitivities

# 5.3.13 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (>5 LSB TUE), out of spec current injection on adjacent pins or other functional failure (for example reset, oscillator frequency deviation).

The test results are given in Table 45

|                  |                                                            | Functional s       |                    |      |

|------------------|------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                | Negative injection | Positive injection | Unit |

|                  | Injected current on OSC_IN32,<br>OSC_OUT32, PA4, PA5, PC13 | -0                 | +0                 |      |

| I <sub>INJ</sub> | Injected current on all FT pins                            | -5                 | +0                 | mA   |

|                  | Injected current on any other pin                          | -5                 | +5                 |      |

#### Table 45. I/O current injection susceptibility

#### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 46* and *Table 48*, respectively.

Unless otherwise specified, the parameters given in *Table 48* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 10*.

| MODEx[1:0]<br>bit value <sup>(1)</sup> | Symbol                  | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Conditions                                                     | Min                | Max                | Unit |  |

|----------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------|--------------------|------|--|

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $C_{L}$ = 50 pF, $V_{DD}$ = 2 V to 3.6 V                       | -                  | 2                  | MHz  |  |

| 10                                     | t <sub>f(IO)out</sub>   | Output high to low level fall time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $C_{1} = 50 \text{ pE} V_{-1} = 2 \text{ V to } 3.6 \text{ V}$ | -                  | 125 <sup>(3)</sup> | ns   |  |

|                                        | t <sub>r(IO)out</sub>   | Maximum frequency(2) $C_L = 50 \text{ pF}, V_{DD} = 2 \text{ V to } 3.6 \text{ V}$ Output high to low<br>level fall time $C_L = 50 \text{ pF}, V_{DD} = 2 \text{ V to } 3.6 \text{ V}$ Output low to high<br>level rise time $C_L = 50 \text{ pF}, V_{DD} = 2 \text{ V to } 3.6 \text{ V}$ Maximum frequency(2) $C_L = 50 \text{ pF}, V_{DD} = 2 \text{ V to } 3.6 \text{ V}$ Output high to low<br>level fall time $C_L = 50 \text{ pF}, V_{DD} = 2 \text{ V to } 3.6 \text{ V}$ Output low to high<br>level rise time $C_L = 50 \text{ pF}, V_{DD} = 2 \text{ V to } 3.6 \text{ V}$ Maximum frequency(2) $C_L = 30 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$ Maximum frequency(2) $C_L = 30 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ C}$ Maximum frequency(2) $C_L = 30 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ C}$ Maximum frequency(2) $C_L = 30 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ C}$ Output high to low<br> | -                                                              | 125 <sup>(3)</sup> | 115                |      |  |

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $C_{L}$ = 50 pF, $V_{DD}$ = 2 V to 3.6 V                       | -                  | 10                 | MHz  |  |

| 01                                     | t <sub>f(IO)out</sub>   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | C = 50  pE V = 2  V to  3.6  V                                 | -                  | 25 <sup>(3)</sup>  | 20   |  |

|                                        | t <sub>r(IO)out</sub>   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ος – 50 pr, v <sub>DD</sub> – 2 v to 3.0 v                     |                    | 25 <sup>(3)</sup>  | ns   |  |

|                                        | F <sub>max(IO)out</sub> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $C_{L}$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V                     | -                  | 50                 | MHz  |  |

|                                        |                         | Maximum frequency <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V                     | -                  | 30                 | MHz  |  |

|                                        |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $C_{L}$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                       | -                  | 20                 | MHz  |  |

|                                        |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $C_L$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V                       | -                  | 5 <sup>(3)</sup>   |      |  |

| 11                                     | t <sub>f(IO)out</sub>   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2.7 V to 3.6 V       |                    | 8 <sup>(3)</sup>   |      |  |

|                                        |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $C_{L}$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                       | -                  | 12 <sup>(3)</sup>  |      |  |

|                                        |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $C_L$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V                       | -                  | 5 <sup>(3)</sup>   | ns   |  |

|                                        | t <sub>r(IO)out</sub>   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V                     | -                  | 8 <sup>(3)</sup>   |      |  |

|                                        |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $C_{L}$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                       | -                  | 12 <sup>(3)</sup>  |      |  |

| -                                      | t <sub>EXTIpw</sub>     | signals detected by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -                                                              | 10                 | -                  | ns   |  |

Table 48. I/O AC characteristics<sup>(1)</sup>

1. The I/O speed is configured using the MODEx[1:0] bits. Refer to the STM32F10xxx reference manual for a description of GPIO Port configuration register.

2. The maximum frequency is defined in Figure 46.

3. Guaranteed by design.

| Symbol           | Parameter                                                           | Conditions              | Min | Max | Unit |  |  |  |  |  |

|------------------|---------------------------------------------------------------------|-------------------------|-----|-----|------|--|--|--|--|--|

|                  | CMD, D inputs (referenced to CK)                                    |                         |     |     |      |  |  |  |  |  |

| t <sub>ISU</sub> | t <sub>ISU</sub> Input setup time $C_L \le 30 \text{ pF}$ 2         |                         |     |     |      |  |  |  |  |  |

| t <sub>IH</sub>  | Input hold time                                                     | $C_L \le 30 \text{ pF}$ | 0   | -   | ns   |  |  |  |  |  |

| CMD, D out       | CMD, D outputs (referenced to CK) in MMC and SD HS mode             |                         |     |     |      |  |  |  |  |  |

| t <sub>OV</sub>  | Output valid time                                                   | $C_L \le 30 \text{ pF}$ | -   | 6   | 200  |  |  |  |  |  |

| t <sub>OH</sub>  | Output hold time                                                    | $C_L \le 30 \text{ pF}$ | 0   | -   | ns   |  |  |  |  |  |

|                  | CMD, D outputs (referenced to CK) in SD default mode <sup>(1)</sup> |                         |     |     |      |  |  |  |  |  |

| t <sub>OVD</sub> | $t_{OVD}$ Output valid default time $C_L \le 30 \text{ pF}$ -       |                         |     |     |      |  |  |  |  |  |

| t <sub>OHD</sub> | Output hold default time                                            | $C_L \le 30 \text{ pF}$ | 0.5 | -   | ns   |  |  |  |  |  |

#### Table 55. SD / MMC characteristics

1. Refer to SDIO\_CLKCR, the SDI clock control register to control the CK output.

#### **USB** characteristics

The USB interface is USB-IF certified (Full Speed).

#### Table 56. USB startup time

| Symbol                              | Parameter                    | Мах | Unit |

|-------------------------------------|------------------------------|-----|------|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB transceiver startup time | 1   | μs   |

1. Guaranteed by design.

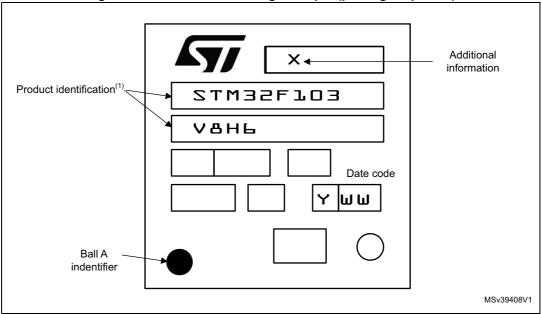

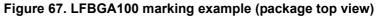

## Device marking for LFBGA100 package

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|--------|-----------------------|--------|--------|

|        | Min         | Тур    | Мах    | Min                   | Тур    | Max    |

| А      | -           | -      | 1.600  | -                     | -      | 0.0630 |

| A1     | 0.050       | -      | 0.150  | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |

| с      | 0.090       | -      | 0.200  | 0.0035                | -      | 0.0079 |

| D      | 21.800      | 22.000 | 22.200 | 0.8583                | 0.8661 | 0.8740 |

| D1     | 19.800      | 20.000 | 20.200 | 0.7795                | 0.7874 | 0.7953 |

| D3     | -           | 17.500 | -      | -                     | 0.6890 | -      |

| E      | 21.800      | 22.000 | 22.200 | 0.8583                | 0.8661 | 0.8740 |

| E1     | 19.800      | 20.000 | 20.200 | 0.7795                | 0.7874 | 0.7953 |

| E3     | -           | 17.500 | -      | -                     | 0.6890 | -      |

| е      | -           | 0.500  | -      | -                     | 0.0197 | -      |

| L      | 0.450       | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000  | -      | -                     | 0.0394 | -      |

| k      | 0°          | 3.5°   | 7°     | 0°                    | 3.5°   | 7°     |

| CCC    | -           | -      | 0.080  | -                     | -      | 0.0031 |

| Table 71. LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package |  |

|-----------------------------------------------------------------------|--|

| mechanical data                                                       |  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 31-08-2015  | 11       | <ul> <li>Replaced USBDP and USBDM by USB_DP and USB_DM in the whole document.</li> <li>Updated: <ul> <li>Introduction</li> <li>Reference standard in <i>Table 43:</i> ESD absolute maximum ratings.</li> <li>Updated I<sub>DDA</sub> description in <i>Table 63:</i> DAC characteristics.</li> <li>Section : I2C interface characteristics</li> <li>Figure 62: LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm, 0.8 mm pitch, package outline</li> <li>Updated sentence before Figure 78: LQFP64 marking example (package top view).</li> <li>Figure 65: LFBGA100 - 10 x 10 mm low profile fine pitch ball grid array package outline and sentence before Figure 75: LQFP100 marking example (package top view)</li> <li>Figure 68: WLCSP, 64-ball 4.466 × 4.395 mm, 0.500 mm pitch, wafer-level chip-scale package outline</li> <li>Figure 48: I2C bus AC waveforms and measurement circuit on page 98</li> <li>Section 6.1: LFBGA144 package information and Section 6.2: LFBGA100 package information.</li> <li>Table 20: Peripheral current consumption</li> <li>Added:</li> <li>Figure 63: LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm, 0.8 mm pitch, package recommended footprint</li> <li>Figure 64: LFBGA144 marking example (package top view)</li> <li>Figure 64: LFBGA144 marking example (package top view)</li> <li>Figure 66: LFBGA144 marking example (package top view)</li> <li>Figure 66: LFBGA144 marking example (package top view)</li> <li>Figure 66: LFBGA144 recommended PCB design rules (0.8 mm pitch wafer level chip scale package recommended footprint</li> <li>Table 66: LFBGA100 recommended PCB design rules (0.8 mm pitch BGA)</li> <li>Table 67: WLCSP64 recommended PCB design rules (0.5 mm pitch BGA)</li> </ul> </li> </ul> |  |  |

| 26-Nov-2015 | 12       | Updated:<br>– Table 59: ADC characteristics<br>– Table 65: LFBGA144 – 144-ball low profile fine pitch ball grid arra<br>10 x 10 mm, 0.8 mm pitch, package mechanical data<br>– Table 66: LFBGA144 recommended PCB design rules (0.8 mm pi<br>BGA)<br>Added:<br>– Note 3 on Table 7: Voltage characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

Table 76.Document revision history

#### IMPORTANT NOTICE – PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics – All rights reserved

DocID14611 Rev 12