Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | ARM® Cortex®-M3                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 72MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB             |

| Peripherals                | DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT             |

| Number of I/O              | 51                                                                       |

| Program Memory Size        | 256KB (256K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 48K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                    |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-UFBGA, WLCSP                                                          |

| Supplier Device Package    | 64-WLCSP (4.4x4.4)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f103rcy6ctr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   |      | 5.3.20        | DAC electrical specifications           | 112 |

|---|------|---------------|-----------------------------------------|-----|

|   |      | 5.3.21        | Temperature sensor characteristics      |     |

| 6 | Pack | cage info     | ormation                                | 115 |

|   | 6.1  | LFBG <i>A</i> | 144 package information                 | 115 |

|   | 6.2  | LFBG <i>A</i> | 100 package information                 | 118 |

|   | 6.3  | WLCS          | P64 package information                 | 121 |

|   | 6.4  | LQFP1         | 44 package information                  | 123 |

|   | 6.5  | LQFP1         | 00 package information                  | 127 |

|   | 6.6  | LQFP6         | 4 package information                   | 130 |

|   | 6.7  | Therm         | al characteristics                      | 133 |

|   |      | 6.7.1         | Reference document                      | 133 |

|   |      | 6.7.2         | Selecting the product temperature range | 134 |

| 7 | Part | numbei        | ring                                    | 136 |

| 8 | Revi | sion his      | story                                   | 137 |

# 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32F103xC, STM32F103xD and STM32F103xE high-density performance line microcontrollers. For more details on the whole STMicroelectronics STM32F103xC/D/E family, please refer to Section 2.2: Full compatibility throughout the family.

The high-density STM32F103xC/D/E datasheet should be read in conjunction with the STM32F10xxx reference manual.

For information on programming, erasing and protection of the internal Flash memory please refer to the *STM32F10xxx Flash programming manual*.

The reference and Flash programming manuals are both available from the STMicroelectronics website *www.st.com*.

For information on the Cortex<sup>®</sup>-M3 core please refer to the Cortex<sup>®</sup>-M3 Technical Reference Manual, available from the *www.arm.com* website at the following address: *http://infocenter.arm.com*.

#### Advanced-control timers (TIM1 and TIM8)

The two advanced-control timers (TIM1 and TIM8) can each be seen as a three-phase PWM multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead-times. They can also be seen as a complete general-purpose timer. The 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge or center-aligned modes)

- · One-pulse mode output

If configured as a standard 16-bit timer, it has the same features as the TIMx timer. If configured as the 16-bit PWM generator, it has full modulation capability (0-100%).

In debug mode, the advanced-control timer counter can be frozen and the PWM outputs disabled to turn off any power switch driven by these outputs.

Many features are shared with those of the general-purpose TIM timers which have the same architecture. The advanced-control timer can therefore work together with the TIM timers via the Timer Link feature for synchronization or event chaining.

#### **General-purpose timers (TIMx)**

There are up to 4 synchronizable general-purpose timers (TIM2, TIM3, TIM4 and TIM5) embedded in the STM32F103xC, STM32F103xD and STM32F103xE performance line devices. These timers are based on a 16-bit auto-reload up/down counter, a 16-bit prescaler and feature 4 independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input captures / output compares / PWMs on the largest packages.

The general-purpose timers can work together with the advanced-control timer via the Timer Link feature for synchronization or event chaining. Their counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs. They all have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

#### **Basic timers TIM6 and TIM7**

These timers are mainly used for DAC trigger generation. They can also be used as a generic 16-bit time base.

#### Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

#### Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the general-purpose timers (TIMx) and the advanced-control timers (TIM1 and TIM8) can be internally connected to the ADC start trigger and injection trigger, respectively, to allow the application to synchronize A/D conversion and timers.

# 2.3.27 DAC (digital-to-analog converter)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs. The chosen design structure is composed of integrated resistor strings and an amplifier in inverting configuration.

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- 8-bit or 12-bit monotonic output

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- external triggers for conversion

- input voltage reference V<sub>REF+</sub>

Eight DAC trigger inputs are used in the STM32F103xC, STM32F103xD and STM32F103xE performance line family. The DAC channels are triggered through the timer update outputs that are also connected to different DMA channels.

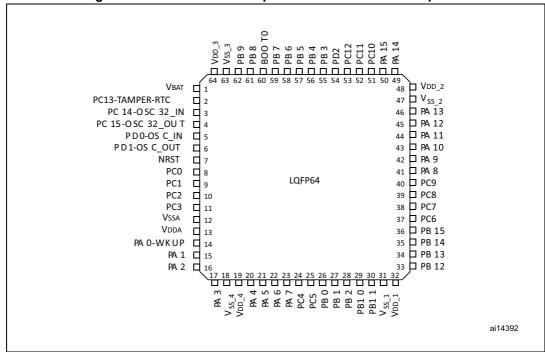

Figure 7. STM32F103xC/D/E performance line LQFP64 pinout

1. The above figure shows the package top view.

### 5.3.2 Operating conditions at power-up / power-down

The parameters given in *Table 11* are derived from tests performed under the ambient temperature condition summarized in *Table 10*.

Table 11. Operating conditions at power-up / power-down

| Symbol           | Parameter                      | Conditions | Min | Max | Unit  |

|------------------|--------------------------------|------------|-----|-----|-------|

| t                | V <sub>DD</sub> rise time rate | _          | 0   | 8   | us/V  |

| τ <sub>VDD</sub> | V <sub>DD</sub> fall time rate | -          | 20  | ∞   | μ5/ ν |

## 5.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 12* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 10*.

Table 12. Embedded reset and power control block characteristics

| Symbol                               | Parameter                | Conditions                  | Min                | Тур           | Max  | Unit       |  |  |

|--------------------------------------|--------------------------|-----------------------------|--------------------|---------------|------|------------|--|--|

|                                      |                          | PLS[2:0]=000 (rising edge)  | 2.1                | 2.18          | 2.26 |            |  |  |

|                                      |                          | PLS[2:0]=000 (falling edge) | 2                  | 2.08          | 2.16 |            |  |  |

|                                      |                          | PLS[2:0]=001 (rising edge)  | 2.19               | 2.28          | 2.37 |            |  |  |

|                                      |                          | PLS[2:0]=001 (falling edge) | 2.09               | 2.18          | 2.27 |            |  |  |

|                                      |                          | PLS[2:0]=010 (rising edge)  | 2.28               | 2.38          | 2.48 |            |  |  |

|                                      |                          | PLS[2:0]=010 (falling edge) | 2.18               | 2.28          | 2.38 |            |  |  |

|                                      |                          | PLS[2:0]=011 (rising edge)  | 2.38               | 2.48          | 2.58 |            |  |  |

| V                                    | Programmable voltage     | PLS[2:0]=011 (falling edge) | 2.28               | 2.38          | 2.48 |            |  |  |

| $V_{PVD}$                            | detector level selection | PLS[2:0]=100 (rising edge)  | 2.47               | 2.58          | 2.69 | ľ          |  |  |

|                                      |                          | PLS[2:0]=100 (falling edge) | 2.37               | 2.48          | 2.59 |            |  |  |

|                                      |                          | PLS[2:0]=101 (rising edge)  | 2.57               | 2.68          | 2.79 |            |  |  |

|                                      |                          | PLS[2:0]=101 (falling edge) | 2.47               | 2.58          | 2.69 |            |  |  |

|                                      |                          | PLS[2:0]=110 (rising edge)  | 2.66               | 2.78          | 2.9  |            |  |  |

|                                      |                          | PLS[2:0]=110 (falling edge) | 2.56               | 2.68          | 2.8  |            |  |  |

|                                      |                          | PLS[2:0]=111 (rising edge)  | 2.76               | 2.88          | 3    |            |  |  |

|                                      |                          | PLS[2:0]=111 (falling edge) | 2.66               | 2.66 2.78 2.9 |      |            |  |  |

| V <sub>PVDhyst</sub> <sup>(2)</sup>  | PVD hysteresis           | -                           | -                  | 100           | -    | mV         |  |  |

|                                      | Power on/power down      | Falling edge                | 1.8 <sup>(1)</sup> | 1.88          | 1.96 | \/         |  |  |

| V <sub>POR/PDR</sub>                 | reset threshold          | Rising edge                 | 1.84               | 1.92          | 2.0  | <b>→</b> ∨ |  |  |

| V <sub>PDRhyst</sub> <sup>(2)</sup>  | PDR hysteresis           | -                           | -                  | 40            | -    | mV         |  |  |

| T <sub>RSTTEMPO</sub> <sup>(2)</sup> | Reset temporization      | -                           | 1                  | 2.5           | 4.5  | ms         |  |  |

<sup>1.</sup> The product behavior is guaranteed by design down to the minimum  $V_{\mbox{\footnotesize{POR/PDR}}}$  value.

<sup>2.</sup> Guaranteed by design.

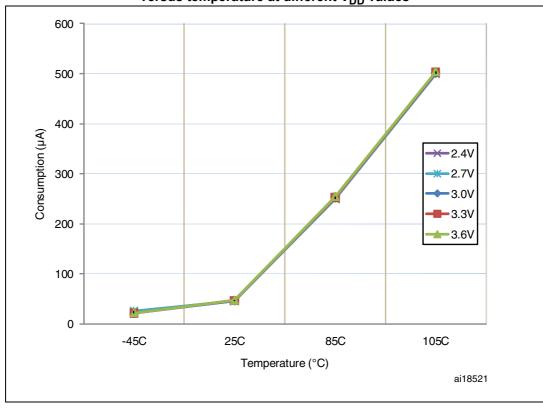

Figure 17. Typical current consumption in Stop mode with regulator in run mode versus temperature at different V<sub>DD</sub> values

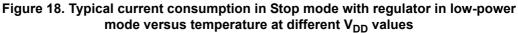

#### **Typical current consumption**

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load).

- All peripherals are disabled except if it is explicitly mentioned.

- The Flash access time is adjusted to f<sub>HCLK</sub> frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 48 MHZ and 2 wait states above).

- Ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in Table 10.

- Prefetch is ON (Reminder: this bit must be set before clock setting and bus prescaling)

When the peripherals are enabled  $f_{PCLK1} = f_{HCLK}/4$ ,  $f_{PCLK2} = f_{HCLK}/2$ ,  $f_{ADCCLK} = f_{PCLK2}/4$

Table 18. Typical current consumption in Run mode, code with data processing running from Flash

|                 |                   |                                 |         | Ту                                        | p <sup>(1)</sup>         |       |     |     |  |

|-----------------|-------------------|---------------------------------|---------|-------------------------------------------|--------------------------|-------|-----|-----|--|

| Symbol          | Parameter         | er Conditions f <sub>HCLK</sub> |         | All peripherals<br>enabled <sup>(2)</sup> | All peripherals disabled | Unit  |     |     |  |

|                 |                   |                                 | 72 MHz  | 51                                        | 30.5                     |       |     |     |  |

|                 |                   |                                 | 48 MHz  | 34.6                                      | 20.7                     |       |     |     |  |

|                 |                   |                                 | 36 MHz  | 26.6                                      | 16.2                     |       |     |     |  |

|                 |                   |                                 | 24 MHz  | 18.5                                      | 11.4                     |       |     |     |  |

|                 |                   |                                 | 16 MHz  | 12.8                                      | 8.2                      |       |     |     |  |

|                 |                   | External clock <sup>(3)</sup>   | 8 MHz   | 7.2                                       | 5                        | mA    |     |     |  |

|                 |                   |                                 | 4 MHz   | 4.2                                       | 3.1                      |       |     |     |  |

|                 | Supply current in |                                 |         |                                           |                          | 2 MHz | 2.7 | 2.1 |  |

|                 |                   |                                 | 1 MHz   | 2                                         | 1.7                      |       |     |     |  |

|                 |                   |                                 | 500 kHz | 1.6                                       | 1.4                      |       |     |     |  |

|                 |                   |                                 | 125 kHz | 1.3                                       | 1.2                      |       |     |     |  |

| I <sub>DD</sub> | Run mode          |                                 | 64 MHz  | 45                                        | 27                       |       |     |     |  |

|                 |                   |                                 | 48 MHz  | 34                                        | 20.1                     |       |     |     |  |

|                 |                   |                                 | 36 MHz  | 26                                        | 15.6                     |       |     |     |  |

|                 |                   | Running on high                 | 24 MHz  | 17.9                                      | 10.8                     |       |     |     |  |

|                 |                   | speed internal RC               | 16 MHz  | 12.2                                      | 7.6                      |       |     |     |  |

|                 |                   | (HSI), AHB prescaler used to    | 8 MHz   | 6.6                                       | 4.4                      | mA    |     |     |  |

|                 |                   | reduce the                      | 4 MHz   | 3.6                                       | 2.5                      |       |     |     |  |

|                 |                   | frequency                       | 2 MHz   | 2.1                                       | 1.5                      |       |     |     |  |

|                 |                   |                                 | 1 MHz   | 1.4                                       | 1.1                      |       |     |     |  |

|                 |                   |                                 | 500 kHz | 1                                         | 0.8                      |       |     |     |  |

|                 |                   |                                 | 125 kHz | 0.7                                       | 0.6                      |       |     |     |  |

<sup>1.</sup> Typical values are measures at  $T_A$  = 25 °C,  $V_{DD}$  = 3.3 V.

<sup>3.</sup> External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

<sup>2.</sup> Add an additional power consumption of 0.8 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

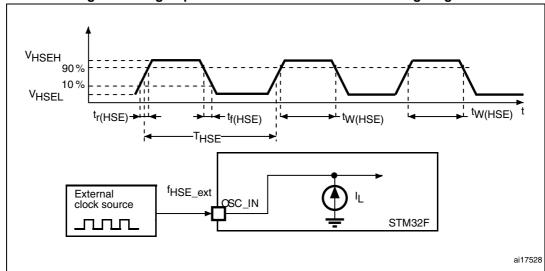

Figure 20. High-speed external clock source AC timing diagram

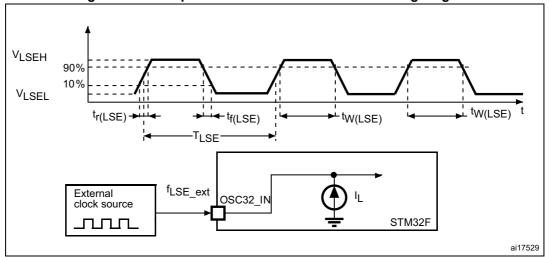

Figure 30. Synchronous non-multiplexed NOR/PSRAM read timings

Table 37. Synchronous non-multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup>

| Symbol                                                               | Parameter                                                           | Min  | Max | Unit |

|----------------------------------------------------------------------|---------------------------------------------------------------------|------|-----|------|

| t <sub>w(CLK)</sub>                                                  | FSMC_CLK period                                                     | 27.7 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>                                            | FSMC_CLK low to FSMC_NEx low (x = 02)                               | -    | 1.5 | ns   |

| t <sub>d(CLKL-NExH)</sub>                                            | FSMC_CLK low to FSMC_NEx high (x = 02)                              | 2    | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub>                                           | FSMC_CLK low to FSMC_NADV low                                       | -    | 4   | ns   |

| t <sub>d(CLKL-NADVH)</sub>                                           | FSMC_CLK low to FSMC_NADV high                                      | 5    | -   | ns   |

| t <sub>d(CLKL-AV)</sub>                                              | FSMC_CLK low to FSMC_Ax valid (x = 025)                             | -    | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>                                             | FSMC_CLK low to FSMC_Ax invalid (x = 025)                           | 4    | -   | ns   |

| t <sub>d(CLKL-NOEL)</sub>                                            | FSMC_CLK low to FSMC_NOE low                                        | -    | 1.5 | ns   |

| t <sub>d(CLKL-NOEH)</sub>                                            | FSMC_CLK low to FSMC_NOE high                                       | 1.5  | -   | ns   |

| t <sub>su(DV-CLKH)</sub>                                             | FSMC_D[15:0] valid data before FSMC_CLK high                        | 6.5  | -   | ns   |

| t <sub>h(CLKH-DV)</sub>                                              | t <sub>h(CLKH-DV)</sub> FSMC_D[15:0] valid data after FSMC_CLK high |      | -   | ns   |

| t <sub>su(NWAITV-CLKH)</sub> FSMC_NWAIT valid before FSMC_SMCLK high |                                                                     | 7    | -   | ns   |

| t <sub>h(CLKH-NWAITV)</sub>                                          | FSMC_NWAIT valid after FSMC_CLK high                                | 2    | -   | ns   |

<sup>1.</sup>  $C_L = 15 pF$ .

5

<sup>2.</sup> Guaranteed by characterization results.

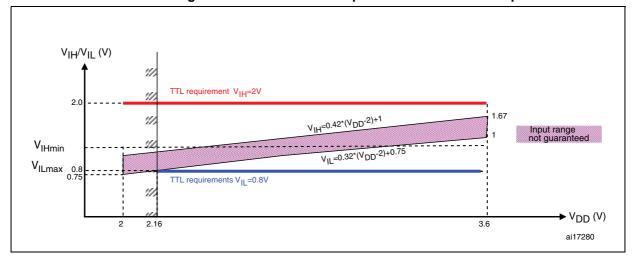

Figure 45. 5 V tolerant I/O input characteristics - TTL port

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with a relaxed  $V_{OL}/V_{OH}$ ) except PC13, PC14 and PC15 which can sink or source up to  $\pm 3$  mA. When using the GPIOs PC13 to PC15 in output mode, the speed should not exceed 2 MHz with a maximum load of 30 pF.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 5.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating I<sub>VDD</sub> (see *Table 8*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating I<sub>VSS</sub> (see *Table 8*).

#### Output voltage levels

Unless otherwise specified, the parameters given in *Table 47* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 10*. All I/Os are CMOS and TTL compliant.

| Symbol                         | Parameter                                                                     | Conditions                                                | Min                  | Max | Unit |  |

|--------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------|-----|------|--|

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at same time     |                                                           |                      | 0.4 | V    |  |

| V <sub>OH</sub> <sup>(2)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at same time | 2.7 V < V <sub>DD</sub> < 3.6 V                           | V <sub>DD</sub> -0.4 | -   | V    |  |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | CMOS port <sup>(3)</sup>                                  | -                    | 0.4 | V    |  |

| V <sub>OH</sub> <sup>(2)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at same time | I <sub>IO</sub> =+ 8mA<br>2.7 V < V <sub>DD</sub> < 3.6 V | 2.4                  | -   | V    |  |

Table 47. Output voltage characteristics

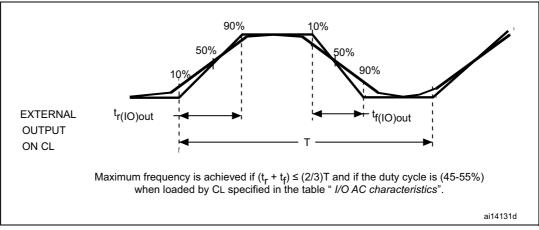

Figure 46. I/O AC characteristics definition

### 5.3.15 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor, R<sub>PU</sub> (see *Table 46*).

Unless otherwise specified, the parameters given in *Table 49* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 10*.

| Symbol                               | Parameter                                       | Conditions        | Min  | Тур | Max                  | Unit |

|--------------------------------------|-------------------------------------------------|-------------------|------|-----|----------------------|------|

| V <sub>IL(NRST)</sub> <sup>(1)</sup> | NRST Input low level voltage                    | -                 | -0.5 | -   | 0.8                  | V    |

| V <sub>IH(NRST)</sub> <sup>(1)</sup> | NRST Input high level voltage                   | -                 | 2    | -   | V <sub>DD</sub> +0.5 | V    |

| V <sub>hys(NRST)</sub>               | NRST Schmitt trigger voltage hysteresis         | -                 | -    | 200 | -                    | mV   |

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(2)</sup> | $V_{IN} = V_{SS}$ | 30   | 40  | 50                   | kΩ   |

| V <sub>F(NRST)</sub> <sup>(1)</sup>  | NRST Input filtered pulse                       | -                 | -    | -   | 100                  | ns   |

| V <sub>NF(NRST)</sub> <sup>(1)</sup> | NRST Input not filtered pulse                   | -                 | 300  | -   | -                    | ns   |

Table 49. NRST pin characteristics

<sup>1.</sup> Guaranteed by design.

<sup>2.</sup> The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance must be minimum (~10% order).

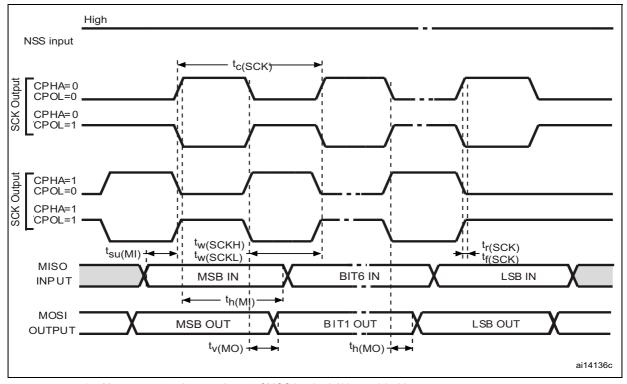

Figure 51. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

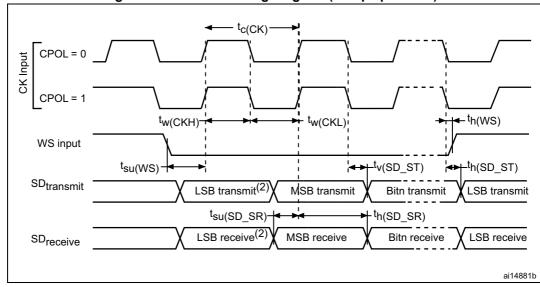

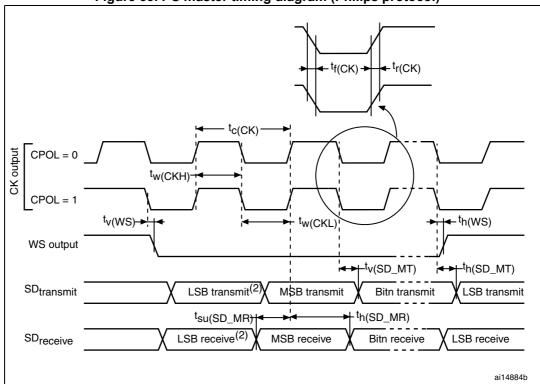

Figure 52. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Measurement points are done at CMOS levels: 0.3  $\times$  V<sub>DD</sub> and 0.7  $\times$  V<sub>DD</sub>.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

Figure 53. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Guaranteed by characterization results.

- LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

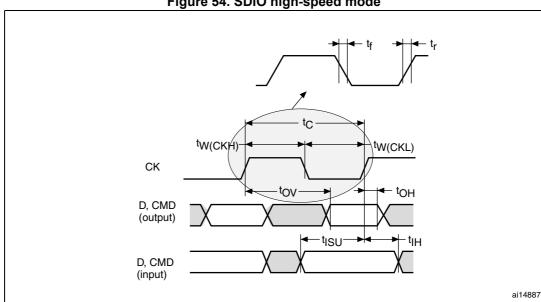

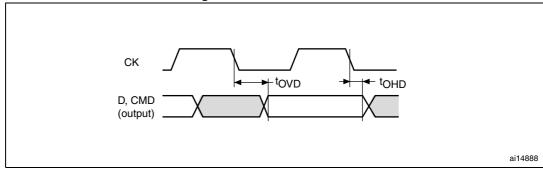

### SD/SDIO MMC card host interface (SDIO) characteristics

Unless otherwise specified, the parameters given in *Table 55* are derived from tests performed under ambient temperature, f<sub>PCLKx</sub> frequency and V<sub>DD</sub> supply voltage conditions summarized in Table 10.

Refer to Section 5.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (D[7:0], CMD, CK).

Figure 54. SDIO high-speed mode

Figure 55. SD default mode

Table 55. SD / MMC characteristics

| Symbol          | Parameter                                 | Conditions             | Min | Max | Unit |

|-----------------|-------------------------------------------|------------------------|-----|-----|------|

| f <sub>PP</sub> | Clock frequency in data transfer mode     | C <sub>L</sub> ≤ 30 pF | 0   | 48  | MHz  |

| tW(CKL)         | Clock low time, f <sub>PP</sub> = 16 MHz  | C <sub>L</sub> ≤ 30 pF | 32  | -   |      |

| tW(CKH)         | Clock high time, f <sub>PP</sub> = 16 MHz | C <sub>L</sub> ≤ 30 pF | 30  | -   | no   |

| t <sub>r</sub>  | Clock rise time                           | C <sub>L</sub> ≤ 30 pF | -   | 4   | ns   |

| t <sub>f</sub>  | Clock fall time                           | C <sub>L</sub> ≤ 30 pF | -   | 5   |      |

| Symbol | Parameter                    | Test conditions                                                                     | Тур  | Max <sup>(4)</sup> | Unit |  |  |  |  |  |

|--------|------------------------------|-------------------------------------------------------------------------------------|------|--------------------|------|--|--|--|--|--|

| ET     | Total unadjusted error       | f - FC MUL                                                                          | ±2   | ±5                 |      |  |  |  |  |  |

| EO     | Offset error                 | f <sub>PCLK2</sub> = 56 MHz,<br>f <sub>ADC</sub> = 14 MHz, R <sub>AIN</sub> < 10 kΩ | ±1.5 | ±2.5               |      |  |  |  |  |  |

| EG     | Gain error                   | V <sub>DDA</sub> = 2.4 V to 3.6 V                                                   | ±1.5 | ±3                 | LSB  |  |  |  |  |  |

| ED     | Differential linearity error | Measurements made after ADC calibration                                             | ±1   | ±2                 |      |  |  |  |  |  |

| EL     | Integral linearity error     | , is a comprant                                                                     | ±1.5 | ±3                 |      |  |  |  |  |  |

Table 62. ADC accuracy<sup>(1)</sup> (2)(3)

- 1. ADC DC accuracy values are measured after internal calibration.

- 2. Better performance could be achieved in restricted  $V_{DD}$ , frequency,  $V_{REF}$  and temperature ranges.

- ADC Accuracy vs. Negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current. Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 5.3.14 does not affect the ADC accuracy.

- Guaranteed by characterization results.

$\frac{V_{DDA}}{V_{DDA}}$  depending on package)] E<sub>G</sub> 4095 4094 4093 6 5 3  $E_{D}$ 2 1L SB<sub>IDEAL</sub> 0 456 4093 4094 4095 4096 VDDA VSSA ai14395c

Figure 57. ADC accuracy characteristics

- 1. Example of an actual transfer curve.

- 2. Ideal transfer curve.

- End point correlation line.

- ET = Total Unadjusted Error: maximum deviation between the actual and the ideal transfer curves. EO = Offset Errór: deviation between the first actual transition and the first ideal one.

- EG = Gain Error: deviation between the last ideal transition and the last actual one.

- ED = Differential Linearity Error: maximum deviation between actual steps and the ideal one. EL = Integral Linearity Error: maximum deviation between any actual transition and the end point correlation line.

# 5.3.20 DAC electrical specifications

Table 63. DAC characteristics

| Symbol                           | Parameter                                                                                                    | Min | Тур | Max                      | Unit | Comments                                                                                                               |

|----------------------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|--------------------------|------|------------------------------------------------------------------------------------------------------------------------|

| V <sub>DDA</sub>                 | Analog supply voltage                                                                                        | 2.4 | -   | 3.6                      | ٧    | -                                                                                                                      |

| V <sub>REF+</sub>                | Reference supply voltage                                                                                     | 2.4 | -   | 3.6                      | V    | V <sub>REF+</sub> must always be below V <sub>DDA</sub>                                                                |

| V <sub>SSA</sub>                 | Ground                                                                                                       | 0   | -   | 0                        | V    | -                                                                                                                      |

| R <sub>LOAD</sub> <sup>(1)</sup> | Resistive load with buffer ON                                                                                | 5   | -   | -                        | kΩ   | -                                                                                                                      |

| R <sub>O</sub> <sup>(2)</sup>    | Impedance output with buffer<br>OFF                                                                          | -   | -   | 15                       | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is 1.5 $M\Omega$ |

| C <sub>LOAD</sub> <sup>(1)</sup> | Capacitive load                                                                                              | -   | -   | 50                       | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                        |

| DAC_OUT                          | Lower DAC_OUT voltage with buffer ON                                                                         | 0.2 | -   | -                        | ٧    | It gives the maximum output excursion of the DAC.  It corresponds to 12-bit input code                                 |

| DAC_OUT<br>max <sup>(1)</sup>    | Higher DAC_OUT voltage with buffer ON                                                                        | -   | -   | V <sub>DDA</sub> - 0.2   | ٧    | (0x0E0) to (0xF1C) at $V_{REF+}$ = 3.6 V and (0x155) and (0xEAB) at $V_{REF+}$ = 2.4 V                                 |

| DAC_OUT min <sup>(1)</sup>       | Lower DAC_OUT voltage with buffer OFF                                                                        | -   | 0.5 | -                        | mV   | It gives the maximum output                                                                                            |

| DAC_OUT max <sup>(1)</sup>       | Higher DAC_OUT voltage with buffer OFF                                                                       | ı   | -   | V <sub>REF+</sub> – 1LSB | V    | excursion of the DAC.                                                                                                  |

| I <sub>DDVREF+</sub>             | DAC DC current consumption in quiescent mode (Standby mode)                                                  | i   | -   | 220                      | μΑ   | With no load, worst code (0xF1C) at V <sub>REF+</sub> = 3.6 V in terms of DC consumption on the inputs                 |

|                                  | DAC DC current                                                                                               | -   | -   | 380                      | μA   | With no load, middle code (0x800) on the inputs                                                                        |

| I <sub>DDA</sub>                 | consumption in quiescent mode <sup>(3)</sup>                                                                 | -   | -   | 480                      | μA   | With no load, worst code (0xF1C) at V <sub>REF+</sub> = 3.6 V in terms of DC consumption on the inputs                 |

| DNL <sup>(4)</sup>               | Differential non linearity Difference between two                                                            | -   | -   | ±0.5                     | LSB  | Given for the DAC in 10-bit configuration                                                                              |

|                                  | consecutive code-1LSB)                                                                                       | -   | -   | ±2                       | LSB  | Given for the DAC in 12-bit configuration                                                                              |

|                                  | Integral non linearity<br>(difference between                                                                | -   | -   | ±1                       | LSB  | Given for the DAC in 10-bit configuration                                                                              |

| INL <sup>(3)</sup>               | measured value at Code i<br>and the value at Code i on a<br>line drawn between Code 0<br>and last Code 1023) | -   | -   | ±4                       | LSB  | Given for the DAC in 12-bit configuration                                                                              |

# 6 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK<sup>®</sup> is an ST trademark.

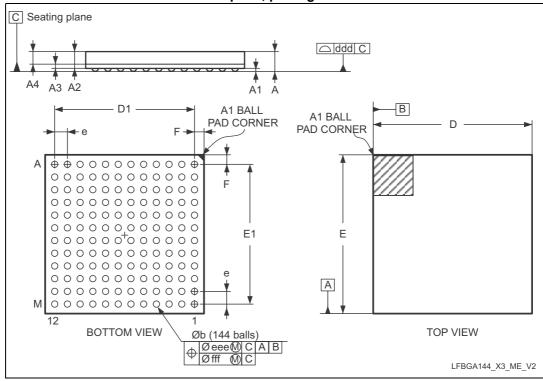

# 6.1 LFBGA144 package information

Figure 62. LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm, 0.8 mm pitch, package outline

1. Drawing is not to scale.

Table 65. LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm, 0.8 mm pitch, package mechanical data

| Symbol           |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|------------------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol           | Min   | Тур         | Max   | Тур    | Min                   | Max    |

| A <sup>(2)</sup> | -     | -           | 1.700 | -      | -                     | 0.0669 |

| A1               | 0.250 | 0.300       | 0.350 | 0.098  | 0.0118                | 0.0138 |

| A2               | 0.810 | 0.910       | 1.010 | 0.0319 | 0.0358                | 0.0398 |

| A3               | 0.225 | 0.26        | 0.295 | 0.0089 | 0.0102                | 0.0116 |

| A4               | 0.585 | 0.650       | 0.715 | 0.0230 | 0.0256                | 0.0281 |

Table 67. LFBGA100 - 10 x 10 mm low profile fine pitch ball grid array package mechanical data

| Symbol | millimeters |     |       | inches <sup>(1)</sup> |     |        |

|--------|-------------|-----|-------|-----------------------|-----|--------|

|        | Min         | Тур | Max   | Min                   | Тур | Max    |

| eee    | -           | -   | 0.150 | -                     | -   | 0.0059 |

| fff    | -           | -   | 0.080 | -                     | -   | 0.0031 |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

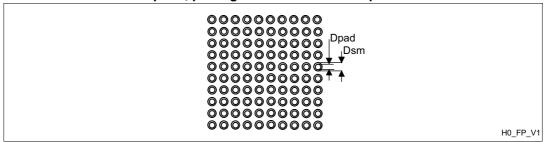

Figure 66. LFBGA100 – 100-ball low profile fine pitch ball grid array, 10 x 10 mm, 0.8 mm pitch, package recommended footprintoutline

Table 68. LFBGA100 recommended PCB design rules (0.8 mm pitch BGA)

| Dimension         | Recommended values                                               |  |  |

|-------------------|------------------------------------------------------------------|--|--|

| Pitch             | 0.8                                                              |  |  |

| Dpad              | 0.500 mm                                                         |  |  |

| Dsm               | 0.570 mm typ. (depends on the soldermask registration tolerance) |  |  |

| Stencil opening   | 0.500 mm                                                         |  |  |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                    |  |  |

| Pad trace width   | 0.120 mm                                                         |  |  |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics - All rights reserved