Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT          |

| Number of I/O              | 51                                                                    |

| Program Memory Size        | 512KB (512K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 64K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f103ret6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of figures

| Figure 1.  | STM32F103xC, STM32F103xD and STM32F103xE performance line block diagram 12  |

|------------|-----------------------------------------------------------------------------|

| Figure 2.  | Clock tree                                                                  |

| Figure 3.  | STM32F103xC/D/E BGA144 ballout                                              |

| Figure 4.  | STM32F103xC/D/E performance line BGA100 ballout                             |

| Figure 5.  | STM32F103xC/D/E performance line LQFP144 pinout                             |

| Figure 6.  | STM32F103xC/D/E performance line LQFP100 pinout                             |

| Figure 7.  | STM32F103xC/D/E performance line LQFP64 pinout                              |

| Figure 8.  | STM32F103xC/D/E performance line                                            |

|            | WLCSP64 ballout, ball side                                                  |

| Figure 9.  | Memory map                                                                  |

| Figure 10. | Pin loading conditions                                                      |

| Figure 11. | Pin input voltage                                                           |

| Figure 12. | Power supply scheme                                                         |

| Figure 13. | Current consumption measurement scheme                                      |

| Figure 14. | Typical current consumption in Run mode versus frequency (at 3.6 V) -       |

|            | code with data processing running from RAM, peripherals enabled             |

| Figure 15. | Typical current consumption in Run mode versus frequency (at 3.6 V)-        |

|            | code with data processing running from RAM, peripherals disabled            |

| Figure 16. | Typical current consumption on V <sub>BAT</sub> with RTC on vs. temperature |

| -          | at different V <sub>BAT</sub> values                                        |

| Figure 17. | Typical current consumption in Stop mode with regulator in run mode         |

| -          | versus temperature at different V <sub>DD</sub> values                      |

| Figure 18. | Typical current consumption in Stop mode with regulator in low-power        |

| -          | mode versus temperature at different V <sub>DD</sub> values                 |

| Figure 19. | Typical current consumption in Standby mode versus temperature at           |

|            | different V <sub>DD</sub> values                                            |

| Figure 20. | High-speed external clock source AC timing diagram                          |

| Figure 21. | Low-speed external clock source AC timing diagram                           |

| Figure 22. | Typical application with an 8 MHz crystal                                   |

| Figure 23. | Typical application with a 32.768 kHz crystal                               |

| Figure 24. | Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms                  |

| Figure 25. | Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms                 |

| Figure 26. | Asynchronous multiplexed PSRAM/NOR read waveforms                           |

| Figure 27. | Asynchronous multiplexed PSRAM/NOR write waveforms                          |

| Figure 28. | Synchronous multiplexed NOR/PSRAM read timings                              |

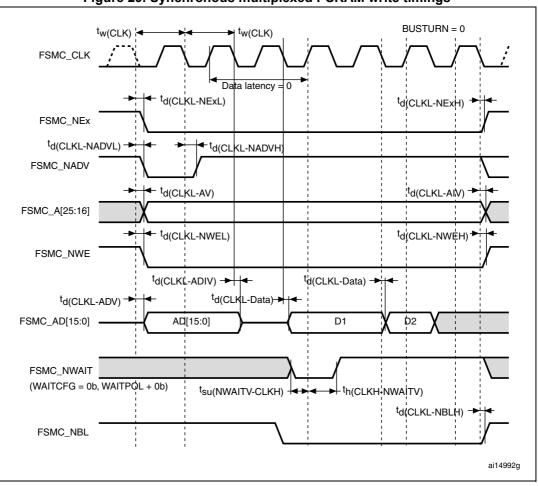

| Figure 29. | Synchronous multiplexed PSRAM write timings                                 |

| Figure 30. | Synchronous non-multiplexed NOR/PSRAM read timings                          |

| Figure 31. | Synchronous non-multiplexed PSRAM write timings                             |

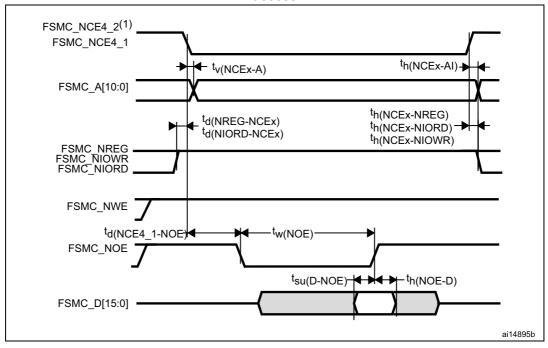

| Figure 32. | PC Card/CompactFlash controller waveforms for common memory read access     |

| Figure 33. | PC Card/CompactFlash controller waveforms for common memory write access    |

| Figure 34. | PC Card/CompactFlash controller waveforms for attribute memory read         |

| -          | access                                                                      |

| Figure 35. | PC Card/CompactFlash controller waveforms for attribute memory write        |

| U          | access                                                                      |

| Figure 36. | PC Card/CompactFlash controller waveforms for I/O space read access         |

| Figure 37. | PC Card/CompactFlash controller waveforms for I/O space write access        |

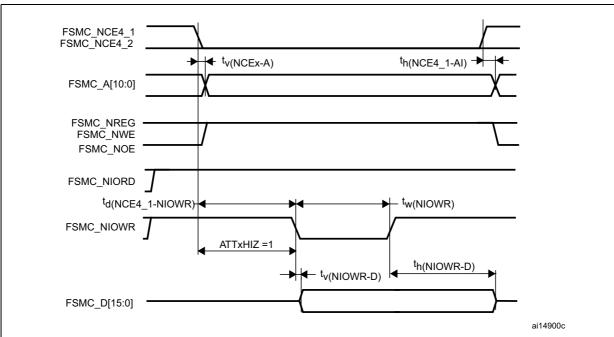

| Figure 38. | NAND controller waveforms for read access                                   |

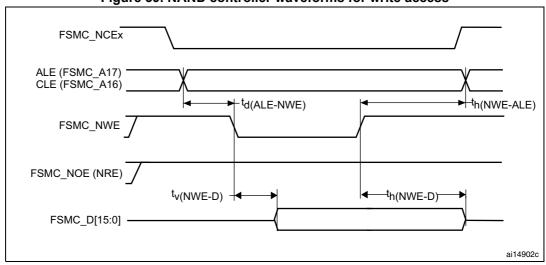

| Figure 39. | NAND controller waveforms for write access                                  |

## 2.1 Device overview

The STM32F103xC/D/E high-density performance line family offers devices in six different package types: from 64 pins to 144 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

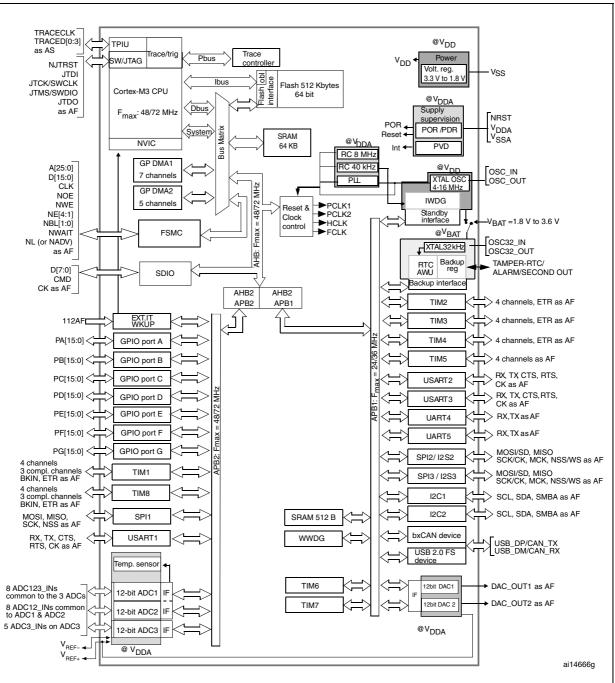

*Figure 1* shows the general block diagram of the device family.

|                    | and peripheral counts                |                                                                                                                            |         |      |             |                    |       |             |         |       |  |

|--------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------|------|-------------|--------------------|-------|-------------|---------|-------|--|

| I                  | Peripherals                          | STM                                                                                                                        | 32F103I | ٦x   | STM32F103Vx |                    |       | STM32F103Zx |         |       |  |

| Flash m            | emory in Kbytes                      | 256                                                                                                                        | 384     | 512  | 256         | 384                | 512   | 256         | 384     | 512   |  |

| SRAM i             | n Kbytes                             | 48                                                                                                                         | 64      | (1)  | 48          | 64                 |       | 48          | 64      |       |  |

| FSMC               |                                      |                                                                                                                            | No      |      |             | Yes <sup>(2)</sup> |       |             | Yes     |       |  |

|                    | General-purpose                      |                                                                                                                            |         |      |             | 4                  |       |             |         |       |  |

| Timers             | Advanced-control                     |                                                                                                                            |         |      |             | 2                  |       |             |         |       |  |

|                    | Basic                                |                                                                                                                            | 2       |      |             |                    |       |             |         |       |  |

|                    | SPI(I <sup>2</sup> S) <sup>(3)</sup> |                                                                                                                            |         |      | ;           | 3(2)               |       |             |         |       |  |

|                    | l <sup>2</sup> C                     |                                                                                                                            | 2       |      |             |                    |       |             |         |       |  |

|                    | USART                                | 5                                                                                                                          |         |      |             |                    |       |             |         |       |  |

| Comm               | USB                                  | 1                                                                                                                          |         |      |             |                    |       |             |         |       |  |

|                    | CAN                                  | 1                                                                                                                          |         |      |             |                    |       |             |         |       |  |

|                    | SDIO                                 |                                                                                                                            |         |      |             | 1                  |       |             |         |       |  |

| GPIOs              |                                      | 51 80                                                                                                                      |         |      |             | 112                |       |             |         |       |  |

| 12-bit A<br>Number | DC<br>of channels                    | 3 3<br>16 16                                                                                                               |         |      | 3<br>21     |                    |       |             |         |       |  |

| 12-bit D<br>Number | AC<br>of channels                    | 2 2                                                                                                                        |         |      |             |                    |       |             |         |       |  |

| CPU frequency      |                                      | 72 MHz                                                                                                                     |         |      |             |                    |       |             |         |       |  |

| Operating voltage  |                                      | 2.0 to 3.6 V                                                                                                               |         |      |             |                    |       |             |         |       |  |

| Operatir           | ng temperatures                      | Ambient temperatures: -40 to +85 °C /-40 to +105 °C (see Table 10)<br>Junction temperature: -40 to + 125 °C (see Table 10) |         |      |             |                    |       |             |         |       |  |

| Package            | e                                    | LQFP6                                                                                                                      | 4, WLCS | SP64 | LQFP        | 100, BG            | GA100 | LQFP        | 144, BC | GA144 |  |

|                    |                                      |                                                                                                                            |         |      |             |                    |       |             |         |       |  |

| Table 2. STM32F103xC, STM32F103xD and STM32F103xE features |

|------------------------------------------------------------|

| and peripheral counts                                      |

1. 64 KB RAM for 256 KB Flash are available on devices delivered in CSP packages only.

For the LQFP100 and BGA100 packages, only FSMC Bank1 and Bank2 are available. Bank1 can only support a multiplexed NOR/PSRAM memory using the NE1 Chip Select. Bank2 can only support a 16- or 8-bit NAND Flash memory using the NCE2 Chip Select. The interrupt line cannot be used since Port G is not available in this package.

3. The SPI2 and SPI3 interfaces give the flexibility to work in an exclusive way in either the SPI mode or the  $I^2S$  audio mode.

# Figure 1. STM32F103xC, STM32F103xD and STM32F103xE performance line block diagram

1.  $T_A = -40$  °C to +85 °C (suffix 6, see *Table* 75) or -40 °C to +105 °C (suffix 7, see *Table* 75), junction temperature up to 105 °C or 125 °C, respectively.

2. AF = alternate function on I/O port pin.9

## 2.2 Full compatibility throughout the family

The STM32F103xC/D/E is a complete family whose members are fully pin-to-pin, software and feature compatible. In the reference manual, the STM32F103x4 and STM32F103x6 are identified as low-density devices, the STM32F103x8 and STM32F103xB are referred to as medium-density devices and the STM32F103xC, STM32F103xD and STM32F103xE are referred to as high-density devices.

Low-density and high-density devices are an extension of the STM32F103x8/B mediumdensity devices, they are specified in the STM32F103x4/6 and STM32F103xC/D/E datasheets, respectively. Low-density devices feature lower Flash memory and RAM capacities, less timers and peripherals. High-density devices have higher Flash memory and RAM capacities, and additional peripherals like SDIO, FSMC, I<sup>2</sup>S and DAC while remaining fully compatible with the other members of the family.

The STM32F103x4, STM32F103x6, STM32F103xC, STM32F103xD and STM32F103xE are a drop-in replacement for the STM32F103x8/B devices, allowing the user to try different memory densities and providing a greater degree of freedom during the development cycle.

Moreover, the STM32F103xx performance line family is fully compatible with all existing STM32F101xx access line and STM32F102xx USB access line devices.

|        | Low-dens                                                               | ity devices                   | Medium-den                                            | sity devices    | High-density devices                                                             |           |                 |  |

|--------|------------------------------------------------------------------------|-------------------------------|-------------------------------------------------------|-----------------|----------------------------------------------------------------------------------|-----------|-----------------|--|

| Pinout | 16 KB<br>Flash                                                         | 32 KB<br>Flash <sup>(1)</sup> | 64 KB<br>Flash                                        | 128 KB<br>Flash |                                                                                  |           | 512 KB<br>Flash |  |

|        | 6 KB RAM                                                               | M 10 KB RAM 20 KB RAM 20 KB   |                                                       | 20 KB RAM       | 48 RAM                                                                           | 64 KB RAM |                 |  |

| 144    |                                                                        |                               |                                                       |                 | 5 × USARTs                                                                       |           |                 |  |

| 100    |                                                                        |                               | 3 × USARTs                                            |                 | 4 × 16-bit timers, 2 × basic timers<br>3 × SPIs, 2 × I <sup>2</sup> Ss, 2 × I2Cs |           |                 |  |

| 64     | 2 × USARTs<br>2 × 16-bit timers<br>1 × SPI, 1 × I <sup>2</sup> C, USB, |                               | $ \begin{array}{llllllllllllllllllllllllllllllllllll$ |                 | × DACs, 1 × 3                                                                    | SDIO      |                 |  |

| 48     | CAN, 1 × PWM timer                                                     |                               | 2 × ADCs                                              |                 |                                                                                  |           |                 |  |

| 36     | 2 × ADCs                                                               |                               |                                                       |                 | 1                                                                                |           |                 |  |

Table 3. STM32F103xx family

For orderable part numbers that do not show the A internal code after the temperature range code (6 or 7), the reference datasheet for electrical characteristics is that of the STM32F103x8/B medium-density devices.

2. Ports F and G are not available in devices delivered in 100-pin packages.

## 2.3 Overview

# 2.3.1 ARM<sup>®</sup> Cortex<sup>®</sup>-M3 core with embedded Flash and SRAM

The ARM Cortex<sup>®</sup>-M3 processor is the latest generation of ARM processors for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM Cortex<sup>®</sup>-M3 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

With its embedded ARM core, STM32F103xC, STM32F103xD and STM32F103xE performance line family is compatible with all ARM tools and software.

*Figure 1* shows the general block diagram of the device family.

### 2.3.2 Embedded Flash memory

Up to 512 Kbytes of embedded Flash is available for storing programs and data.

#### 2.3.3 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

#### 2.3.4 Embedded SRAM

Up to 64 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states.

#### 2.3.5 FSMC (flexible static memory controller)

The FSMC is embedded in the STM32F103xC, STM32F103xD and STM32F103xE performance line family. It has four Chip Select outputs supporting the following modes: PC Card/Compact Flash, SRAM, PSRAM, NOR and NAND.

Functionality overview:

- The three FSMC interrupt lines are ORed in order to be connected to the NVIC

- Write FIFO

- Code execution from external memory except for NAND Flash and PC Card

- The targeted frequency, f<sub>CLK</sub>, is HCLK/2, so external access is at 36 MHz when HCLK is at 72 MHz and external access is at 24 MHz when HCLK is at 48 MHz

### 2.3.28 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 2 V <  $V_{DDA}$  < 3.6 V. The temperature sensor is internally connected to the ADC1\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

## 2.3.29 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP Interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target. The JTAG TMS and TCK pins are shared respectively with SWDIO and SWCLK and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

#### 2.3.30 Embedded Trace Macrocell™

The ARM<sup>®</sup> Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F10xxx through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or any other high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer running debugger software. TPA hardware is commercially available from common development tool vendors. It operates with third party debugger software tools.

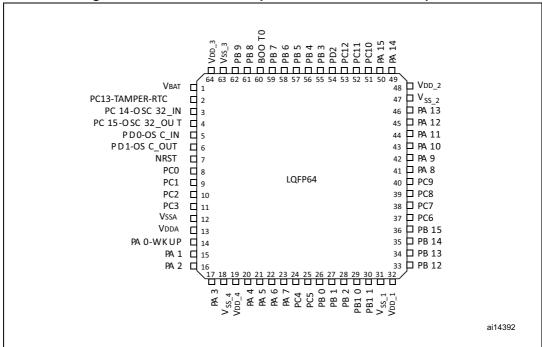

Figure 7. STM32F103xC/D/E performance line LQFP64 pinout

1. The above figure shows the package top view.

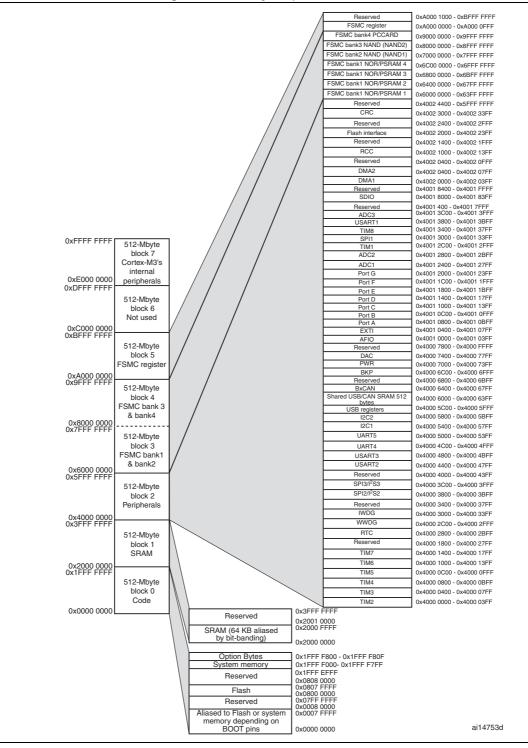

## 4 Memory mapping

The memory map is shown in Figure 9.

Figure 9. Memory map

#### 5.3.4 Embedded reference voltage

The parameters given in *Table 13* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 10*.

|                                                                                                       |                                                                     |                                   |      | -    |                     |        |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------|------|------|---------------------|--------|

| Symbol                                                                                                | Parameter                                                           | Conditions                        | Min  | Тур  | Мах                 | Unit   |

| V                                                                                                     | Internal reference voltage                                          | –40 °C < T <sub>A</sub> < +105 °C | 1.16 | 1.20 | 1.26                | V      |

| V <sub>REFINT</sub>                                                                                   | Internal reference voltage                                          | –40 °C < T <sub>A</sub> < +85 °C  | 1.16 | 1.20 | 1.24                | v      |

| T <sub>S_vrefint</sub> <sup>(1)</sup>                                                                 | ADC sampling time when<br>reading the internal reference<br>voltage | -                                 | -    | 5.1  | 17.1 <sup>(2)</sup> | μs     |

| V <sub>RERINT</sub> <sup>(2)</sup> Internal reference voltage<br>spread over the temperature<br>range |                                                                     | V <sub>DD</sub> = 3 V ±10 mV      | -    | -    | 10                  | mV     |

| T <sub>Coeff</sub> <sup>(2)</sup>                                                                     | Temperature coefficient                                             | -                                 | -    | -    | 100                 | ppm/°C |

1. Shortest sampling time can be determined in the application by multiple iterations.

2. Guaranteed by design.

#### 5.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 13: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to Dhrystone 2.1 code.

#### Maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time is adjusted to the f<sub>HCLK</sub> frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 48 MHz and 2 wait states above)

- Prefetch in ON (reminder: this bit must be set before clock setting and bus prescaling)

- When the peripherals are enabled f<sub>PCLK1</sub> = f<sub>HCLK</sub>/2, f<sub>PCLK2</sub> = f<sub>HCLK</sub>

The parameters given in *Table 14*, *Table 15* and *Table 16* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 10*.

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 24*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

|                                     |                                                                                                         |                                                                                           | <b>,</b>                |     |     |     |      |

|-------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------|-----|-----|-----|------|

| Symbol                              | Parameter                                                                                               | C                                                                                         | Conditions              | Min | Тур | Max | Unit |

| R <sub>F</sub>                      | Feedback resistor                                                                                       |                                                                                           | -                       | -   | 5   | -   | MΩ   |

| C <sup>(2)</sup>                    | Recommended load capacitance<br>versus equivalent serial<br>resistance of the crystal (R <sub>S</sub> ) | R <sub>S</sub> = 30 kΩ<br>V <sub>DD</sub> = 3.3 V, V <sub>IN</sub> = V <sub>SS</sub><br>- |                         | -   | -   | 15  | pF   |

| I <sub>2</sub>                      | LSE driving current                                                                                     |                                                                                           |                         | -   | -   | 1.4 | μA   |

| 9 <sub>m</sub>                      | Oscillator transconductance                                                                             |                                                                                           |                         | 5   | -   | -   | μA/V |

|                                     |                                                                                                         | V <sub>DD</sub> is<br>stabilized                                                          | T <sub>A</sub> = 50 °C  | -   | 1.5 | -   | - S  |

|                                     | Startup time                                                                                            |                                                                                           | T <sub>A</sub> = 25 °C  | -   | 2.5 | -   |      |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> |                                                                                                         |                                                                                           | T <sub>A</sub> = 10 °C  | -   | 4   | -   |      |

|                                     |                                                                                                         |                                                                                           | T <sub>A</sub> = 0 °C   | -   | 6   | -   |      |

|                                     |                                                                                                         |                                                                                           | T <sub>A</sub> = -10 °C | -   | 10  | -   |      |

|                                     |                                                                                                         |                                                                                           | T <sub>A</sub> = -20 °C | -   | 17  | -   |      |

|                                     |                                                                                                         |                                                                                           | T <sub>A</sub> = -30 °C | -   | 32  | -   |      |

|                                     |                                                                                                         |                                                                                           | T <sub>A</sub> = -40 °C | -   | 60  | -   |      |

| Table 24. LSE oscillator characteristics $(f_{LSE} = 32.768 \text{ kHz})^{(1)(2)}$ | ) |

|------------------------------------------------------------------------------------|---|

|------------------------------------------------------------------------------------|---|

1. Guaranteed by characterization results.

Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) until a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer, PCB layout and humidity.

**Caution:** To avoid exceeding the maximum value of  $C_{L1}$  and  $C_{L2}$  (15 pF) it is strongly recommended to use a resonator with a load capacitance  $C_L \le 7$  pF. Never use a resonator with a load capacitance of 12.5 pF. **Example:** if you choose a resonator with a load capacitance of  $C_L = 6$  pF, and  $C_{stray} = 2$  pF, then  $C_{L1} = C_{L2} = 8$  pF.

Note: For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality ceramic capacitors in the 5 pF to 15 pF range selected to match the requirements of the crystal or resonator (see Figure 23).  $C_{L1}$  and  $C_{L2}$ , are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . Load capacitance  $C_L$  has the following formula:  $C_L = C_{L1} \times C_{L2} / (C_{L1} + C_{L2}) + C_{stray}$  where  $C_{stray}$  is the pin capacitance and board or trace PCB-related capacitance. Typically, it is between 2 pF and 7 pF.

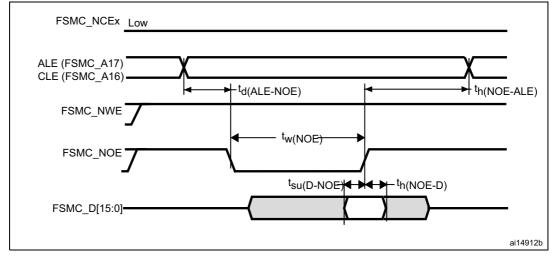

## 5.3.10 FSMC characteristics

#### Asynchronous waveforms and timings

*Figure 24* through *Figure 27* represent asynchronous waveforms and *Table 31* through *Table 34* provide the corresponding timings. The results shown in these tables are obtained with the following FSMC configuration:

- AddressSetupTime = 0

- AddressHoldTime = 1

- DataSetupTime = 1

#### Figure 24. Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms

1. Mode 2/B, C and D only. In Mode 1, FSMC\_NADV is not used.

Figure 29. Synchronous multiplexed PSRAM write timings

#### PC Card/CompactFlash controller waveforms and timings

*Figure 32* through *Figure 37* represent synchronous waveforms and *Table 39* provides the corresponding timings. The results shown in this table are obtained with the following FSMC configuration:

- COM.FSMC\_SetupTime = 0x04;

- COM.FSMC\_WaitSetupTime = 0x07;

- COM.FSMC\_HoldSetupTime = 0x04;

- COM.FSMC\_HiZSetupTime = 0x00;

- ATT.FSMC\_SetupTime = 0x04;

- ATT.FSMC\_WaitSetupTime = 0x07;

- ATT.FSMC\_HoldSetupTime = 0x04;

- ATT.FSMC HiZSetupTime = 0x00;

- IO.FSMC\_SetupTime = 0x04;

- IO.FSMC\_WaitSetupTime = 0x07;

- IO.FSMC HoldSetupTime = 0x04;

- IO.FSMC\_HiZSetupTime = 0x00;

- TCLRSetupTime = 0;

- TARSetupTime = 0;

# Figure 32. PC Card/CompactFlash controller waveforms for common memory read access

#### 1. FSMC\_NCE4\_2 remains high (inactive during 8-bit access.

Figure 37. PC Card/CompactFlash controller waveforms for I/O space write access

|  | Table 39. Switchin | g characteristics for PC Card/CF read | and write cycles <sup>(1)(2)</sup> |

|--|--------------------|---------------------------------------|------------------------------------|

|--|--------------------|---------------------------------------|------------------------------------|

| Symbol                                                    | Parameter                                                                                                                   | Min                     | Max                      | Unit |

|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------|------|

| t <sub>v(NCEx-A)</sub><br>t <sub>v(NCE4_1-A)</sub>        | FSMC_NCEx low (x = 4_1/4_2) to FSMC_Ay valid (y = 010) FSMC_NCE4_1 low (x = 4_1/4_2) to FSMC_Ay valid (y = 010)             | -                       | 0                        | ns   |

| t <sub>h(NCEx-AI)</sub><br>t <sub>h(NCE4_1-AI)</sub>      | FSMC_NCEx high (x = $4_1/4_2$ ) to FSMC_Ax invalid (x = 010) FSMC_NCE4_1 high (x = $4_1/4_2$ ) to FSMC_Ax invalid (x = 010) | 2.5                     | -                        | ns   |

| t <sub>d(NREG-NCEx)</sub><br>t <sub>d(NREG-NCE4_1)</sub>  | FSMC_NCEx low to FSMC_NREG valid FSMC_NCE4_1 low to FSMC_NREG valid                                                         | -                       | 5                        | ns   |

| t <sub>h(NCEx-NREG)</sub><br>t <sub>h(NCE4_</sub> 1-NREG) | FSMC_NCEx high to FSMC_NREG invalid FSMC_NCE4_1 high to FSMC_NREG invalid                                                   | t <sub>HCLK</sub> + 3   | -                        | ns   |

| t <sub>d(NCE4_1-NOE)</sub>                                | FSMC_NCE4_1 low to FSMC_NOE low                                                                                             | -                       | 5t <sub>HCLK</sub> + 2   | ns   |

| t <sub>w(NOE)</sub>                                       | FSMC_NOE low width                                                                                                          | 8t <sub>HCLK</sub> –1.5 | 8t <sub>HCLK</sub> + 1   | ns   |

| t <sub>d(NOE-NCE4_1</sub>                                 | FSMC_NOE high to FSMC_NCE4_1 high                                                                                           | 5t <sub>HCLK</sub> + 2  | -                        | ns   |

| t <sub>su(D-NOE)</sub>                                    | FSMC_D[15:0] valid data before FSMC_NOE high                                                                                | 25                      | -                        | ns   |

| t <sub>h(NOE-D)</sub>                                     | FSMC_D[15:0] valid data after FSMC_NOE high                                                                                 | 15                      | -                        | ns   |

| t <sub>w(NWE)</sub>                                       | FSMC_NWE low width                                                                                                          | 8t <sub>HCLK</sub> – 1  | 8t <sub>HCLK</sub> + 2   | ns   |

| t <sub>d(NWE-NCE4_1)</sub>                                | FSMC_NWE high to FSMC_NCE4_1 high                                                                                           | 5t <sub>HCLK</sub> + 2  | -                        | ns   |

| t <sub>d(NCE4_1-NWE)</sub>                                | FSMC_NCE4_1 low to FSMC_NWE low                                                                                             | -                       | 5t <sub>HCLK</sub> + 1.5 | ns   |

| t <sub>v(NWE-D)</sub>                                     | FSMC_NWE low to FSMC_D[15:0] valid                                                                                          | -                       | 0                        | ns   |

| t <sub>h(NWE-D)</sub>                                     | FSMC_NWE high to FSMC_D[15:0] invalid                                                                                       | 11t <sub>HCLK</sub>     | -                        | ns   |

| t <sub>d(D-NWE)</sub>                                     | FSMC_D[15:0] valid before FSMC_NWE high                                                                                     | 13t <sub>HCLK</sub>     | -                        | ns   |

Figure 39. NAND controller waveforms for write access

Figure 40. NAND controller waveforms for common memory read access

| Symbol | Parameter             | Conditions                            | Class      |

|--------|-----------------------|---------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +105$ °C conforming to JESD78A | II level A |

#### Table 44. Electrical sensitivities

### 5.3.13 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (>5 LSB TUE), out of spec current injection on adjacent pins or other functional failure (for example reset, oscillator frequency deviation).

The test results are given in Table 45

|                  |                                                            | Functional s       |                    |      |  |

|------------------|------------------------------------------------------------|--------------------|--------------------|------|--|

| Symbol           | Description                                                | Negative injection | Positive injection | Unit |  |

| I <sub>INJ</sub> | Injected current on OSC_IN32,<br>OSC_OUT32, PA4, PA5, PC13 | -0                 | +0                 |      |  |

|                  | Injected current on all FT pins                            | -5                 | +0                 | mA   |  |

|                  | Injected current on any other pin                          | -5                 | +5                 | ]    |  |

#### Table 45. I/O current injection susceptibility

## 5.3.14 I/O port characteristics

#### General input/output characteristics

Unless otherwise specified, the parameters given in *Table 46* are derived from tests performed under the conditions summarized in *Table 10*. All I/Os are CMOS and TTL compliant.

| Symbol           | Parameter                                                           | Conditions                                                         | Min                                  | Тур                              | Мах                                | Unit |

|------------------|---------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------|----------------------------------|------------------------------------|------|

| V <sub>IL</sub>  | Standard IO input low<br>level voltage                              |                                                                    | -0.3                                 | -                                | 0.28*(V <sub>DD</sub> -2 V)+0.8 V  | V    |

|                  | IO FT <sup>(1)</sup> input low level voltage                        | -                                                                  | -0.3                                 | -                                | 0.32*(V <sub>DD</sub> -2 V)+0.75 V | V    |

| V <sub>IH</sub>  | Standard IO input high<br>level voltage                             | -                                                                  | 0.41*(V <sub>DD</sub> -2 V)+1.3<br>V |                                  | V <sub>DD</sub> +0.3               | V    |

|                  | IO FT <sup>(1)</sup> input high level voltage                       | V <sub>DD</sub> > 2 V                                              | 0.42*()/ 2.)/)+1.)/                  |                                  | 5.5                                | v    |

|                  |                                                                     | V <sub>DD</sub> ≤2 V                                               | 0.42 (V <sub>DD</sub> -2 V)+1 V      | .42*(V <sub>DD</sub> -2 V)+1 V - |                                    | v    |

| V <sub>hys</sub> | Standard IO Schmitt<br>trigger voltage<br>hysteresis <sup>(2)</sup> | -                                                                  | 200                                  | -                                | -                                  | mV   |

|                  | IO FT Schmitt trigger voltage hysteresis <sup>(2)</sup>             |                                                                    | 5% V <sub>DD</sub> <sup>(3)</sup>    | -                                | -                                  | mV   |

| I <sub>lkg</sub> | Input leakage current <sup>(4)</sup>                                | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>Standard I/Os | -                                    | -                                | ±1                                 |      |

|                  |                                                                     | V <sub>IN</sub> = 5 V,<br>I/O FT                                   | -                                    | -                                | 3                                  | μA   |

| R <sub>PU</sub>  | Weak pull-up equivalent resistor <sup>(5)</sup>                     | $V_{IN} = V_{SS}$                                                  | 30                                   | 40                               | 50                                 | kΩ   |

| R <sub>PD</sub>  | Weak pull-down<br>equivalent resistor <sup>(5)</sup>                | $V_{IN} = V_{DD}$                                                  | 30                                   | 40                               | 50                                 | kΩ   |

| C <sub>IO</sub>  | I/O pin capacitance                                                 | -                                                                  | -                                    | 5                                | -                                  | pF   |

1. FT = Five-volt tolerant. In order to sustain a voltage higher than V<sub>DD</sub>+0.3 the internal pull-up/pull-down resistors must be disabled.

2. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by characterization results.

3. With a minimum of 100 mV.

4. Leakage could be higher than max. if negative current is injected on adjacent pins.

Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This MOS/NMOS contribution to the series resistance is minimum (~10% order).

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 42* and *Figure 43* for standard I/Os, and in *Figure 44* and *Figure 45* for 5 V tolerant I/Os.

# 6 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

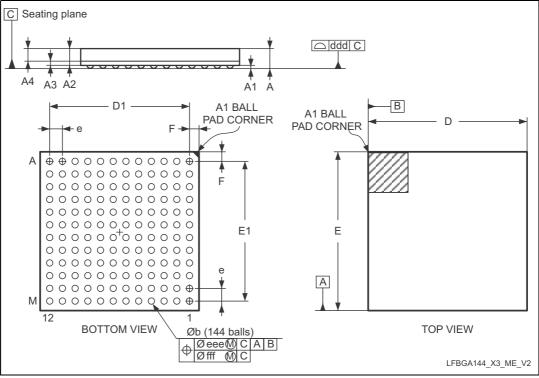

## 6.1 LFBGA144 package information

Figure 62. LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm, 0.8 mm pitch, package outline

1. Drawing is not to scale.

| Table 65. LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm, |

|-----------------------------------------------------------------------------------|

| 0.8 mm pitch, package mechanical data                                             |

| Symbol           | millimeters |       | inches <sup>(1)</sup> |        |        |        |

|------------------|-------------|-------|-----------------------|--------|--------|--------|

|                  | Min         | Тур   | Мах                   | Тур    | Min    | Max    |

| A <sup>(2)</sup> | -           | -     | 1.700                 | -      | -      | 0.0669 |

| A1               | 0.250       | 0.300 | 0.350                 | 0.098  | 0.0118 | 0.0138 |

| A2               | 0.810       | 0.910 | 1.010                 | 0.0319 | 0.0358 | 0.0398 |

| A3               | 0.225       | 0.26  | 0.295                 | 0.0089 | 0.0102 | 0.0116 |

| A4               | 0.585       | 0.650 | 0.715                 | 0.0230 | 0.0256 | 0.0281 |

# 7 Part numbering

## Example: STM32 F 103 R C т 6 xxx **Device family** STM32 = ARM-based 32-bit microcontroller Product type F = general-purpose **Device subfamily** 103 = performance line Pin count R = 64 pinsV = 100 pins Z = 144 pins Flash memory size C = 256 Kbytes of Flash memory D = 384 Kbytes of Flash memory E = 512 Kbytes of Flash memory Package H = BGA T = LQFPY = WLCSP64 **Temperature range** 6 = Industrial temperature range, -40 to 85 °C. 7 = Industrial temperature range, -40 to 105 °C. Options

#### Table 75. Ordering information scheme

xxx = programmed parts TR = tape and real

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.

#### IMPORTANT NOTICE – PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics – All rights reserved

DocID14611 Rev 12