Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 72MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB            |

| Peripherals                | DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT            |

| Number of I/O              | 51                                                                      |

| Program Memory Size        | 512KB (512K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | ·                                                                       |

| RAM Size                   | 64K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f103ret6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.3.10 Boot modes

At startup, boot pins are used to select one of three boot options:

- Boot from user Flash: you have an option to boot from any of two memory banks. By default, boot from Flash memory bank 1 is selected. You can choose to boot from Flash memory bank 2 by setting a bit in the option bytes.

- Boot from system memory

- Boot from embedded SRAM

The boot loader is located in system memory. It is used to reprogram the Flash memory by using USART1.

#### 2.3.11 **Power supply schemes**

- $V_{DD}$  = 2.0 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through V<sub>DD</sub> pins.

- $V_{SSA}$ ,  $V_{DDA} = 2.0$  to 3.6 V: external analog power supplies for ADC, DAC, Reset blocks, RCs and PLL (minimum voltage to be applied to VDDA is 2.4 V when the ADC or DAC is used).  $V_{DDA}$  and  $V_{SSA}$  must be connected to  $V_{DD}$  and  $V_{SS}$ , respectively.

- V<sub>BAT</sub> = 1.8 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

For more details on how to connect power pins, refer to *Figure 12: Power supply scheme*.

### 2.3.12 Power supply supervisor

The device has an integrated power-on reset (POR)/power-down reset (PDR) circuitry. It is always active, and ensures proper operation starting from/down to 2 V. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$ , without the need for an external reset circuit.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software. Refer to *Table 12: Embedded reset and power control block characteristics* for the values of  $V_{POR/PDR}$  and  $V_{PVD}$ .

### 2.3.13 Voltage regulator

The regulator has three operation modes: main (MR), low-power (LPR) and power down.

- MR is used in the nominal regulation mode (Run)

- LPR is used in the Stop modes.

- Power down is used in Standby mode: the regulator output is in high impedance: the kernel circuitry is powered down, inducing zero consumption (but the contents of the registers and SRAM are lost)

This regulator is always enabled after reset. It is disabled in Standby mode.

#### Advanced-control timers (TIM1 and TIM8)

The two advanced-control timers (TIM1 and TIM8) can each be seen as a three-phase PWM multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead-times. They can also be seen as a complete general-purpose timer. The 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge or center-aligned modes)

- One-pulse mode output

If configured as a standard 16-bit timer, it has the same features as the TIMx timer. If configured as the 16-bit PWM generator, it has full modulation capability (0-100%).

In debug mode, the advanced-control timer counter can be frozen and the PWM outputs disabled to turn off any power switch driven by these outputs.

Many features are shared with those of the general-purpose TIM timers which have the same architecture. The advanced-control timer can therefore work together with the TIM timers via the Timer Link feature for synchronization or event chaining.

#### General-purpose timers (TIMx)

There are up to 4 synchronizable general-purpose timers (TIM2, TIM3, TIM4 and TIM5) embedded in the STM32F103xC, STM32F103xD and STM32F103xE performance line devices. These timers are based on a 16-bit auto-reload up/down counter, a 16-bit prescaler and feature 4 independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input captures / output compares / PWMs on the largest packages.

The general-purpose timers can work together with the advanced-control timer via the Timer Link feature for synchronization or event chaining. Their counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs. They all have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

#### Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger generation. They can also be used as a generic 16-bit time base.

#### Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

#### Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from

the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

#### SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard down counter. It features:

- A 24-bit down counter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0.

- Programmable clock source

#### 2.3.18 I<sup>2</sup>C bus

Up to two I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support standard and fast modes.

They support 7/10-bit addressing mode and 7-bit dual addressing mode (as slave). A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SMBus 2.0/PMBus.

#### 2.3.19 Universal synchronous/asynchronous receiver transmitters (USARTs)

The STM32F103xC, STM32F103xD and STM32F103xE performance line embeds three universal synchronous/asynchronous receiver transmitters (USART1, USART2 and USART3) and two universal asynchronous receiver transmitters (UART4 and UART5).

These five interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability.

The USART1 interface is able to communicate at speeds of up to 4.5 Mbit/s. The other available interfaces communicate at up to 2.25 Mbit/s.

USART1, USART2 and USART3 also provide hardware management of the CTS and RTS signals, Smart Card mode (ISO 7816 compliant) and SPI-like communication capability. All interfaces can be served by the DMA controller except for UART5.

### 2.3.20 Serial peripheral interface (SPI)

Up to three SPIs are able to communicate up to 18 Mbits/s in slave and master modes in full-duplex and simplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

All SPIs can be served by the DMA controller.

## 2.3.21 Inter-integrated sound (I<sup>2</sup>S)

Two standard I<sup>2</sup>S interfaces (multiplexed with SPI2 and SPI3) are available, that can be operated in master or slave mode. These interfaces can be configured to operate with 16/32 bit resolution, as input or output channels. Audio sampling frequencies from 8 kHz up to 48 kHz are supported. When either or both of the I<sup>2</sup>S interfaces is/are configured in master

DocID14611 Rev 12

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the general-purpose timers (TIMx) and the advanced-control timers (TIM1 and TIM8) can be internally connected to the ADC start trigger and injection trigger, respectively, to allow the application to synchronize A/D conversion and timers.

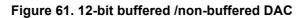

#### 2.3.27 DAC (digital-to-analog converter)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs. The chosen design structure is composed of integrated resistor strings and an amplifier in inverting configuration.

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- 8-bit or 12-bit monotonic output

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- external triggers for conversion

- input voltage reference V<sub>REF+</sub>

Eight DAC trigger inputs are used in the STM32F103xC, STM32F103xD and STM32F103xE performance line family. The DAC channels are triggered through the timer update outputs that are also connected to different DMA channels.

| г | 1                  | 2                       | 3   | 4                 | 5                 | 6                 | 7                 | 8    | 9    | 10   |

|---|--------------------|-------------------------|-----|-------------------|-------------------|-------------------|-------------------|------|------|------|

| A | PC14-<br>OSC32_IN  | PC13-<br>TAMPER-<br>RTC | PE2 | PB9               | РВ7               | PB4               | РВЗ               | PA15 | PA14 | PA13 |

| в | PC15-<br>osc32_out | V <sub>BAT</sub>        | PE3 | РВ8               | PB6               | PD5               | PD2               | PC11 | PC10 | PA12 |

| с | OSC_IN             | V <sub>SS_5</sub>       | PE4 | PE1               | PB5               | PD6               | PD3               | PC12 | PA9  | PA11 |

| D | OSC_OUT            | V <sub>DD_5</sub>       | PE5 | PEO               | BOOTO             | PD7               | PD4               | PD0  | PA8  | PA10 |

| E | NRST               | PC2                     | PE6 | V <sub>SS_4</sub> | V <sub>SS_3</sub> | V <sub>SS_2</sub> | V <sub>SS_1</sub> | PD1  | PC9  | PC7  |

| F | PC0                | PC1                     | PC3 | V <sub>DD_4</sub> | V <sub>DD_3</sub> | V <sub>DD_2</sub> | V <sub>DD_1</sub> | NC   | PC8  | PC6  |

| G | V <sub>SSA</sub>   | PA0-WKUP                | PA4 | PC4               | PB2               | PE10              | PE14              | PB15 | PD11 | PD15 |

| н | V <sub>REF-</sub>  | PA1                     | PA5 | PC5               | PE7               | PE11              | PE15              | PB14 | PD10 | PD14 |

| J | V <sub>REF+</sub>  | PA2                     | PA6 | PB0               | PE8               | PE12              | PB10              | PB13 | PD9  | PD13 |

| к | V <sub>DDA</sub>   | PA3                     | PA7 | PB1               | PE9               | PE13              | PB11              | PB12 | PD8  | PD12 |

Figure 4. STM32F103xC/D/E performance line BGA100 ballout

1. The above figure shows the package top view.

| Table 6. FSMC pin definition<br>FSMC |        |        |      |               |             |                                  |

|--------------------------------------|--------|--------|------|---------------|-------------|----------------------------------|

| Pins                                 |        |        |      |               |             | LQFP100<br>BGA100 <sup>(1)</sup> |

|                                      | CF     | CF/IDE | SRAM | NOR/PSRAM Mux | NAND 16 bit | 20/1100                          |

| PE2                                  | -      | -      | A23  | A23           | -           | Yes                              |

| PE3                                  | -      | -      | A19  | A19           | -           | Yes                              |

| PE4                                  | -      | -      | A20  | A20           | -           | Yes                              |

| PE5                                  | -      | -      | A21  | A21           | -           | Yes                              |

| PE6                                  | -      | -      | A22  | A22           | -           | Yes                              |

| PF0                                  | A0     | A0     | A0   | -             | -           | -                                |

| PF1                                  | A1     | A1     | A1   | -             | -           | -                                |

| PF2                                  | A2     | A2     | A2   | -             | -           | -                                |

| PF3                                  | A3     | -      | A3   | -             | -           | -                                |

| PF4                                  | A4     | -      | A4   | -             | -           | -                                |

| PF5                                  | A5     | -      | A5   | -             | -           | -                                |

| PF6                                  | NIORD  | NIORD  | -    | -             | -           | -                                |

| PF7                                  | NREG   | NREG   | -    | -             | -           | -                                |

| PF8                                  | NIOWR  | NIOWR  | -    | -             | -           | -                                |

| PF9                                  | CD     | CD     | -    | -             | -           | -                                |

| PF10                                 | INTR   | INTR   | -    | -             | -           | -                                |

| PF11                                 | NIOS16 | NIOS16 | -    | -             | -           | -                                |

| PF12                                 | A6     | -      | A6   | -             | -           | -                                |

| PF13                                 | A7     | -      | A7   | -             | -           | -                                |

| PF14                                 | A8     | -      | A8   | -             | -           | -                                |

| PF15                                 | A9     | -      | A9   | -             | -           | -                                |

| PG0                                  | A10    | -      | A10  | -             | -           | -                                |

| PG1                                  | -      | -      | A11  | -             | -           | -                                |

| PE7                                  | D4     | D4     | D4   | DA4           | D4          | Yes                              |

| PE8                                  | D5     | D5     | D5   | DA5           | D5          | Yes                              |

| PE9                                  | D6     | D6     | D6   | DA6           | D6          | Yes                              |

| PE10                                 | D7     | D7     | D7   | DA7           | D7          | Yes                              |

| PE11                                 | D8     | D8     | D8   | DA8           | D8          | Yes                              |

| PE12                                 | D9     | D9     | D9   | DA9           | D9          | Yes                              |

| PE13                                 | D10    | D10    | D10  | DA10          | D10         | Yes                              |

| PE14                                 | D11    | D11    | D11  | DA11          | D11         | Yes                              |

| PE15                                 | D12    | D12    | D12  | DA12          | D12         | Yes                              |

| PD8                                  | D13    | D13    | D13  | DA13          | D13         | Yes                              |

#### Table 6. FSMC pin definition

| Symbol Ratings Value |                              | Value       | Unit |  |

|----------------------|------------------------------|-------------|------|--|

| T <sub>STG</sub>     | Storage temperature range    | -65 to +150 | °C   |  |

| TJ                   | Maximum junction temperature | 150         | °C   |  |

#### Table 9. Thermal characteristics

# 5.3 Operating conditions

#### 5.3.1 General operating conditions

| Table 10. General operating conditions        |                                                                                                     |                                      |     |     |      |  |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------|-----|-----|------|--|

| Symbol                                        | Parameter                                                                                           | Conditions                           | Min | Max | Unit |  |

| f <sub>HCLK</sub>                             | Internal AHB clock frequency                                                                        | -                                    | 0   | 72  |      |  |

| f <sub>PCLK1</sub> Internal APB1 clock freque |                                                                                                     | -                                    | 0   | 36  | MHz  |  |

| f <sub>PCLK2</sub>                            |                                                                                                     |                                      | 0   | 72  |      |  |

| V <sub>DD</sub>                               | Standard operating voltage                                                                          | -                                    | 2   | 3.6 | V    |  |

| V (1)                                         | Analog operating voltage<br>(ADC not used)                                                          | Must be the same potential           | 2   | 3.6 | V    |  |

| V <sub>DDA</sub> <sup>(1)</sup>               | Analog operating voltage (ADC used)                                                                 | as V <sub>DD</sub> <sup>(2)</sup>    | 2.4 | 3.6 | v    |  |

| $V_{BAT}$                                     | Backup operating voltage                                                                            | -                                    | 1.8 | 3.6 | V    |  |

|                                               |                                                                                                     | LQFP144                              | -   | 666 |      |  |

|                                               |                                                                                                     | LQFP100                              | -   | 434 |      |  |

| Pp                                            | Power dissipation at $T_A =$<br>85 °C for suffix 6 or $T_A =$<br>105 °C for suffix 7 <sup>(3)</sup> | LQFP64                               | -   | 444 | mW   |  |

| ГD                                            |                                                                                                     | LFBGA100                             | -   | 500 |      |  |

|                                               |                                                                                                     | LFBGA144                             | -   | 500 |      |  |

|                                               |                                                                                                     | WLCSP64                              | -   | 400 |      |  |

|                                               | Ambient temperature for 6                                                                           | Maximum power dissipation            | -40 | 85  | °C   |  |

| Та                                            | suffix version                                                                                      | Low-power dissipation <sup>(4)</sup> | -40 | 105 | C    |  |

|                                               | Ambient temperature for 7                                                                           | Maximum power dissipation            | -40 | 105 | °C   |  |

|                                               | suffix version                                                                                      | Low-power dissipation <sup>(4)</sup> | -40 | 125 | C    |  |

| TJ                                            | lunction tomporature range                                                                          | 6 suffix version                     | -40 | 105 | °C   |  |

| IJ                                            | Junction temperature range                                                                          | 7 suffix version                     | -40 | 125 | C    |  |

#### Table 10. General operating conditions

1. When the ADC is used, refer to Table 59: ADC characteristics.

2. It is recommended to power  $V_{DD}$  and  $V_{DDA}$  from the same source. A maximum difference of 300 mV between  $V_{DD}$  and  $V_{DDA}$  can be tolerated during power-up and operation.

If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>J</sub>max (see Table 6.7: Thermal characteristics on page 133).

In low-power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>J</sub>max (see Table 6.7: Thermal characteristics on page 133).

#### **Typical current consumption**

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load).

- All peripherals are disabled except if it is explicitly mentioned.

- The Flash access time is adjusted to f<sub>HCLK</sub> frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 48 MHZ and 2 wait states above).

- Ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in *Table 10*.

- Prefetch is ON (Reminder: this bit must be set before clock setting and bus prescaling)

When the peripherals are enabled  $f_{PCLK1} = f_{HCLK}/4$ ,  $f_{PCLK2} = f_{HCLK}/2$ ,  $f_{ADCCLK} = f_{PCLK2}/4$

|                 |                                  |                                                       |                   | Туј                                       | p <sup>(1)</sup>            |      |

|-----------------|----------------------------------|-------------------------------------------------------|-------------------|-------------------------------------------|-----------------------------|------|

| Symbol          | Parameter                        | Conditions                                            | f <sub>HCLK</sub> | All peripherals<br>enabled <sup>(2)</sup> | All peripherals<br>disabled | Unit |

|                 |                                  |                                                       | 72 MHz            | 51                                        | 30.5                        |      |

|                 |                                  |                                                       | 48 MHz            | 34.6                                      | 20.7                        |      |

|                 |                                  |                                                       | 36 MHz            | 26.6                                      | 16.2                        |      |

|                 |                                  |                                                       | 24 MHz            | 18.5                                      | 11.4                        |      |

|                 |                                  |                                                       | 16 MHz            | 12.8                                      | 8.2                         |      |

|                 |                                  | External clock <sup>(3)</sup>                         | 8 MHz             | 7.2                                       | 5                           | mA   |

|                 |                                  |                                                       | 4 MHz             | 4.2                                       | 3.1                         |      |

|                 | Supply<br>current in<br>Run mode | nt in<br>node<br>Running on high<br>speed internal RC | 2 MHz             | 2.7                                       | 2.1                         |      |

|                 |                                  |                                                       | 1 MHz             | 2                                         | 1.7                         |      |

|                 |                                  |                                                       | 500 kHz           | 1.6                                       | 1.4                         |      |

| I <sub>DD</sub> |                                  |                                                       | 125 kHz           | 1.3                                       | 1.2                         |      |

| DD              |                                  |                                                       | 64 MHz            | 45                                        | 27                          |      |

|                 |                                  |                                                       | 48 MHz            | 34                                        | 20.1                        |      |

|                 |                                  |                                                       | 36 MHz            | 26                                        | 15.6                        |      |

|                 |                                  |                                                       | 24 MHz            | 17.9                                      | 10.8                        |      |

|                 |                                  |                                                       | 16 MHz            | 12.2                                      | 7.6                         |      |

|                 |                                  | (HSI), AHB<br>prescaler used to                       | 8 MHz             | 6.6                                       | 4.4                         | mA   |

|                 |                                  | reduce the                                            | 4 MHz             | 3.6                                       | 2.5                         |      |

|                 |                                  | frequency                                             | 2 MHz             | 2.1                                       | 1.5                         |      |

|                 |                                  |                                                       | 1 MHz             | 1.4                                       | 1.1                         |      |

|                 |                                  |                                                       | 500 kHz           | 1                                         | 0.8                         |      |

|                 |                                  |                                                       | 125 kHz           | 0.7                                       | 0.6                         |      |

# Table 18. Typical current consumption in Run mode, code with data processing<br/>running from Flash

1. Typical values are measures at  $T_A$  = 25 °C,  $V_{DD}$  = 3.3 V.

2. Add an additional power consumption of 0.8 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

3. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 24*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

|                                     |                                                                                                         |                                       | 131103 (ILSE - 32.700 I | <b>,</b> |     |     |      |

|-------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------|----------|-----|-----|------|

| Symbol                              | Parameter                                                                                               | C                                     | Conditions              | Min      | Тур | Max | Unit |

| R <sub>F</sub>                      | Feedback resistor                                                                                       |                                       | -                       | -        | 5   | -   | MΩ   |

| C <sup>(2)</sup>                    | Recommended load capacitance<br>versus equivalent serial<br>resistance of the crystal (R <sub>S</sub> ) | R <sub>S</sub> = 30 kΩ                |                         | -        | -   | 15  | pF   |

| I <sub>2</sub>                      | LSE driving current                                                                                     | $V_{DD}$ = 3.3 V, $V_{IN}$ = $V_{SS}$ |                         | -        | -   | 1.4 | μA   |

| 9 <sub>m</sub>                      | Oscillator transconductance                                                                             | -                                     |                         | 5        | -   | -   | μA/V |

|                                     | Startup time                                                                                            |                                       | T <sub>A</sub> = 50 °C  | -        | 1.5 | -   | S    |

|                                     |                                                                                                         |                                       | T <sub>A</sub> = 25 °C  | -        | 2.5 | -   |      |

|                                     |                                                                                                         | V <sub>DD</sub> is<br>stabilized      | T <sub>A</sub> = 10 °C  | -        | 4   | -   |      |

| + (3)                               |                                                                                                         |                                       | T <sub>A</sub> = 0 °C   | -        | 6   | -   |      |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> |                                                                                                         |                                       | T <sub>A</sub> = -10 °C | -        | 10  | -   |      |

|                                     |                                                                                                         |                                       | T <sub>A</sub> = -20 °C | -        | 17  | -   |      |

|                                     |                                                                                                         |                                       | T <sub>A</sub> = -30 °C | -        | 32  | -   |      |

|                                     |                                                                                                         |                                       | T <sub>A</sub> = -40 °C | -        | 60  | -   |      |

| Table 24. LSE oscillator characteristics $(f_{LSE} = 32.768 \text{ kHz})^{(1)(2)}$ | ) |

|------------------------------------------------------------------------------------|---|

|------------------------------------------------------------------------------------|---|

1. Guaranteed by characterization results.

Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) until a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer, PCB layout and humidity.

**Caution:** To avoid exceeding the maximum value of  $C_{L1}$  and  $C_{L2}$  (15 pF) it is strongly recommended to use a resonator with a load capacitance  $C_L \le 7$  pF. Never use a resonator with a load capacitance of 12.5 pF. **Example:** if you choose a resonator with a load capacitance of  $C_L = 6$  pF, and  $C_{stray} = 2$  pF, then  $C_{L1} = C_{L2} = 8$  pF.

Note: For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality ceramic capacitors in the 5 pF to 15 pF range selected to match the requirements of the crystal or resonator (see Figure 23).  $C_{L1}$  and  $C_{L2}$ , are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . Load capacitance  $C_L$  has the following formula:  $C_L = C_{L1} \times C_{L2} / (C_{L1} + C_{L2}) + C_{stray}$  where  $C_{stray}$  is the pin capacitance and board or trace PCB-related capacitance. Typically, it is between 2 pF and 7 pF.

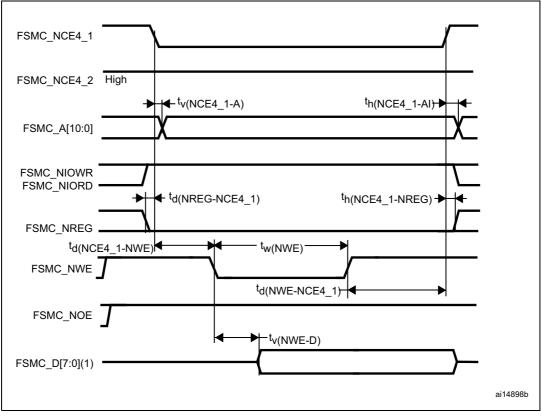

Figure 35. PC Card/CompactFlash controller waveforms for attribute memory write access

1. Only data bits 0...7 are driven (bits 8...15 remains HiZ).

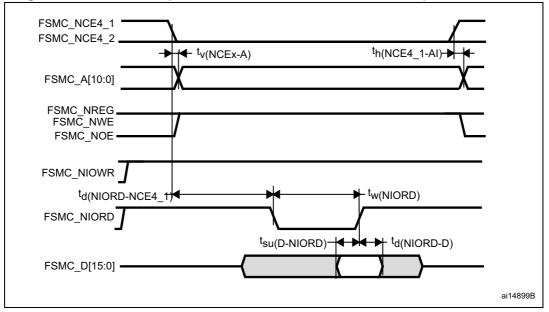

#### Figure 36. PC Card/CompactFlash controller waveforms for I/O space read access

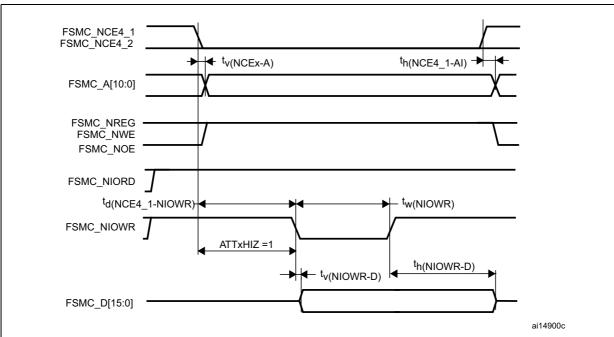

Figure 37. PC Card/CompactFlash controller waveforms for I/O space write access

|  | Table 39. Switchin | g characteristics for PC Card/CF read | and write cycles <sup>(1)(2)</sup> |

|--|--------------------|---------------------------------------|------------------------------------|

|--|--------------------|---------------------------------------|------------------------------------|

| Symbol                                                    | Parameter                                                                                                                   | Min                     | Max                      | Unit |

|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------|------|

| t <sub>v(NCEx-A)</sub><br>t <sub>v(NCE4_1-A)</sub>        | FSMC_NCEx low (x = 4_1/4_2) to FSMC_Ay valid (y = 010) FSMC_NCE4_1 low (x = 4_1/4_2) to FSMC_Ay valid (y = 010)             | -                       | 0                        | ns   |

| t <sub>h(NCEx-AI)</sub><br>t <sub>h(NCE4_1-AI)</sub>      | FSMC_NCEx high (x = $4_1/4_2$ ) to FSMC_Ax invalid (x = 010) FSMC_NCE4_1 high (x = $4_1/4_2$ ) to FSMC_Ax invalid (x = 010) | 2.5                     | -                        | ns   |

| t <sub>d(NREG-NCEx)</sub><br>t <sub>d(NREG-NCE4_1)</sub>  | FSMC_NCEx low to FSMC_NREG valid FSMC_NCE4_1 low to FSMC_NREG valid                                                         | -                       | 5                        | ns   |

| t <sub>h(NCEx-NREG)</sub><br>t <sub>h(NCE4_</sub> 1-NREG) | FSMC_NCEx high to FSMC_NREG invalid FSMC_NCE4_1 high to FSMC_NREG invalid                                                   | t <sub>HCLK</sub> + 3   | -                        | ns   |

| t <sub>d(NCE4_1-NOE)</sub>                                | FSMC_NCE4_1 low to FSMC_NOE low                                                                                             | -                       | 5t <sub>HCLK</sub> + 2   | ns   |

| t <sub>w(NOE)</sub>                                       | FSMC_NOE low width                                                                                                          | 8t <sub>HCLK</sub> –1.5 | 8t <sub>HCLK</sub> + 1   | ns   |

| t <sub>d(NOE-NCE4_1</sub>                                 | FSMC_NOE high to FSMC_NCE4_1 high                                                                                           | 5t <sub>HCLK</sub> + 2  | -                        | ns   |

| t <sub>su(D-NOE)</sub>                                    | FSMC_D[15:0] valid data before FSMC_NOE high                                                                                | 25                      | -                        | ns   |

| t <sub>h(NOE-D)</sub>                                     | FSMC_D[15:0] valid data after FSMC_NOE high                                                                                 | 15                      | -                        | ns   |

| t <sub>w(NWE)</sub>                                       | FSMC_NWE low width                                                                                                          | 8t <sub>HCLK</sub> – 1  | 8t <sub>HCLK</sub> + 2   | ns   |

| t <sub>d(NWE-NCE4_1)</sub>                                | FSMC_NWE high to FSMC_NCE4_1 high                                                                                           | 5t <sub>HCLK</sub> + 2  | -                        | ns   |

| t <sub>d(NCE4_1-NWE)</sub>                                | FSMC_NCE4_1 low to FSMC_NWE low                                                                                             | -                       | 5t <sub>HCLK</sub> + 1.5 | ns   |

| t <sub>v(NWE-D)</sub>                                     | FSMC_NWE low to FSMC_D[15:0] valid                                                                                          | -                       | 0                        | ns   |

| t <sub>h(NWE-D)</sub>                                     | FSMC_NWE high to FSMC_D[15:0] invalid                                                                                       | 11t <sub>HCLK</sub>     | -                        | ns   |

| t <sub>d(D-NWE)</sub>                                     | FSMC_D[15:0] valid before FSMC_NWE high                                                                                     | 13t <sub>HCLK</sub>     | -                        | ns   |

| Symbol | Parameter             | Conditions                                    | Class      |  |  |

|--------|-----------------------|-----------------------------------------------|------------|--|--|

| LU     | Static latch-up class | $T_A = +105 \text{ °C conforming to JESD78A}$ | II level A |  |  |

#### Table 44. Electrical sensitivities

### 5.3.13 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (>5 LSB TUE), out of spec current injection on adjacent pins or other functional failure (for example reset, oscillator frequency deviation).

The test results are given in Table 45

|                  |                                                            | Functional s       |                    |      |

|------------------|------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                | Negative injection | Positive injection | Unit |

|                  | Injected current on OSC_IN32,<br>OSC_OUT32, PA4, PA5, PC13 | -0                 | +0                 |      |

| I <sub>INJ</sub> | Injected current on all FT pins                            | -5                 | +0                 | mA   |

|                  | Injected current on any other pin                          | -5                 | +5                 |      |

#### Table 45. I/O current injection susceptibility

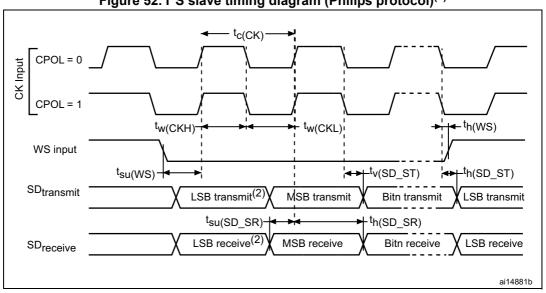

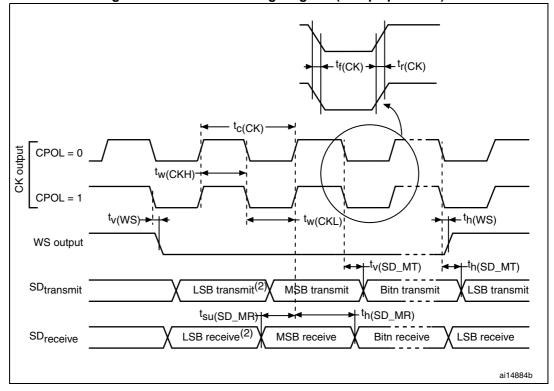

Figure 52. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Measurement points are done at CMOS levels: 0.3 ×  $V_{DD}$  and 0.7 ×  $V_{DD.}$

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

#### Figure 53. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

1. Guaranteed by characterization results.

2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

# 5.3.20 DAC electrical specifications

| Symbol                           | Parameter                                                                                                    | Min | Тур | Мах                      | Unit | Comments                                                                                                               |  |

|----------------------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|--------------------------|------|------------------------------------------------------------------------------------------------------------------------|--|

| V <sub>DDA</sub>                 | Analog supply voltage                                                                                        | 2.4 | -   | 3.6                      | V    | -                                                                                                                      |  |

| V <sub>REF+</sub>                | Reference supply voltage                                                                                     | 2.4 | -   | 3.6                      | V    | V <sub>REF+</sub> must always be below V <sub>DDA</sub>                                                                |  |

| V <sub>SSA</sub>                 | Ground                                                                                                       | 0   | -   | 0                        | V    | -                                                                                                                      |  |

| R <sub>LOAD</sub> <sup>(1)</sup> | Resistive load with buffer ON                                                                                | 5   | -   | -                        | kΩ   | -                                                                                                                      |  |

| R <sub>0</sub> <sup>(2)</sup>    | Impedance output with buffer<br>OFF                                                                          | -   | -   | 15                       | kΩ   | When the buffer is OFF, the Minimi resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is 1.5 M $\Omega$ |  |

| C <sub>LOAD</sub> <sup>(1)</sup> | Capacitive load                                                                                              | -   | -   | 50                       | pF   | Maximum capacitive load at<br>DAC_OUT pin (when the buffer is<br>ON).                                                  |  |

| DAC_OUT<br>min <sup>(1)</sup>    | Lower DAC_OUT voltage with buffer ON                                                                         | 0.2 | -   | -                        | V    | It gives the maximum output<br>excursion of the DAC.<br>It corresponds to 12-bit input code                            |  |

| DAC_OUT<br>max <sup>(1)</sup>    | Higher DAC_OUT voltage with buffer ON                                                                        | -   | -   | V <sub>DDA</sub> – 0.2   | V    | (0x0E0) to (0xF1C) at $V_{REF+}$ = 3.6 V<br>and (0x155) and (0xEAB) at $V_{REF+}$<br>2.4 V                             |  |

| DAC_OUT<br>min <sup>(1)</sup>    | Lower DAC_OUT voltage with buffer OFF                                                                        | -   | 0.5 | -                        | mV   | It gives the maximum output                                                                                            |  |

| DAC_OUT<br>max <sup>(1)</sup>    | Higher DAC_OUT voltage<br>with buffer OFF                                                                    | -   | -   | V <sub>REF+</sub> – 1LSB | V    | excursion of the DAC.                                                                                                  |  |

| I <sub>DDVREF+</sub>             | DAC DC current<br>consumption in quiescent<br>mode (Standby mode)                                            | -   | -   | 220                      | μA   | With no load, worst code (0xF1C) at<br>V <sub>REF+</sub> = 3.6 V in terms of DC<br>consumption on the inputs           |  |

|                                  | DAC DC current                                                                                               | -   | -   | 380                      | μA   | With no load, middle code (0x800) on the inputs                                                                        |  |

| I <sub>DDA</sub>                 | consumption in quiescent<br>mode <sup>(3)</sup>                                                              | -   | -   | 480                      | μA   | With no load, worst code (0xF1C) at<br>V <sub>REF+</sub> = 3.6 V in terms of DC<br>consumption on the inputs           |  |

| DNL <sup>(4)</sup>               | Differential non linearity<br>Difference between two                                                         | -   | -   | ±0.5                     | LSB  | Given for the DAC in 10-bit configuration                                                                              |  |

|                                  | consecutive code-1LSB)                                                                                       | -   | -   | ±2                       | LSB  | Given for the DAC in 12-bit configuration                                                                              |  |

|                                  | Integral non linearity<br>(difference between                                                                | -   | -   | ±1                       | LSB  | Given for the DAC in 10-bit configuration                                                                              |  |

| INL <sup>(3)</sup>               | measured value at Code i<br>and the value at Code i on a<br>line drawn between Code 0<br>and last Code 1023) | -   | -   | ±4                       | LSB  | Given for the DAC in 12-bit configuration                                                                              |  |

| TADIE 03. DAG CHARACTERISTICS | Table | 63. | DAC | characteristics |

|-------------------------------|-------|-----|-----|-----------------|

|-------------------------------|-------|-----|-----|-----------------|

| Symbol                               | Parameter                                                                                                                                                          | Min | Тур | Мах  | Unit  | Comments                                                                                                                |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|-------|-------------------------------------------------------------------------------------------------------------------------|

|                                      | Offset error                                                                                                                                                       | -   | -   | ±10  | mV    | -                                                                                                                       |

| Offset <sup>(3)</sup>                | (difference between<br>measured value at Code<br>(0x800) and the ideal value =<br>$V_{REF+}/2$ )                                                                   | -   | -   | ±3   | LSB   | Given for the DAC in 10-bit at V <sub>REF+</sub><br>= 3.6 V                                                             |

|                                      |                                                                                                                                                                    | -   | -   | ±12  | IL SB | Given for the DAC in 12-bit at V <sub>REF+</sub><br>= 3.6 V                                                             |

| Gain<br>error <sup>(3)</sup>         | Gain error                                                                                                                                                         | -   | -   | ±0.5 | %     | Given for the DAC in 12bit configuration                                                                                |

| t <sub>SETTLING</sub> <sup>(3)</sup> | Settling time (full scale: for a<br>10-bit input code transition<br>between the lowest and the<br>highest input codes when<br>DAC_OUT reaches final<br>value ±1LSB | -   | 3   | 4    | μs    | $C_{LOAD} \le 50 \text{ pF, } R_{LOAD} \ge 5 \text{ k}\Omega$                                                           |

| Update<br>rate <sup>(3)</sup>        | Max frequency for a correct<br>DAC_OUT change when<br>small variation in the input<br>code (from code i to i+1LSB)                                                 | -   | -   | 1    | MS/s  | $C_{LOAD} \le 50 \text{ pF, } R_{LOAD} \ge 5 \text{ k}\Omega$                                                           |

| t <sub>wakeup</sub> (3)              | Wakeup time from off state<br>(Setting the ENx bit in the<br>DAC Control register)                                                                                 | -   | 6.5 | 10   | μs    | $C_{LOAD} \le 50 \text{ pF}, R_{LOAD} \ge 5 \text{ k}\Omega$<br>input code between lowest and<br>highest possible ones. |

| PSRR+ <sup>(1)</sup>                 | Power supply rejection ratio<br>(to V <sub>DDA</sub> ) (static DC<br>measurement                                                                                   | -   | -67 | -40  | dB    | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                                        |

Table 63. DAC characteristics (continued)

1. Guaranteed by design.

2. Guaranteed by characterization.

3. The quiescent mode corresponds to a state where the DAC maintains a stable output level to ensure that no dynamic consumption occurs.

4. Guaranteed by characterization results.

1. The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

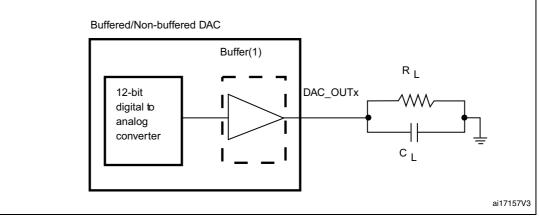

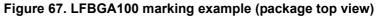

# 6.2 LFBGA100 package information

Figure 65. LFBGA100 - 10 x 10 mm low profile fine pitch ball grid array package outline

1. Drawing is not to scale.

| Table 67. LFBGA100 - 10 x 10 mm low profile fine pitch ball grid array package |

|--------------------------------------------------------------------------------|

| mechanical data                                                                |

| Cumb al |         | millimeters |        | inches <sup>(1)</sup> |        |        |  |

|---------|---------|-------------|--------|-----------------------|--------|--------|--|

| Symbol  | Min Typ |             | Мах    | Min                   | Тур    | Max    |  |

| A       | -       | -           | 1.700  | -                     | -      | 0.0669 |  |

| A1      | 0.270   | -           | -      | 0.0106                | -      | -      |  |

| A2      | -       | 0.300       | -      | -                     | 0.0118 | -      |  |

| A4      | -       | -           | 0.800  | -                     | -      | 0.0315 |  |

| b       | 0.450   | 0.500       | 0.550  | 0.0177                | 0.0197 | 0.0217 |  |

| D       | 9.850   | 10.000      | 10.150 | 0.3878                | 0.3937 | 0.3996 |  |

| D1      | -       | 7.200       | -      | -                     | 0.2835 | -      |  |

| E       | 9.850   | 10.000      | 10.150 | 0.3878                | 0.3937 | 0.3996 |  |

| E1      | -       | 7.200       | -      | -                     | 0.2835 | -      |  |

| е       | -       | 0.800       | -      | -                     | 0.0315 | -      |  |

| F       | -       | 1.400       | -      | -                     | 0.0551 | -      |  |

| ddd     | -       | -           | 0.120  | -                     | -      | 0.0047 |  |

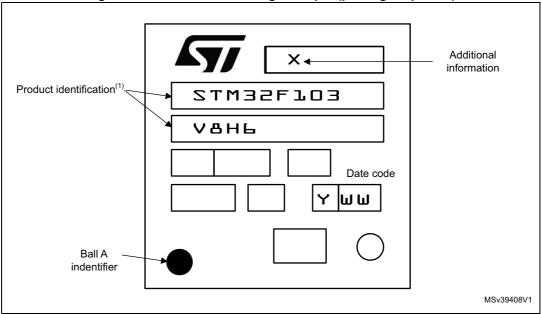

### Device marking for LFBGA100 package

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

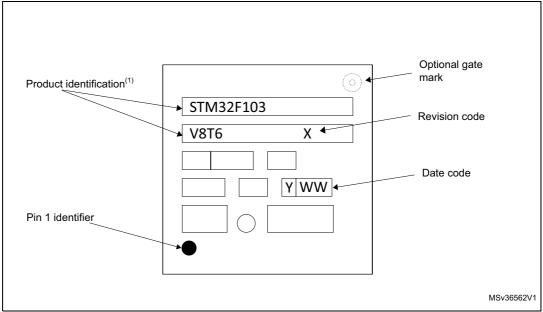

# 6.3 WLCSP64 package information

Figure 68. WLCSP, 64-ball 4.466 × 4.395 mm, 0.500 mm pitch, wafer-level chip-scale package outline

1. Drawing is not to scale.

2. Primary datum Z and seating plane are defined by the spherical crowns of the ball.

| Table 69. WLCSP, 64-ball 4.466 × 4.395 mm, 0.500 mm pitch, wafer-level chip-scale |  |  |  |  |  |

|-----------------------------------------------------------------------------------|--|--|--|--|--|

| package mechanical data                                                           |  |  |  |  |  |

| Symbol           |             | millimeters | 5          | inches <sup>(1)</sup> |        |        |

|------------------|-------------|-------------|------------|-----------------------|--------|--------|

| Symbol           | Min Typ Max |             | Min Typ Ma |                       | Max    |        |

| А                | 0.535       | 0.585       | 0.635      | 0.0211                | 0.0230 | 0.0250 |

| A1               | 0.205       | 0.230       | 0.255      | 0.0081                | 0.0091 | 0.0100 |

| A2               | 0.330       | 0.355       | 0.380      | 0.0130                | 0.0140 | 0.0150 |

| b <sup>(2)</sup> | 0.290       | 0.320       | 0.350      | 0.0114                | 0.0126 | 0.0138 |

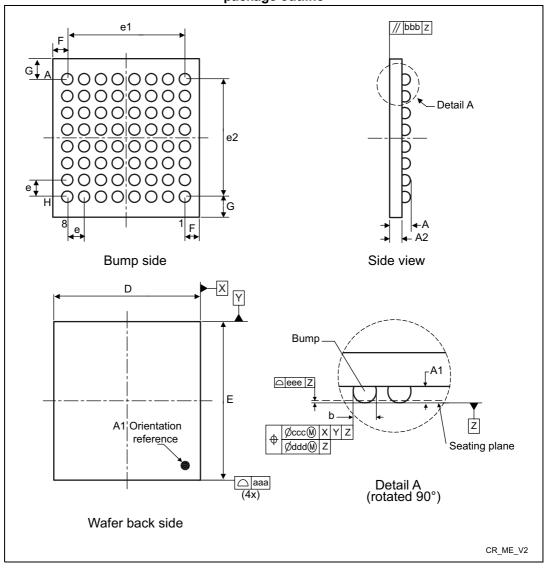

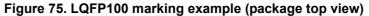

#### Device marking for LQFP100 package

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# 8 Revision history

| Date        | Revision | Changes                                                                                                                                                        |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 07-Apr-2008 | 1        | Initial release.                                                                                                                                               |

|             |          | -                                                                                                                                                              |

|             |          | Tolerance values corrected in <i>Table 74: LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm, 0.8 mm pitch, package data on page 139.</i> |

#### Table 76.Document revision history