# STMicroelectronics - <u>STM32F103VCT6TR Datasheet</u>

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 72MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB            |

| Peripherals                | DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT            |

| Number of I/O              | 80                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 48K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 100-LQFP                                                                |

| Supplier Device Package    | 100-LQFP (14x14)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f103vct6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.3.14 Low-power modes

The STM32F103xC, STM32F103xD and STM32F103xE performance line supports three low-power modes to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

• Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

• Stop mode

Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.

The device can be woken up from Stop mode by any of the EXTI line. The EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm or the USB wakeup.

• Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.8 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, SRAM and register contents are lost except for registers in the Backup domain and Standby circuitry.

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped by entering Stop or Standby mode.

# 2.3.15 DMA

The flexible 12-channel general-purpose DMAs (7 channels for DMA1 and 5 channels for DMA2) are able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The two DMA controllers support circular buffer management, removing the need for user code intervention when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with support for software trigger on each channel. Configuration is made by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: SPI, I<sup>2</sup>C, USART, general-purpose, basic and advanced-control timers TIMx, DAC, I<sup>2</sup>S, SDIO and ADC.

# 2.3.16 RTC (real-time clock) and backup registers

The RTC and the backup registers are supplied through a switch that takes power either on  $V_{DD}$  supply when present or through the  $V_{BAT}$  pin. The backup registers are forty-two 16-bit registers used to store 84 bytes of user application data when  $V_{DD}$  power is not present. They are not reset by a system or power reset, and they are not reset when the device wakes up from the Standby mode.

The real-time clock provides a set of continuously running counters which can be used with suitable software to provide a clock calendar function, and provides an alarm interrupt and a

mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

# 2.3.22 SDIO

An SD/SDIO/MMC host interface is available, that supports MultiMediaCard System Specification Version 4.2 in three different databus modes: 1-bit (default), 4-bit and 8-bit. The interface allows data transfer at up to 48 MHz in 8-bit mode, and is compliant with SD Memory Card Specifications Version 2.0.

The SDIO Card Specification Version 2.0 is also supported with two different databus modes: 1-bit (default) and 4-bit.

The current version supports only one SD/SDIO/MMC4.2 card at any one time and a stack of MMC4.1 or previous.

In addition to SD/SDIO/MMC, this interface is also fully compliant with the CE-ATA digital protocol Rev1.1.

# 2.3.23 Controller area network (CAN)

The CAN is compliant with specifications 2.0A and B (active) with a bit rate up to 1 Mbit/s. It can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. It has three transmit mailboxes, two receive FIFOs with 3 stages and 14 scalable filter banks.

# 2.3.24 Universal serial bus (USB)

The STM32F103xC, STM32F103xD and STM32F103xE performance line embed a USB device peripheral compatible with the USB full-speed 12 Mbs. The USB interface implements a full-speed (12 Mbit/s) function interface. It has software-configurable endpoint setting and suspend/resume support. The dedicated 48 MHz clock is generated from the internal main PLL (the clock source must use a HSE crystal oscillator).

## 2.3.25 GPIOs (general-purpose inputs/outputs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. All GPIOs are high current-capable.

The I/Os alternate function configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

# 2.3.26 ADC (analog to digital converter)

Three 12-bit analog-to-digital converters are embedded into STM32F103xC, STM32F103xD and STM32F103xE performance line devices and each ADC shares up to 21 external channels, performing conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.

Additional logic functions embedded in the ADC interface allow:

- Simultaneous sample and hold

- Interleaved sample and hold

- Single shunt

DocID14611 Rev 12

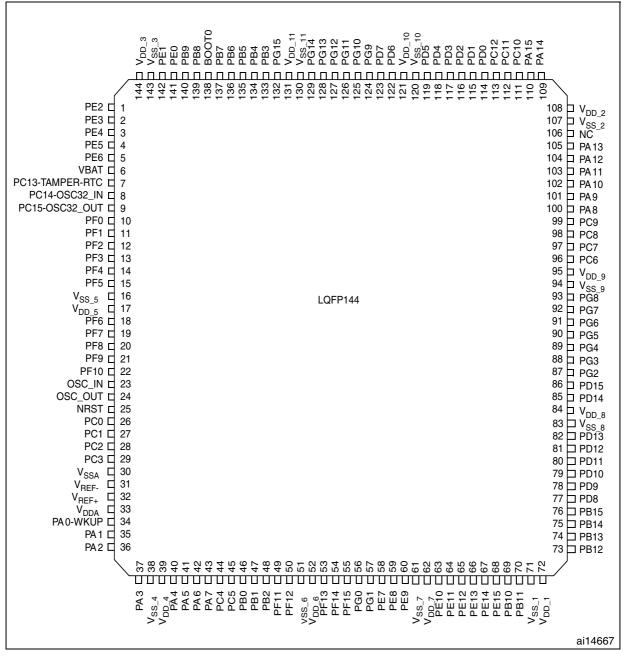

Figure 5. STM32F103xC/D/E performance line LQFP144 pinout

1. The above figure shows the package top view.

| Table 6. FSMC pin definition       FSMC |        |        |            |               |             |                                  |

|-----------------------------------------|--------|--------|------------|---------------|-------------|----------------------------------|

| Pins                                    |        |        | NOR/PSRAM/ |               |             | LQFP100<br>BGA100 <sup>(1)</sup> |

|                                         | CF     | CF/IDE | SRAM       | NOR/PSRAM Mux | NAND 16 bit | 20/1100                          |

| PE2                                     | -      | -      | A23        | A23           | -           | Yes                              |

| PE3                                     | -      | -      | A19        | A19           | -           | Yes                              |

| PE4                                     | -      | -      | A20        | A20           | -           | Yes                              |

| PE5                                     | -      | -      | A21        | A21           | -           | Yes                              |

| PE6                                     | -      | -      | A22        | A22           | -           | Yes                              |

| PF0                                     | A0     | A0     | A0         | -             | -           | -                                |

| PF1                                     | A1     | A1     | A1         | -             | -           | -                                |

| PF2                                     | A2     | A2     | A2         | -             | -           | -                                |

| PF3                                     | A3     | -      | A3         | -             | -           | -                                |

| PF4                                     | A4     | -      | A4         | -             | -           | -                                |

| PF5                                     | A5     | -      | A5         | -             | -           | -                                |

| PF6                                     | NIORD  | NIORD  | -          | -             | -           | -                                |

| PF7                                     | NREG   | NREG   | -          | -             | -           | -                                |

| PF8                                     | NIOWR  | NIOWR  | -          | -             | -           | -                                |

| PF9                                     | CD     | CD     | -          | -             | -           | -                                |

| PF10                                    | INTR   | INTR   | -          | -             | -           | -                                |

| PF11                                    | NIOS16 | NIOS16 | -          | -             | -           | -                                |

| PF12                                    | A6     | -      | A6         | -             | -           | -                                |

| PF13                                    | A7     | -      | A7         | -             | -           | -                                |

| PF14                                    | A8     | -      | A8         | -             | -           | -                                |

| PF15                                    | A9     | -      | A9         | -             | -           | -                                |

| PG0                                     | A10    | -      | A10        | -             | -           | -                                |

| PG1                                     | -      | -      | A11        | -             | -           | -                                |

| PE7                                     | D4     | D4     | D4         | DA4           | D4          | Yes                              |

| PE8                                     | D5     | D5     | D5         | DA5           | D5          | Yes                              |

| PE9                                     | D6     | D6     | D6         | DA6           | D6          | Yes                              |

| PE10                                    | D7     | D7     | D7         | DA7           | D7          | Yes                              |

| PE11                                    | D8     | D8     | D8         | DA8           | D8          | Yes                              |

| PE12                                    | D9     | D9     | D9         | DA9           | D9          | Yes                              |

| PE13                                    | D10    | D10    | D10        | DA10          | D10         | Yes                              |

| PE14                                    | D11    | D11    | D11        | DA11          | D11         | Yes                              |

| PE15                                    | D12    | D12    | D12        | DA12          | D12         | Yes                              |

| PD8                                     | D13    | D13    | D13        | DA13          | D13         | Yes                              |

# Table 6. FSMC pin definition

|      | FSMC   |        |                    |               |             |                                  |

|------|--------|--------|--------------------|---------------|-------------|----------------------------------|

| Pins | CF     | CF/IDE | NOR/PSRAM/<br>SRAM | NOR/PSRAM Mux | NAND 16 bit | LQFP100<br>BGA100 <sup>(1)</sup> |

| PD9  | D14    | D14    | D14                | DA14          | D14         | Yes                              |

| PD10 | D15    | D15    | D15                | DA15 D15      |             | Yes                              |

| PD11 | -      | -      | A16                | A16           | CLE         | Yes                              |

| PD12 | -      | -      | A17                | A17           | ALE         | Yes                              |

| PD13 | -      | -      | A18                | A18           | -           | Yes                              |

| PD14 | D0     | D0     | D0                 | DA0           | D0          | Yes                              |

| PD15 | D1     | D1     | D1                 | DA1           | D1          | Yes                              |

| PG2  | -      | -      | A12                | -             | -           | -                                |

| PG3  | -      | -      | A13                | -             | -           | -                                |

| PG4  | -      | -      | A14                | -             | -           | -                                |

| PG5  | -      | -      | A15                | -             | -           | -                                |

| PG6  | -      | -      | -                  | -             | INT2        | -                                |

| PG7  | -      | -      | -                  | -             | INT3        | -                                |

| PD0  | D2     | D2     | D2                 | DA2           | D2          | Yes                              |

| PD1  | D3     | D3     | D3                 | DA3           | D3          | Yes                              |

| PD3  | -      | -      | CLK                | CLK           | -           | Yes                              |

| PD4  | NOE    | NOE    | NOE                | NOE           | NOE         | Yes                              |

| PD5  | NWE    | NWE    | NWE                | NWE           | NWE         | Yes                              |

| PD6  | NWAIT  | NWAIT  | NWAIT              | NWAIT         | NWAIT       | Yes                              |

| PD7  | -      | -      | NE1                | NE1           | NCE2        | Yes                              |

| PG9  | -      | -      | NE2                | NE2           | NCE3        | -                                |

| PG10 | NCE4_1 | NCE4_1 | NE3                | NE3           | -           | -                                |

| PG11 | NCE4_2 | NCE4_2 | -                  | -             | -           | -                                |

| PG12 | -      | -      | NE4                | NE4           | -           | -                                |

| PG13 | -      | -      | A24                | A24           | -           | -                                |

| PG14 | -      | -      | A25                | A25           | -           | -                                |

| PB7  | -      | -      | NADV               | NADV          | -           | Yes                              |

| PE0  | -      | -      | NBL0               | NBL0          | -           | Yes                              |

| PE1  | -      | -      | NBL1               | NBL1          | -           | Yes                              |

Table 6. FSMC pin definition (continued)

1. Ports F and G are not available in devices delivered in 100-pin packages.

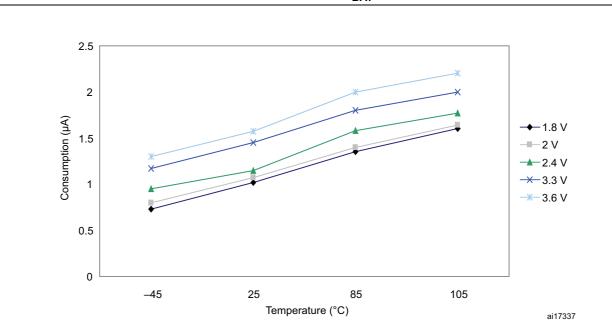

|                      |                                 |                                                                                                                                                 |                                              | Typ <sup>(1)</sup>                           |                                              | М                         | ax                         |      |

|----------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|---------------------------|----------------------------|------|

| Symbol               | Parameter                       | Conditions                                                                                                                                      | V <sub>DD</sub> /V <sub>BAT</sub><br>= 2.0 V | V <sub>DD</sub> /V <sub>BAT</sub><br>= 2.4 V | V <sub>DD</sub> /V <sub>BAT</sub><br>= 3.3 V | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                      | Supply current                  | Regulator in run mode, low-speed<br>and high-speed internal RC<br>oscillators and high-speed oscillator<br>OFF (no independent watchdog)        | -                                            | 34.5                                         | 35                                           | 379                       | 1130                       |      |

| I <sub>DD</sub>      | in Stop mode                    | Regulator in low-power mode, low-<br>speed and high-speed internal RC<br>oscillators and high-speed oscillator<br>OFF (no independent watchdog) | -                                            | 24.5                                         | 25                                           | 365                       | 1110                       |      |

|                      |                                 | Low-speed internal RC oscillator<br>and independent watchdog ON                                                                                 | -                                            | 3                                            | 3.8                                          | -                         | -                          | μA   |

|                      | in Standby                      | Low-speed internal RC oscillator<br>ON, independent watchdog OFF                                                                                | -                                            | 2.8                                          | 3.6                                          | -                         | -                          |      |

|                      | mode                            | Low-speed internal RC oscillator<br>and independent watchdog OFF,<br>low-speed oscillator and RTC OFF                                           | -                                            | 1.9                                          | 2.1                                          | 5 <sup>(2)</sup>          | 6.5 <sup>(2)</sup>         |      |

| I <sub>DD_VBAT</sub> | Backup domain<br>supply current | Low-speed oscillator and RTC ON                                                                                                                 | 1.05                                         | 1.1                                          | 1.4                                          | 2 <sup>(2)</sup>          | 2.3 <sup>(2)</sup>         |      |

Table 17. Typical and maximum current consumptions in Stop and Standby modes

1. Typical values are measured at  $T_A$  = 25 °C.

2. Guaranteed by characterization results.

Figure 16. Typical current consumption on  $\rm V_{BAT}$  with RTC on vs. temperature at different  $\rm V_{BAT}$  values

## **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in *Table 20*. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- ambient operating temperature and V<sub>DD</sub> supply voltage conditions summarized in Table 7

| Per                | ipheral                  | Current consumption | Unit   |

|--------------------|--------------------------|---------------------|--------|

|                    | DMA1                     | 20,42               |        |

|                    | DMA2                     | 19,03               |        |

| AHB (up to 72 MHz) | FSMC                     | 52,36               |        |

|                    | CRC                      | 2,36                | µA/MHz |

|                    | SDIO                     | 33,33               |        |

|                    | BusMatrix <sup>(1)</sup> | 9,72                |        |

#### Table 20. Peripheral current consumption

| Peri                | pheral                   | Current<br>consumption | Unit     |

|---------------------|--------------------------|------------------------|----------|

|                     | APB1-Bridge              | 7,78                   |          |

|                     | TIM2                     | 33,06                  |          |

|                     | TIM3                     | 31,94                  |          |

|                     | TIM4                     | 31,67                  |          |

| APB1 (up to 36 MHz) | TIM5                     | 31,94                  |          |

|                     | TIM6                     | 8,06                   |          |

|                     | TIM7                     | 8,06                   |          |

|                     | SPI2/I2S2 <sup>(2)</sup> | 8,33                   |          |

|                     | SPI3/I2S3 <sup>(2)</sup> | 8,33                   |          |

|                     | USART2                   | 12,22                  |          |

|                     | USART3                   | 12,22                  | μA/MHz   |

|                     | UART4                    | 12,22                  | μονικιτε |

|                     | UART5                    | 12,22                  |          |

|                     | I2C1                     | 10,28                  |          |

|                     | I2C2                     | 10,00                  |          |

|                     | USB                      | 18,06                  |          |

|                     | CAN1                     | 18,33                  |          |

|                     | DAC <sup>(3)</sup>       | 8,06                   | ]        |

|                     | WWDG                     | 3,89                   | ]        |

|                     | PWR                      | 1,11                   |          |

|                     | BKP                      | 1,11                   |          |

|                     | IWDG                     | 5,28                   |          |

| Table 20. Peripheral current consumption (continued) | able 20. Peripheral current consun | nption (contin | ued) |

|------------------------------------------------------|------------------------------------|----------------|------|

|------------------------------------------------------|------------------------------------|----------------|------|

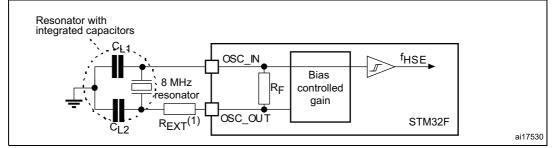

## High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 16 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 23*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                       | Parameter                                                                                     | Conditions                                                                    | Min | Тур | Max | Unit |

|------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>OSC_IN</sub>          | Oscillator frequency                                                                          | -                                                                             | 4   | 8   | 16  | MHz  |

| R <sub>F</sub>               | Feedback resistor                                                                             | -                                                                             | -   | 200 | -   | kΩ   |

| С                            | Recommended load capacitance versus equivalent serial resistance of the crystal $(R_S)^{(3)}$ | R <sub>S</sub> = 30 Ω                                                         | -   | 30  | -   | pF   |

| i <sub>2</sub>               | HSE driving current                                                                           | V <sub>DD</sub> = 3.3 V, V <sub>IN</sub> = V <sub>SS</sub><br>with 30 pF load | -   | -   | 1   | mA   |

| 9 <sub>m</sub>               | Oscillator transconductance                                                                   | Startup                                                                       | 25  | -   | -   | mA/V |

| ${t_{\text{SU(HSE)}}}^{(4)}$ | Startup time                                                                                  | $V_{DD}$ is stabilized                                                        | -   | 2   | -   | ms   |

| Table 23. HSE 4-16 MHz oscillator chara | cteristics <sup>(1)(2)</sup> |

|-----------------------------------------|------------------------------|

|-----------------------------------------|------------------------------|

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

2. Guaranteed by characterization results.

3. The relatively low value of the RF resistor offers a good protection against issues resulting from use in a humid environment, due to the induced leakage and the bias condition change. However, it is recommended to take this point into account if the MCU is used in tough humidity conditions.

4. t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 22*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ . Refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website *www.st.com*.

1. R<sub>EXT</sub> value depends on the crystal characteristics.

DocID14611 Rev 12

# 5.3.8 PLL characteristics

The parameters given in *Table 28* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 10*.

| Symbol               | Devemator                      |     | Value |                    | Unit |

|----------------------|--------------------------------|-----|-------|--------------------|------|

| Symbol               | Parameter                      | Min | Тур   | Max <sup>(1)</sup> | Unit |

| £                    | PLL input clock <sup>(2)</sup> | 1   | 8.0   | 25                 | MHz  |

| f <sub>PLL_IN</sub>  | PLL input clock duty cycle     | 40  | -     | 60                 | %    |

| f <sub>PLL_OUT</sub> | PLL multiplier output clock    | 16  | -     | 72                 | MHz  |

| t <sub>LOCK</sub>    | PLL lock time                  | -   | -     | 200                | μs   |

| Jitter               | Cycle-to-cycle jitter          | -   | -     | 300                | ps   |

| Table 20. PLL characteristics | Table | 28. | PLL | characteristics |

|-------------------------------|-------|-----|-----|-----------------|

|-------------------------------|-------|-----|-----|-----------------|

1. Guaranteed by characterization results.

2. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{\text{PLL}_{OUT}}$ .

# 5.3.9 Memory characteristics

## **Flash memory**

The characteristics are given at  $T_A$  = -40 to 105 °C unless otherwise specified.

| Symbol             | Parameter               | Conditions                                                                             | Min | Тур  | Max <sup>(1)</sup> | Unit |

|--------------------|-------------------------|----------------------------------------------------------------------------------------|-----|------|--------------------|------|

| t <sub>prog</sub>  | 16-bit programming time | $T_A = -40$ to +105 °C                                                                 | 40  | 52.5 | 70                 | μs   |

| t <sub>ERASE</sub> | Page (2 KB) erase time  | $T_A = -40$ to +105 °C                                                                 | 20  | -    | 40                 | ms   |

| t <sub>ME</sub>    | Mass erase time         | $T_A = -40$ to +105 °C                                                                 | 20  | -    | 40                 | ms   |

|                    |                         | Read mode<br>f <sub>HCLK</sub> = 72 MHz with 2 wait<br>states, V <sub>DD</sub> = 3.3 V | -   | -    | 28                 | mA   |

| I <sub>DD</sub>    | Supply current          | Write mode<br>f <sub>HCLK</sub> = 72 MHz, V <sub>DD</sub> = 3.3 V                      | -   | -    | 7                  | mA   |

|                    |                         | Erase mode<br>f <sub>HCLK</sub> = 72 MHz, V <sub>DD</sub> = 3.3 V                      | -   | -    | 5                  | mA   |

|                    |                         | Power-down mode / Halt,<br>$V_{DD}$ = 3.0 to 3.6 V                                     | -   | -    | 50                 | μA   |

| V <sub>prog</sub>  | Programming voltage     | -                                                                                      | 2   | -    | 3.6                | V    |

## Table 29. Flash memory characteristics

1. Guaranteed by design.

| Gumbal                          | Devenueter | Conditions                                                                              | Value              | 11:0:14 |

|---------------------------------|------------|-----------------------------------------------------------------------------------------|--------------------|---------|

| Symbol                          | Parameter  | Conditions                                                                              | Min <sup>(1)</sup> | Unit    |

| N <sub>END</sub>                | Endurance  | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                 | kcycles |

|                                 |            | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                 |         |

| t <sub>RET</sub> Data retention |            | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                 | Years   |

|                                 |            | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                 |         |

Table 30. Flash memory endurance and data retention

1. Guaranteed by characterization results.

2. Cycling performed over the whole temperature range.

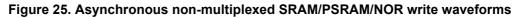

| Symbol                    | Parameter                               | Min                      | Мах                      | Unit |

|---------------------------|-----------------------------------------|--------------------------|--------------------------|------|

| t <sub>w(NE)</sub>        | FSMC_NE low time                        | 5t <sub>HCLK</sub> – 1.5 | 5t <sub>HCLK</sub> + 2   | ns   |

| t <sub>v(NOE_NE)</sub>    | FSMC_NEx low to FSMC_NOE low            | 0.5                      | 1.5                      | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low time                       | 5t <sub>HCLK</sub> – 1.5 | 5t <sub>HCLK</sub> + 1.5 | ns   |

| t <sub>h(NE_NOE)</sub>    | FSMC_NOE high to FSMC_NE high hold time | -1.5                     | -                        | ns   |

| t <sub>v(A_NE)</sub>      | FSMC_NEx low to FSMC_A valid            | -                        | 0                        | ns   |

| t <sub>h(A_NOE)</sub>     | Address hold time after FSMC_NOE high   | 0.1                      | -                        | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid           | -                        | 0                        | ns   |

| t <sub>h(BL_NOE)</sub>    | FSMC_BL hold time after FSMC_NOE high   | 0                        | -                        | ns   |

| t <sub>su(Data_NE)</sub>  | Data to FSMC_NEx high setup time        | 2t <sub>HCLK</sub> + 25  | -                        | ns   |

| t <sub>su(Data_NOE)</sub> | Data to FSMC_NOEx high setup time       | 2t <sub>HCLK</sub> + 25  | -                        | ns   |

| t <sub>h(Data_NOE)</sub>  | Data hold time after FSMC_NOE high      | 0                        | -                        | ns   |

| t <sub>h(Data_NE)</sub>   | Data hold time after FSMC_NEx high      | 0                        | -                        | ns   |

| t <sub>v(NADV_NE)</sub>   | FSMC_NEx low to FSMC_NADV low           | -                        | 5                        | ns   |

| t <sub>w(NADV)</sub>      | FSMC_NADV low time                      | -                        | t <sub>HCLK</sub> + 1.5  | ns   |

Table 31. Asynchronous non-multiplexed SRAM/PSRAM/NOR read timings<sup>(1)</sup>

#### 1. Mode 2/B, C and D only. In Mode 1, FSMC\_NADV is not used.

| Symbol                       | Parameter                                                | Min  | Max | Unit |

|------------------------------|----------------------------------------------------------|------|-----|------|

| t <sub>w(CLK)</sub>          | FSMC_CLK period                                          | 27.7 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>    | FSMC_CLK low to FSMC_NEx low (x = 02)                    | -    | 1.5 | ns   |

| t <sub>d(CLKL-NExH)</sub>    | FSMC_CLK low to FSMC_NEx high (x = 02)                   | 2    | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub>   | FSMC_CLK low to FSMC_NADV low                            | -    | 4   | ns   |

| t <sub>d(CLKL-NADVH)</sub>   | FSMC_CLK low to FSMC_NADV high                           | 5    | -   | ns   |

| t <sub>d(CLKL-AV)</sub>      | FSMC_CLK low to FSMC_Ax valid (x = 1625)                 | -    | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>     | FSMC_CLK low to FSMC_Ax invalid (x = 1625)               | 2    | -   | ns   |

| t <sub>d(CLKL-NOEL)</sub>    | FSMC_CLK low to FSMC_NOE low                             | -    | 1   | ns   |

| t <sub>d(CLKL-NOEH)</sub>    | FSMC_CLK low to FSMC_NOE high                            | 1.5  | -   | ns   |

| t <sub>d(CLKL-ADV)</sub>     | FSMC_CLK low to FSMC_AD[15:0] valid                      | -    | 12  | ns   |

| t <sub>d(CLKL-ADIV)</sub>    | FSMC_CLK low to FSMC_AD[15:0] invalid                    | 0    | -   | ns   |

| t <sub>su(ADV-CLKH)</sub>    | FSMC_A/D[15:0] valid data before FSMC_CLK<br>high        | 6    | -   | ns   |

| t <sub>h(CLKH-ADV)</sub>     | FSMC_A/D[15:0] valid data after FSMC_CLK high            | 0    | -   | ns   |

| t <sub>su(NWAITV-CLKH)</sub> | J(NWAITV-CLKH) FSMC_NWAIT valid before FSMC_CLK high 8 - |      | -   | ns   |

| t <sub>h(CLKH-NWAITV)</sub>  | FSMC_NWAIT valid after FSMC_CLK high                     | 2    | -   | ns   |

Table 35. Synchronous multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup>

2. Guaranteed by characterization results.

| Symbol                       | Parameter                                  | Min  | Мах | Unit |

|------------------------------|--------------------------------------------|------|-----|------|

| t <sub>w(CLK)</sub>          | FSMC_CLK period                            | 27.7 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>    | FSMC_CLK low to FSMC_Nex low (x = 02)      | -    | 2   | ns   |

| t <sub>d(CLKL-NExH)</sub>    | FSMC_CLK low to FSMC_NEx high (x = 02)     | 2    | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub>   | FSMC_CLK low to FSMC_NADV low              | -    | 4   | ns   |

| t <sub>d(CLKL-NADVH)</sub>   | FSMC_CLK low to FSMC_NADV high             | 5    | -   | ns   |

| t <sub>d(CLKL-AV)</sub>      | FSMC_CLK low to FSMC_Ax valid (x = 1625)   | -    | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>     | FSMC_CLK low to FSMC_Ax invalid (x = 1625) | 2    | -   | ns   |

| t <sub>d(CLKL-NWEL)</sub>    | FSMC_CLK low to FSMC_NWE low               | -    | 1   | ns   |

| t <sub>d(CLKL-NWEH)</sub>    | FSMC_CLK low to FSMC_NWE high              | 1    | -   | ns   |

| t <sub>d(CLKL-ADV)</sub>     | FSMC_CLK low to FSMC_AD[15:0] valid        | -    | 12  | ns   |

| t <sub>d(CLKL-ADIV)</sub>    | FSMC_CLK low to FSMC_AD[15:0] invalid      | 3    | -   | ns   |

| t <sub>d(CLKL-Data)</sub>    | FSMC_A/D[15:0] valid after FSMC_CLK low    | -    | 6   | ns   |

| t <sub>d(CLKL-NBLH)</sub>    | FSMC_CLK low to FSMC_NBL high              | 1    | -   | ns   |

| t <sub>su(NWAITV-CLKH)</sub> | FSMC_NWAIT valid before FSMC_CLK high      | 7    | -   | ns   |

| t <sub>h(CLKH-NWAITV)</sub>  | FSMC_NWAIT valid after FSMC_CLK high       | 2    | -   | ns   |

Table 36. Synchronous multiplexed PSRAM write timings<sup>(1)(2)</sup>

2. Guaranteed by characterization results.

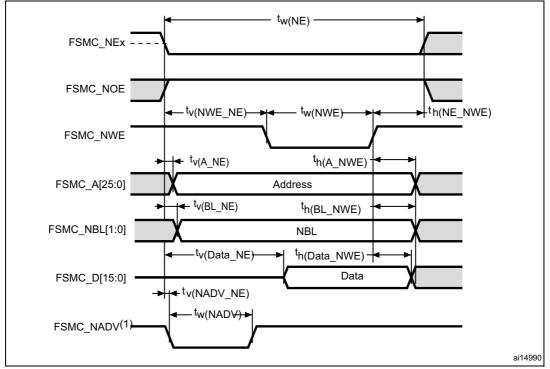

Figure 41. NAND controller waveforms for common memory write access

| Table 40. Switching characteristics for NAND Flash read and write cycles <sup>(1)</sup> | ) |

|-----------------------------------------------------------------------------------------|---|

|-----------------------------------------------------------------------------------------|---|

| Symbol                                 | Parameter                                          | Min                      | Max                      | Unit |

|----------------------------------------|----------------------------------------------------|--------------------------|--------------------------|------|

| t <sub>d(D-NWE)</sub> <sup>(2)</sup>   | FSMC_D[15:0] valid before FSMC_NWE high            | 5t <sub>HCLK</sub> + 12  | -                        | ns   |

| t <sub>w(NOE)</sub> <sup>(2)</sup>     | FSMC_NWE low width                                 | 4t <sub>HCLK-1.5</sub>   | 4t <sub>HCLK+1.5</sub>   | ns   |

| t <sub>su(D-NOE)</sub> <sup>(2)</sup>  | FSMC_D[15:0] valid data before<br>FSMC_NOE<br>high | 25                       | -                        | ns   |

| t <sub>h(NOE-D)</sub> <sup>(2)</sup>   | FSMC_D[15:0] valid data after FSMC_NOE high        | 7                        | -                        | -    |

| t <sub>w(NWE)</sub> <sup>(2)</sup>     | FSMC_NWE low width                                 | 4t <sub>HCLK-1</sub>     | 4t <sub>HCLK+1</sub>     | ns   |

| t <sub>v(NWE-D)</sub> <sup>(2)</sup>   | FSMC_NWE low to FSMC_D[15:0] valid                 | -                        | 0                        | ns   |

| t <sub>h(NWE-D)</sub> <sup>(2)</sup>   | FSMC_NWE high to FSMC_D[15:0] invalid              | 2t <sub>HCLK</sub> + 4   | -                        | ns   |

| t <sub>d(ALE-NWE)</sub> <sup>(3)</sup> | FSMC_ALE valid before FSMC_NWE low                 | -                        | 3t <sub>HCLK</sub> + 1.5 | ns   |

| $t_{h(NWE-ALE)}^{(3)}$                 | FSMC_NWE high to FSMC_ALE invalid                  | 3t <sub>HCLK</sub> + 4.5 | -                        | ns   |

| t <sub>d(ALE-NOE)</sub> <sup>(3)</sup> | FSMC_ALE valid before FSMC_NOE low                 | -                        | 3t <sub>HCLK</sub> + 2   | ns   |

| $t_{h(NOE-ALE)}^{(3)}$                 | FSMC_NWE high to FSMC_ALE invalid                  | 3t <sub>HCLK</sub> + 4.5 | -                        | ns   |

2. Guaranteed by characterization results.

3. Guaranteed by design.

# 5.3.14 I/O port characteristics

# General input/output characteristics

Unless otherwise specified, the parameters given in *Table 46* are derived from tests performed under the conditions summarized in *Table 10*. All I/Os are CMOS and TTL compliant.

| Symbol           | Parameter                                                           | Conditions                                                         | Min                                  | Тур | Max                                | Unit |

|------------------|---------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------|-----|------------------------------------|------|

| V                | Standard IO input low<br>level voltage                              |                                                                    | -0.3                                 | -   | 0.28*(V <sub>DD</sub> -2 V)+0.8 V  | V    |

| V <sub>IL</sub>  | IO FT <sup>(1)</sup> input low level voltage                        | _                                                                  | -0.3                                 | _   | 0.32*(V <sub>DD</sub> -2 V)+0.75 V | V    |

|                  | Standard IO input high<br>level voltage                             | -                                                                  | 0.41*(V <sub>DD</sub> -2 V)+1.3<br>V | -   | V <sub>DD</sub> +0.3               | V    |

| V <sub>IH</sub>  | IO FT <sup>(1)</sup> input high level                               | V <sub>DD</sub> > 2 V                                              | 0.42*()/ 2.)()+1.)/                  |     | 5.5                                | v    |

|                  | voltage                                                             | $V_{DD} \le V$                                                     | 0.42*(V <sub>DD</sub> -2 V)+1 V      | -   | 5.2                                | v    |

| V <sub>hys</sub> | Standard IO Schmitt<br>trigger voltage<br>hysteresis <sup>(2)</sup> | -                                                                  | 200                                  | -   | -                                  | mV   |

| 1170             | IO FT Schmitt trigger voltage hysteresis <sup>(2)</sup>             |                                                                    | 5% V <sub>DD</sub> <sup>(3)</sup>    | -   | -                                  | mV   |

| 1                | Input leakage current (4)                                           | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>Standard I/Os | -                                    | -   | ±1                                 | μA   |

| l <sub>lkg</sub> | input leakage current V                                             | V <sub>IN</sub> = 5 V,<br>I/O FT                                   | -                                    | -   | 3                                  | μΛ   |

| R <sub>PU</sub>  | Weak pull-up equivalent resistor <sup>(5)</sup>                     | $V_{IN} = V_{SS}$                                                  | 30                                   | 40  | 50                                 | kΩ   |

| R <sub>PD</sub>  | Weak pull-down<br>equivalent resistor <sup>(5)</sup>                | $V_{IN} = V_{DD}$                                                  | 30                                   | 40  | 50                                 | kΩ   |

| C <sub>IO</sub>  | I/O pin capacitance                                                 | -                                                                  | -                                    | 5   | -                                  | pF   |

1. FT = Five-volt tolerant. In order to sustain a voltage higher than V<sub>DD</sub>+0.3 the internal pull-up/pull-down resistors must be disabled.

2. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by characterization results.

3. With a minimum of 100 mV.

4. Leakage could be higher than max. if negative current is injected on adjacent pins.

Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This MOS/NMOS contribution to the series resistance is minimum (~10% order).

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 42* and *Figure 43* for standard I/Os, and in *Figure 44* and *Figure 45* for 5 V tolerant I/Os.

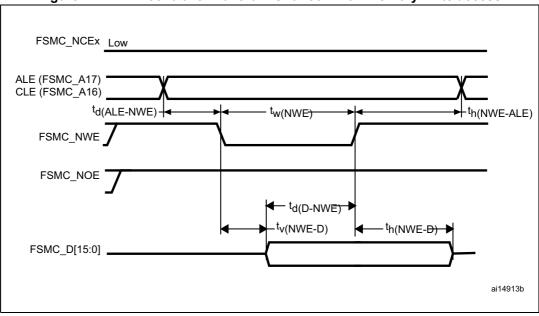

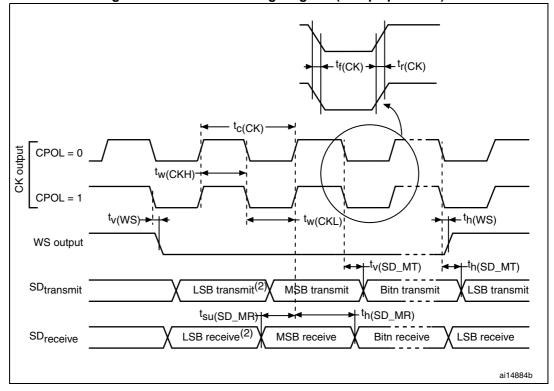

Figure 52. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Measurement points are done at CMOS levels: 0.3 ×  $V_{DD}$  and 0.7 ×  $V_{DD.}$

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

## Figure 53. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

1. Guaranteed by characterization results.

2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

#### Table 66. LFBGA144 recommended PCB design rules (0.8 mm pitch BGA) (continued)

| Dimension         | Recommended values                                                |

|-------------------|-------------------------------------------------------------------|

| Dsm               | 0.470 mm typ. (depends on the solder mask registration tolerance) |

| Stencil opening   | 0.400 mm                                                          |

| Stencil thickness | Between 0.100 mm to 0.125 mm                                      |

| Pad trace width   | 0.120 mm                                                          |

| Ball Diameter     | 0.400 mm                                                          |

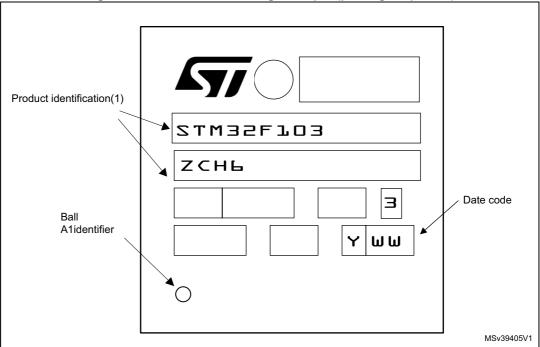

## Device marking for LFBGA144 package

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Figure 64. LFBGA144 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

| Cumhal   |       | millimeters |       | inches <sup>(1)</sup> |        |        |

|----------|-------|-------------|-------|-----------------------|--------|--------|

| Symbol - | Min   | Тур         | Мах   | Min                   | Тур    | Max    |

| е        | -     | 0.500       | -     | -                     | 0.0197 | -      |

| L        | 0.450 | 0.600       | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1       | -     | 1.000       | -     | -                     | 0.0394 | -      |

| k        | 0°    | 3.5°        | 7°    | 0°                    | 3.5°   | 7°     |

| CCC      | -     | -           | 0.08  | -                     | -      | 0.0031 |

# Table 72. LQPF100 – 14 x 14 mm 100-pin low-profile quad flat package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

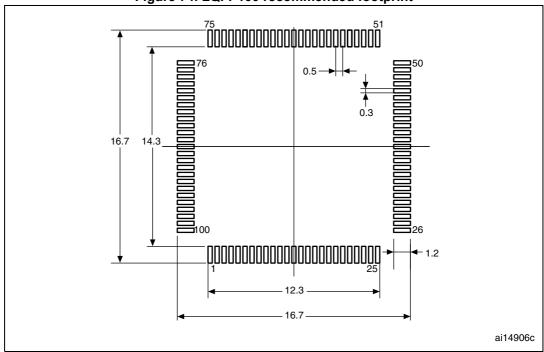

# Figure 74. LQFP100 recommended footprint

1. Dimensions are in millimeters.

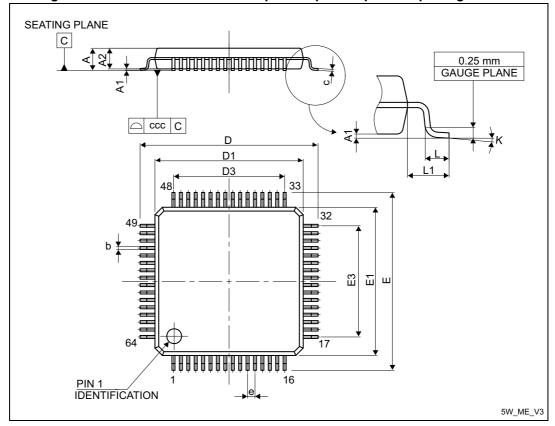

# 6.6 LQFP64 package information

Figure 76. LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package outline

#### Table 73. LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package mechanical data

| Symbol |       | millimeters |       | inches <sup>(1)</sup> |        |        |

|--------|-------|-------------|-------|-----------------------|--------|--------|

|        | Min   | Тур         | Мах   | Min                   | Тур    | Max    |

| А      | -     | -           | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050 | -           | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350 | 1.400       | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170 | 0.220       | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090 | -           | 0.200 | 0.0035                | -      | 0.0079 |

| D      | -     | 12.000      | -     | -                     | 0.4724 | -      |

| D1     | -     | 10.000      | -     | -                     | 0.3937 | -      |

| D3     | -     | 7.500       | -     | -                     | 0.2953 | -      |

| E      | -     | 12.000      | -     | -                     | 0.4724 | -      |

| E1     | -     | 10.000      | -     | -                     | 0.3937 | -      |

<sup>1.</sup> Drawing is not in scale.