Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 72MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB            |

| Peripherals                | DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT            |

| Number of I/O              | 80                                                                      |

| Program Memory Size        | 512KB (512K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 64K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 100-LFBGA                                                               |

| Supplier Device Package    | 100-LFBGA (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f103veh6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 8 | Revi | sion his | tory                                    |

|---|------|----------|-----------------------------------------|

| 7 | Part | number   | ing                                     |

|   |      | 6.7.2    | Selecting the product temperature range |

|   |      | 6.7.1    | Reference document                      |

|   | 6.7  | Therma   | al characteristics                      |

|   | 6.6  | LQFP6    | 4 package information 130               |

|   | 6.5  | LQFP1    | 00 package information                  |

|   | 6.4  | LQFP1    | 44 package information                  |

|   | 6.3  | WLCS     | P64 package information 121             |

|   | 6.2  | LFBGA    | 100 package information 118             |

|   | 6.1  | LFBGA    | 144 package information 115             |

| 6 | Pack | age info | ormation                                |

|   |      | 5.3.21   | Temperature sensor characteristics      |

|   |      | 5.3.20   | DAC electrical specifications           |

## 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32F103xC, STM32F103xD and STM32F103xE high-density performance line microcontrollers. For more details on the whole STMicroelectronics STM32F103xC/D/E family, please refer to *Section 2.2: Full compatibility throughout the family*.

The high-density STM32F103xC/D/E datasheet should be read in conjunction with the STM32F10xxx reference manual.

For information on programming, erasing and protection of the internal Flash memory please refer to the *STM32F10xxx* Flash programming manual. The reference and Flash programming manuals are both available from the STMicroelectronics website *www.st.com*.

For information on the Cortex<sup>®</sup>-M3 core please refer to the Cortex<sup>®</sup>-M3 Technical Reference Manual, available from the *www.arm.com* website at the following address: *http://infocenter.arm.com*.

# 2 Description

The STM32F103xC, STM32F103xD and STM32F103xE performance line family incorporates the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M3 32-bit RISC core operating at a 72 MHz frequency, high-speed embedded memories (Flash memory up to 512 Kbytes and SRAM up to 64 Kbytes), and an extensive range of enhanced I/Os and peripherals connected to two APB buses. All devices offer three 12-bit ADCs, four general-purpose 16-bit timers plus two PWM timers, as well as standard and advanced communication interfaces: up to two I<sup>2</sup>Cs, three SPIs, two I<sup>2</sup>Ss, one SDIO, five USARTs, an USB and a CAN.

The STM32F103xC/D/E high-density performance line family operates in the -40 to +105 °C temperature range, from a 2.0 to 3.6 V power supply. A comprehensive set of power-saving mode allows the design of low-power applications.

These features make the STM32F103xC/D/E high-density performance line microcontroller family suitable for a wide range of applications such as motor drives, application control, medical and handheld equipment, PC and gaming peripherals, GPS platforms, industrial applications, PLCs, inverters, printers, scanners, alarm systems video intercom, and HVAC.

## 2.3 Overview

## 2.3.1 ARM<sup>®</sup> Cortex<sup>®</sup>-M3 core with embedded Flash and SRAM

The ARM Cortex<sup>®</sup>-M3 processor is the latest generation of ARM processors for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM Cortex<sup>®</sup>-M3 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

With its embedded ARM core, STM32F103xC, STM32F103xD and STM32F103xE performance line family is compatible with all ARM tools and software.

*Figure 1* shows the general block diagram of the device family.

## 2.3.2 Embedded Flash memory

Up to 512 Kbytes of embedded Flash is available for storing programs and data.

## 2.3.3 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

## 2.3.4 Embedded SRAM

Up to 64 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states.

## 2.3.5 FSMC (flexible static memory controller)

The FSMC is embedded in the STM32F103xC, STM32F103xD and STM32F103xE performance line family. It has four Chip Select outputs supporting the following modes: PC Card/Compact Flash, SRAM, PSRAM, NOR and NAND.

Functionality overview:

- The three FSMC interrupt lines are ORed in order to be connected to the NVIC

- Write FIFO

- Code execution from external memory except for NAND Flash and PC Card

- The targeted frequency, f<sub>CLK</sub>, is HCLK/2, so external access is at 36 MHz when HCLK is at 72 MHz and external access is at 24 MHz when HCLK is at 48 MHz

## 2.3.10 Boot modes

At startup, boot pins are used to select one of three boot options:

- Boot from user Flash: you have an option to boot from any of two memory banks. By default, boot from Flash memory bank 1 is selected. You can choose to boot from Flash memory bank 2 by setting a bit in the option bytes.

- Boot from system memory

- Boot from embedded SRAM

The boot loader is located in system memory. It is used to reprogram the Flash memory by using USART1.

## 2.3.11 **Power supply schemes**

- $V_{DD}$  = 2.0 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through V<sub>DD</sub> pins.

- $V_{SSA}$ ,  $V_{DDA} = 2.0$  to 3.6 V: external analog power supplies for ADC, DAC, Reset blocks, RCs and PLL (minimum voltage to be applied to VDDA is 2.4 V when the ADC or DAC is used).  $V_{DDA}$  and  $V_{SSA}$  must be connected to  $V_{DD}$  and  $V_{SS}$ , respectively.

- V<sub>BAT</sub> = 1.8 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

For more details on how to connect power pins, refer to *Figure 12: Power supply scheme*.

## 2.3.12 Power supply supervisor

The device has an integrated power-on reset (POR)/power-down reset (PDR) circuitry. It is always active, and ensures proper operation starting from/down to 2 V. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$ , without the need for an external reset circuit.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software. Refer to *Table 12: Embedded reset and power control block characteristics* for the values of  $V_{POR/PDR}$  and  $V_{PVD}$ .

## 2.3.13 Voltage regulator

The regulator has three operation modes: main (MR), low-power (LPR) and power down.

- MR is used in the nominal regulation mode (Run)

- LPR is used in the Stop modes.

- Power down is used in Standby mode: the regulator output is in high impedance: the kernel circuitry is powered down, inducing zero consumption (but the contents of the registers and SRAM are lost)

This regulator is always enabled after reset. It is disabled in Standby mode.

periodic interrupt. It is clocked by a 32.768 kHz external crystal, resonator or oscillator, the internal low-power RC oscillator or the high-speed external clock divided by 128. The internal low-speed RC has a typical frequency of 40 kHz. The RTC can be calibrated using an external 512 Hz output to compensate for any natural quartz deviation. The RTC features a 32-bit programmable counter for long term measurement using the Compare register to generate an alarm. A 20-bit prescaler is used for the time base clock and is by default configured to generate a time base of 1 second from a clock at 32.768 kHz.

## 2.3.17 Timers and watchdogs

The high-density STM32F103xC/D/E performance line devices include up to two advancedcontrol timers, up to four general-purpose timers, two basic timers, two watchdog timers and a SysTick timer.

Table 4 compares the features of the advanced-control, general-purpose and basic timers.

| Timer                           | Counter resolution | Counter<br>type         | Prescaler<br>factor                   | DMA request generation | Capture/compare<br>channels | Complementary<br>outputs |  |  |  |  |

|---------------------------------|--------------------|-------------------------|---------------------------------------|------------------------|-----------------------------|--------------------------|--|--|--|--|

| TIM1,<br>TIM8                   | 16-bit             | Up,<br>down,<br>up/down | Any integer<br>between 1<br>and 65536 | Yes                    | 4                           | Yes                      |  |  |  |  |

| TIM2,<br>TIM3,<br>TIM4,<br>TIM5 | 16-bit             | Up,<br>down,<br>up/down | Any integer<br>between 1<br>and 65536 | Yes                    | 4                           | No                       |  |  |  |  |

| TIM6,<br>TIM7                   | 16-bit             | Up                      | Any integer<br>between 1<br>and 65536 | Yes                    | 0                           | No                       |  |  |  |  |

Table 4. High-density timer feature comparison

| Pins     |          |         |        |         |         | nign-density S    |                     | 52F1                       | IU3XC/D/E PI                                     | n definitions (continued                                                                  | -                        |

|----------|----------|---------|--------|---------|---------|-------------------|---------------------|----------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------|

|          | 1        | Pir     | ıs     | 1       | 1       |                   |                     |                            |                                                  | Alternate funct                                                                           | tions <sup>(+)</sup>     |

| LFBGA144 | LFBGA100 | WLCSP64 | LQFP64 | LQFP100 | LQFP144 | Pin name          | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                                                   | Remap                    |

| M11      | K8       | G2      | 33     | 51      | 73      | PB12              | I/O                 | FT                         | PB12                                             | SPI2_NSS/I2S2_WS/<br>I2C2_SMBA/<br>USART3_CK <sup>(9)</sup> /<br>TIM1_BKIN <sup>(9)</sup> | -                        |

| M12      | J8       | G1      | 34     | 52      | 74      | PB13              | I/O                 | FT                         | PB13                                             | SPI2_SCK/I2S2_CK<br>USART3_CTS <sup>(9)</sup> /<br>TIM1_CH1N                              | -                        |

| L11      | H8       | F2      | 35     | 53      | 75      | PB14              | I/O                 | FT                         | PB14                                             | SPI2_MISO/TIM1_CH2N<br>USART3_RTS <sup>(9)</sup> /                                        | -                        |

| L12      | G8       | F1      | 36     | 54      | 76      | PB15              | I/O                 | FT                         | PB15                                             | SPI2_MOSI/I2S2_SD<br>TIM1_CH3N <sup>(9)</sup> /                                           | -                        |

| L9       | K9       | -       | -      | 55      | 77      | PD8               | I/O                 | FT                         | PD8                                              | FSMC_D13                                                                                  | USART3_TX                |

| K9       | J9       | -       | -      | 56      | 78      | PD9               | I/O                 | FT                         | PD9                                              | FSMC_D14                                                                                  | USART3_RX                |

| J9       | H9       | -       | -      | 57      | 79      | PD10              | I/O                 | FT                         | PD10                                             | FSMC_D15                                                                                  | USART3_CK                |

| H9       | G9       | -       | -      | 58      | 80      | PD11              | I/O                 | FT                         | PD11                                             | FSMC_A16                                                                                  | USART3_CTS               |

| L10      | K10      | -       | -      | 59      | 81      | PD12              | I/O                 | FT                         | PD12                                             | FSMC_A17                                                                                  | TIM4_CH1 /<br>USART3_RTS |

| K10      | J10      | -       | -      | 60      | 82      | PD13              | I/O                 | FT                         | PD13                                             | FSMC_A18                                                                                  | TIM4_CH2                 |

| G8       | -        | -       | -      | -       | 83      | V <sub>SS_8</sub> | S                   | -                          | V <sub>SS_8</sub>                                | -                                                                                         | -                        |

| F8       | -        | -       | -      | -       | 84      | V <sub>DD_8</sub> | S                   | -                          | V <sub>DD_8</sub>                                | -                                                                                         | -                        |

| K11      | H10      | -       | -      | 61      | 85      | PD14              | I/O                 | FT                         | PD14                                             | FSMC_D0                                                                                   | TIM4_CH3                 |

| K12      | G10      | -       | -      | 62      | 86      | PD15              | I/O                 | FT                         | PD15                                             | FSMC_D1                                                                                   | TIM4_CH4                 |

| J12      | -        | -       | -      | -       | 87      | PG2               | I/O                 | FT                         | PG2                                              | FSMC_A12                                                                                  | -                        |

| J11      | -        | -       | -      | -       | 88      | PG3               | I/O                 | FT                         | PG3                                              | FSMC_A13                                                                                  | -                        |

| J10      | -        | -       | -      | -       | 89      | PG4               | I/O                 | FT                         | PG4                                              | FSMC_A14                                                                                  | -                        |

| H12      | -        | -       | -      | -       | 90      | PG5               | I/O                 | FT                         | PG5                                              | FSMC_A15                                                                                  | -                        |

| H11      | -        | -       | -      | -       | 91      | PG6               | I/O                 | FT                         | PG6                                              | FSMC_INT2                                                                                 | -                        |

| H10      | -        | -       | -      | -       | 92      | PG7               | I/O                 | FT                         | PG7                                              | FSMC_INT3                                                                                 | -                        |

| G11      | -        | -       | -      | -       | 93      | PG8               | I/O                 | FT                         | PG8                                              | -                                                                                         | -                        |

| G10      | -        | -       | -      | -       | 94      | V <sub>SS_9</sub> | S                   | -                          | V <sub>SS_9</sub>                                | -                                                                                         | -                        |

| F10      | -        | -       | -      | -       | 95      | $V_{DD_9}$        | S                   | -                          | $V_{DD_9}$                                       | -                                                                                         | -                        |

| Table 5. High-density STM32F103xC/D/E pin definitions (continued) | C/D/E pin definitions (continued) |

|-------------------------------------------------------------------|-----------------------------------|

|-------------------------------------------------------------------|-----------------------------------|

|          |          | Pir     | IS     |         |         |                   |                     |                            |                                                  | Alternate functions <sup>(4)</sup> |       |  |  |

|----------|----------|---------|--------|---------|---------|-------------------|---------------------|----------------------------|--------------------------------------------------|------------------------------------|-------|--|--|

| LFBGA144 | LFBGA100 | WLCSP64 | LQFP64 | LQFP100 | LQFP144 | Pin name          | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                            | Remap |  |  |

| A5       | D4       | -       | -      | 97      | 141     | PE0               | I/O                 | FT                         | PE0                                              | TIM4_ETR / FSMC_NBL0               | -     |  |  |

| A4       | C4       | -       | -      | 98      | 142     | PE1               | I/O                 | FT                         | PE1                                              | FSMC_NBL1                          | -     |  |  |

| E5       | E5       | A7      | 63     | 99      | 143     | V <sub>SS_3</sub> | S                   | -                          | V <sub>SS_3</sub>                                | -                                  | -     |  |  |

| F5       | F5       | A8      | 64     | 100     | 144     | $V_{DD_3}$        | S                   | -                          | V <sub>DD_3</sub>                                | -                                  | _     |  |  |

Table 5. High-density STM32F103xC/D/E pin definitions (continued)

1. I = input, O = output, S = supply.

2. FT = 5 V tolerant.

3. Function availability depends on the chosen device.

- 4. If several peripherals share the same I/O pin, to avoid conflict between these alternate functions only one peripheral should be enabled at a time through the peripheral clock enable bit (in the corresponding RCC peripheral clock enable register).

- PC13, PC14 and PC15 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 in output mode is limited: the speed should not exceed 2 MHz with a maximum load of 30 pF and these IOs must not be used as a current source (e.g. to drive an LED).

- 6. Main function after the first backup domain power-up. Later on, it depends on the contents of the Backup registers even after reset (because these registers are not reset by the main reset). For details on how to manage these IOs, refer to the Battery backup domain and BKP register description sections in the STM32F10xxx reference manual, available from the STMicroelectronics website: www.st.com.

- 7. In the WCLSP64 package, the PC3 I/O pin is not bonded and it must be configured by software to output mode (Push-pull) and writing 0 to the data register in order to avoid an extra consumption during low-power modes.

- 8. Unlike in the LQFP64 package, there is no PC3 in the WLCSP package. The V<sub>REF+</sub> functionality is provided instead.

- This alternate function can be remapped by software to some other port pins (if available on the used package). For more

details, refer to the Alternate function I/O and debug configuration section in the STM32F10xxx reference manual,

available from the STMicroelectronics website: www.st.com.

- 10. For the WCLSP64/LQFP64 package, the pins number 5 and 6 are configured as OSC\_IN/OSC\_OUT after reset, however the functionality of PD0 and PD1 can be remapped by software on these pins. For the LQFP100/BGA100 and LQFP144/BGA144 packages, PD0 and PD1 are available by default, so there is no need for remapping. For more details, refer to Alternate function I/O and debug configuration section in the STM32F10xxx reference manual.

- 11. For devices delivered in LQFP64 packages, the FSMC function is not available.

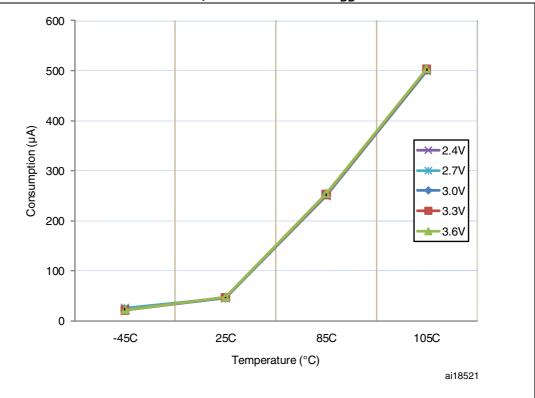

Figure 17. Typical current consumption in Stop mode with regulator in run mode versus temperature at different V<sub>DD</sub> values

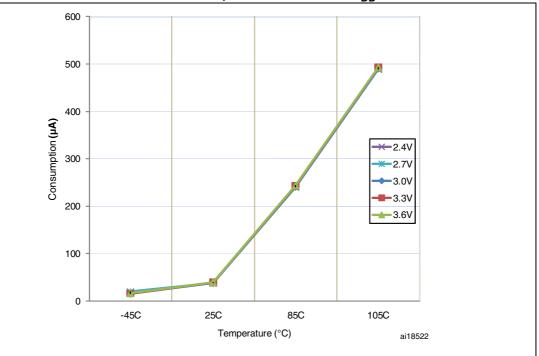

Figure 18. Typical current consumption in Stop mode with regulator in low-power mode versus temperature at different V<sub>DD</sub> values

DocID14611 Rev 12

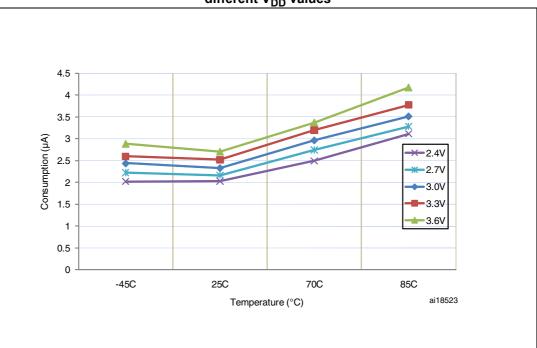

Figure 19. Typical current consumption in Standby mode versus temperature at different  $\rm V_{DD}$  values

#### **Typical current consumption**

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load).

- All peripherals are disabled except if it is explicitly mentioned.

- The Flash access time is adjusted to f<sub>HCLK</sub> frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 48 MHZ and 2 wait states above).

- Ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in *Table 10*.

- Prefetch is ON (Reminder: this bit must be set before clock setting and bus prescaling)

When the peripherals are enabled  $f_{PCLK1} = f_{HCLK}/4$ ,  $f_{PCLK2} = f_{HCLK}/2$ ,  $f_{ADCCLK} = f_{PCLK2}/4$

|                 |                                  |                                 |                   | Туј                                       | p <sup>(1)</sup>            |      |

|-----------------|----------------------------------|---------------------------------|-------------------|-------------------------------------------|-----------------------------|------|

| Symbol          | Parameter                        | Conditions                      | f <sub>HCLK</sub> | All peripherals<br>enabled <sup>(2)</sup> | All peripherals<br>disabled | Unit |

|                 |                                  |                                 | 72 MHz            | 51                                        | 30.5                        |      |

|                 |                                  |                                 | 48 MHz            | 34.6                                      | 20.7                        |      |

|                 |                                  |                                 | 36 MHz            | 26.6                                      | 16.2                        |      |

|                 |                                  |                                 | 24 MHz            | 18.5                                      | 11.4                        |      |

|                 |                                  |                                 | 16 MHz            | 12.8                                      | 8.2                         |      |

|                 |                                  | External clock <sup>(3)</sup>   | 8 MHz             | 7.2                                       | 5                           | mA   |

|                 |                                  |                                 | 4 MHz             | 4.2                                       | 3.1                         |      |

|                 | Supply<br>current in<br>Run mode |                                 | 2 MHz             | 2.7                                       | 2.1                         |      |

|                 |                                  |                                 | 1 MHz             | 2                                         | 1.7                         |      |

|                 |                                  |                                 | 500 kHz           | 1.6                                       | 1.4                         |      |

| I <sub>DD</sub> |                                  |                                 | 125 kHz           | 1.3                                       | 1.2                         |      |

| DD              |                                  |                                 | 64 MHz            | 45                                        | 27                          |      |

|                 |                                  |                                 | 48 MHz            | 34                                        | 20.1                        |      |

|                 |                                  |                                 | 36 MHz            | 26                                        | 15.6                        |      |

|                 |                                  | Running on high                 | 24 MHz            | 17.9                                      | 10.8                        |      |

|                 |                                  | speed internal RC               | 16 MHz            | 12.2                                      | 7.6                         |      |

|                 |                                  | (HSI), AHB<br>prescaler used to | 8 MHz             | 6.6                                       | 4.4                         | mA   |

|                 |                                  | reduce the                      | 4 MHz             | 3.6                                       | 2.5                         |      |

|                 |                                  | frequency                       | 2 MHz             | 2.1                                       | 1.5                         |      |

|                 |                                  |                                 | 1 MHz             | 1.4                                       | 1.1                         |      |

|                 |                                  |                                 | 500 kHz           | 1                                         | 0.8                         |      |

|                 |                                  |                                 | 125 kHz           | 0.7                                       | 0.6                         |      |

# Table 18. Typical current consumption in Run mode, code with data processing<br/>running from Flash

1. Typical values are measures at  $T_A$  = 25 °C,  $V_{DD}$  = 3.3 V.

2. Add an additional power consumption of 0.8 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

3. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

## 5.3.8 PLL characteristics

The parameters given in *Table 28* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 10*.

| Symbol               | Devementer                     |     | Unit |                    |      |

|----------------------|--------------------------------|-----|------|--------------------|------|

|                      | Parameter                      | Min | Тур  | Max <sup>(1)</sup> | Unit |

| £                    | PLL input clock <sup>(2)</sup> | 1   | 8.0  | 25                 | MHz  |

| f <sub>PLL_IN</sub>  | PLL input clock duty cycle     | 40  | -    | 60                 | %    |

| f <sub>PLL_OUT</sub> | PLL multiplier output clock    | 16  | -    | 72                 | MHz  |

| t <sub>LOCK</sub>    | PLL lock time                  | -   | -    | 200                | μs   |

| Jitter               | Cycle-to-cycle jitter          | -   | -    | 300                | ps   |

1. Guaranteed by characterization results.

2. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{\text{PLL}_{OUT}}$ .

## 5.3.9 Memory characteristics

#### **Flash memory**

The characteristics are given at  $T_A$  = -40 to 105 °C unless otherwise specified.

| Symbol             | Parameter               | Conditions                                                                             | Min | Тур  | Max <sup>(1)</sup> | Unit |

|--------------------|-------------------------|----------------------------------------------------------------------------------------|-----|------|--------------------|------|

| t <sub>prog</sub>  | 16-bit programming time | $T_A = -40$ to +105 °C                                                                 | 40  | 52.5 | 70                 | μs   |

| t <sub>ERASE</sub> | Page (2 KB) erase time  | $T_A = -40$ to +105 °C                                                                 | 20  | -    | 40                 | ms   |

| t <sub>ME</sub>    | Mass erase time         | $T_A = -40$ to +105 °C                                                                 | 20  | -    | 40                 | ms   |

|                    |                         | Read mode<br>f <sub>HCLK</sub> = 72 MHz with 2 wait<br>states, V <sub>DD</sub> = 3.3 V | -   | -    | 28                 | mA   |

| I <sub>DD</sub>    | Supply current          | Write mode<br>f <sub>HCLK</sub> = 72 MHz, V <sub>DD</sub> = 3.3 V                      | -   | -    | 7                  | mA   |

|                    |                         | Erase mode<br>f <sub>HCLK</sub> = 72 MHz, V <sub>DD</sub> = 3.3 V                      | -   | -    | 5                  | mA   |

|                    |                         | Power-down mode / Halt,<br>$V_{DD}$ = 3.0 to 3.6 V                                     | -   | -    | 50                 | μA   |

| V <sub>prog</sub>  | Programming voltage     | -                                                                                      | 2   | -    | 3.6                | V    |

#### Table 29. Flash memory characteristics

1. Guaranteed by design.

## 5.3.10 FSMC characteristics

## Asynchronous waveforms and timings

*Figure 24* through *Figure 27* represent asynchronous waveforms and *Table 31* through *Table 34* provide the corresponding timings. The results shown in these tables are obtained with the following FSMC configuration:

- AddressSetupTime = 0

- AddressHoldTime = 1

- DataSetupTime = 1

#### Figure 24. Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms

1. Mode 2/B, C and D only. In Mode 1, FSMC\_NADV is not used.

|                           | -                                                         |                         | •                       |      |

|---------------------------|-----------------------------------------------------------|-------------------------|-------------------------|------|

| Symbol                    | Parameter                                                 | Min                     | Мах                     | Unit |

| t <sub>h(AD_NADV)</sub>   | FSMC_AD (address) valid hold time after<br>FSMC_NADV high | t <sub>HCLK</sub> – 3   | -                       | ns   |

| t <sub>h(A_NWE)</sub>     | Address hold time after FSMC_NWE high                     | 4t <sub>HCLK</sub>      | -                       | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid                             | -                       | 1.6                     | ns   |

| t <sub>h(BL_NWE)</sub>    | FSMC_BL hold time after FSMC_NWE high                     | t <sub>HCLK</sub> – 1.5 | -                       | ns   |

| t <sub>v(Data_NADV)</sub> | FSMC_NADV high to Data valid                              | -                       | t <sub>HCLK</sub> + 1.5 | ns   |

| t <sub>h(Data_NWE)</sub>  | Data hold time after FSMC_NWE high                        | t <sub>HCLK</sub> – 5   | -                       | ns   |

Table 34. Asynchronous multiplexed PSRAM/NOR write timings<sup>(1)(2)</sup>

1. C<sub>L</sub> = 15 pF.

2. BGuaranteed by characterization results.

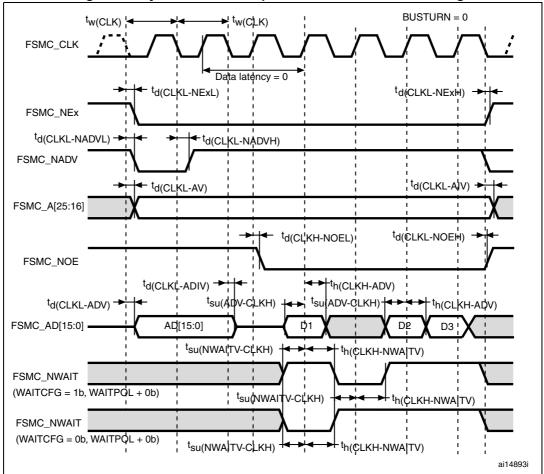

#### Synchronous waveforms and timings

*Figure 28* through *Figure 31* represent synchronous waveforms and *Table 36* through *Table 38* provide the corresponding timings. The results shown in these tables are obtained with the following FSMC configuration:

- BurstAccessMode = FSMC\_BurstAccessMode\_Enable;

- MemoryType = FSMC\_MemoryType\_CRAM;

- WriteBurst = FSMC\_WriteBurst\_Enable;

- CLKDivision = 1; (0 is not supported, see the STM32F10xxx reference manual)

- DataLatency = 1 for NOR Flash; DataLatency = 0 for PSRAM

#### Figure 28. Synchronous multiplexed NOR/PSRAM read timings

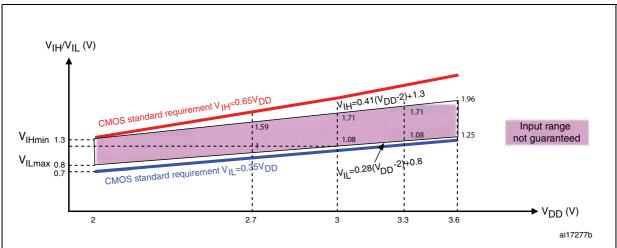

Figure 42. Standard I/O input characteristics - CMOS port

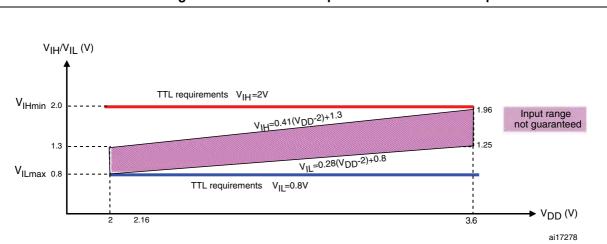

Figure 43. Standard I/O input characteristics - TTL port

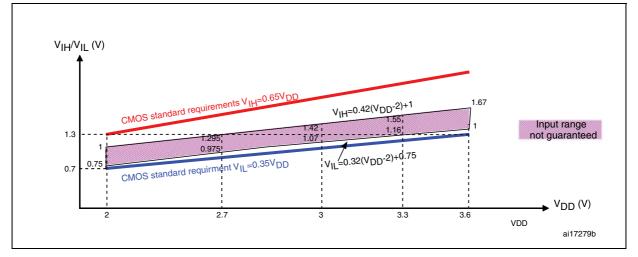

Figure 44. 5 V tolerant I/O input characteristics - CMOS port

## 5.3.18 CAN (controller area network) interface

Refer to Section 5.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CAN\_TX and CAN\_RX).

## 5.3.19 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 59* are preliminary values derived from tests performed under ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 10*.

Note: It is recommended to perform a calibration after each power-up.

| Symbol                           | Parameter                                                                                         | Conditions                                            | Min                                                                        | Тур                | Max               | Unit               |

|----------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------|--------------------|-------------------|--------------------|

| V <sub>DDA</sub>                 | Power supply                                                                                      | -                                                     | 2.4                                                                        | -                  | 3.6               | V                  |

| V <sub>REF+</sub>                | Positive reference voltage                                                                        | -                                                     | 2.4                                                                        | -                  | V <sub>DDA</sub>  | V                  |

| V <sub>REF-</sub>                | Negative reference voltage                                                                        | -                                                     | 0                                                                          | •                  |                   | V                  |

| I <sub>VREF</sub>                | Current on the V <sub>REF</sub> input pin                                                         | -                                                     | -                                                                          | 160 <sup>(1)</sup> | 220               | μA                 |

| f <sub>ADC</sub>                 | ADC clock frequency                                                                               | -                                                     | 0.6                                                                        | -                  | 14                | MHz                |

| f <sub>S</sub> <sup>(2)</sup>    | Sampling rate                                                                                     | -                                                     | 0.05                                                                       | -                  | 1                 | MHz                |

| £ (2)                            | External trigger frequency                                                                        | f <sub>ADC</sub> = 14 MHz                             | -                                                                          | -                  | 823               | kHz                |

| f <sub>TRIG</sub> <sup>(2)</sup> | External trigger frequency                                                                        | -                                                     | -                                                                          | -                  | 17                | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                 | Conversion voltage range <sup>(3)</sup> - 0 (V <sub>SSA</sub> or V <sub>R</sub><br>tied to ground |                                                       | 0 (V <sub>SSA</sub> or V <sub>REF-</sub><br>tied to ground)                | -                  | V <sub>REF+</sub> | V                  |

| R <sub>AIN</sub> <sup>(2)</sup>  | External input impedance                                                                          | See <i>Equation 1</i> and <i>Table 60</i> for details | -                                                                          | -                  | 50                | κΩ                 |

| R <sub>ADC</sub> <sup>(2)</sup>  | Sampling switch resistance                                                                        | -                                                     | -                                                                          | -                  | 1                 | κΩ                 |

| C <sub>ADC</sub> <sup>(2)</sup>  | Internal sample and hold capacitor                                                                | -                                                     | -                                                                          | -                  | 8                 | pF                 |

| + (2)                            | Collibration time                                                                                 | f <sub>ADC</sub> = 14 MHz                             | 5.                                                                         | μs                 |                   |                    |

| t <sub>CAL</sub> <sup>(2)</sup>  | Calibration time                                                                                  | -                                                     | 83                                                                         |                    |                   | 1/f <sub>ADC</sub> |

| t <sub>lat</sub> (2)             | Injection trigger conversion                                                                      | f <sub>ADC</sub> = 14 MHz                             | -                                                                          | -                  | 0.214             | μs                 |

| <sup>4</sup> lat` ′              | latency                                                                                           | -                                                     | -                                                                          | -                  | 3 <sup>(4)</sup>  | 1/f <sub>ADC</sub> |

| t <sub>latr</sub> (2)            | Regular trigger conversion                                                                        | f <sub>ADC</sub> = 14 MHz                             | -                                                                          | -                  | 0.143             | μs                 |

| 'latr' '                         | latency                                                                                           | -                                                     | -                                                                          | -                  | 2 <sup>(4)</sup>  | 1/f <sub>ADC</sub> |

| ts <sup>(2)</sup>                | Compling time                                                                                     | f <sub>ADC</sub> = 14 MHz                             | 0.107                                                                      | -                  | 17.1              | μs                 |

| ι <sub>S`</sub> ΄                | Sampling time                                                                                     | -                                                     | 1.5                                                                        | -                  | 239.5             | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(2)</sup> | Power-up time                                                                                     | -                                                     | 0                                                                          | 0                  | 1                 | μs                 |

|                                  |                                                                                                   | f <sub>ADC</sub> = 14 MHz                             | 1                                                                          | -                  | 18                | μs                 |

| t <sub>CONV</sub> <sup>(2)</sup> | Total conversion time<br>(including sampling time)                                                | -                                                     | 14 to 252 (t <sub>S</sub> for sampling +12.5 for successive approximation) |                    |                   | 1/f <sub>ADC</sub> |

Table 59. ADC characteristics

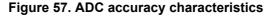

| Symbol | Parameter                    | Test conditions                                                                     | Тур  | Max <sup>(4)</sup> | Unit |

|--------|------------------------------|-------------------------------------------------------------------------------------|------|--------------------|------|

| ET     | Total unadjusted error       | 6 - 50 MUL                                                                          | ±2   | ±5                 |      |

| EO     | Offset error                 | f <sub>PCLK2</sub> = 56 MHz,<br>f <sub>ADC</sub> = 14 MHz, R <sub>AIN</sub> < 10 kΩ | ±1.5 | ±2.5               |      |

| EG     | Gain error                   | $V_{DDA} = 2.4 V \text{ to } 3.6 V$                                                 | ±1.5 | ±3                 | LSB  |

| ED     | Differential linearity error | Measurements made after<br>ADC calibration                                          | ±1   | ±2                 |      |

| EL     | Integral linearity error     |                                                                                     | ±1.5 | ±3                 |      |

Table 62. ADC accuracy<sup>(1) (2)(3)</sup>

1. ADC DC accuracy values are measured after internal calibration.

2. Better performance could be achieved in restricted  $V_{DD}$ , frequency,  $V_{REF}$  and temperature ranges.

ADC Accuracy vs. Negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current.

Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 5.3.14 does not affect the ADC accuracy.

4. Guaranteed by characterization results.

- 1. Example of an actual transfer curve.

- 2. Ideal transfer curve.

- 3. End point correlation line.

- 4. ET = Total Unadjusted Error: maximum deviation between the actual and the ideal transfer curves. EO = Offset Error: deviation between the first actual transition and the first ideal one. EG = Gain Error: deviation between the last ideal transition and the last actual one. ED = Differential Linearity Error: maximum deviation between actual steps and the ideal one. EL = Integral Linearity Error: maximum deviation between any actual transition and the end point correlation line.

DocID14611 Rev 12

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|--------|-----------------------|--------|--------|

|        | Min         | Тур    | Max    | Тур                   | Min    | Max    |

| b      | 0.350       | 0.400  | 0.450  | 0.0138                | 0.0157 | 0.0177 |

| D      | 9.900       | 10.000 | 10.100 | 0.3898                | 0.3937 | 0.3976 |

| D1     | -           | 8.800  | -      | -                     | 0.3465 | -      |

| E      | 9.900       | 10.000 | 10.100 | 0.3898                | 0.3937 | 0.3976 |

| E1     | -           | 8.800  | -      | -                     | 0.3465 | -      |

| е      | -           | 0.800  | -      | -                     | 0.0315 | -      |

| F      | -           | 0.600  | -      | -                     | 0.0236 | -      |

| ddd    | -           | -      | 0.100  | -                     | -      | 0.0039 |

| eee    | -           | -      | 0.150  | -                     | -      | 0.0059 |

| fff    | -           | -      | 0.080  | -                     | -      | 0.0031 |

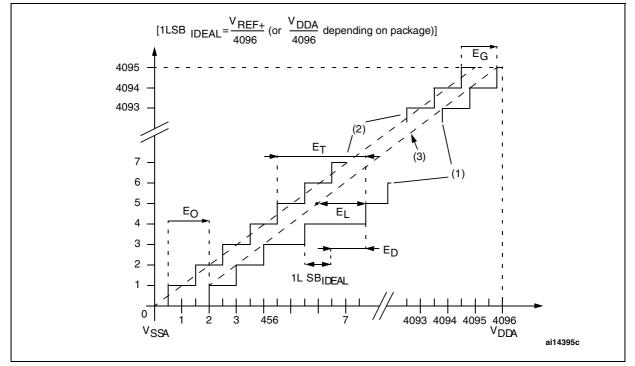

# Table 65. LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm,0.8 mm pitch, package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. STATSChipPAC package dimensions.

#### Table 66. LFBGA144 recommended PCB design rules (0.8 mm pitch BGA)

| Dimension | Recommended values |  |

|-----------|--------------------|--|

| Pitch     | 0.8 mm             |  |

| Dpad      | 0.400 mm           |  |

| UBM       | 0.350 mm           |  |

DocID14611 Rev 12

# 8 Revision history

| Date        | Revision | Changes                                                                                                                                                        |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 07-Apr-2008 | 1        | Initial release.                                                                                                                                               |

|             |          | -                                                                                                                                                              |

|             |          | Tolerance values corrected in <i>Table 74: LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm, 0.8 mm pitch, package data on page 139.</i> |

#### Table 76.Document revision history