Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT          |

| Number of I/O              | 112                                                                   |

| Program Memory Size        | 256KB (256K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 48K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 21x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 144-LFBGA                                                             |

| Supplier Device Package    | 144-LFBGA (10x10)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f103zch6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 8 | Revi | sion his | tory                                    |

|---|------|----------|-----------------------------------------|

| 7 | Part | number   | ing                                     |

|   |      | 6.7.2    | Selecting the product temperature range |

|   |      | 6.7.1    | Reference document                      |

|   | 6.7  | Therma   | al characteristics                      |

|   | 6.6  | LQFP6    | 4 package information 130               |

|   | 6.5  | LQFP1    | 00 package information                  |

|   | 6.4  | LQFP1    | 44 package information                  |

|   | 6.3  | WLCS     | P64 package information 121             |

|   | 6.2  | LFBGA    | 100 package information 118             |

|   | 6.1  | LFBGA    | 144 package information 115             |

| 6 | Pack | age info | ormation                                |

|   |      | 5.3.21   | Temperature sensor characteristics      |

|   |      | 5.3.20   | DAC electrical specifications           |

# 2.3.14 Low-power modes

The STM32F103xC, STM32F103xD and STM32F103xE performance line supports three low-power modes to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

• Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

• Stop mode

Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.

The device can be woken up from Stop mode by any of the EXTI line. The EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm or the USB wakeup.

• Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.8 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, SRAM and register contents are lost except for registers in the Backup domain and Standby circuitry.

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped by entering Stop or Standby mode.

# 2.3.15 DMA

The flexible 12-channel general-purpose DMAs (7 channels for DMA1 and 5 channels for DMA2) are able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The two DMA controllers support circular buffer management, removing the need for user code intervention when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with support for software trigger on each channel. Configuration is made by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: SPI, I<sup>2</sup>C, USART, general-purpose, basic and advanced-control timers TIMx, DAC, I<sup>2</sup>S, SDIO and ADC.

#### 2.3.16 RTC (real-time clock) and backup registers

The RTC and the backup registers are supplied through a switch that takes power either on  $V_{DD}$  supply when present or through the  $V_{BAT}$  pin. The backup registers are forty-two 16-bit registers used to store 84 bytes of user application data when  $V_{DD}$  power is not present. They are not reset by a system or power reset, and they are not reset when the device wakes up from the Standby mode.

The real-time clock provides a set of continuously running counters which can be used with suitable software to provide a clock calendar function, and provides an alarm interrupt and a

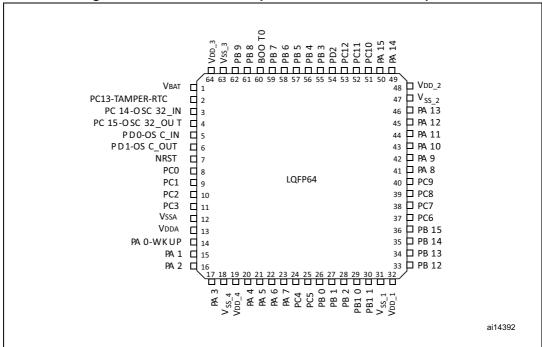

Figure 7. STM32F103xC/D/E performance line LQFP64 pinout

1. The above figure shows the package top view.

# 5 Electrical characteristics

# 5.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

#### 5.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

#### 5.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 3.3$  V (for the 2 V  $\leq V_{DD} \leq 3.6$  V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\Sigma$ ).

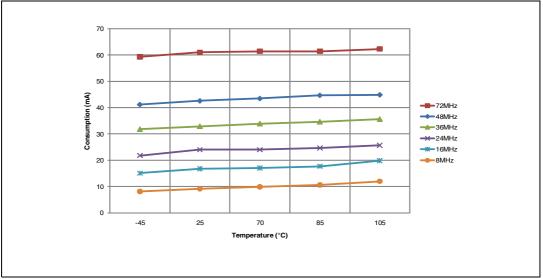

#### 5.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

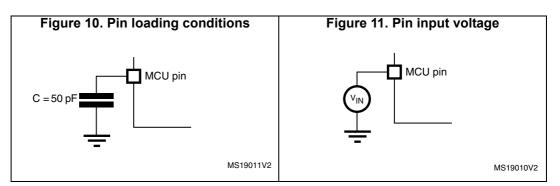

#### 5.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 10*.

#### 5.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 11*.

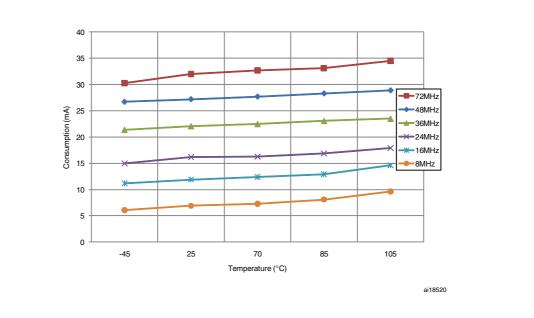

Figure 14. Typical current consumption in Run mode versus frequency (at 3.6 V) - code with data processing running from RAM, peripherals enabled

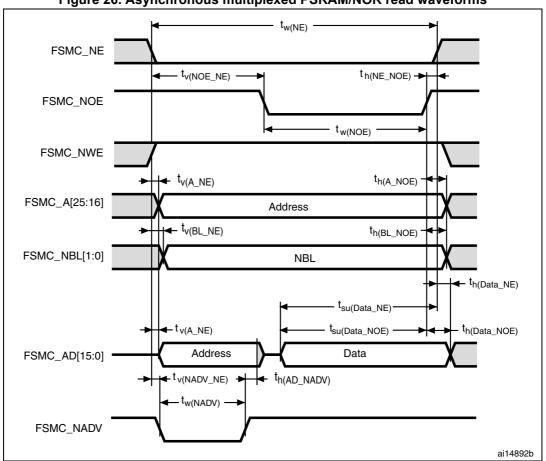

Figure 26. Asynchronous multiplexed PSRAM/NOR read waveforms

| Table 33. Asynchronous multiplexed PSRAM/NOR read timings <sup>(1)(2</sup> |

|----------------------------------------------------------------------------|

|----------------------------------------------------------------------------|

| Symbol                    | Parameter                                                 | Min                      | Мах                      | Unit |

|---------------------------|-----------------------------------------------------------|--------------------------|--------------------------|------|

| t <sub>w(NE)</sub>        | FSMC_NE low time                                          | 7t <sub>HCLK</sub> – 2   | 7t <sub>HCLK</sub> + 2   | ns   |

| t <sub>v(NOE_NE)</sub>    | FSMC_NEx low to FSMC_NOE low                              | 3t <sub>HCLK</sub> – 0.5 | 3t <sub>HCLK</sub> + 1.5 | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low time                                         | 4t <sub>HCLK</sub> – 1   | 4t <sub>HCLK</sub> + 2   | ns   |

| t <sub>h(NE_NOE)</sub>    | FSMC_NOE high to FSMC_NE high hold time                   | –1                       | -                        | ns   |

| t <sub>v(A_NE)</sub>      | FSMC_NEx low to FSMC_A valid                              | -                        | 0                        | ns   |

| t <sub>v(NADV_NE)</sub>   | FSMC_NEx low to FSMC_NADV low                             | 3                        | 5                        | ns   |

| t <sub>w(NADV)</sub>      | FSMC_NADV low time                                        | t <sub>HCLK</sub> –1.5   | t <sub>HCLK</sub> + 1.5  | ns   |

| t <sub>h(AD_NADV)</sub>   | FSMC_AD (address) valid hold time after<br>FSMC_NADV high | t <sub>HCLK</sub>        | -                        | ns   |

| t <sub>h(A_NOE)</sub>     | Address hold time after FSMC_NOE high                     | t <sub>HCLK</sub> -2     | -                        | ns   |

| t <sub>h(BL_NOE)</sub>    | FSMC_BL hold time after FSMC_NOE high                     | 0                        | -                        | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid                             | -                        | 0                        | ns   |

| t <sub>su(Data_NE)</sub>  | Data to FSMC_NEx high setup time                          | 2t <sub>HCLK</sub> + 24  | -                        | ns   |

| t <sub>su(Data_NOE)</sub> | Data to FSMC_NOE high setup time                          | 2t <sub>HCLK</sub> + 25  | -                        | ns   |

|                           | -                                                         |                         | •                       |      |

|---------------------------|-----------------------------------------------------------|-------------------------|-------------------------|------|

| Symbol                    | Parameter                                                 | Min                     | Мах                     | Unit |

| t <sub>h(AD_NADV)</sub>   | FSMC_AD (address) valid hold time after<br>FSMC_NADV high | t <sub>HCLK</sub> – 3   | -                       | ns   |

| t <sub>h(A_NWE)</sub>     | Address hold time after FSMC_NWE high                     | 4t <sub>HCLK</sub>      | -                       | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid                             | -                       | 1.6                     | ns   |

| t <sub>h(BL_NWE)</sub>    | FSMC_BL hold time after FSMC_NWE high                     | t <sub>HCLK</sub> – 1.5 | -                       | ns   |

| t <sub>v(Data_NADV)</sub> | FSMC_NADV high to Data valid                              | -                       | t <sub>HCLK</sub> + 1.5 | ns   |

| t <sub>h(Data_NWE)</sub>  | Data hold time after FSMC_NWE high                        | t <sub>HCLK</sub> – 5   | -                       | ns   |

Table 34. Asynchronous multiplexed PSRAM/NOR write timings<sup>(1)(2)</sup>

1. C<sub>L</sub> = 15 pF.

2. BGuaranteed by characterization results.

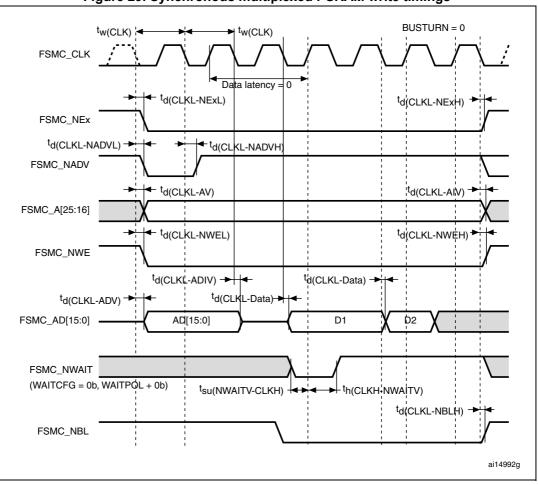

Figure 29. Synchronous multiplexed PSRAM write timings

| Symbol | Parameter             | Conditions                            | Class      |  |  |  |

|--------|-----------------------|---------------------------------------|------------|--|--|--|

| LU     | Static latch-up class | $T_A = +105$ °C conforming to JESD78A | II level A |  |  |  |

#### Table 44. Electrical sensitivities

# 5.3.13 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (>5 LSB TUE), out of spec current injection on adjacent pins or other functional failure (for example reset, oscillator frequency deviation).

The test results are given in Table 45

|                  |                                                            | Functional s       |                    |      |

|------------------|------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                | Negative injection | Positive injection | Unit |

|                  | Injected current on OSC_IN32,<br>OSC_OUT32, PA4, PA5, PC13 | -0                 | +0                 |      |

| I <sub>INJ</sub> | Injected current on all FT pins                            | -5                 | +0                 | mA   |

|                  | Injected current on any other pin                          | -5                 | +5                 |      |

#### Table 45. I/O current injection susceptibility

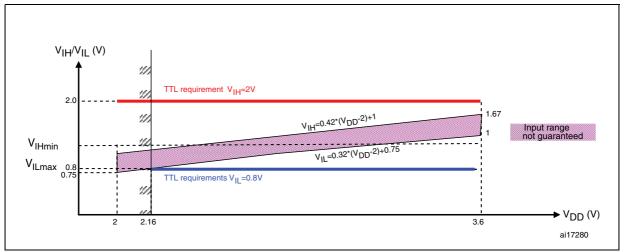

Figure 45. 5 V tolerant I/O input characteristics - TTL port

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to ±8 mA, and sink or source up to ± 20 mA (with a relaxed  $V_{OL}/V_{OH}$ ) except PC13, PC14 and PC15 which can sink or source up to ±3 mA. When using the GPIOs PC13 to PC15 in output mode, the speed should not exceed 2 MHz with a maximum load of 30 pF.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 5.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating I<sub>VDD</sub> (see *Table 8*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating I<sub>VSS</sub> (see *Table 8*).

#### **Output voltage levels**

Unless otherwise specified, the parameters given in *Table 47* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 10*. All I/Os are CMOS and TTL compliant.

| Symbol                         | Parameter                                                                     | Conditions                                                | Min                 | Max | Unit |  |

|--------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------|---------------------|-----|------|--|

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | TTL port <sup>(3)</sup><br>I <sub>IO</sub> = +8 mA        | -                   | 0.4 | V    |  |

| V <sub>OH</sub> <sup>(2)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at same time | $2.7 V < V_{DD} < 3.6 V$                                  | V <sub>DD</sub> 0.4 | -   | v    |  |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | CMOS port <sup>(3)</sup>                                  | -                   | 0.4 | V    |  |

| V <sub>OH</sub> <sup>(2)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at same time | I <sub>IO</sub> =+ 8mA<br>2.7 V < V <sub>DD</sub> < 3.6 V | 2.4                 | -   | V    |  |

| Table | 47  | Output | voltano | chara  | cteristics |

|-------|-----|--------|---------|--------|------------|

| lable | 41. | υαιραι | voitage | Cilara |            |

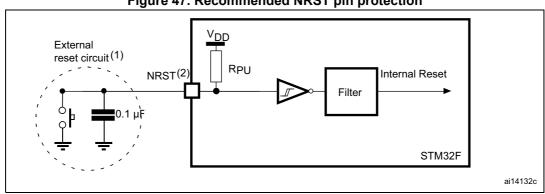

Figure 47. Recommended NRST pin protection

- 1. The reset network protects the device against parasitic resets.

- The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 49. Otherwise the reset will not be taken into account by the device.

#### 5.3.16 TIM timer characteristics

The parameters given in Table 50 are guaranteed by design.

Refer to *Section 5.3.14: I/O port characteristics* for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                       | Conditions                    | Min    | Max                     | Unit                 |

|------------------------|---------------------------------|-------------------------------|--------|-------------------------|----------------------|

| t (THO                 | Timer resolution time           | -                             | 1      | -                       | t <sub>TIMxCLK</sub> |

| t <sub>res(TIM)</sub>  |                                 | f <sub>TIMxCLK</sub> = 72 MHz | 13.9   | -                       | ns                   |

| f                      | Timer external clock            | -                             | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |

|                        | frequency on CH1 to CH4         | f <sub>TIMxCLK</sub> = 72 MHz | 0      | 36                      | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution                | -                             | -      | 16                      | bit                  |

|                        | 16-bit counter clock period     | -                             | 1      | 65536                   | t <sub>TIMxCLK</sub> |

| <sup>t</sup> COUNTER   | when internal clock is selected | f <sub>TIMxCLK</sub> = 72 MHz | 0.0139 | 910                     | μs                   |

| 4                      | Maximum possible count          | -                             | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |

| <sup>t</sup> MAX_COUNT |                                 | f <sub>TIMxCLK</sub> = 72 MHz | -      | 59.6                    | s                    |

Table 50. TIMx<sup>(1)</sup> characteristics

1. TIMx is used as a general term to refer to the TIM1, TIM2, TIM3 and TIM4 timers.

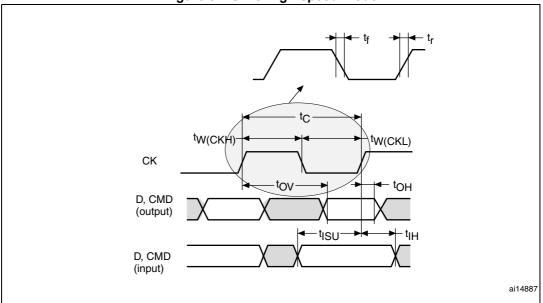

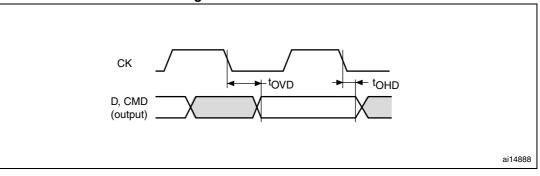

#### SD/SDIO MMC card host interface (SDIO) characteristics

Unless otherwise specified, the parameters given in *Table 55* are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 10*.

Refer to Section 5.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (D[7:0], CMD, CK).

Figure 54. SDIO high-speed mode

Figure 55. SD default mode

Table 55. SD / MMC characteristics

| Symbol          | Parameter                                 | Conditions              | Min | Мах | Unit |

|-----------------|-------------------------------------------|-------------------------|-----|-----|------|

| f <sub>PP</sub> | Clock frequency in data transfer mode     | $C_L \le 30 \text{ pF}$ | 0   | 48  | MHz  |

| tW(CKL)         | Clock low time, f <sub>PP</sub> = 16 MHz  | $C_L \le 30 \text{ pF}$ | 32  | -   |      |

| tW(CKH)         | Clock high time, f <sub>PP</sub> = 16 MHz | $C_L \le 30 \text{ pF}$ | 30  | -   | 200  |

| t <sub>r</sub>  | Clock rise time                           | $C_L \le 30 \text{ pF}$ | -   | 4   | ns   |

| t <sub>f</sub>  | Clock fall time                           | $C_L \le 30 \text{ pF}$ | -   | 5   |      |

DocID14611 Rev 12

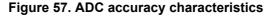

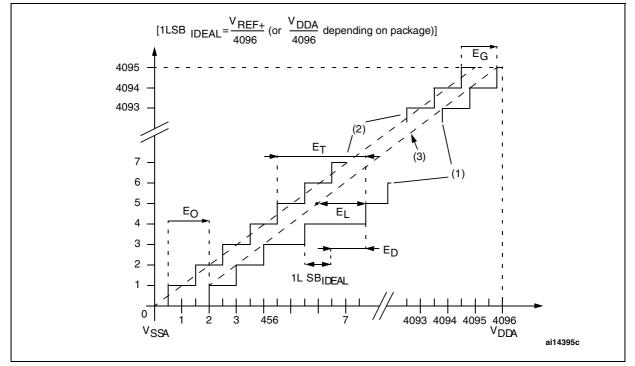

| Symbol | Parameter                    | Test conditions                                                                                                          | Тур  | Max <sup>(4)</sup> | Unit |

|--------|------------------------------|--------------------------------------------------------------------------------------------------------------------------|------|--------------------|------|

| ET     | Total unadjusted error       | 6 - 50 MUL                                                                                                               | ±2   | ±5                 |      |

| EO     | Offset error                 | f <sub>PCLK2</sub> = 56 MHz,<br>f <sub>ADC</sub> = 14 MHz, R <sub>AIN</sub> < 10 kΩ<br>V <sub>DDA</sub> = 2.4 V to 3.6 V | ±1.5 | ±2.5               |      |

| EG     | Gain error                   |                                                                                                                          | ±1.5 | ±3                 | LSB  |

| ED     | Differential linearity error | Measurements made after<br>ADC calibration                                                                               | ±1   | ±2                 |      |

| EL     | Integral linearity error     |                                                                                                                          | ±1.5 | ±3                 |      |

Table 62. ADC accuracy<sup>(1) (2)(3)</sup>

1. ADC DC accuracy values are measured after internal calibration.

2. Better performance could be achieved in restricted  $V_{DD}$ , frequency,  $V_{REF}$  and temperature ranges.

ADC Accuracy vs. Negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current.

Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 5.3.14 does not affect the ADC accuracy.

4. Guaranteed by characterization results.

- 1. Example of an actual transfer curve.

- 2. Ideal transfer curve.

- 3. End point correlation line.

- 4. ET = Total Unadjusted Error: maximum deviation between the actual and the ideal transfer curves. EO = Offset Error: deviation between the first actual transition and the first ideal one. EG = Gain Error: deviation between the last ideal transition and the last actual one. ED = Differential Linearity Error: maximum deviation between actual steps and the ideal one. EL = Integral Linearity Error: maximum deviation between any actual transition and the end point correlation line.

DocID14611 Rev 12

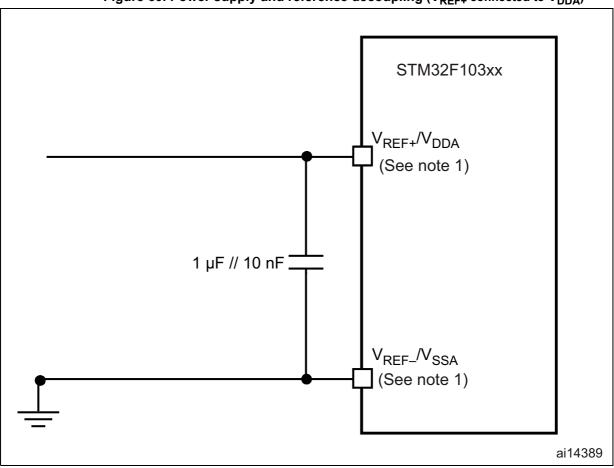

Figure 60. Power supply and reference decoupling (V<sub>REF+</sub> connected to V<sub>DDA</sub>)

1.  $V_{REF+}$  and  $V_{REF-}$  inputs are available only on 100-pin packages.

# 5.3.21 Temperature sensor characteristics

| Symbol                                | Parameter                                      | Min  | Тур  | Мах  | Unit  |

|---------------------------------------|------------------------------------------------|------|------|------|-------|

| ΤL                                    | $V_{\text{SENSE}}$ linearity with temperature  | -    | ±1   | ±2   | °C    |

| Avg_Slope                             | Average slope                                  | 4.0  | 4.3  | 4.6  | mV/°C |

| V <sub>25</sub>                       | Voltage at 25 °C                               | 1.34 | 1.43 | 1.52 | V     |

| t <sub>START</sub> <sup>(1)</sup>     | Startup time                                   | 4    | -    | 10   | μs    |

| T <sub>S_temp</sub> <sup>(2)(1)</sup> | ADC sampling time when reading the temperature | -    | -    | 17.1 | μs    |

Table 64. TS characteristics

1. Guaranteed by design.

2. Shortest sampling time can be determined in the application by multiple iterations.

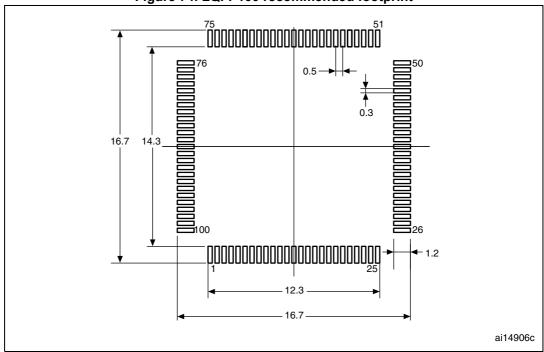

| Symbol - | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|----------|-------------|-------|-------|-----------------------|--------|--------|

|          | Min         | Тур   | Мах   | Min                   | Тур    | Max    |

| е        | -           | 0.500 | -     | -                     | 0.0197 | -      |

| L        | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1       | -           | 1.000 | -     | -                     | 0.0394 | -      |

| k        | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |

| CCC      | -           | -     | 0.08  | -                     | -      | 0.0031 |

# Table 72. LQPF100 – 14 x 14 mm 100-pin low-profile quad flat package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

# Figure 74. LQFP100 recommended footprint

1. Dimensions are in millimeters.

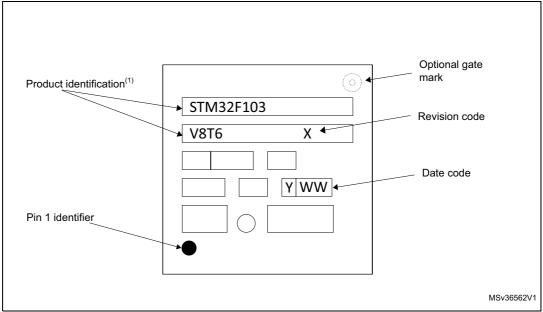

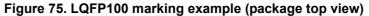

#### Device marking for LQFP100 package

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# 6.7 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 10: General operating conditions on page 44*.

The maximum chip-junction temperature,  $T_J$  max, in degrees Celsius, may be calculated using the following equation:

$T_J \max = T_A \max + (P_D \max x \Theta_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in °C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

$\mathsf{P}_{\mathsf{I}\!/\!\mathsf{O}}$  max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V<sub>OL</sub> / I<sub>OL</sub> and V<sub>OH</sub> / I<sub>OH</sub> of the I/Os at low and high level in the application.

| Symbol | Parameter                                                                   | Value | Unit |

|--------|-----------------------------------------------------------------------------|-------|------|

| ΘյΑ    | Thermal resistance junction-ambient<br>LFBGA144 - 10 × 10 mm / 0.8 mm pitch | 40    |      |

|        | Thermal resistance junction-ambient<br>LQFP144 - 20 × 20 mm / 0.5 mm pitch  | 30    |      |

|        | Thermal resistance junction-ambient<br>LFBGA100 - 10 × 10 mm / 0.8 mm pitch | 40    | °C/W |

|        | Thermal resistance junction-ambient<br>LQFP100 - 14 × 14 mm / 0.5 mm pitch  | 46    | C/W  |

|        | Thermal resistance junction-ambient<br>LQFP64 - 10 × 10 mm / 0.5 mm pitch   | 45    |      |

|        | Thermal resistance junction-ambient<br>WLCSP64                              | 50    |      |

#### 6.7.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org

#### 6.7.2 Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the ordering information scheme shown in *Table 75: Ordering information scheme*.

Each temperature range suffix corresponds to a specific guaranteed ambient temperature at maximum dissipation and, to a specific maximum junction temperature.

As applications do not commonly use the STM32F103xC, STM32F103xD and STM32F103xE at maximum dissipation, it is useful to calculate the exact power consumption and junction temperature to determine which temperature range will be best suited to the application.

The following examples show how to calculate the temperature range needed for a given application.

#### Example 1: High-performance application

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax} = 82$  °C (measured according to JESD51-2), I<sub>DDmax</sub> = 50 mA, V<sub>DD</sub> = 3.5 V, maximum 20 I/Os used at the same time in output at low level with I<sub>OL</sub> = 8 mA, V<sub>OL</sub>= 0.4 V and maximum 8 I/Os used at the same time in output at low level with I<sub>OL</sub> = 20 mA, V<sub>OL</sub>= 1.3 V

P<sub>INTmax</sub> = 50 mA × 3.5 V= 175 mW

P<sub>IOmax = 20</sub> × 8 mA × 0.4 V + 8 × 20 mA × 1.3 V = 272 mW

This gives:  $P_{INTmax}$  = 175 mW and  $P_{IOmax}$  = 272 mW:

P<sub>Dmax =</sub> 175 <sub>+</sub> 272 = 447 mW

Thus: P<sub>Dmax</sub> = 447 mW

Using the values obtained in *Table 74* T<sub>Jmax</sub> is calculated as follows:

- For LQFP100, 46 °C/W

- T<sub>Jmax</sub> = 82 °C + (46 °C/W × 447 mW) = 82 °C + 20.6 °C = 102.6 °C

This is within the range of the suffix 6 version parts ( $-40 < T_J < 105 \text{ °C}$ ).

In this case, parts must be ordered at least with the temperature range suffix 6 (see *Table 75: Ordering information scheme*).

#### **Example 2: High-temperature application**

Using the same rules, it is possible to address applications that run at high ambient temperatures with a low dissipation, as long as junction temperature  $T_J$  remains within the specified range.

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax} = 115 \text{ °C}$  (measured according to JESD51-2),  $I_{DDmax} = 20 \text{ mA}, V_{DD} = 3.5 \text{ V}, \text{ maximum } 20 \text{ I/Os used at the same time in output at low level with } I_{OL} = 8 \text{ mA}, V_{OL} = 0.4 \text{ V}$   $P_{INTmax} = 20 \text{ mA} \times 3.5 \text{ V} = 70 \text{ mW}$   $P_{IOmax} = _{20} \times 8 \text{ mA} \times 0.4 \text{ V} = 64 \text{ mW}$ This gives:  $P_{INTmax} = 70 \text{ mW}$  and  $P_{IOmax} = 64 \text{ mW}$ :  $P_{Dmax} = 70 + 64 = 134 \text{ mW}$

Thus: P<sub>Dmax</sub> = 134 mW

DocID14611 Rev 12

| Iable /6.Document revision history           Data         Revision |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|--------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Date                                                               | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                                                                    |          | Updated package choice for 103Rx in <i>Table 2</i><br>Updated footnotes below <i>Table 7: Voltage characteristics on page 43</i><br>and <i>Table 8: Current characteristics on page 43</i>                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                                                                    |          | Updated tw min in Table 21: High-speed external user clock<br>characteristics on page 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|                                                                    |          | Updated startup time in <i>Table 24: LSE oscillator characteristics (fLSE</i> = 32.768 kHz) on page 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                                                                    |          | Updated note 2 in Table 51: I2C characteristics on page 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                                                                    | 8        | Updated Figure 48: I2C bus AC waveforms and measurement circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                                                                    |          | Updated Figure 47: Recommended NRST pin protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                                                                    |          | Updated Section 5.3.14: I/O port characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 19-Apr-2011                                                        |          | Updated Table 35: Synchronous multiplexed NOR/PSRAM read timings on page 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                                                                    |          | Updated FSMC Figure 26 thru Figure 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|                                                                    |          | Updated Figure 41.: NAND controller waveforms for common memory write access and Figure 48.: I2C bus AC waveforms and measurement circuit                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|                                                                    |          | Added Section 5.3.13: I/O current injection characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                                                                    |          | Updated Figure 67 and added Table 69: WLCSP, 64-ball 4.466 × 4.395 mm, 0.500 mm pitch, wafer-level chip-scale package mechanical data on page 121                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                                                                    |          | LQFP64 package mechanical data updated: see <i>Figure 73.:</i> LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package outline and Table 73: LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package mechanical data on page 130.                                                                                                                                                                                                                                                                                                                                         |  |

|                                                                    | 9        | Added Note 7 in Table 5: High-density STM32F103xC/D/E pin definitions on page 31.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 30-Sept-2014                                                       |          | Updated Note 10 in Table 5: High-density STM32F103xC/D/E pin definitions on page 31.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                                                                    |          | Modified Note 2 in Table 62: ADC accuracy on page 109<br>Modified Note 3 in Table 62: ADC accuracy on page 109<br>Modified notes in Table 51: I2C characteristics on page 97<br>Updated Figure 51: SPI timing diagram - master mode(1) on page 101                                                                                                                                                                                                                                                                                                                          |  |

| 23-Feb-2015                                                        | 10       | Updated Figure 66.: BGA pad footprint, Figure 70: LQFP144 - 144-pin,<br>20 x 20 mm low-profile quad flat package outline, Figure 73.: LQFP100<br>- 14 x 14 mm 100 pin low-profile quad flat package outline, Figure 74.:<br>LQFP100 recommended footprint, Figure 76.: LQFP64 - 10 x 10 mm<br>64 pin low-profile quad flat package outline, Figure 77.: LQFP64 - 64-<br>pin, 10 x 10 mm low-profile quad flat recommended footprint<br>Added Figure 72.: LQFP144 marking example (package top view),<br>Figure 75.: LQFP100 marking example (package top view), Figure 78.: |  |

|                                                                    |          | LQFP64 marking example (package top view), Figure 78<br>LQFP64 marking example (package top view)<br>Updated Table 72: LQPF100 – 14 x 14 mm 100-pin low-profile quad flat<br>package mechanical data, Table 73: LQFP64 – 10 x 10 mm 64 pin low-<br>profile quad flat package mechanical data                                                                                                                                                                                                                                                                                |  |

#### Table 76.Document revision history