Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT          |

| Number of I/O              | 112                                                                   |

| Program Memory Size        | 512KB (512K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | - ·                                                                   |

| RAM Size                   | 64K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 21x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 144-LFBGA                                                             |

| Supplier Device Package    |                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f103zeh6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 | Intro | duction  |                                                                            |

|---|-------|----------|----------------------------------------------------------------------------|

| 2 | Dese  | cription |                                                                            |

|   | 2.1   | Device   | overview                                                                   |

|   | 2.2   | Full co  | mpatibility throughout the family                                          |

|   | 2.3   |          | ew                                                                         |

|   |       | 2.3.1    | ARM <sup>®</sup> Cortex <sup>®</sup> -M3 core with embedded Flash and SRAM |

|   |       | 2.3.2    | Embedded Flash memory15                                                    |

|   |       | 2.3.3    | CRC (cyclic redundancy check) calculation unit                             |

|   |       | 2.3.4    | Embedded SRAM                                                              |

|   |       | 2.3.5    | FSMC (flexible static memory controller)                                   |

|   |       | 2.3.6    | LCD parallel interface                                                     |

|   |       | 2.3.7    | Nested vectored interrupt controller (NVIC)                                |

|   |       | 2.3.8    | External interrupt/event controller (EXTI)                                 |

|   |       | 2.3.9    | Clocks and startup                                                         |

|   |       | 2.3.10   | Boot modes                                                                 |

|   |       | 2.3.11   | Power supply schemes17                                                     |

|   |       | 2.3.12   | Power supply supervisor                                                    |

|   |       | 2.3.13   | Voltage regulator                                                          |

|   |       | 2.3.14   | Low-power modes                                                            |

|   |       | 2.3.15   | DMA                                                                        |

|   |       | 2.3.16   | RTC (real-time clock) and backup registers                                 |

|   |       | 2.3.17   | Timers and watchdogs                                                       |

|   |       | 2.3.18   | I <sup>2</sup> C bus                                                       |

|   |       | 2.3.19   | Universal synchronous/asynchronous receiver transmitters (USARTs) 21       |

|   |       | 2.3.20   | Serial peripheral interface (SPI) 21                                       |

|   |       | 2.3.21   | Inter-integrated sound (I <sup>2</sup> S)21                                |

|   |       | 2.3.22   | SDIO                                                                       |

|   |       | 2.3.23   | Controller area network (CAN)                                              |

|   |       | 2.3.24   | Universal serial bus (USB)                                                 |

|   |       | 2.3.25   | GPIOs (general-purpose inputs/outputs)                                     |

|   |       | 2.3.26   | ADC (analog to digital converter) 22                                       |

|   |       | 2.3.27   | DAC (digital-to-analog converter)                                          |

|   |       | 2.3.28   | Temperature sensor                                                         |

DocID14611 Rev 12

# 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32F103xC, STM32F103xD and STM32F103xE high-density performance line microcontrollers. For more details on the whole STMicroelectronics STM32F103xC/D/E family, please refer to *Section 2.2: Full compatibility throughout the family*.

The high-density STM32F103xC/D/E datasheet should be read in conjunction with the STM32F10xxx reference manual.

For information on programming, erasing and protection of the internal Flash memory please refer to the *STM32F10xxx* Flash programming manual. The reference and Flash programming manuals are both available from the STMicroelectronics website *www.st.com*.

For information on the Cortex<sup>®</sup>-M3 core please refer to the Cortex<sup>®</sup>-M3 Technical Reference Manual, available from the *www.arm.com* website at the following address: *http://infocenter.arm.com*.

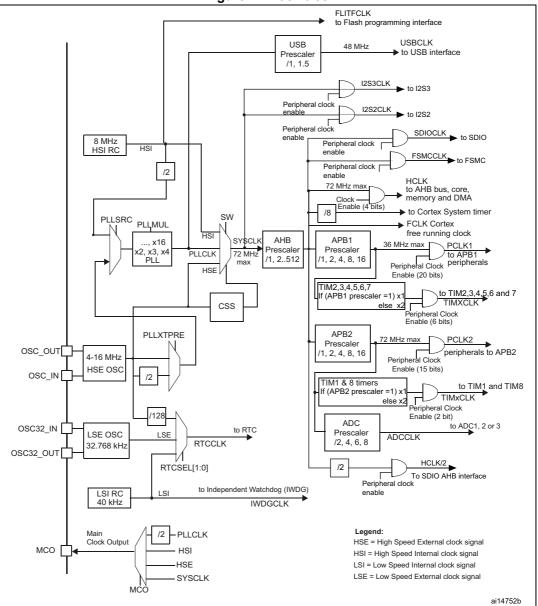

Figure 2. Clock tree

1. When the HSI is used as a PLL clock input, the maximum system clock frequency that can be achieved is 64 MHz.

2. For the USB function to be available, both HSE and PLL must be enabled, with the USBCLK at 48 MHz.

3. To have an ADC conversion time of 1 µs, APB2 must be at 14 MHz, 28 MHz or 56 MHz.

## 2.2 Full compatibility throughout the family

The STM32F103xC/D/E is a complete family whose members are fully pin-to-pin, software and feature compatible. In the reference manual, the STM32F103x4 and STM32F103x6 are identified as low-density devices, the STM32F103x8 and STM32F103xB are referred to as medium-density devices and the STM32F103xC, STM32F103xD and STM32F103xE are referred to as high-density devices.

Low-density and high-density devices are an extension of the STM32F103x8/B mediumdensity devices, they are specified in the STM32F103x4/6 and STM32F103xC/D/E datasheets, respectively. Low-density devices feature lower Flash memory and RAM capacities, less timers and peripherals. High-density devices have higher Flash memory and RAM capacities, and additional peripherals like SDIO, FSMC, I<sup>2</sup>S and DAC while remaining fully compatible with the other members of the family.

The STM32F103x4, STM32F103x6, STM32F103xC, STM32F103xD and STM32F103xE are a drop-in replacement for the STM32F103x8/B devices, allowing the user to try different memory densities and providing a greater degree of freedom during the development cycle.

Moreover, the STM32F103xx performance line family is fully compatible with all existing STM32F101xx access line and STM32F102xx USB access line devices.

|        | Low-dens                                                               | ity devices               | Medium-density devices                                     |                         | High-density devices                                                                                     |           |                 |  |  |

|--------|------------------------------------------------------------------------|---------------------------|------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------|-----------|-----------------|--|--|

| Pinout | 16 KB<br>Flash                                                         |                           |                                                            | 128 KB<br>Flash         | 256 KB 384 KB<br>Flash Flash                                                                             |           | 512 KB<br>Flash |  |  |

|        | 6 KB RAM 10 KB RAM 2                                                   |                           | B RAM 10 KB RAM 20 KB RAM                                  |                         | 48 RAM                                                                                                   | 64 KB RAM | 64 KB RAM       |  |  |

| 144    |                                                                        |                           |                                                            |                         | 5 × USARTs                                                                                               |           |                 |  |  |

| 100    | 3 × USARTs                                                             |                           |                                                            |                         | 4 × 16-bit timers, 2 × basic timers<br>3 × SPIs, 2 × I <sup>2</sup> Ss, 2 × I2Cs                         |           |                 |  |  |

| 64     | 2 × USARTs<br>2 × 16-bit timers<br>1 × SPI, 1 × I <sup>2</sup> C, USB, |                           | 3 × 16-bit tim<br>2 × SPIs, 2 ×<br>CAN, 1 × PW<br>2 × ADCs | l <sup>2</sup> Cs, USB, | USB, CAN, 2 × PWM timers<br>3 × ADCs, 2 × DACs, 1 × SDIO<br>FSMC (100- and 144-pin packages <sup>(</sup> |           |                 |  |  |

| 48     | CAN, 1 × P                                                             | CAN, $1 \times PWM$ timer |                                                            |                         |                                                                                                          |           |                 |  |  |

| 36     | 2 × ADCs                                                               |                           |                                                            |                         | 1                                                                                                        |           |                 |  |  |

Table 3. STM32F103xx family

For orderable part numbers that do not show the A internal code after the temperature range code (6 or 7), the reference datasheet for electrical characteristics is that of the STM32F103x8/B medium-density devices.

2. Ports F and G are not available in devices delivered in 100-pin packages.

## 2.3 Overview

# 2.3.1 ARM<sup>®</sup> Cortex<sup>®</sup>-M3 core with embedded Flash and SRAM

The ARM Cortex<sup>®</sup>-M3 processor is the latest generation of ARM processors for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM Cortex<sup>®</sup>-M3 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

With its embedded ARM core, STM32F103xC, STM32F103xD and STM32F103xE performance line family is compatible with all ARM tools and software.

*Figure 1* shows the general block diagram of the device family.

## 2.3.2 Embedded Flash memory

Up to 512 Kbytes of embedded Flash is available for storing programs and data.

### 2.3.3 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

### 2.3.4 Embedded SRAM

Up to 64 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states.

### 2.3.5 FSMC (flexible static memory controller)

The FSMC is embedded in the STM32F103xC, STM32F103xD and STM32F103xE performance line family. It has four Chip Select outputs supporting the following modes: PC Card/Compact Flash, SRAM, PSRAM, NOR and NAND.

Functionality overview:

- The three FSMC interrupt lines are ORed in order to be connected to the NVIC

- Write FIFO

- Code execution from external memory except for NAND Flash and PC Card

- The targeted frequency, f<sub>CLK</sub>, is HCLK/2, so external access is at 36 MHz when HCLK is at 72 MHz and external access is at 24 MHz when HCLK is at 48 MHz

### Advanced-control timers (TIM1 and TIM8)

The two advanced-control timers (TIM1 and TIM8) can each be seen as a three-phase PWM multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead-times. They can also be seen as a complete general-purpose timer. The 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge or center-aligned modes)

- One-pulse mode output

If configured as a standard 16-bit timer, it has the same features as the TIMx timer. If configured as the 16-bit PWM generator, it has full modulation capability (0-100%).

In debug mode, the advanced-control timer counter can be frozen and the PWM outputs disabled to turn off any power switch driven by these outputs.

Many features are shared with those of the general-purpose TIM timers which have the same architecture. The advanced-control timer can therefore work together with the TIM timers via the Timer Link feature for synchronization or event chaining.

### General-purpose timers (TIMx)

There are up to 4 synchronizable general-purpose timers (TIM2, TIM3, TIM4 and TIM5) embedded in the STM32F103xC, STM32F103xD and STM32F103xE performance line devices. These timers are based on a 16-bit auto-reload up/down counter, a 16-bit prescaler and feature 4 independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input captures / output compares / PWMs on the largest packages.

The general-purpose timers can work together with the advanced-control timer via the Timer Link feature for synchronization or event chaining. Their counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs. They all have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

### Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger generation. They can also be used as a generic 16-bit time base.

### Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

### Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from

## 2.3.28 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 2 V <  $V_{DDA}$  < 3.6 V. The temperature sensor is internally connected to the ADC1\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

## 2.3.29 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP Interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target. The JTAG TMS and TCK pins are shared respectively with SWDIO and SWCLK and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

## 2.3.30 Embedded Trace Macrocell™

The ARM<sup>®</sup> Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F10xxx through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or any other high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer running debugger software. TPA hardware is commercially available from common development tool vendors. It operates with third party debugger software tools.

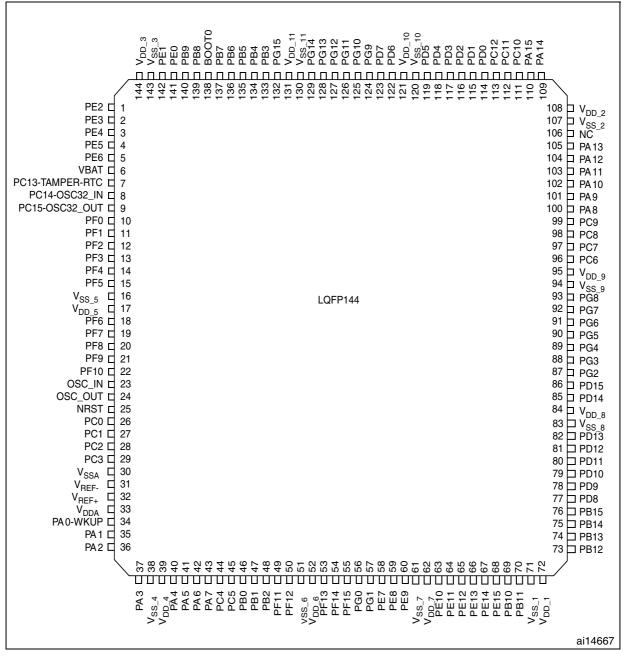

Figure 5. STM32F103xC/D/E performance line LQFP144 pinout

1. The above figure shows the package top view.

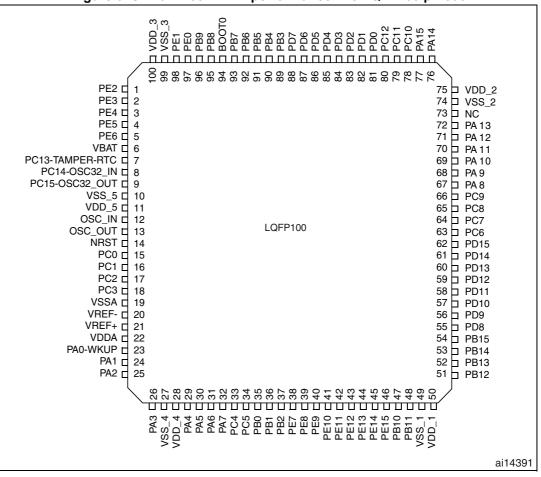

Figure 6. STM32F103xC/D/E performance line LQFP100 pinout

1. The above figure shows the package top view.

## 5.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 7: Voltage characteristics*, *Table 8: Current characteristics*, and *Table 9: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                            | Ratings                                                                            | Min                                                                         | Мах                   | Unit |

|-----------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>  | External main supply voltage (including $V_{DDA}$ and $V_{DD})^{(1)}$              | -0.3                                                                        | 4.0                   |      |

| V <sub>IN</sub> <sup>(2)</sup>    | Input voltage on five volt tolerant pin                                            | V <sub>SS</sub> –0.3                                                        | V <sub>DD</sub> + 4.0 | V    |

| VIN V                             | Input voltage on any other pin                                                     | V <sub>SS</sub> -0.3                                                        | 4.0                   |      |

| $ \Delta V_{DDx} $                | Variations between different $V_{DD}$ power pins                                   | -                                                                           | 50                    |      |

| V <sub>SSX</sub> –V <sub>SS</sub> | $ _{SX} - V_{SS} $ Variations between all the different ground pins <sup>(3)</sup> |                                                                             | 50                    | mV   |

| V <sub>ESD(HBM)</sub>             | Electrostatic discharge voltage (human body model)                                 | see Section 5.3.12:<br>Absolute maximum ratings<br>(electrical sensitivity) |                       | -    |

1. All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 8: Current characteristics* for the maximum allowed injected current values.

3. Include  $V_{REF-}$  pin.

#### Table 8. Current characteristics

| Symbol                               | Ratings                                                                                                   | Max.  | Unit |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------|-------|------|

| I <sub>VDD</sub>                     | I <sub>VDD</sub> Total current into V <sub>DD</sub> /V <sub>DDA</sub> power lines (source) <sup>(1)</sup> |       |      |

| I <sub>VSS</sub>                     | Total current out of V <sub>SS</sub> ground lines (sink) <sup>(1)</sup>                                   |       |      |

|                                      | Output current sunk by any I/O and control pin                                                            | 25    |      |

| Ι <sub>ΙΟ</sub>                      | Output current source by any I/Os and control pin                                                         | -25   | mA   |

| I <sub>INJ(PIN)</sub> <sup>(2)</sup> | Injected current on five volt tolerant pins <sup>(3)</sup>                                                | -5/+0 |      |

|                                      | Injected current on any other pin <sup>(4)</sup>                                                          | ± 5   |      |

| $\Sigma I_{INJ(PIN)}$                | Total injected current (sum of all I/O and control pins) <sup>(5)</sup>                                   | ± 25  |      |

1. All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2. Negative injection disturbs the analog performance of the device. See note 3 below Table 62 on page 109.

- Positive injection is not possible on these I/Os. A negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN</sub>) must never be exceeded. Refer to *Table 7: Voltage characteristics* for the maximum allowed input voltage values.

- A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 7: Voltage characteristics* for the maximum allowed input voltage values.

- 5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

## 5.3.2 Operating conditions at power-up / power-down

The parameters given in *Table 11* are derived from tests performed under the ambient temperature condition summarized in *Table 10*.

| Symbol | Parameter                      | Conditions | Min | Max | Unit  |

|--------|--------------------------------|------------|-----|-----|-------|

|        | V <sub>DD</sub> rise time rate | _          | 0   | 8   | us/V  |

| tvnn   | $V_{DD}$ fall time rate        | -          | 20  | 8   | μ5/ ν |

Table 11. Operating conditions at power-up / power-down

## 5.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 12* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 10*.

| Symbol                               | Parameter                                     | Conditions                  | Min                | Тур  | Max  | Unit |  |  |  |  |

|--------------------------------------|-----------------------------------------------|-----------------------------|--------------------|------|------|------|--|--|--|--|

|                                      |                                               | PLS[2:0]=000 (rising edge)  | 2.1                | 2.18 | 2.26 |      |  |  |  |  |

| V <sub>PVD</sub>                     |                                               | PLS[2:0]=000 (falling edge) | 2                  | 2.08 | 2.16 |      |  |  |  |  |

|                                      |                                               | PLS[2:0]=001 (rising edge)  | 2.19               | 2.28 | 2.37 |      |  |  |  |  |

|                                      |                                               | PLS[2:0]=001 (falling edge) | 2.09               | 2.18 | 2.27 |      |  |  |  |  |

|                                      |                                               | PLS[2:0]=010 (rising edge)  | 2.28               | 2.38 | 2.48 |      |  |  |  |  |

|                                      |                                               | PLS[2:0]=010 (falling edge) | 2.18               | 2.28 | 2.38 |      |  |  |  |  |

|                                      |                                               | PLS[2:0]=011 (rising edge)  | 2.38               | 2.48 | 2.58 |      |  |  |  |  |

|                                      | Programmable voltage detector level selection | PLS[2:0]=011 (falling edge) | 2.28               | 2.38 | 2.48 | v    |  |  |  |  |

|                                      |                                               | PLS[2:0]=100 (rising edge)  | 2.47               | 2.58 | 2.69 | v    |  |  |  |  |

|                                      |                                               | PLS[2:0]=100 (falling edge) | 2.37               | 2.48 | 2.59 |      |  |  |  |  |

|                                      |                                               | PLS[2:0]=101 (rising edge)  | 2.57               | 2.68 | 2.79 |      |  |  |  |  |

|                                      |                                               | PLS[2:0]=101 (falling edge) | 2.47               | 2.58 | 2.69 |      |  |  |  |  |

|                                      |                                               | PLS[2:0]=110 (rising edge)  | 2.66               | 2.78 | 2.9  |      |  |  |  |  |

|                                      |                                               | PLS[2:0]=110 (falling edge) | 2.56               | 2.68 | 2.8  |      |  |  |  |  |

|                                      |                                               | PLS[2:0]=111 (rising edge)  | 2.76               | 2.88 | 3    |      |  |  |  |  |

|                                      |                                               | PLS[2:0]=111 (falling edge) | 2.66               | 2.78 | 2.9  |      |  |  |  |  |

| V <sub>PVDhyst</sub> <sup>(2)</sup>  | PVD hysteresis                                | -                           | -                  | 100  | -    | mV   |  |  |  |  |

|                                      | Power on/power down                           | Falling edge                | 1.8 <sup>(1)</sup> | 1.88 | 1.96 | V    |  |  |  |  |

| V <sub>POR/PDR</sub>                 | reset threshold                               | Rising edge                 | 1.84               | 1.92 | 2.0  | V    |  |  |  |  |

| V <sub>PDRhyst</sub> <sup>(2)</sup>  | PDR hysteresis                                | -                           | -                  | 40   | -    | mV   |  |  |  |  |

| T <sub>RSTTEMPO</sub> <sup>(2)</sup> | Reset temporization                           | -                           | 1                  | 2.5  | 4.5  | ms   |  |  |  |  |

Table 12. Embedded reset and power control block characteristics

1. The product behavior is guaranteed by design down to the minimum  $V_{\text{POR/PDR}}$  value.

2. Guaranteed by design.

|                                                    |            |                                   |                   | Ту                                        | Unit |                          |

|----------------------------------------------------|------------|-----------------------------------|-------------------|-------------------------------------------|------|--------------------------|

| Symbol Parameter                                   |            | Conditions                        | f <sub>HCLK</sub> | All peripherals<br>enabled <sup>(2)</sup> |      | All peripherals disabled |

|                                                    |            |                                   | 72 MHz            | 29.5                                      | 6.4  |                          |

|                                                    |            | 48 MHz                            | 20                | 4.6                                       |      |                          |

|                                                    |            | 36 MHz                            | 15.1              | 3.6                                       |      |                          |

|                                                    |            |                                   | 24 MHz            | 10.4                                      | 2.6  |                          |

|                                                    |            |                                   | 16 MHz            | 7.2                                       | 2    |                          |

|                                                    |            | External clock <sup>(3)</sup>     | 8 MHz             | 3.9                                       | 1.3  |                          |

| Supply<br>I <sub>DD</sub> current in<br>Sleep mode |            |                                   | 4 MHz             | 2.6                                       | 1.2  |                          |

|                                                    |            |                                   | 2 MHz             | 1.85                                      | 1.15 |                          |

|                                                    |            |                                   | 1 MHz             | 1.5                                       | 1.1  |                          |

|                                                    |            |                                   | 500 kHz           | 1.3                                       | 1.05 |                          |

|                                                    |            |                                   | 125 kHz           | 1.2                                       | 1.05 | mA                       |

|                                                    | Sleep mode |                                   | 64 MHz            | 25.6                                      | 5.1  |                          |

|                                                    |            |                                   | 48 MHz            | 19.4                                      | 4    |                          |

|                                                    |            |                                   | 36 MHz            | 14.5                                      | 3    |                          |

|                                                    |            |                                   | 24 MHz            | 9.8                                       | 2    |                          |

|                                                    |            | Running on high speed internal RC | 16 MHz            | 6.6                                       | 1.4  |                          |

|                                                    |            | (HSI), AHB prescaler              | 8 MHz             | 3.3                                       | 0.7  |                          |

|                                                    |            | used to reduce the<br>frequency   | 4 MHz             | 2                                         | 0.6  |                          |

|                                                    |            | . ,                               | 2 MHz             | 1.25                                      | 0.55 |                          |

|                                                    |            |                                   | 1 MHz             | 0.9                                       | 0.5  |                          |

|                                                    |            |                                   | 500 kHz           | 0.7                                       | 0.45 |                          |

|                                                    |            |                                   | 125 kHz           | 0.6                                       | 0.45 |                          |

Table 19. Typical current consumption in Sleep mode, code running from Flash or RAM

1. Typical values are measures at  $T_A$  = 25 °C,  $V_{DD}$  = 3.3 V.

2. Add an additional power consumption of 0.8 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

3. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

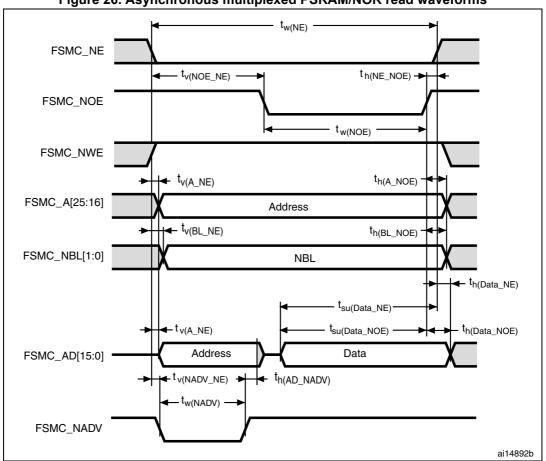

Figure 26. Asynchronous multiplexed PSRAM/NOR read waveforms

| Table 33. Asynchronous multiplexed PSRAM/NOR read timings <sup>(1)(2</sup> |

|----------------------------------------------------------------------------|

|----------------------------------------------------------------------------|

| Symbol                    | Parameter                                                 | Min                      | Мах                      | Unit |

|---------------------------|-----------------------------------------------------------|--------------------------|--------------------------|------|

| t <sub>w(NE)</sub>        | FSMC_NE low time                                          | 7t <sub>HCLK</sub> – 2   | 7t <sub>HCLK</sub> + 2   | ns   |

| t <sub>v(NOE_NE)</sub>    | FSMC_NEx low to FSMC_NOE low                              | 3t <sub>HCLK</sub> – 0.5 | 3t <sub>HCLK</sub> + 1.5 | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low time                                         | 4t <sub>HCLK</sub> – 1   | 4t <sub>HCLK</sub> + 2   | ns   |

| t <sub>h(NE_NOE)</sub>    | FSMC_NOE high to FSMC_NE high hold time                   | –1                       | -                        | ns   |

| t <sub>v(A_NE)</sub>      | FSMC_NEx low to FSMC_A valid                              | -                        | 0                        | ns   |

| t <sub>v(NADV_NE)</sub>   | FSMC_NEx low to FSMC_NADV low                             | 3                        | 5                        | ns   |

| t <sub>w(NADV)</sub>      | FSMC_NADV low time                                        | t <sub>HCLK</sub> –1.5   | t <sub>HCLK</sub> + 1.5  | ns   |

| t <sub>h(AD_NADV)</sub>   | FSMC_AD (address) valid hold time after<br>FSMC_NADV high | t <sub>HCLK</sub>        | -                        | ns   |

| t <sub>h(A_NOE)</sub>     | Address hold time after FSMC_NOE high                     | t <sub>HCLK</sub> -2     | -                        | ns   |

| t <sub>h(BL_NOE)</sub>    | FSMC_BL hold time after FSMC_NOE high                     | 0                        | -                        | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid                             | -                        | 0                        | ns   |

| t <sub>su(Data_NE)</sub>  | Data to FSMC_NEx high setup time                          | 2t <sub>HCLK</sub> + 24  | -                        | ns   |

| t <sub>su(Data_NOE)</sub> | Data to FSMC_NOE high setup time                          | 2t <sub>HCLK</sub> + 25  | -                        | ns   |

## 5.3.14 I/O port characteristics

## General input/output characteristics

Unless otherwise specified, the parameters given in *Table 46* are derived from tests performed under the conditions summarized in *Table 10*. All I/Os are CMOS and TTL compliant.

| Symbol           | Parameter                                                           | Conditions                                                         | Min                                  | Тур | Мах                                | Unit |

|------------------|---------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------|-----|------------------------------------|------|

| V <sub>IL</sub>  | Standard IO input low<br>level voltage                              |                                                                    | -0.3                                 | -   | 0.28*(V <sub>DD</sub> -2 V)+0.8 V  | V    |

|                  | IO FT <sup>(1)</sup> input low level voltage                        | -                                                                  | -0.3                                 | -   | 0.32*(V <sub>DD</sub> -2 V)+0.75 V | V    |

|                  | Standard IO input high<br>level voltage                             | -                                                                  | 0.41*(V <sub>DD</sub> -2 V)+1.3<br>V | -   | V <sub>DD</sub> +0.3               | V    |

| V <sub>IH</sub>  | IO FT <sup>(1)</sup> input high level                               | V <sub>DD</sub> > 2 V                                              | 0.42*()/ 2.)/)+1.)/                  |     | 5.5                                | v    |

|                  | voltage                                                             | V <sub>DD</sub> ≤2 V                                               | 0.42*(V <sub>DD</sub> -2 V)+1 V      | -   | 5.2                                | v    |

| V <sub>hys</sub> | Standard IO Schmitt<br>trigger voltage<br>hysteresis <sup>(2)</sup> | -                                                                  | 200                                  | -   | -                                  | mV   |

| liys             | IO FT Schmitt trigger voltage hysteresis <sup>(2)</sup>             |                                                                    | 5% V <sub>DD</sub> <sup>(3)</sup>    | -   | -                                  | mV   |

| 1                | Input leakage current <sup>(4)</sup>                                | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>Standard I/Os | -                                    | -   | ±1                                 |      |

| l <sub>ikg</sub> |                                                                     | V <sub>IN</sub> = 5 V,<br>I/O FT                                   | -                                    | -   | 3                                  | μA   |

| R <sub>PU</sub>  | Weak pull-up equivalent resistor <sup>(5)</sup>                     | $V_{IN} = V_{SS}$                                                  | 30                                   | 40  | 50                                 | kΩ   |

| R <sub>PD</sub>  | Weak pull-down<br>equivalent resistor <sup>(5)</sup>                | $V_{IN} = V_{DD}$                                                  | 30                                   | 40  | 50                                 | kΩ   |

| C <sub>IO</sub>  | I/O pin capacitance                                                 | -                                                                  | -                                    | 5   | -                                  | pF   |

1. FT = Five-volt tolerant. In order to sustain a voltage higher than V<sub>DD</sub>+0.3 the internal pull-up/pull-down resistors must be disabled.

2. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by characterization results.

3. With a minimum of 100 mV.

4. Leakage could be higher than max. if negative current is injected on adjacent pins.

Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This MOS/NMOS contribution to the series resistance is minimum (~10% order).

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 42* and *Figure 43* for standard I/Os, and in *Figure 44* and *Figure 45* for 5 V tolerant I/Os.

| Symbol                            | Parameter                                                                     | Conditions                                                  | Min                  | Мах | Unit |

|-----------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------|-----|------|

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | I <sub>IO</sub> = +20 mA                                    | -                    | 1.3 | V    |

| V <sub>OH</sub> <sup>(2)(4)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at same time | I <sub>IO</sub> = +20 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V | V <sub>DD</sub> -1.3 | -   |      |

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | I <sub>IO</sub> = +6 mA<br>2 V < V <sub>DD</sub> < 2.7 V    | -                    | 0.4 | v    |

| V <sub>OH</sub> <sup>(2)(4)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at same time | 2 V < V <sub>DD</sub> < 2.7 V                               | V <sub>DD</sub> -0.4 | -   |      |

Table 47. Output voltage characteristics (continued)

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 8* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 8 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

3. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

4. Guaranteed by characterization results.

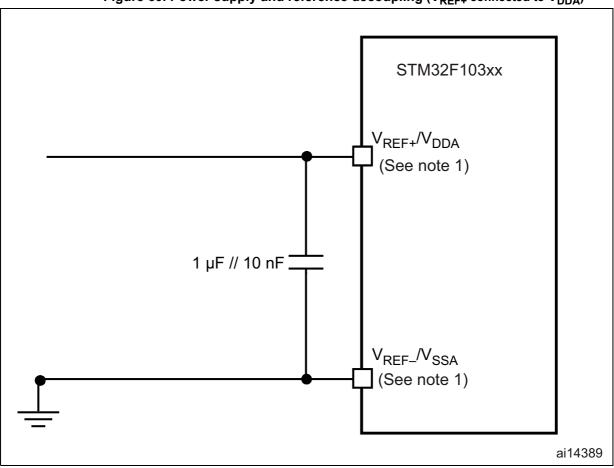

Figure 60. Power supply and reference decoupling (V<sub>REF+</sub> connected to V<sub>DDA</sub>)

1.  $V_{REF+}$  and  $V_{REF-}$  inputs are available only on 100-pin packages.

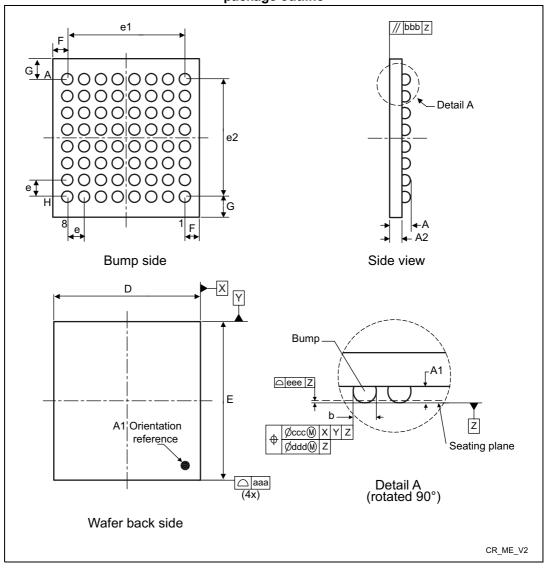

## 6.3 WLCSP64 package information

Figure 68. WLCSP, 64-ball 4.466 × 4.395 mm, 0.500 mm pitch, wafer-level chip-scale package outline

1. Drawing is not to scale.

2. Primary datum Z and seating plane are defined by the spherical crowns of the ball.

| Table 69. WLCSP, 64-ball 4.466 × 4.395 mm, 0.500 mm pitch, wafer-level chip-scale |  |  |  |  |

|-----------------------------------------------------------------------------------|--|--|--|--|

| package mechanical data                                                           |  |  |  |  |

| Symbol           | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|------------------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol           | Min         | Тур   | Мах   | Min                   | Тур    | Max    |

| А                | 0.535       | 0.585 | 0.635 | 0.0211                | 0.0230 | 0.0250 |

| A1               | 0.205       | 0.230 | 0.255 | 0.0081                | 0.0091 | 0.0100 |

| A2               | 0.330       | 0.355 | 0.380 | 0.0130                | 0.0140 | 0.0150 |

| b <sup>(2)</sup> | 0.290       | 0.320 | 0.350 | 0.0114                | 0.0126 | 0.0138 |

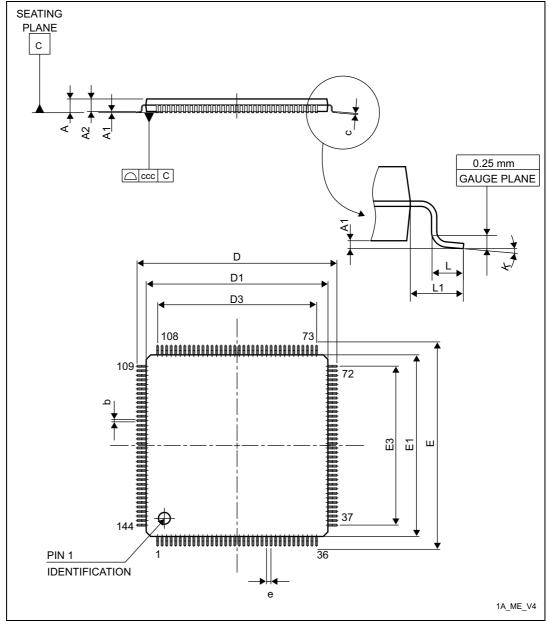

# 6.4 LQFP144 package information

Figure 70. LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package outline

1. Drawing is not to scale.

## 6.7 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 10: General operating conditions on page 44*.

The maximum chip-junction temperature,  $T_J$  max, in degrees Celsius, may be calculated using the following equation:

$T_J \max = T_A \max + (P_D \max x \Theta_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in °C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

$\mathsf{P}_{\mathsf{I}\!/\!\mathsf{O}}$  max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V<sub>OL</sub> / I<sub>OL</sub> and V<sub>OH</sub> / I<sub>OH</sub> of the I/Os at low and high level in the application.

| Symbol          | Parameter                                                                   | Value | Unit |  |

|-----------------|-----------------------------------------------------------------------------|-------|------|--|

| Θ <sub>JA</sub> | Thermal resistance junction-ambient<br>LFBGA144 - 10 × 10 mm / 0.8 mm pitch | 40    |      |  |

|                 | Thermal resistance junction-ambient<br>LQFP144 - 20 × 20 mm / 0.5 mm pitch  | 30    | °C/W |  |

|                 | Thermal resistance junction-ambient<br>LFBGA100 - 10 × 10 mm / 0.8 mm pitch | 40    |      |  |

|                 | Thermal resistance junction-ambient<br>LQFP100 - 14 × 14 mm / 0.5 mm pitch  | 46    |      |  |

|                 | Thermal resistance junction-ambient<br>LQFP64 - 10 × 10 mm / 0.5 mm pitch   | 45    |      |  |

|                 | Thermal resistance junction-ambient<br>WLCSP64                              | 50    |      |  |

### 6.7.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org

#### IMPORTANT NOTICE – PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics – All rights reserved

DocID14611 Rev 12