Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 12x12b; D/A 2x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep16gs202-i-mm |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                         | Pin<br>Type          | Buffer<br>Type       | PPS                  | Description                                                                                                                                                                                           |  |  |  |  |  |

|----------------------------------|----------------------|----------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PGA1P1-PGA1P3                    | I                    | Analog               | No                   | PGA1 Positive Inputs 1 through 3.                                                                                                                                                                     |  |  |  |  |  |

| PGA1N2                           | I                    | Analog               | No                   | PGA1 Negative Input 2.                                                                                                                                                                                |  |  |  |  |  |

| PGA2P1-PGA2P3                    | I                    | Analog               | No                   | PGA2 Positive Inputs 1 through 3.                                                                                                                                                                     |  |  |  |  |  |

| PGA2N2                           | I                    | Analog               | No                   | PGA2 Negative Input 2.                                                                                                                                                                                |  |  |  |  |  |

| ADTRG31                          | I                    | ST                   | No                   | External ADC trigger source.                                                                                                                                                                          |  |  |  |  |  |

| PGED1<br>PGEC1<br>PGED2<br>PGEC2 | I/O<br>I<br>I/O<br>I | ST<br>ST<br>ST<br>ST | No<br>No<br>No<br>No | Clock input pin for Programming/Debugging Communication Channel<br>Data I/O pin for Programming/Debugging Communication Channel 2.<br>Clock input pin for Programming/Debugging Communication Channel |  |  |  |  |  |

| PGED3<br>PGEC3                   | I/O<br>I             | ST<br>ST             | No<br>No             | Data I/O pin for Programming/Debugging Communication Channel 3.<br>Clock input pin for Programming/Debugging Communication Channel 3.                                                                 |  |  |  |  |  |

| MCLR                             | I/P                  | ST                   | No                   | Master Clear (Reset) input. This pin is an active-low Reset to the device.                                                                                                                            |  |  |  |  |  |

| AVdd                             | Р                    | Р                    | No                   | Positive supply for analog modules. This pin must be connected at all times.                                                                                                                          |  |  |  |  |  |

| AVss                             | Р                    | Р                    | No                   | Ground reference for analog modules. This pin must be connected at all times.                                                                                                                         |  |  |  |  |  |

| Vdd                              | Р                    | _                    | No                   | Positive supply for peripheral logic and I/O pins.                                                                                                                                                    |  |  |  |  |  |

| VCAP                             | Р                    |                      | No                   | CPU logic filter capacitor connection.                                                                                                                                                                |  |  |  |  |  |

| Vss                              | Р                    |                      | No                   | Ground reference for logic and I/O pins.                                                                                                                                                              |  |  |  |  |  |

#### TABLE 1-1. **PINOUT I/O DESCRIPTIONS (CONTINUED)**

egend: CMOS : CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels O = Output PPS = Peripheral Pin Select

Analog = Analog Input TTL = TTL input buffer

```

= Power

I = Input

```

# 4.5 Special Function Register Maps

### TABLE 4-2: CPU CORE REGISTER MAP

|                       | -2.   |        |        |        |              |            |              |            |              |            |            |           |             |               |             |                     |        |               |

|-----------------------|-------|--------|--------|--------|--------------|------------|--------------|------------|--------------|------------|------------|-----------|-------------|---------------|-------------|---------------------|--------|---------------|

| File<br>Name          | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12       | Bit 11     | Bit 10       | Bit 9      | Bit 8        | Bit 7      | Bit 6      | Bit 5     | Bit 4       | Bit 3         | Bit 2       | Bit 1               | Bit 0  | All<br>Resets |

| W0                    | 0000  |        |        |        |              |            |              |            | W0 (WRE      | G)         |            |           |             |               |             |                     |        | xxxx          |

| W1                    | 0002  |        |        |        |              |            |              |            | W1           |            |            |           |             |               |             |                     |        | xxxx          |

| W2                    | 0004  |        |        |        |              |            |              |            | W2           |            |            |           |             |               |             |                     |        | xxxx          |

| W3                    | 0006  |        |        |        |              |            |              |            | W3           |            |            |           |             |               |             |                     |        | xxxx          |

| W4                    | 8000  |        |        |        |              |            |              |            | W4           |            |            |           |             |               |             |                     |        | xxxx          |

| W5                    | 000A  |        |        |        |              |            |              |            | W5           |            |            |           |             |               |             |                     |        | xxxx          |

| W6                    | 000C  |        |        |        |              |            |              |            | W6           |            |            |           |             |               |             |                     |        | xxxx          |

| W7                    | 000E  |        |        |        |              |            |              |            | W7           |            |            |           |             |               |             |                     |        | xxxx          |

| W8                    | 0010  |        |        |        |              |            |              |            | W8           |            |            |           |             |               |             |                     |        | xxxx          |

| W9                    | 0012  |        | W9     |        |              |            |              |            |              |            | xxxx       |           |             |               |             |                     |        |               |

| W10                   | 0014  |        |        |        |              |            |              |            | W10          |            |            |           |             |               |             |                     |        | xxxx          |

| W11                   | 0016  |        |        |        |              |            |              |            | W11          |            |            |           |             |               |             |                     |        | xxxx          |

| W12                   | 0018  |        |        |        |              |            |              |            | W12          |            |            |           |             |               |             |                     |        | xxxx          |

| W13                   | 001A  |        |        |        |              |            |              |            | W13          |            |            |           |             |               |             |                     |        | xxxx          |

| W14                   | 001C  |        |        |        |              |            |              |            | W14          |            |            |           |             |               |             |                     |        | xxxx          |

| W15                   | 001E  |        |        |        |              |            |              |            | W15          |            |            |           |             |               |             |                     |        | xxxx          |

| SPLIM                 | 0020  |        |        |        |              |            |              |            | SPLIM        |            |            |           |             |               |             |                     |        | 0000          |

| ACCAL                 | 0022  |        |        |        |              |            |              |            | ACCAL        |            |            |           |             |               |             |                     |        | 0000          |

| ACCAH                 | 0024  |        |        |        |              |            |              |            | ACCAH        |            |            |           |             |               |             |                     |        | 0000          |

| ACCAU                 | 0026  |        |        | Się    | gn Extension | of ACCA<39 | )>           |            |              |            |            |           | ACC         | AU            |             |                     |        | 0000          |

| ACCBL                 | 0028  |        |        |        |              |            |              |            | ACCBL        |            |            |           |             |               |             |                     |        | 0000          |

| ACCBH                 | 002A  |        |        |        |              |            |              |            | ACCBH        |            |            |           |             |               |             |                     |        | 0000          |

| ACCBU                 | 002C  |        |        | Się    | gn Extension | of ACCB<39 | )>           |            |              |            |            |           | ACC         | BU            |             |                     |        | 0000          |

| PCL                   | 002E  |        |        |        |              |            |              | PC         | L<15:1>      |            |            |           |             |               |             |                     | _      | 0000          |

| PCH                   | 0030  | _      | _      | _      | _            | —          | —            | _          | _            | _          |            |           |             | PCH<6:0>      |             |                     |        | 0000          |

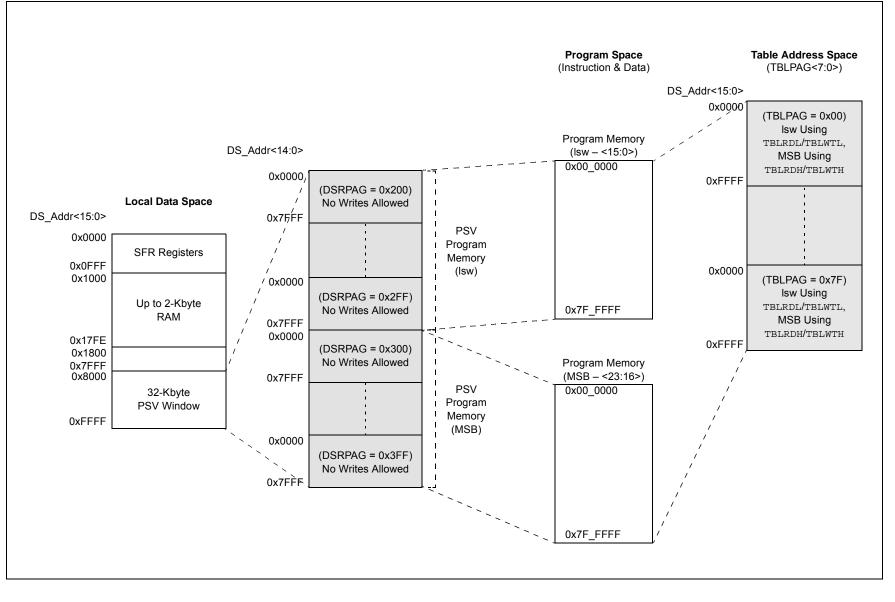

| DSRPAG                | 0032  | _      | _      | _      | _            | _          | _            |            | E            | Extended D | ata Space  | EDS) Read | I Page Reg  | ister (DSRI   | PAG<9:0>)   |                     |        | 0001          |

| DSWPAG <sup>(1)</sup> | 0034  | _      | _      | _      | _            | _          | _            | _          |              | Extend     | ed Data Sp | ace (EDS) | Write Page  | e Register (I | DSWPAG8     | :0>) <sup>(1)</sup> |        | 0001          |

| RCOUNT                | 0036  |        |        |        |              |            |              | F          | RCOUNT<1     | 5:0>       |            |           |             |               |             |                     |        | 0000          |

| DCOUNT                | 0038  |        |        |        |              |            | DO           | Loop Count | er Register  | (DCOUNT«   | <15:0>)    |           |             |               |             |                     |        | 0000          |

| DOSTARTL              | 003A  |        |        |        |              | DO         | Loop Start A | Address Re | gister Low ( | DOSTARTL   | _<15:1>)   |           |             |               |             |                     | —      | 0000          |

| DOSTARTH              | 003C  | —      | —      | —      | —            | —          | —            | —          | —            | —          | —          | DO LOO    | p Start Add | dress Regis   | ter High (D | OSTARTH             | <5:0>) | 0000          |

|                       | • •   |        |        |        |              |            |              |            |              |            |            | •         |             |               |             |                     |        | ·             |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The contents of this register should never be modified. The DSWPAG must always point to the first page.

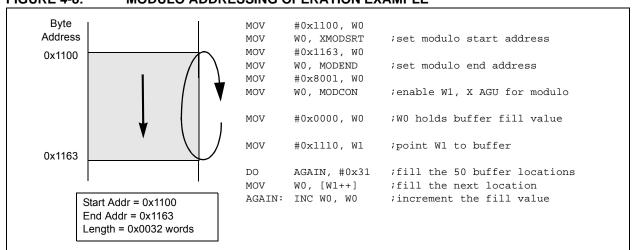

# 4.7 Modulo Addressing

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a Bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

### 4.7.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-2).

Note: Y space Modulo Addressing EA calculations assume word-sized data (LSb of every EA is always clear).

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

### 4.7.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags, as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-2). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit is set (MODCON<15>).

The Y Address Space Pointer W register (YWM), to which Modulo Addressing is to be applied, is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit is set at MODCON<14>.

### FIGURE 4-8: MODULO ADDRESSING OPERATION EXAMPLE

# **REGISTER 7-1:** SR: CPU STATUS REGISTER<sup>(1)</sup>

| R/W-0                | R/W-0                | R/W-0                | R/W-0 | R/C-0 | R/C-0 | R-0   | R/W-0 |

|----------------------|----------------------|----------------------|-------|-------|-------|-------|-------|

| OA                   | OB                   | SA                   | SB    | OAB   | SAB   | DA    | DC    |

| bit 15               |                      | •                    |       |       |       |       | bit 8 |

|                      |                      |                      |       |       |       |       |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA    | N     | OV    | Z     | С     |

| bit 7                | •                    | •                    |       | •     |       |       | bit 0 |

|                      |                      |                      |       |       |       |       |       |

| Legend:           | C = Clearable bit |                             |                    |

|-------------------|-------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2,3)</sup> 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled 110 = CPU Interrupt Priority Level is 6 (14) 101 = CPU Interrupt Priority Level is 5 (13) 100 = CPU Interrupt Priority Level is 4 (12) 011 = CPU Interrupt Priority Level is 3 (11) 010 = CPU Interrupt Priority Level is 2 (10) 001 = CPU Interrupt Priority Level is 2 (10)

- 001 = CPU Interrupt Priority Level is 1 (9)

- 000 = CPU Interrupt Priority Level is 0 (8)

**Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

### REGISTER 7-2: CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| R/W-0  | U-0 | R/W-0 | R/W-0 | R/W-0 | R-0 | R-0 | R-0   |

|--------|-----|-------|-------|-------|-----|-----|-------|

| VAR    | —   | US1   | US0   | EDT   | DL2 | DL1 | DL0   |

| bit 15 |     |       |       |       |     |     | bit 8 |

| R/W-0 | R/W-0 | R/W-1 | R/W-0  | R/C-0               | R-0 | R/W-0 | R/W-0 |

|-------|-------|-------|--------|---------------------|-----|-------|-------|

| SATA  | SATB  | SATDW | ACCSAT | IPL3 <sup>(2)</sup> | SFA | RND   | IF    |

| bit 7 |       |       |        |                     |     |       | bit 0 |

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

bit 15 VAR: Variable Exception Processing Latency Control bit 1 = Variable exception processing latency

0 = Fixed exception processing latency

bit 3 IPL3: CPU Interrupt Priority Level Status bit 3<sup>(2)</sup> 1 = CPU Interrupt Priority Level is greater than 7 0 = CPU Interrupt Priority Level is 7 or less

Note 1: For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

# REGISTER 7-5: INTCON3: INTERRUPT CONTROL REGISTER 3

| U-0          | U-0           | U-0                                              | U-0              | U-0                                     | U-0              | U-0      | R/W-0 |  |  |  |  |  |  |

|--------------|---------------|--------------------------------------------------|------------------|-----------------------------------------|------------------|----------|-------|--|--|--|--|--|--|

|              |               | _                                                | —                | —                                       | —                | —        | NAE   |  |  |  |  |  |  |

| bit 15       |               |                                                  |                  |                                         |                  |          | bit 8 |  |  |  |  |  |  |

|              |               |                                                  |                  |                                         |                  |          |       |  |  |  |  |  |  |

| U-0          | U-0           | U-0                                              | R/W-0            | U-0                                     | U-0              | U-0      | R/W-0 |  |  |  |  |  |  |

|              |               |                                                  | DOOVR            |                                         |                  |          | APLL  |  |  |  |  |  |  |

| bit 7        |               |                                                  |                  |                                         |                  |          | bit 0 |  |  |  |  |  |  |

|              |               |                                                  |                  |                                         |                  |          |       |  |  |  |  |  |  |

| Legend:      |               |                                                  |                  |                                         |                  |          |       |  |  |  |  |  |  |

| R = Readab   | ole bit       | W = Writable                                     | bit              | U = Unimplei                            | mented bit, read | l as '0' |       |  |  |  |  |  |  |

| -n = Value a | at POR        | '1' = Bit is se                                  | t                | '0' = Bit is cleared x = Bit is unknown |                  |          |       |  |  |  |  |  |  |

|              |               |                                                  |                  |                                         |                  |          |       |  |  |  |  |  |  |

| bit 15-9     | Unimplemen    | ted: Read as                                     | '0'              |                                         |                  |          |       |  |  |  |  |  |  |

| bit 8        | NAE: NVM A    | NAE: NVM Address Error Soft Trap Status bit      |                  |                                         |                  |          |       |  |  |  |  |  |  |

|              | 1 = NVM add   | 1 = NVM address error soft trap has occurred     |                  |                                         |                  |          |       |  |  |  |  |  |  |

|              | 0 = NVM add   | 0 = NVM address error soft trap has not occurred |                  |                                         |                  |          |       |  |  |  |  |  |  |

| bit 7-5      | Unimplemen    | ted: Read as                                     | '0'              |                                         |                  |          |       |  |  |  |  |  |  |

| bit 4        | DOOVR: DO     | Stack Overflov                                   | v Soft Trap Sta  | itus bit                                |                  |          |       |  |  |  |  |  |  |

|              | 1 = DO stack  | overflow soft t                                  | rap has occurr   | ed                                      |                  |          |       |  |  |  |  |  |  |

|              |               |                                                  | rap has not oc   |                                         |                  |          |       |  |  |  |  |  |  |

| bit 3-1      | Unimplemen    | ted: Read as                                     | '0'              |                                         |                  |          |       |  |  |  |  |  |  |

| bit 0        | APLL: Auxilia | ary PLL Loss o                                   | of Lock Soft Tra | ap Status bit                           |                  |          |       |  |  |  |  |  |  |

|              | 1 = APLL loc  | k soft trap has                                  | occurred         |                                         |                  |          |       |  |  |  |  |  |  |

|              |               | k coft tran hac                                  | not occurred     |                                         |                  |          |       |  |  |  |  |  |  |

0 = APLL lock soft trap has not occurred

### REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0             | U-0                                           | U-0              | U-0            | U-0                                     | U-0              | U-0    | U-0   |  |  |  |  |

|-----------------|-----------------------------------------------|------------------|----------------|-----------------------------------------|------------------|--------|-------|--|--|--|--|

| —               | —                                             | —                | —              | —                                       | —                | —      | —     |  |  |  |  |

| bit 15          |                                               |                  |                |                                         |                  |        | bit 8 |  |  |  |  |

|                 |                                               |                  |                |                                         |                  |        |       |  |  |  |  |

| U-0             | U-0                                           | U-0              | U-0            | U-0                                     | U-0              | U-0    | R/W-0 |  |  |  |  |

| —               | —                                             | —                | —              | —                                       | —                | —      | SGHT  |  |  |  |  |

| bit 7           |                                               |                  |                | •                                       |                  | •      | bit 0 |  |  |  |  |

|                 |                                               |                  |                |                                         |                  |        |       |  |  |  |  |

| Legend:         |                                               |                  |                |                                         |                  |        |       |  |  |  |  |

| R = Readable    | bit                                           | W = Writable     | bit            | U = Unimpler                            | mented bit, read | as '0' |       |  |  |  |  |

| -n = Value at F | POR                                           | '1' = Bit is set |                | '0' = Bit is cleared x = Bit is unknown |                  |        |       |  |  |  |  |

|                 |                                               |                  |                |                                         |                  |        |       |  |  |  |  |

| bit 15-1        | Unimplemen                                    | ted: Read as '   | 0'             |                                         |                  |        |       |  |  |  |  |

| bit 0           | SGHT: Softwa                                  | are Generated    | Hard Trap Sta  | tus bit                                 |                  |        |       |  |  |  |  |

|                 | 1 = Software generated hard trap has occurred |                  |                |                                         |                  |        |       |  |  |  |  |

|                 | 0 = Software                                  | generated har    | d trap has not | occurred                                |                  |        |       |  |  |  |  |

|                 |                                               |                  |                |                                         |                  |        |       |  |  |  |  |

NOTES:

| R/W-0                                                                    | R/W-0                                            | R/W-0                                                                                                            | R/W-0                              | R/W-0            | R/W-0          | R/W-0              | R/W-0  |  |

|--------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------|----------------|--------------------|--------|--|

| FLT4R7                                                                   | FLT4R6                                           | FLT4R5                                                                                                           | FLT4R4                             | FLT4R3           | FLT4R2         | FLT4R1             | FLT4R0 |  |

| bit 15                                                                   |                                                  |                                                                                                                  |                                    |                  |                |                    | bit 8  |  |

|                                                                          |                                                  |                                                                                                                  |                                    |                  |                |                    |        |  |

| R/W-0                                                                    | R/W-0                                            | R/W-0                                                                                                            | R/W-0                              | R/W-0            | R/W-0          | R/W-0              | R/W-0  |  |

| FLT3R7                                                                   | FLT3R6                                           | FLT3R5                                                                                                           | FLT3R4                             | FLT3R3           | FLT3R2         | FLT3R1             | FLT3R0 |  |

| bit 7                                                                    |                                                  |                                                                                                                  |                                    |                  |                |                    | bit (  |  |

| Legend:                                                                  |                                                  |                                                                                                                  |                                    |                  |                |                    |        |  |

| R = Readable bit $W$ = Writable bit $U$ = Unimplemented bit, read as '0' |                                                  |                                                                                                                  |                                    |                  |                |                    |        |  |

| -n = Value at                                                            | POR                                              | '1' = Bit is set                                                                                                 |                                    | '0' = Bit is cle | ared           | x = Bit is unknown |        |  |

| bit 7-0                                                                  | 10110100 =<br>•<br>•<br>00000000 =<br>FLT3R<7:0> | Input tied to RI<br>Input tied to RI<br>Input tied to RI<br>Input tied to Vs<br>: Assign PWM<br>Input tied to RI | ⊃180<br>⊃1<br>SS<br>Fault 3 (FLT3) | to the Corresp   | ponding RPn Pi | in bits            |        |  |

|                                                                          | 10110100 =<br>•<br>•<br>•<br>00000001 =          | Input tied to RI<br>Input tied to RI<br>Input tied to RI                                                         | ⊃180<br>⊃1                         |                  |                |                    |        |  |

### REGISTER 10-8: RPINR13: PERIPHERAL PIN SELECT INPUT REGISTER 13

### REGISTER 15-27: PWMCAPx: PWMx PRIMARY TIME BASE CAPTURE REGISTER

| R-0              | R-0 | R-0                        | R-0    | R-0                         | R-0              | R-0      | R-0   |

|------------------|-----|----------------------------|--------|-----------------------------|------------------|----------|-------|

|                  |     |                            | PWMCAP | <12:5> <sup>(1,2,3,4)</sup> |                  |          |       |

| bit 15           |     |                            |        |                             |                  |          | bit 8 |

|                  |     |                            |        |                             |                  |          |       |

| R-0              | R-0 | R-0                        | R-0    | R-0                         | U-0              | U-0      | U-0   |

|                  | PW  | /MCAP<4:0> <sup>(1,2</sup> | ,3,4)  |                             | —                | —        | —     |

| bit 7            |     |                            |        |                             |                  |          | bit 0 |

|                  |     |                            |        |                             |                  |          |       |

| Legend:          |     |                            |        |                             |                  |          |       |

| R = Readable bit |     | W = Writable I             | bit    | U = Unimplen                | nented bit, read | l as '0' |       |

R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-3 **PWMCAP<12:0>:** Captured PWMx Time Base Value bits<sup>(1,2,3,4)</sup> The value in this register represents the captured PWMx time base value when a leading edge is detected on the current-limit input.

#### bit 2-0 Unimplemented: Read as '0'

- **Note 1:** The capture feature is only available on a primary output (PWMxH).

- 2: This feature is active only after LEB processing on the current-limit input signal is complete.

- **3:** The minimum capture resolution is 8.32 ns.

- 4: This feature can be used when the XPRES bit (PWMCONx<1>) is set to '0'.

### 16.1 SPI Helpful Tips

- 1. In Frame mode, if there is a possibility that the master may not be initialized before the slave:

- a) If FRMPOL (SPI1CON2<13>) = 1, use a pull-down resistor on SS1.

- b) If FRMPOL = 0, use a pull-up resistor on  $\overline{SS1}$ .

| Note: | This                  | ensures   | that     | the       | first | fra | ame |

|-------|-----------------------|-----------|----------|-----------|-------|-----|-----|

|       | transr                | mission a | after in | nitializa | ation | is  | not |

|       | shifted or corrupted. |           |          |           |       |     |     |

- 2. In Non-Framed 3-Wire mode (i.e., not using SS1 from a master):

- a) If CKP (SPI1CON1<6>) = 1, always place a pull-up resistor on SS1.

- b) If CKP = <u>0</u>, always place a pull-down resistor on SS1.

- **Note:** This will ensure that during power-up and initialization, the master/slave will not lose synchronization due to an errant SCK1 transition that would cause the slave to accumulate data shift errors for both transmit and receive, appearing as corrupted data.

- FRMEN (SPI1CON2<15>) = 1 and SSEN (SPI1CON1<7>) = 1 are exclusive and invalid. In Frame mode, SCK1 is continuous and the frame sync pulse is active on the SS1 pin, which indicates the start of a data frame.

| Note: | Not all third-party devices support Frame  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|

|       | mode timing. Refer to the SPI1             |  |  |  |  |  |  |  |

|       | specifications in Section 25.0 "Electrical |  |  |  |  |  |  |  |

|       | Characteristics" for details.              |  |  |  |  |  |  |  |

In Master mode only, set the SMP bit (SPI1CON1<9>) to a '1' for the fastest SPI1 data rate possible. The SMP bit can only be set at the same time or after the MSTEN bit (SPI1CON1<5>) is set.

To avoid invalid slave read data to the master, the user's master software must ensure enough time for slave software to fill its write buffer before the user application initiates a master write/read cycle. It is always advisable to preload the SPI1BUF Transmit register in advance of the next master transaction cycle. SPI1BUF is transferred to the SPI1 Shift register and is empty once the data transmission begins.

### 16.2 SPI Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 16.2.1 KEY RESOURCES

- "Serial Peripheral Interface (SPI)" (DS70005185) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

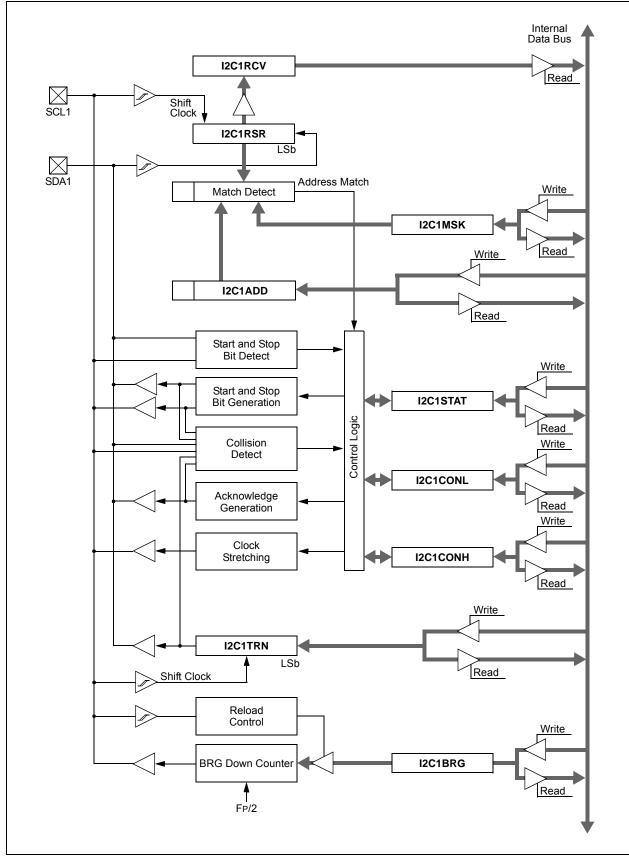

# FIGURE 17-1: I2C1 BLOCK DIAGRAM

### REGISTER 19-7: ADCON4L: ADC CONTROL REGISTER 4 LOW

| -n = Value at POR (1' = Bit is set |     |     | '0' = Bit is clea                  | ared | x = Bit is unkno | wn                      |                         |

|------------------------------------|-----|-----|------------------------------------|------|------------------|-------------------------|-------------------------|

| R = Readable bit W = Writable bit  |     |     | U = Unimplemented bit, read as '0' |      |                  |                         |                         |

| Legend:                            |     |     |                                    |      |                  |                         |                         |

|                                    |     |     |                                    |      |                  |                         | bit o                   |

| bit 7                              |     |     |                                    |      |                  |                         | bit 0                   |

| _                                  |     | —   |                                    |      |                  | SAMC1EN                 | SAMC0EN                 |

| U-0                                | U-0 | U-0 | U-0                                | U-0  | U-0              | R/W-0                   | R/W-0                   |

|                                    |     |     |                                    |      |                  |                         |                         |

| bit 15                             |     |     |                                    | ·    |                  |                         | bit 8                   |

| —                                  | _   | —   | —                                  | —    | _                | SYNCTRG1 <sup>(1)</sup> | SYNCTRG0 <sup>(1)</sup> |

| U-0                                | U-0 | U-0 | U-0                                | U-0  | U-0              | R/W-0                   | R/W-0                   |

bit 15-10 Unimplemented: Read as '0'

bit 9-8 **SYNCTRG<1:0>** Dedicated ADC Core x Trigger Synchronization bits<sup>(1)</sup> 1 = All triggers are synchronized with the Core Source Clock (TCORESRC) 0 = The ADC core triggers are not synchronized

#### bit 7-2 Unimplemented: Read as '0'

### bit 1-0 SAMC1EN:SAMC0EN: Dedicated ADC Core x Conversion Delay Enable bits

1 = After trigger, the conversion will be delayed and the ADC core will continue sampling during the time specified by the SAMC<9:0> bits in the ADCORExL register

- 0 = After trigger, the sampling will be stopped immediately and the conversion will be started on the next core clock cycle.

- **Note 1:** For proper ADC performance, this bit must be set when using level-sensitive triggers and cleared for edge-sensitive triggers.

# REGISTER 19-13: ADLVLTRGL: ADC LEVEL-SENSITIVE TRIGGER CONTROL REGISTER LOW

| U-0                                            | R/W-0                      | U-0                                             | U-0               | R/W-0             | R/W-0           | R/W-0            | R/W-0 |  |  |  |

|------------------------------------------------|----------------------------|-------------------------------------------------|-------------------|-------------------|-----------------|------------------|-------|--|--|--|

| _                                              | LVLEN14                    | —                                               | —                 |                   | LVLE            | EN<11:8>         |       |  |  |  |

| bit 15                                         |                            |                                                 |                   |                   |                 |                  | bit 8 |  |  |  |

|                                                |                            |                                                 |                   |                   |                 |                  |       |  |  |  |

| R/W-0                                          | R/W-0                      | R/W-0                                           | R/W-0             | R/W-0             | R/W-0           | R/W-0            | R/W-0 |  |  |  |

|                                                |                            |                                                 | LVL               | .EN<7:0>          |                 |                  |       |  |  |  |

| bit 7                                          |                            |                                                 |                   |                   |                 | bit 0            |       |  |  |  |

|                                                |                            |                                                 |                   |                   |                 |                  |       |  |  |  |

| Legend:                                        |                            |                                                 |                   |                   |                 |                  |       |  |  |  |

| R = Readab                                     | ole bit                    | W = Writable                                    | bit               | U = Unimplem      | nented bit, rea | d as '0'         |       |  |  |  |

| -n = Value a                                   | at POR                     | '1' = Bit is set                                |                   | '0' = Bit is clea | ared            | x = Bit is unkno | wn    |  |  |  |

|                                                |                            |                                                 |                   |                   |                 |                  |       |  |  |  |

| bit 15                                         | Unimpleme                  | nted: Read as                                   | '0'               |                   |                 |                  |       |  |  |  |

| bit 14                                         | LVLEN14: L                 | evel Trigger 14                                 | Enable bit        |                   |                 |                  |       |  |  |  |

|                                                | 1 = Input Ch               | 1 = Input Channel 14 trigger is level-sensitive |                   |                   |                 |                  |       |  |  |  |

| 0 = Input Channel 14 trigger is edge-sensitive |                            |                                                 |                   |                   |                 |                  |       |  |  |  |

| bit 13-12                                      | Unimplemented: Read as '0' |                                                 |                   |                   |                 |                  |       |  |  |  |

| bit 11-0                                       | LVLEN<11:0                 | VLEN<11:0>: Level Trigger x Enable bits         |                   |                   |                 |                  |       |  |  |  |

|                                                | 1 = Input Ch               | annel x trigger                                 | is level-sensitiv | ve                |                 |                  |       |  |  |  |

|                                                | 0 = Input Ch               | annel x trigger                                 | is edge-sensiti   | ve                |                 |                  |       |  |  |  |

|                                                |                            |                                                 |                   |                   |                 |                  |       |  |  |  |

# 20.0 HIGH-SPEED ANALOG COMPARATOR

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed Analog Comparator Module" (DS70005128) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The high-speed analog comparator module monitors current and/or voltage transients that may be too fast for the CPU and ADC to capture.

### 20.1 Features Overview

The SMPS comparator module offers the following major features:

- Two Rail-to-Rail Analog Comparators

- Dedicated 12-Bit DAC for each Analog Comparator

- Up to Six Selectable Input Sources per Comparator:

- Four external inputs

- Two internal inputs from the PGAx module

- Programmable Comparator Hysteresis

- Programmable Output Polarity

- Voltage References for the DACx:

- AVDD

- Interrupt Generation Capability

- Functional Support for PWM:

- PWM duty cycle control

- PWM period control

- PWM Fault detected

#### TABLE 25-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

| DC CHARACTERISTICS |        |                                                               | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |         |            |                        |  |

|--------------------|--------|---------------------------------------------------------------|-------------------------------------------------------|-----|---------|------------|------------------------|--|

| Param<br>No.       | Symbol | I Characteristic Min. Typ. <sup>(1)</sup> Max. Units          |                                                       |     |         | Conditions |                        |  |

|                    | VIL    | Input Low Voltage                                             |                                                       |     |         |            |                        |  |

| DI10               |        | Any I/O Pin and MCLR                                          | Vss                                                   | —   | 0.2 Vdd | V          |                        |  |

| DI18               |        | I/O Pins with SDA1, SCL1                                      | Vss                                                   | —   | 0.3 Vdd | V          | SMBus disabled         |  |

| DI19               |        | I/O Pins with SDA1, SCL1                                      | Vss                                                   | —   | 0.8     | V          | SMBus enabled          |  |

|                    | Vih    | Input High Voltage                                            |                                                       |     |         |            |                        |  |

| DI20               |        | I/O Pins Not 5V Tolerant <sup>(4)</sup>                       | 0.8 Vdd                                               | —   | Vdd     | V          |                        |  |

|                    |        | I/O Pins 5V Tolerant and MCLR <sup>(4)</sup>                  | 0.8 VDD                                               | —   | 5.5     | V          |                        |  |

|                    |        | 5V Tolerant I/O Pins with SDA1, SCL1 <sup>(4)</sup>           | 0.8 Vdd                                               | —   | 5.5     | V          | SMBus disabled         |  |

|                    |        | 5V I/O Pins with SDA1, SCL1 <sup>(4)</sup>                    | 2.1                                                   | —   | 5.5     | V          | SMBus enabled          |  |

|                    |        | I/O Pins with SDA1, SCL1 Not<br>5V Tolerant <sup>(4)</sup>    | 0.8 Vdd                                               | —   | Vdd     | V          | SMBus disabled         |  |

|                    |        | I/O Pins with SDA1, SCL1 Not<br>5V Tolerant <sup>(4)</sup>    | 2.1                                                   | —   | Vdd     | V          | SMBus enabled          |  |

| DI30               | ICNPU  | Input Change Notification<br>Pull-up Current                  | 50                                                    | 250 | 600     | μA         | VDD = 3.3V, VPIN = VSS |  |

| DI31               | ICNPD  | Input Change Notification<br>Pull-Down Current <sup>(5)</sup> | —                                                     | 50  |         | μA         | VDD = 3.3V, VPIN = VDD |  |

**Note 1:** Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

- 4: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 5: VIL Source < (Vss 0.3). Characterized but not tested.

- **6:** VIH source > (VDD + 0.3) for non-5V tolerant pins only.

- 7: Digital 5V tolerant pins do not have an internal high side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

- 8: |Injection Currents| > 0 can affect the ADC results by approximately 4-6 counts.

- **9:** Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted, provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

### TABLE 25-42: ADC MODULE SPECIFICATIONS (CONTINUED)

| AC CHA       |        | STICS                               | Standard Op<br>(unless othe<br>Operating ter | erwise stat | <b>ed)<sup>(4)</sup></b><br>-40°C ≤ T⁄ | م ≤ +85° | 3.6V<br>C for Industrial<br>°C for Extended    |

|--------------|--------|-------------------------------------|----------------------------------------------|-------------|----------------------------------------|----------|------------------------------------------------|

| Param<br>No. | Symbol | Characteristics <sup>(3)</sup>      | Min.                                         | Typical     | Max.                                   | Units    | Conditions                                     |

|              |        | ADC                                 | Accuracy: S                                  | ingle-Ende  | ed Input                               |          |                                                |

| AD20b        | Nr     | Resolution                          |                                              | 12          |                                        | bits     |                                                |

| AD21b        | INL    | Integral Nonlinearity               | > -4                                         | _           | < 4                                    | LSb      | AVss = 0V, AVDD = 3.3V                         |

| AD22b        | DNL    | Pseudo-Differential<br>Nonlinearity | > -1                                         | —           | < 1.5                                  | LSb      | AVss = 0V, AVDD = 3.3V<br>(Note 5)             |

| AD23b        | Gerr   | Gain Error<br>(Dedicated Core)      | > -5                                         | —           | < 5                                    | LSb      | AVss = 0V, AVdd = 3.3V                         |

|              |        | Gain Error<br>(Shared Core)         | > -5                                         | —           | < 5                                    | LSb      | AVss = 0V, AVdd = 3.3V,<br>-40°C < TA ≤ +85°C  |

|              |        |                                     | > -6                                         | —           | < 6                                    | LSb      | AVss = 0V, AVdd = 3.3V,<br>-85°C < TA ≤ +125°C |

| AD24b        | EOFF   | Offset Error<br>(Dedicated Core)    | 0                                            | 7           | < 12                                   | LSb      | AVss = 0V, AVdd = 3.3V                         |

|              |        | Offset Error<br>(Shared Core)       | 0                                            | 7           | < 12                                   | LSb      |                                                |

| AD25b        | _      | Monotonicity                        | —                                            | _           | —                                      | —        | Guaranteed                                     |

|              |        |                                     | Dynamic Po                                   | erformanc   | e                                      |          |                                                |

| AD31b        | SINAD  | Signal-to-Noise and<br>Distortion   | 63                                           | _           | > 65                                   | dB       | (Notes 2, 3)                                   |

| AD34b        | ENOB   | Effective Number of bits            | 10.3                                         | _           |                                        | bits     | (Notes 2, 3)                                   |

Note 1: These parameters are not characterized or tested in manufacturing.

2: These parameters are characterized but not tested in manufacturing.

**3:** Characterized with a 1 kHz sine wave.

**4:** The ADC module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is ensured, but not characterized.

5: No missing codes, limits are based on the characterization results.

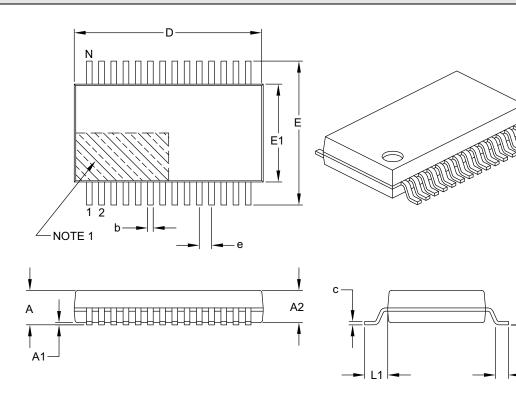

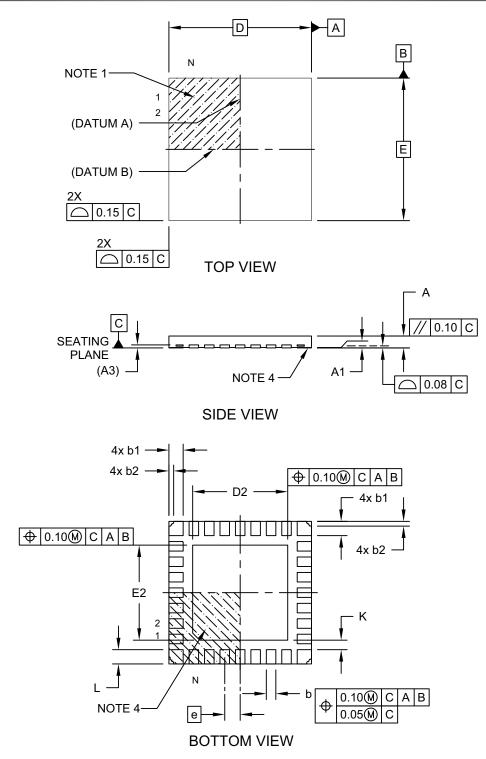

### 27.2 Package Details

# 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    |          |          | 5     |  |

|--------------------------|----------|----------|----------|-------|--|

| Dimensio                 | n Limits | MIN      | NOM      | MAX   |  |

| Number of Pins           | Ν        |          | 28       |       |  |

| Pitch                    | е        |          | 0.65 BSC |       |  |

| Overall Height           | А        | -        | -        | 2.00  |  |

| Molded Package Thickness | A2       | 1.65     | 1.75     | 1.85  |  |

| Standoff                 | A1       | 0.05     | -        | -     |  |

| Overall Width            | Е        | 7.40     | 7.80     | 8.20  |  |

| Molded Package Width     | E1       | 5.00     | 5.30     | 5.60  |  |

| Overall Length           | D        | 9.90     | 10.20    | 10.50 |  |

| Foot Length              | L        | 0.55     | 0.75     | 0.95  |  |

| Footprint                | L1       | 1.25 REF |          |       |  |

| Lead Thickness           | С        | 0.09     | _        | 0.25  |  |

| Foot Angle               | φ        | 0°       | 4°       | 8°    |  |

| Lead Width               | b        | 0.22     | -        | 0.38  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

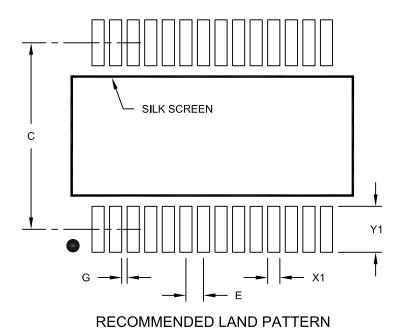

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |          |      |      |  |

|--------------------------|------------------|----------|------|------|--|

| Dimensio                 | Dimension Limits |          |      | MAX  |  |

| Contact Pitch            | E                | 0.65 BSC |      |      |  |

| Contact Pad Spacing      | С                |          | 7.20 |      |  |

| Contact Pad Width (X28)  | X1               |          |      | 0.45 |  |

| Contact Pad Length (X28) | Y1               |          |      | 1.75 |  |

| Distance Between Pads    | G                | 0.20     |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

# 28-Lead Plastic Quad Flat, No Lead Package (MX) - 6x6x0.5mm Body [UQFN] Ultra-Thin with 0.40 x 0.60 mm Terminal Width/Length and Corner Anchors

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-0209 Rev C Sheet 1 of 2