#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 12x12b; D/A 2x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                  |

| Supplier Device Package    | 28-SSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep16gs202-i-ss |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

## 2.1 Basic Connection Requirements

Getting started with the dsPIC33EPXXGS202 family requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins regardless if ADC module is not used (see Section 2.2 "Decoupling Capacitors")

- VCAP (see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.5 "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used (see Section 2.6 "External Oscillator Pins")

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended to use ceramic capacitors.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, above tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

## 4.3 Data Address Space

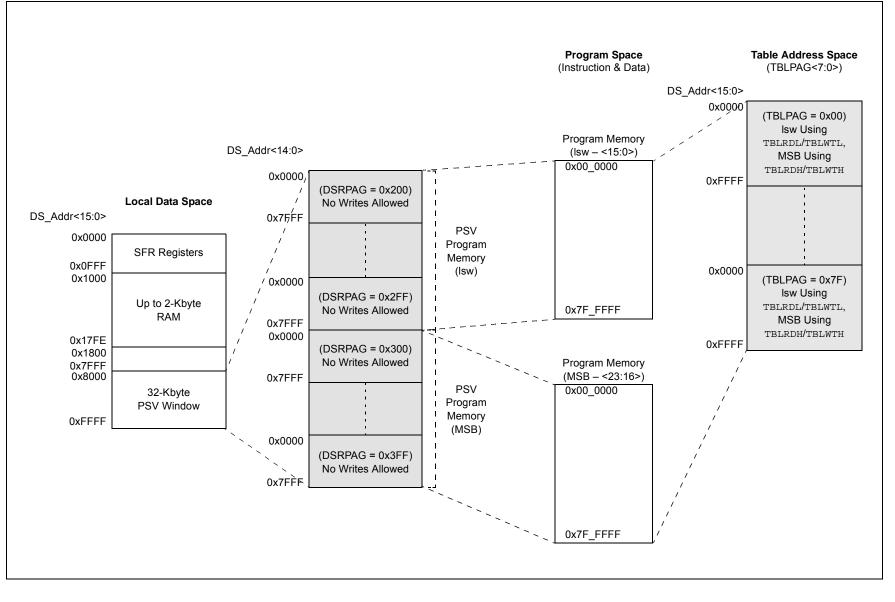

The dsPIC33EPXXGS202 family CPU has a separate 16-bit wide data memory space. The Data Space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory map is shown in Figure 4-4.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This arrangement gives a base Data Space address range of 64 Kbytes or 32K words.

The lower half of the data memory space (i.e., when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility (PSV).

dsPIC33EPXXGS202 family devices implement up to 12 Kbytes of data memory. If an EA points to a location outside of this area, an all-zero word or byte is returned.

### 4.3.1 DATA SPACE WIDTH

The data memory space is organized in byteaddressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### 4.3.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve Data Space memory usage efficiency, the dsPIC33EPXXGS202 family instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through wordaligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode, but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB; the MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

### 4.3.3 SFR SPACE

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, are primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33EPXXGS202 family core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control, and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

## 4.3.4 NEAR DATA SPACE

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a Working register as an Address Pointer.

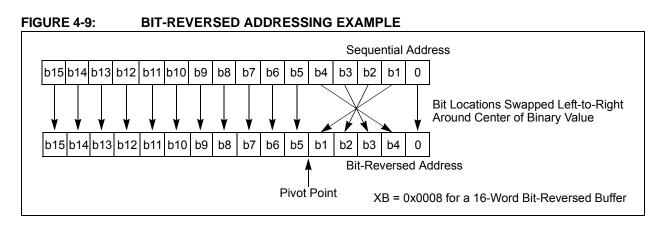

### TABLE 4-26: BIT-REVERSED ADDRESSING SEQUENCE (16-ENTRY)

|    | Normal Address |    |    |         |    |    | Bit-Rev | ersed Ac | Idress  |

|----|----------------|----|----|---------|----|----|---------|----------|---------|

| A3 | A2             | A1 | A0 | Decimal | A3 | A2 | A1      | A0       | Decimal |

| 0  | 0              | 0  | 0  | 0       | 0  | 0  | 0       | 0        | 0       |

| 0  | 0              | 0  | 1  | 1       | 1  | 0  | 0       | 0        | 8       |

| 0  | 0              | 1  | 0  | 2       | 0  | 1  | 0       | 0        | 4       |

| 0  | 0              | 1  | 1  | 3       | 1  | 1  | 0       | 0        | 12      |

| 0  | 1              | 0  | 0  | 4       | 0  | 0  | 1       | 0        | 2       |

| 0  | 1              | 0  | 1  | 5       | 1  | 0  | 1       | 0        | 10      |

| 0  | 1              | 1  | 0  | 6       | 0  | 1  | 1       | 0        | 6       |

| 0  | 1              | 1  | 1  | 7       | 1  | 1  | 1       | 0        | 14      |

| 1  | 0              | 0  | 0  | 8       | 0  | 0  | 0       | 1        | 1       |

| 1  | 0              | 0  | 1  | 9       | 1  | 0  | 0       | 1        | 9       |

| 1  | 0              | 1  | 0  | 10      | 0  | 1  | 0       | 1        | 5       |

| 1  | 0              | 1  | 1  | 11      | 1  | 1  | 0       | 1        | 13      |

| 1  | 1              | 0  | 0  | 12      | 0  | 0  | 1       | 1        | 3       |

| 1  | 1              | 0  | 1  | 13      | 1  | 0  | 1       | 1        | 11      |

| 1  | 1              | 1  | 0  | 14      | 0  | 1  | 1       | 1        | 7       |

| 1  | 1              | 1  | 1  | 15      | 1  | 1  | 1       | 1        | 15      |

NOTES:

| TABLE I-I. INTERROTTVEC           |         |         |                   | i                      |           |              |  |

|-----------------------------------|---------|---------|-------------------|------------------------|-----------|--------------|--|

| Interrunt Source                  | Vector  | IRQ     | IVT Address       | Interrupt Bit Location |           |              |  |

| Interrupt Source                  | #       | #       | IVI Address       | Flag                   | Enable    | Priority     |  |

| Reserved                          | 126-158 | 118-150 | 0x000100-0x000140 | —                      |           | _            |  |

| AN8 Conversion Done               | 159     | 151     | 0x000142          | IFS9<7>                | IEC9<7>   | IPC37<14:12> |  |

| AN9 Conversion Done               | 160     | 152     | 0x000144          | IFS9<8>                | IEC9<8>   | IPC38<2:0>   |  |

| AN10 Conversion Done              | 161     | 153     | 0x000146          | IFS9<9>                | IEC9<9>   | IPC38<6:4>   |  |

| AN11 Conversion Done              | 162     | 154     | 0x000148          | IFS9<10>               | IEC9<10>  | IPC38<10:8>  |  |

| Reserved                          | 163-164 | 155-156 | 0x00014A-0x00014C | —                      | -         | _            |  |

| AN14 Conversion Done              | 165     | 157     | 0x00014E          | IFS9<13>               | IEC9<13>  | IPC39<6:4>   |  |

| Reserved                          | 163-180 | 155-172 | 0x00014A-0x00016C | —                      | -         | _            |  |

| I2C1 – I2C1 Bus Collision         | 181     | 173     | 0x00016E          | IFS10<13>              | IEC10<13> | IPC43<6:4>   |  |

| Reserved                          | 182-184 | 174-176 | 0x000170-0x000174 | —                      | -         | —            |  |

| ADCMP0 – ADC Digital Comparator 0 | 185     | 177     | 0x000176          | IFS11<1>               | IEC11<1>  | IPC44<6:4>   |  |

| ADCMP1 – ADC Digital Comparator 1 | 186     | 178     | 0x000178          | IFS11<2>               | IEC11<2>  | IPC44<10:8>  |  |

| ADFL0 – ADC Filter 0              | 187     | 179     | 0x00017A          | IFS11<3>               | IEC11<3>  | IPC44<14:12> |  |

| Reserved                          | 188-253 | 180-245 | 0x00017C-0x0001FE | _                      | _         | _            |  |

#### TABLE 7-1: INTERRUPT VECTOR DETAILS (CONTINUED)

## 7.3 Interrupt Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 7.3.1 KEY RESOURCES

- "Interrupts" (DS70000600) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## 7.4 Interrupt Control and Status Registers

dsPIC33EPXXGS202 family devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON3

- INTCON4

- INTTREG

#### 7.4.1 INTCON1 THROUGH INTCON4

Global interrupt control functions are controlled from INTCON1, INTCON2, INTCON3 and INTCON4.

INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS), as well as the control and status flags for the processor trap sources.

The INTCON2 register controls external interrupt request signal behavior, contains the Global Interrupt Enable bit (GIE) and the Alternate Interrupt Vector Table Enable bit (AIVTEN).

INTCON3 contains the status flags for the Auxiliary PLL and DO stack overflow status trap sources.

The INTCON4 register contains the Software Generated Hard Trap Status bit (SGHT).

#### 7.4.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

## 7.4.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

#### 7.4.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt sources can be assigned to one of seven priority levels.

#### 7.4.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number (VECNUM<7:0>) and Interrupt Level bits (ILR<3:0>) fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP<2:0> bits in the first position of IPC0 (IPC0<2:0>).

## 7.4.6 STATUS/CONTROL REGISTERS

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers refer to "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual".

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-3 through Register 7-7 in the following pages.

## 9.0 POWER-SAVING FEATURES

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com)

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EPXXGS202 family devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of peripherals being clocked constitutes lower consumed power.

dsPIC33EPXXGS202 family devices can manage power consumption in four ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- · Software-Controlled Doze mode

- Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

#### EXAMPLE 9-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE ; Put the device into Sleep mode

PWRSAV #IDLE\_MODE ; Put the device into Idle mode

### 9.1 Clock Frequency and Clock Switching

The dsPIC33EPXXGS202 family devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSCx bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 8.0 "Oscillator Configuration"**.

### 9.2 Instruction-Based Power-Saving Modes

The dsPIC33EPXXGS202 family devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 9-1.

**Note:** SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

| U-0           | U-0                                    | R/W-0                                | R/W-0    | R/W-0            | U-0            | R/W-0           | U-0   |

|---------------|----------------------------------------|--------------------------------------|----------|------------------|----------------|-----------------|-------|

| —             | _                                      | T3MD                                 | T2MD     | T1MD             | —              | PWMMD           | —     |

| bit 15        |                                        |                                      |          |                  |                |                 | bit 8 |

| R/W-0         | U-0                                    | R/W-0                                | U-0      | R/W-0            | U-0            | U-0             | R/W-0 |

| I2C1MD        | _                                      | U1MD                                 | _        | SPI1MD           |                |                 | ADCMD |

| bit 7         |                                        |                                      |          |                  |                |                 | bit ( |

| Legend:       |                                        |                                      |          |                  |                |                 |       |

| R = Readable  | e bit                                  | W = Writable                         | bit      | U = Unimple      | mented bit, re | ad as '0'       |       |

| -n = Value at |                                        | '1' = Bit is set                     |          | '0' = Bit is cle |                | x = Bit is unkr | nown  |

|               | -                                      |                                      |          |                  |                |                 |       |

| bit 15-14     | Unimpleme                              | nted: Read as '                      | 0'       |                  |                |                 |       |

| bit 13        | T3MD: Time                             | er3 Module Disat                     | ole bit  |                  |                |                 |       |

|               |                                        | nodule is disable                    |          |                  |                |                 |       |

|               |                                        | nodule is enable                     |          |                  |                |                 |       |

| bit 12        | -                                      | r2 Module Disat<br>nodule is disable |          |                  |                |                 |       |

|               |                                        | nodule is disable                    |          |                  |                |                 |       |

| bit 11        | <b>T1MD:</b> Timer1 Module Disable bit |                                      |          |                  |                |                 |       |

|               | -                                      | nodule is disable                    |          |                  |                |                 |       |

|               | 0 = Timer1 n                           | nodule is enable                     | ed       |                  |                |                 |       |

| bit 10        | Unimpleme                              | nted: Read as '                      | 0'       |                  |                |                 |       |

| bit 9         | PWMMD: P                               | WM Module Disa                       | able bit |                  |                |                 |       |

|               |                                        | odule is disabled                    |          |                  |                |                 |       |

|               |                                        | odule is enabled                     |          |                  |                |                 |       |

| bit 8         | -                                      | nted: Read as '                      |          |                  |                |                 |       |

| bit 7         | -                                      | C1 Module Disat                      | ble bit  |                  |                |                 |       |

|               |                                        | dule is disabled                     |          |                  |                |                 |       |

| bit 6         |                                        | nted: Read as '                      | n'       |                  |                |                 |       |

| bit 5         | -                                      | T1 Module Disa                       |          |                  |                |                 |       |

| bit o         |                                        | module is disabl                     |          |                  |                |                 |       |

|               |                                        | module is enable                     |          |                  |                |                 |       |

| bit 4         | Unimplemented: Read as '0'             |                                      |          |                  |                |                 |       |

| bit 3         | SPI1MD: SPI1 Module Disable bit        |                                      |          |                  |                |                 |       |

|               |                                        | dule is disabled                     |          |                  |                |                 |       |

|               |                                        | odule is enabled                     |          |                  |                |                 |       |

| bit 2-1       | Unimplemented: Read as '0'             |                                      |          |                  |                |                 |       |

|               |                                        |                                      |          |                  |                |                 |       |

| bit 0         |                                        | DC Module Disat                      | ole bit  |                  |                |                 |       |

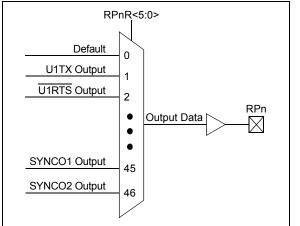

### 10.4.5 OUTPUT MAPPING

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 10-16 through Register 10-26). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 10-2 and Figure 10-3).

A null output is associated with the Output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

## 10.4.5.1 Mapping Limitations

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings across any or all of the RPn pins is possible. This includes both many-to-one and one-to-many mappings of peripheral inputs, and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

## TABLE 10-2: OUTPUT SELECTION FOR REMAPPABLE PINS (RPn)

| Function     | RPnR<5:0> | Output Name                                            |

|--------------|-----------|--------------------------------------------------------|

| Default PORT | 000000    | RPn tied to Default Pin                                |

| U1TX         | 000001    | RPn tied to UART1 Transmit                             |

| U1RTS/BCLK   | 000010    | RPn tied to UART1 Request-to-Send                      |

| SDO1         | 000101    | RPn tied to SPI1 Data Output                           |

| SCK1         | 000110    | RPn tied to SPI1 Clock Output                          |

| SS1          | 000111    | RPn tied to SPI1 Slave Select                          |

| OC1          | 010000    | RPn tied to Output Compare 1 Output                    |

| ACMP1        | 011000    | RPn tied to Analog Comparator 1 Output                 |

| ACMP2        | 011001    | RPn tied to Analog Comparator 2 Output                 |

| SYNCO1       | 101101    | RPn tied to PWM Primary Master Time Base Sync Output   |

| SYNCO2       | 101110    | RPn tied to PWM Secondary Master Time Base Sync Output |

NOTES:

NOTES:

### REGISTER 19-20: ADTRIGXL: ADC CHANNEL TRIGGER x SELECTION REGISTER LOW

(x = 0 to 3)

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0         | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|---------------|-------|-------|

|        |     | _   |       | TR    | GSRC(4x+1)<4  | :0>   |       |

| bit 15 |     |     |       |       |               |       | bit 8 |

|        |     |     |       |       |               |       |       |

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0         | R/W-0 | R/W-0 |

| _      |     | —   |       | TF    | RGSRC(4x)<4:0 | )>    |       |

| bit 7  |     |     |       |       |               |       | bit 0 |

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 15-13 Unimplemented: Read as '0'

| bit 12-8 | TRGSRC(4x+1)<4:0>: Trigger Source Selection for Corresponding Analog Inputs bits   |

|----------|------------------------------------------------------------------------------------|

|          | 11111 = ADTRG31                                                                    |

|          | 11110 = Reserved                                                                   |

|          | 11101 = Reserved                                                                   |

|          | 11100 = Reserved                                                                   |

|          | 11011 = Reserved                                                                   |

|          | 11010 = PWM Generator 3 current-limit trigger                                      |

|          | 11001 = PWM Generator 2 current-limit trigger                                      |

|          | 11000 = PWM Generator 1 current-limit trigger                                      |

|          | 10111 = Reserved                                                                   |

|          | 10110 = Output Compare 1 trigger                                                   |

|          | 10101 = Reserved                                                                   |

|          | 10100 = Reserved                                                                   |

|          | 10011 = Reserved                                                                   |

|          | 10010 = Reserved                                                                   |

|          | 10001 = PWM Generator 3 secondary trigger                                          |

|          | 10000 = PWM Generator 2 secondary trigger                                          |

|          | 01111 = PWM Generator 1 secondary trigger                                          |

|          | 01110 = PWM secondary Special Event Trigger                                        |

|          | 01101 = Timer2 period match                                                        |

|          | 01100 = Timer1 period match                                                        |

|          | 01011 = Reserved                                                                   |

|          | 01010 = Reserved                                                                   |

|          | 01001 = Reserved                                                                   |

|          | 01000 = Reserved                                                                   |

|          | 00111 = PWM Generator 3 primary trigger                                            |

|          | 00110 = PWM Generator 2 primary trigger<br>00101 = PWM Generator 1 primary trigger |

|          | 00100 = PWM Secial Event Trigger                                                   |

|          | 00011 = Reserved                                                                   |

|          | 00010 = Level software trigger                                                     |

|          | 00001 = Common software trigger                                                    |

|          | 00000 = No trigger is enabled                                                      |

| bit 7-5  | Unimplemented: Read as '0'                                                         |

| DIL 7-0  | Uninpienteu. Nedu as U                                                             |

## 21.2 PGA Resources

Many useful resources are provided on the main product page of the Microchip website for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 21.2.1 KEY RESOURCES

- "Programmable Gain Amplifier (PGA)" (DS70005146) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### **REGISTER 21-1: PGAxCON: PGAx CONTROL REGISTER (x = 1,2)**

| R/W-0  | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| PGAEN  | —   | SELPI2 | SELPI1 | SELPI0 | SELNI2 | SELNI1 | SELNI0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-----|-------|-------|-------|

| —     | —   | —   | -   | —   | GAIN2 | GAIN1 | GAIN0 |

| bit 7 |     |     |     |     |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15    | PGAEN: PGAx Enable bit                                  |

|-----------|---------------------------------------------------------|

|           | 1 = PGAx module is enabled                              |

|           | 0 = PGAx module is disabled (reduces power consumption) |

|           |                                                         |

| bit 14    | Unimplemented: Read as '0'                              |

| bit 13-11 | SELPI<2:0>: PGAx Positive Input Selection bits          |

|           | 111 = Reserved                                          |

|           | 110 = Reserved                                          |

|           | 101 = Reserved                                          |

|           | 100 = Reserved                                          |

|           | 011 = Reserved                                          |

|           | 010 = PGAxP3                                            |

|           | 001 = PGAxP2                                            |

|           | 000 = PGAxP1                                            |

| bit 10-8  | SELNI<2:0>: PGAx Negative Input Selection bits          |

|           | 111 = Reserved                                          |

|           | 110 = Reserved                                          |

|           | 101 = Reserved                                          |

|           | 100 = Reserved                                          |

|           | 011 = Ground (Single-Ended mode)                        |

|           | 010 = Reserved                                          |

|           | 001 = PGAxN2                                            |

|           | 000 = Ground (Single-Ended mode)                        |

| bit 7-3   | Unimplemented: Read as '0'                              |

## 25.1 DC Characteristics

#### TABLE 25-1: OPERATING MIPS vs. VOLTAGE

| Characteristic | naracteristic VDD Range Temperature Range<br>(in Volts) (in °C) |                 | Maximum MIPS            |

|----------------|-----------------------------------------------------------------|-----------------|-------------------------|

| Characteristic |                                                                 |                 | dsPIC33EPXXGS202 Family |

|                | 3.0V to 3.6V <sup>(1)</sup>                                     | -40°C to +85°C  | 70                      |

| —              | 3.0V to 3.6V <sup>(1)</sup>                                     | -40°C to +125°C | 60                      |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules (ADC, PGAs and comparators) may have degraded performance. Device functionality is tested but not characterized. Refer to Parameter BO10 in Table 25-13 for the minimum and maximum BOR values.

#### TABLE 25-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                      | Symbol | Min. | Тур.        | Max. | Unit |

|---------------------------------------------------------------------------------------------|--------|------|-------------|------|------|

| Industrial Temperature Devices                                                              |        |      |             |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40  |             | +125 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40  |             | +85  | °C   |

| Extended Temperature Devices                                                                |        |      |             |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40  |             | +140 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40  |             | +125 | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$ |        |      | Pint + Pi/c | D    | W    |

| I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$     |        |      |             |      |      |

| Maximum Allowed Power Dissipation                                                           | PDMAX  | (    | TJ — ΤΑ)/θ. | IA   | W    |

#### TABLE 25-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                           | Symbol | Тур. | Max. | Unit | Notes |

|------------------------------------------|--------|------|------|------|-------|

| Package Thermal Resistance, 28-Pin QFN-S | θJA    | 30.0 |      | °C/W | 1     |

| Package Thermal Resistance, 28-Pin UQFN  | θJA    | 26.0 | _    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SOIC  | θJA    | 69.7 | —    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SSOP  | θJA    | 71.0 | _    | °C/W | 1     |

Note 1: Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

| DC CH        | ARACTE | RISTICS                                 | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extende |                     |      |       |                                                                                                           |

|--------------|--------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-----------------------------------------------------------------------------------------------------------|

| Param<br>No. | Symbol | Characteristic                          | Min.                                                                                                                                                                                                       | Тур. <sup>(1)</sup> | Max. | Units | Conditions                                                                                                |

|              | lı∟    | Input Leakage Current <sup>(2,3)</sup>  |                                                                                                                                                                                                            |                     |      |       |                                                                                                           |

| DI50         |        | I/O Pins 5V Tolerant <sup>(4)</sup>     | -1                                                                                                                                                                                                         | —                   | +1   | μA    | $\label{eq:VSS} \begin{split} VSS \leq V PIN \leq V DD, \\ \text{pin at high-impedance} \end{split}$      |

| DI51         |        | I/O Pins Not 5V Tolerant <sup>(4)</sup> | -1                                                                                                                                                                                                         | —                   | +1   | μΑ    | Vss $\leq$ VPIN $\leq$ VDD,<br>pin at high-impedance,<br>-40°C $\leq$ TA $\leq$ +85°C                     |

| DI51a        |        | I/O Pins Not 5V Tolerant <sup>(4)</sup> | -1                                                                                                                                                                                                         | —                   | +1   | μA    | Analog pins shared with<br>external reference pins,<br>$-40^{\circ}C \le TA \le +85^{\circ}C$             |

| DI51b        |        | I/O Pins Not 5V Tolerant <sup>(4)</sup> | -1                                                                                                                                                                                                         | —                   | +1   | μA    | $Vss \le VPIN \le VDD$ ,<br>pin at high-impedance,<br>-40°C \le TA \le +125°C                             |

| DI51c        |        | I/O Pins Not 5V Tolerant <sup>(4)</sup> | -1                                                                                                                                                                                                         | —                   | +1   | μA    | Analog pins shared with<br>external reference pins,<br>$-40^{\circ}C \le TA \le +125^{\circ}C$            |

| DI55         |        | MCLR                                    | -5                                                                                                                                                                                                         | —                   | +5   | μA    | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                                  |

| DI56         |        | OSC1                                    | -5                                                                                                                                                                                                         | —                   | +5   | μA    | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ XT \text{ and } HS \text{ modes} \end{array}$ |

#### TABLE 25-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 5: VIL Source < (Vss 0.3). Characterized but not tested.

- **6:** VIH source > (VDD + 0.3) for non-5V tolerant pins only.

- 7: Digital 5V tolerant pins do not have an internal high side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

- 8: |Injection Currents| > 0 can affect the ADC results by approximately 4-6 counts.

- **9:** Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted, provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

## 25.2 AC Characteristics and Timing Parameters

This section defines the dsPIC33EPXXGS202 family AC characteristics and timing parameters.

#### TABLE 25-15: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)                                                                                                       |  |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| AC CHARACTERISTICS | $\begin{array}{ll} Operating \ temperature & -40^\circ C \leq TA \leq +85^\circ C \ for \ Industrial \\ -40^\circ C \leq TA \leq +125^\circ C \ for \ Extended \end{array}$ |  |  |  |  |

|                    | Operating voltage VDD range as described in Section 25.1 "DC Characteristics".                                                                                              |  |  |  |  |

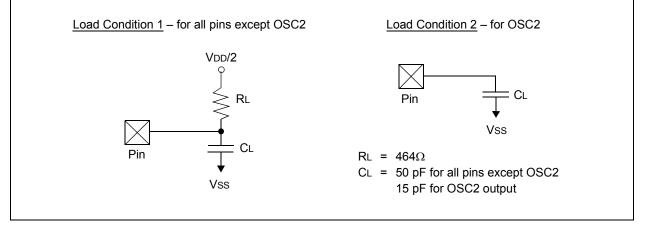

### FIGURE 25-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 25-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min. | Тур. | Max. | Units | Conditions                                                          |

|--------------|--------|-----------------------|------|------|------|-------|---------------------------------------------------------------------|

| DO50         | Cosco  | OSC2 Pin              | _    | —    | 15   |       | In XT and HS modes, when<br>external clock is used to drive<br>OSC1 |

| DO56         | Сю     | All I/O Pins and OSC2 | —    | —    | 50   | pF    | EC mode                                                             |

| DO58         | Св     | SCL1, SDA1            | _    | —    | 400  | pF    | In I <sup>2</sup> C mode                                            |

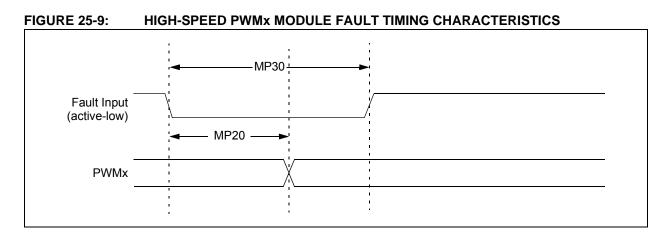

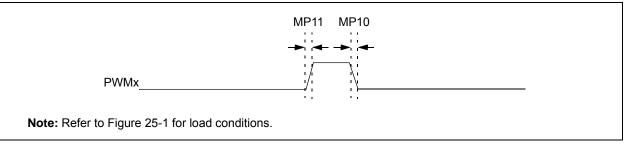

#### FIGURE 25-10: HIGH-SPEED PWMx MODULE TIMING CHARACTERISTICS

#### TABLE 25-30: HIGH-SPEED PWMx MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                     | (unless                         | rd Opera<br>otherwi<br>ng tempe | se stateo<br>rature - | <b>l)</b><br>∙40°C ≤ T. | 3.0V to 3.6V<br>A ≤ +85°C for Industrial<br>A ≤ +125°C for Extended |

|--------------------|--------|-------------------------------------|---------------------------------|---------------------------------|-----------------------|-------------------------|---------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>       | Min. Typ. Max. Units Conditions |                                 |                       |                         | Conditions                                                          |

| MP10               | TFPWM  | PWMx Output Fall Time               | —                               |                                 | —                     | ns                      | See Parameter DO32                                                  |

| MP11               | TRPWM  | PWMx Output Rise Time               | —                               | _                               | —                     | ns                      | See Parameter DO31                                                  |

| MP20               | Tfd    | Fault Input ↓ to PWMx<br>I/O Change | _                               | _                               | 15                    | ns                      |                                                                     |

| MP30               | Tfh    | Fault Input Pulse Width             | 15                              | —                               | —                     | ns                      |                                                                     |

**Note 1:** These parameters are characterized but not tested in manufacturing.

| Instruction Addressing Modes.       53         File Register Instructions       53         Fundamental Modes Supported.       53         MAC Instructions.       54         MCU Instructions       53         Move and Accumulator Instructions.       54         Other Instructions.       54 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction Set                                                                                                                                                                                                                                                                                |

| Overview                                                                                                                                                                                                                                                                                       |

| Summary251                                                                                                                                                                                                                                                                                     |

| Symbols Used in Opcode Descriptions                                                                                                                                                                                                                                                            |

| Instruction-Based Power-Saving Modes                                                                                                                                                                                                                                                           |

| Idle                                                                                                                                                                                                                                                                                           |

| Sleep                                                                                                                                                                                                                                                                                          |

| Inter-Integrated Circuit (I <sup>2</sup> C)                                                                                                                                                                                                                                                    |

| Control Registers 187                                                                                                                                                                                                                                                                          |

| Resources185                                                                                                                                                                                                                                                                                   |

| Inter-Integrated Circuit. See I <sup>2</sup> C.                                                                                                                                                                                                                                                |

| Internet Address                                                                                                                                                                                                                                                                               |

| Interrupt Controller                                                                                                                                                                                                                                                                           |

| Alternate Interrupt Vector Table (AIVT)73                                                                                                                                                                                                                                                      |

| Control and Status Registers78                                                                                                                                                                                                                                                                 |

| INTCON178                                                                                                                                                                                                                                                                                      |

| INTCON278                                                                                                                                                                                                                                                                                      |

| INTCON378                                                                                                                                                                                                                                                                                      |

| INTCON478                                                                                                                                                                                                                                                                                      |

| INTTREG78                                                                                                                                                                                                                                                                                      |

| Interrupt Vector Details76                                                                                                                                                                                                                                                                     |

| Interrupt Vector Table (IVT)73                                                                                                                                                                                                                                                                 |

| Reset Sequence73                                                                                                                                                                                                                                                                               |

| Resources78                                                                                                                                                                                                                                                                                    |

| Interrupts Coincident with Power Save Instructions 100                                                                                                                                                                                                                                         |

| .I                                                                                                                                                                                                                                                                                             |

#### J

| JTAG Boundary Scan Interface | 239 |

|------------------------------|-----|

| JTAG Interface               | 248 |

| 1                            |     |

#### L Le

| Leading-Edge Blanking (LEB)15 | 51 |

|-------------------------------|----|

| LPRC Oscillator               |    |

| Use with WDT 24               | 7  |

#### Μ

| Memory Organization                         | 27  |

|---------------------------------------------|-----|

| Resources                                   | 33  |

| Microchip Internet Web Site                 | 338 |

| Modulo Addressing                           | 55  |

| Applicability                               |     |

| Operation Example                           | 55  |

| Start and End Address                       |     |

| W Address Register Selection                |     |

| MPLAB Assembler, Linker, Librarian          |     |

| MPLAB ICD 3 In-Circuit Debugger             |     |

| MPLAB PM3 Device Programmer                 |     |

| MPLAB REAL ICE In-Circuit Emulator System   |     |

| MPLAB X Integrated Development              |     |

| Environment Software                        |     |

| MPLINK Object Linker/MPLIB Object Librarian |     |

| •                                           |     |

## **O**

| Oscillator        |    |

|-------------------|----|

| Control Registers | 91 |

| Resources         |    |

| OTP Memory Area   |    |

| Output Compare    |    |

| Control Registers |    |

| Resources         |    |

|                   |    |

#### Ρ

| •                                       |     |

|-----------------------------------------|-----|

| Packaging                               | 315 |

| Details                                 | 316 |

| Marking                                 | 315 |

| Peripheral Module Disable (PMD)         | 101 |

| Peripheral Pin Select (PPS)             | 109 |

| Available Peripherals                   | 109 |

| Available Pins                          | 109 |

| Control                                 | 109 |

| Control Registers                       | 115 |

| Input Mapping                           | 110 |

| Output Mapping                          | 112 |

| Output Selection for Remappable Pins    | 112 |

| Selectable Input Sources                | 111 |

| Peripheral Pin Select. See PPS.         |     |

| PICkit 3 In-Circuit Debugger/Programmer |     |

| Pinout I/O Descriptions (table)         | 8   |

| Power-Saving Features                   |     |

| Clock Frequency and Switching           | 99  |

| Control Registers                       | 102 |

| Resources                               | 101 |

| Program Address Space                   | 27  |

| Construction                            | 58  |

| Data Access from Program Memory Using   |     |

| Table Instructions                      | 59  |

| Memory Map (dsPIC33EP16GS202 Devices)   |     |

| Memory Map (dsPIC33EP32GS202 Devices)   | 29  |

| Table Read High Instructions (TBLRDH)   | 59  |

| Table Read Low Instructions (TBLRDL)    | 59  |

| Program Memory                          |     |

| Organization                            | 30  |

| Reset Vector                            |     |

| Programmable Gain Amplifier (PGA)       | 235 |

| Control Registers                       | 237 |

| Description                             | 236 |

| Resources                               | 237 |

| Programmable Gain Amplifier. See PGA.   |     |

| Programmer's Model                      |     |

| Register Descriptions                   | 19  |

| Pulse-Width Modulation. See PWM.        |     |

|                                         |     |

## R

| Register Maps                |    |

|------------------------------|----|

| ADC                          | 43 |

| Analog Comparator            | 47 |

| CPU Core                     | 34 |

| I2C1                         | 42 |

| Input Capture 1              | 38 |

| Interrupt Controller         |    |

| NVM                          | 46 |

| Output Compare 1             | 38 |

| Peripheral Pin Select Output |    |

| PMD                          |    |

| PORTA                        | 48 |

| PORTB                        | 48 |

| Programmable Gain Amplifier  | 47 |

| PWM                          | 39 |

| PWM Generator 1              | 39 |

| PWM Generator 2              | 40 |

| PWM Generator 3              | 41 |

| SPI1                         | 42 |

| System Control               | 46 |

| Timer1 through Timer3        | 38 |

| UART1                        | 42 |

|                              |    |

© 2015-2016 Microchip Technology Inc.