Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 2K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

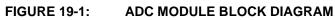

| Data Converters            | A/D 12x12b, 2x12b                                                                |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-UQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-UQFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep16gs202t-e-mx |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 3 MHz < FIN < 5.5 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLDBF to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

## 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic-low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins and drive the output to logic low.

## 2.9 Targeted Applications

- Power Factor Correction (PFC)

- Interleaved PFC

- Critical Conduction PFC

- Bridgeless PFC

- DC/DC Converters

- Buck, Boost, Forward, Flyback, Push-Pull

- Half/Full-Bridge

- Phase-Shift Full-Bridge

- Resonant Converters

- DC/AC

- Half/Full-Bridge Inverter

- Resonant Inverter

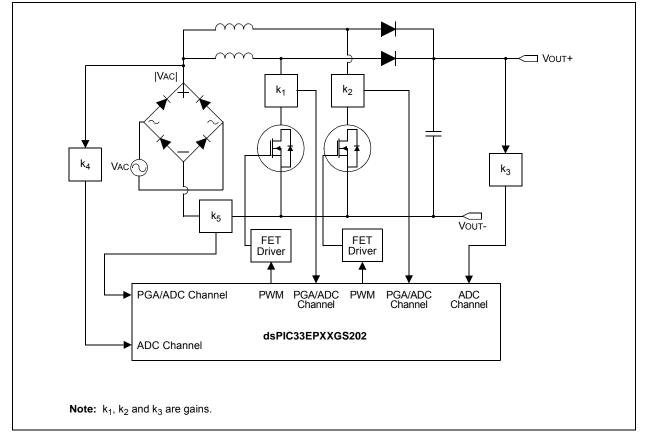

Examples of typical application connections are shown in Figure 2-4 through Figure 2-6.

### FIGURE 2-4: INTERLEAVED PFC

### 4.3.5 X AND Y DATA SPACES

The dsPIC33EPXXGS202 core has two Data Spaces, X and Y. These Data Spaces can be considered either separate (for some DSP instructions) or as one unified linear address range (for MCU instructions). The Data Spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms, such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X Data Space is used by all instructions and supports all addressing modes. X Data Space has separate read and write data buses. The X read data bus is the read data path for all instructions that view Data Space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y Data Space is used in concert with the X Data Space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y Data Spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X Data Space.

All data memory writes, including in DSP instructions, view Data Space as combined X and Y address space. The boundary between the X and Y Data Spaces is device-dependent and is not user-programmable.

## 4.4 Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 4.4.1 KEY RESOURCES

- "dsPIC33E/PIC24E Program Memory" (DS70000613) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

### TABLE 4-4: TIMER1 THROUGH TIMER3 REGISTER MAP

| File<br>Name | Addr. | Bit 15 | Bit 14            | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8         | Bit 7        | Bit 6      | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|-------------------|--------|--------|--------|--------|--------------|---------------|--------------|------------|--------|--------|-------|-------|-------|-------|---------------|

| TMR1         | 0100  |        |                   |        |        |        |        |              | Timer1        | Register     |            |        |        |       |       |       |       | xxxx          |

| PR1          | 0102  |        | Period Register 1 |        |        |        |        |              |               |              |            |        |        | FFFF  |       |       |       |               |

| T1CON        | 0104  | TON    | —                 | TSIDL  | _      | —      | _      | —            | —             | _            | TGATE      | TCKPS1 | TCKPS0 | _     | TSYNC | TCS   | —     | 0000          |

| TMR2         | 0106  |        | Timer2 Register   |        |        |        |        |              |               |              |            |        | xxxx   |       |       |       |       |               |

| TMR3HLD      | 0108  |        |                   |        |        |        | Time   | r3 Holding F | Register (for | 32-bit timer | operations | only)  |        |       |       |       |       | xxxx          |

| TMR3         | 010A  |        |                   |        |        |        |        |              | Timer3        | Register     |            |        |        |       |       |       |       | xxxx          |

| PR2          | 010C  |        |                   |        |        |        |        |              | Period R      | egister 2    |            |        |        |       |       |       |       | FFFF          |

| PR3          | 010E  |        |                   |        |        |        |        |              | Period R      | egister 3    |            |        |        |       |       |       |       | FFFF          |

| T2CON        | 0110  | TON    | —                 | TSIDL  | _      | —      | _      | —            | —             | _            | TGATE      | TCKPS1 | TCKPS0 | T32   | —     | TCS   | —     | 0000          |

| T3CON        | 0112  | TON    | _                 | TSIDL  | _      | —      | _      | —            | _             | _            | TGATE      | TCKPS1 | TCKPS0 | _     | —     | TCS   | _     | 0000          |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-5: INPUT CAPTURE 1 REGISTER MAP

| File<br>Name | Addr. | Bit 15 | Bit 14                          | Bit 13 | Bit 12  | Bit 11  | Bit 10  | Bit 9 | Bit 8 | Bit 7  | Bit 6    | Bit 5 | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------|--------|---------------------------------|--------|---------|---------|---------|-------|-------|--------|----------|-------|----------|----------|----------|----------|----------|---------------|

| IC1CON1      | 0140  | _      | _                               | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | —     | _     | —      | ICI1     | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC1CON2      | 0142  | _      | —                               | _      | _       | -       | _       |       | _     | ICTRIG | TRIGSTAT | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC1BUF       | 0144  |        | Input Capture 1 Buffer Register |        |         |         |         |       |       |        |          |       |          | xxxx     |          |          |          |               |

| IC1TMR       | 0146  |        | Input Capture 1 Timer Register  |        |         |         |         |       |       |        |          |       |          | 0000     |          |          |          |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-6: OUTPUT COMPARE 1 REGISTER MAP

| File<br>Name | Addr. | Bit 15 | Bit 14                 | Bit 13   | Bit 12  | Bit 11  | Bit 10  | Bit 9 | Bit 8     | Bit 7       | Bit 6       | Bit 5  | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------|--------|------------------------|----------|---------|---------|---------|-------|-----------|-------------|-------------|--------|----------|----------|----------|----------|----------|---------------|

| OC1CON1      | 0900  |        | _                      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _     |           | ENFLTA      | _           |        | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC1CON2      | 0902  | FLTMD  | FLTOUT                 | FLTTRIEN | OCINV   | _       | —       | —     | —         | OCTRIG      | TRIGSTAT    | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC1RS        | 0904  |        |                        |          |         |         |         | 0     | utput Com | pare 1 Seco | ndary Regis | ter    |          |          |          |          |          | xxxx          |

| OC1R         | 0906  |        |                        |          |         |         |         |       | Output    | Compare 1   | Register    |        |          |          |          |          |          | xxxx          |

| OC1TMR       | 0908  |        | Timer Value 1 Register |          |         |         |         |       |           |             |             |        | xxxx     |          |          |          |          |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## **REGISTER 6-1:** RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

| bit 3 | <b>SLEEP:</b> Wake-up from Sleep Flag bit<br>1 = Device has been in Sleep mode<br>0 = Device has not been in Sleep mode |

|-------|-------------------------------------------------------------------------------------------------------------------------|

| bit 2 | IDLE: Wake-up from Idle Flag bit                                                                                        |

|       | <ol> <li>1 = Device has been in Idle mode</li> <li>0 = Device has not been in Idle mode</li> </ol>                      |

| bit 1 | BOR: Brown-out Reset Flag bit                                                                                           |

|       | <ul><li>1 = A Brown-out Reset has occurred</li><li>0 = A Brown-out Reset has not occurred</li></ul>                     |

| bit 0 | POR: Power-on Reset Flag bit                                                                                            |

|       | <ul><li>1 = A Power-on Reset has occurred</li><li>0 = A Power-on Reset has not occurred</li></ul>                       |

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the WDTEN<1:0> Configuration bits are '11' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| R/W-1        | R/W-0                                                                | R/W-0                               | U-0      | U-0                               | U-0              | U-0             | R/W-0          |  |  |  |  |  |  |

|--------------|----------------------------------------------------------------------|-------------------------------------|----------|-----------------------------------|------------------|-----------------|----------------|--|--|--|--|--|--|

| GIE          | DISI                                                                 | SWTRAP                              |          | —                                 | —                | —               | AIVTEN         |  |  |  |  |  |  |

| bit 15       |                                                                      |                                     |          |                                   |                  |                 | bit 8          |  |  |  |  |  |  |

|              |                                                                      |                                     |          |                                   | <b>D11</b> (0)   | <b>D</b> 444 0  | <b>D</b> 444 A |  |  |  |  |  |  |

| U-0          | U-0                                                                  | U-0                                 | U-0      | U-0                               | R/W-0            | R/W-0           | R/W-0          |  |  |  |  |  |  |

|              |                                                                      | —                                   |          |                                   | INT2EP           | INT1EP          | INT0EP         |  |  |  |  |  |  |

| bit 7        |                                                                      |                                     |          |                                   |                  |                 | bit (          |  |  |  |  |  |  |

| Legend:      |                                                                      |                                     |          |                                   |                  |                 |                |  |  |  |  |  |  |

| R = Readab   | le bit                                                               | W = Writable b                      | bit      | U = Unimpler                      | mented bit, read | as '0'          |                |  |  |  |  |  |  |

| -n = Value a | t POR                                                                | '1' = Bit is set                    |          | '0' = Bit is cle                  | ared             | x = Bit is unki | nown           |  |  |  |  |  |  |

|              |                                                                      |                                     |          |                                   |                  |                 |                |  |  |  |  |  |  |

| bit 15       |                                                                      | nterrupt Enable                     |          |                                   |                  |                 |                |  |  |  |  |  |  |

|              |                                                                      | and associated                      |          |                                   |                  |                 |                |  |  |  |  |  |  |

| L:1 4 4      |                                                                      | are disabled, b                     | •        | still enabled                     |                  |                 |                |  |  |  |  |  |  |

| bit 14       |                                                                      | nstruction Status                   |          |                                   |                  |                 |                |  |  |  |  |  |  |

|              | 1 = DISI instruction is active<br>0 = DISI instruction is not active |                                     |          |                                   |                  |                 |                |  |  |  |  |  |  |

| bit 13       | SWTRAP: Se                                                           | oftware Trap Sta                    | atus bit |                                   |                  |                 |                |  |  |  |  |  |  |

|              |                                                                      | trap is enabled                     |          |                                   |                  |                 |                |  |  |  |  |  |  |

|              |                                                                      | trap is disabled                    |          |                                   |                  |                 |                |  |  |  |  |  |  |

| bit 12-9     | -                                                                    | ted: Read as '                      |          |                                   |                  |                 |                |  |  |  |  |  |  |

| bit 8        |                                                                      | ernate Interrupt                    |          |                                   |                  |                 |                |  |  |  |  |  |  |

|              |                                                                      | ernate Interrupt                    |          |                                   |                  |                 |                |  |  |  |  |  |  |

| bit 7-3      |                                                                      | ted: Read as '(                     |          |                                   |                  |                 |                |  |  |  |  |  |  |

| bit 2        |                                                                      | ernal Interrupt 2                   |          | t Polarity Selec                  | t bit            |                 |                |  |  |  |  |  |  |

|              |                                                                      | on negative edg                     |          |                                   |                  |                 |                |  |  |  |  |  |  |

|              | •                                                                    | on positive edge                    |          |                                   |                  |                 |                |  |  |  |  |  |  |

| bit 1        |                                                                      | ernal Interrupt 1                   | •        | t Polarity Selec                  | t bit            |                 |                |  |  |  |  |  |  |

|              |                                                                      | on negative edg<br>on positive edge |          |                                   |                  |                 |                |  |  |  |  |  |  |

| bit 0        | •                                                                    | ernal Interrupt 0                   |          | t Polarity Selec                  | t bit            |                 |                |  |  |  |  |  |  |

|              |                                                                      | on negative edg                     | •        | · <b>,</b> · <b>,</b> - · · · · · | -                |                 |                |  |  |  |  |  |  |

|              |                                                                      |                                     |          |                                   |                  |                 |                |  |  |  |  |  |  |

### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

### 10.7 Peripheral Pin Select Registers

### REGISTER 10-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

|        |       |       | INT1R | <7:0> |       |       |       |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| U-0    | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   |

| —      | —     | —     | —     | —     | —     | —     | —     |

| bit 7  | ·     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-8 INT1R<7:0>: Assign External Interrupt 1 (INT1) to the Corresponding RPn Pin bits 10110101 = Input tied to RP181 10110100 = Input tied to RP180 . . 00000001 = Input tied to RP1 00000000 = Input tied to Vss

bit 7-0 Unimplemented: Read as '0'

### REGISTER 10-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0          | U-0        | U-0              | U-0            | U-0              | U-0              | U-0             | U-0   |

|--------------|------------|------------------|----------------|------------------|------------------|-----------------|-------|

|              | —          | —                | _              | —                | —                | —               | _     |

| bit 15       |            |                  |                |                  |                  | •<br>•          | bit 8 |

|              |            |                  |                |                  |                  |                 |       |

| R/W-0        | R/W-0      | R/W-0            | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

|              |            |                  | INT2           | R<7:0>           |                  |                 |       |

| bit 7        |            |                  |                |                  |                  |                 | bit 0 |

|              |            |                  |                |                  |                  |                 |       |

| Legend:      |            |                  |                |                  |                  |                 |       |

| R = Readab   | ole bit    | W = Writable     | bit            | U = Unimpler     | mented bit, read | d as '0'        |       |

| -n = Value a | at POR     | '1' = Bit is set | t              | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|              |            |                  |                |                  |                  |                 |       |

| bit 15-8     | Unimpleme  | nted: Read as '  | 0'             |                  |                  |                 |       |

| bit 7-0      | INT2R<7:0> | : Assign Extern  | al Interrupt 2 | (INT2) to the C  | orresponding R   | Pn Pin bits     |       |

|              |            | Input tied to R  | -              | . ,              |                  |                 |       |

|              |            | Input tied to R  |                |                  |                  |                 |       |

|              | •          | ·                |                |                  |                  |                 |       |

|              | •          |                  |                |                  |                  |                 |       |

|              | •          |                  |                |                  |                  |                 |       |

|              | 00000001 = | Input tied to R  | P1             |                  |                  |                 |       |

|              |            |                  |                |                  |                  |                 |       |

00000000 = Input tied to Vss

| R/W-0           | R/W-0                                                               | R/W-0                                                                                                             | R/W-0                                       | R/W-0            | R/W-0            | R/W-0              | R/W-0    |  |

|-----------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------------|------------------|--------------------|----------|--|

| SCK1INR7        | SCK1INR6                                                            | SCK1INR5                                                                                                          | SCK1INR4                                    | SCK1INR3         | SCK1INR2         | SCK1INR1           | SCK1INR0 |  |

| bit 15          |                                                                     |                                                                                                                   |                                             |                  |                  |                    | bit 8    |  |

|                 |                                                                     |                                                                                                                   |                                             |                  |                  |                    |          |  |

| R/W-0           | R/W-0                                                               | R/W-0                                                                                                             | R/W-0                                       | R/W-0            | R/W-0            | R/W-0              | R/W-0    |  |

| SDI1R7          | SDI1R6                                                              | SDI1R5                                                                                                            | SDI1R4                                      | SDI1R3           | SDI1R2           | SDI1R1             | SDI1R0   |  |

| bit 7           |                                                                     |                                                                                                                   |                                             |                  |                  |                    | bit 0    |  |

| Legend:         |                                                                     |                                                                                                                   |                                             |                  |                  |                    |          |  |

| R = Readable    | bit                                                                 | W = Writable                                                                                                      | bit                                         | U = Unimpler     | nented bit, read | as '0'             |          |  |

| -n = Value at F | POR                                                                 | '1' = Bit is set                                                                                                  |                                             | '0' = Bit is cle | ared             | x = Bit is unknown |          |  |

| bit 7-0         | 10110100 =<br>00000001 =<br>00000000 =<br>SDI1R<7:0>:<br>10110101 = | Input tied to RF<br>Input tied to RF<br>Input tied to Vs<br>Assign SPI1 D<br>Input tied to RF<br>Input tied to RF | 2180<br>21<br>55<br>Pata Input (SDI<br>2181 | 11) to the Corre | esponding RPn    | Pin bits           |          |  |

|                 |                                                                     | Input tied to RF<br>Input tied to Vs                                                                              |                                             |                  |                  |                    |          |  |

### REGISTER 10-10: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

| U-0    | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| _      | _   | RP177R5 | RP177R4 | RP177R3 | RP177R2 | RP177R1 | RP177R0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

|        |     |         |         |         |         |         |         |

| U-0    | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

### REGISTER 10-24: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | RP176R5 | RP176R4 | RP176R3 | RP176R2 | RP176R1 | RP176R0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP177R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP177 Output Pin bits (see Table 10-2 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                                 |

| bit 5-0   | <b>RP176R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP176 Output Pin bits (see Table 10-2 for peripheral function numbers) |

### REGISTER 10-25: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0    | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |  |

|--------|-----|---------|---------|---------|---------|---------|---------|--|

| —      | —   | RP179R5 | RP179R4 | RP179R3 | RP179R2 | RP179R1 | RP179R0 |  |

| bit 15 |     |         |         |         |         |         | bit 8   |  |

| U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | RP178R5 | RP178R4 | RP178R3 | RP178R2 | RP178R1 | RP178R0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP179R<5:0>:** Peripheral Output Function is Assigned to RP179 Output Pin bits (see Table 10-2 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0' bit 5-0 RP178R<5:0>: Peripheral Output Function is

bit 5-0 **RP178R<5:0>:** Peripheral Output Function is Assigned to RP178 Output Pin bits (see Table 10-2 for peripheral function numbers)

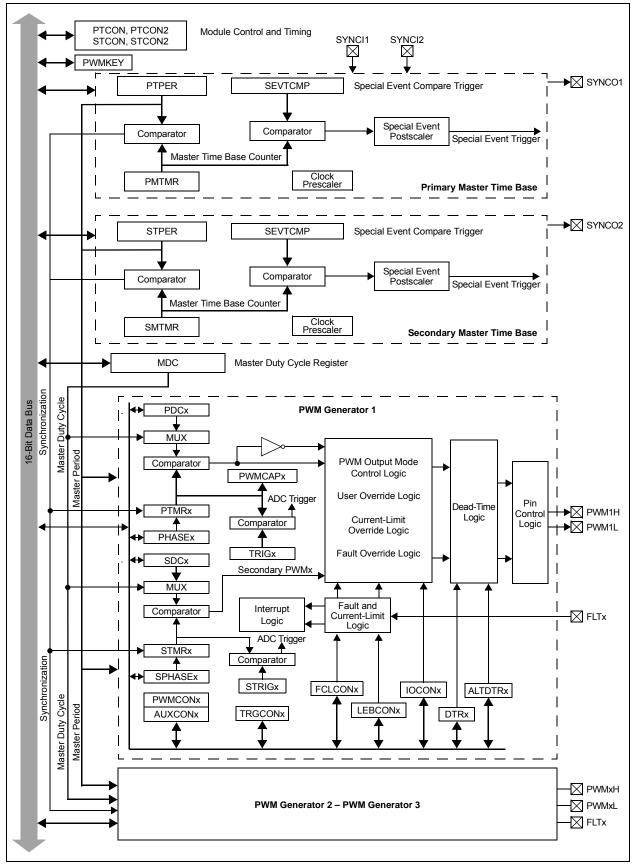

#### FIGURE 15-2: SIMPLIFIED CONCEPTUAL BLOCK DIAGRAM OF THE HIGH-SPEED PWM

### REGISTER 15-1: PTCON: PWM TIME BASE CONTROL REGISTER (CONTINUED)

10001 = 12 Postscaler generates a Special Event Trigger on every second compare match event 0000 = 1:1 Postscaler generates a Special Event Trigger on every compare match event

**Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCIx feature, the user application must program the Period register with a value that is slightly larger than the expected period of the external synchronization input signal.

### REGISTER 15-2: PTCON2: PWM CLOCK DIVIDER SELECT REGISTER 2

| U-0                                                                  | U-0       | U-0              | U-0 | U-0              | U-0   | U-0             | U-0   |

|----------------------------------------------------------------------|-----------|------------------|-----|------------------|-------|-----------------|-------|

| —                                                                    | —         | —                |     | _                | —     | _               | —     |

| bit 15                                                               |           |                  |     |                  |       |                 | bit 8 |

|                                                                      |           |                  |     |                  |       |                 |       |

| U-0                                                                  | U-0       | U-0              | U-0 | U-0              | R/W-0 | R/W-0           | R/W-0 |

| _                                                                    | PCLKDIV<2 |                  |     |                  |       |                 | )     |

| bit 7                                                                |           |                  |     |                  |       |                 | bit 0 |

|                                                                      |           |                  |     |                  |       |                 |       |

| Legend:                                                              |           |                  |     |                  |       |                 |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |           |                  |     |                  |       | 1 as '0'        |       |

| -n = Value at PO                                                     | R         | '1' = Bit is set |     | '0' = Bit is cle | ared  | x = Bit is unkr | iown  |

bit 15-3 Unimplemented: Read as '0'

bit 2-0 PCLKDIV<2:0>: PWM Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

111 = Reserved

110 = Divide-by-64, maximum PWM timing resolution

101 = Divide-by-32, maximum PWM timing resolution

- 100 = Divide-by-16, maximum PWM timing resolution

- 011 = Divide-by-8, maximum PWM timing resolution

- 010 = Divide-by-4, maximum PWM timing resolution

- 001 = Divide-by-2, maximum PWM timing resolution

- 000 = Divide-by-1, maximum PWM timing resolution (power-on default)

**Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

## REGISTER 15-26: AUXCONX: PWMx AUXILIARY CONTROL REGISTER

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                              | U-0                                                                                                                | U-0                                                | R/W-0                     | R/W-0           | R/W-0           | R/W-0     |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------------|-----------------|-----------------|-----------|--|--|--|

| HRPDIS          | HRDDIS                                                                                                                                                                                                                                                                                                                                                                                                                             | _                                                                                                                  | —                                                  | BLANKSEL3                 | BLANKSEL2       | BLANKSEL1       | BLANKSEL0 |  |  |  |

| bit 15          |                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                    |                                                    |                           |                 |                 | bit 8     |  |  |  |

| U-0             | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-0                                                                                                              | R/W-0                                              | R/W-0                     | R/W-0           | R/W-0           | R/W-0     |  |  |  |

| _               | _                                                                                                                                                                                                                                                                                                                                                                                                                                  | CHOPSEL3                                                                                                           | CHOPSEL2                                           | CHOPSEL1                  | CHOPSEL0        | CHOPHEN         | CHOPLEN   |  |  |  |

| bit 7           |                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                    |                                                    |                           |                 |                 | bit 0     |  |  |  |

| r               |                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                    |                                                    |                           |                 |                 |           |  |  |  |

| Legend:         |                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                    |                                                    |                           |                 |                 |           |  |  |  |

| R = Readable    |                                                                                                                                                                                                                                                                                                                                                                                                                                    | W = Writable                                                                                                       |                                                    | •                         | ented bit, read |                 |           |  |  |  |

| -n = Value at P | 'UR                                                                                                                                                                                                                                                                                                                                                                                                                                | '1' = Bit is set                                                                                                   |                                                    | '0' = Bit is clea         | ired            | x = Bit is unkn | iown      |  |  |  |

| bit 15          | 1 = High-reso<br>0 = High-reso                                                                                                                                                                                                                                                                                                                                                                                                     | lution PWMx p                                                                                                      | eriod is disabl<br>eriod is enable                 | ed to reduce po<br>ed     | ower consumpt   | ion             |           |  |  |  |

| bit 14          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                  | h-Resolution P                                                                                                     |                                                    |                           |                 |                 |           |  |  |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                    | lution PWMx d<br>lution PWMx d                                                                                     |                                                    | sabled to reduc<br>nabled | e power consu   | mption          |           |  |  |  |

| bit 13-12       | -                                                                                                                                                                                                                                                                                                                                                                                                                                  | ted: Read as '                                                                                                     |                                                    |                           |                 |                 |           |  |  |  |

| bit 11-8        | •                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                    |                                                    | urce Select bits          |                 |                 |           |  |  |  |

|                 | 1001 = Reset<br>1000 = Reset<br>0111 = Reset<br>0101 = Reset<br>0100 = Reset<br>0011 = PWM<br>0010 = PWM<br>0001 = PWM                                                                                                                                                                                                                                                                                                             | rved<br>rved<br>rved<br>rved<br>rved<br>rved<br>3H is selected<br>2H is selected<br>1H is selected<br>ate blanking | as the state b<br>as the state b<br>as the state b | lank source               | gister).        |                 |           |  |  |  |

| bit 7-6         | -                                                                                                                                                                                                                                                                                                                                                                                                                                  | ted: Read as '                                                                                                     |                                                    |                           |                 |                 |           |  |  |  |

| bit 5-2         |                                                                                                                                                                                                                                                                                                                                                                                                                                    | :0>: PWMx Ch                                                                                                       | -                                                  |                           |                 |                 |           |  |  |  |

|                 | The selected signal will enable and disable (chop) the selected PWMx outputs.<br>1001 = Reserved<br>1000 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0101 = Reserved<br>0100 = Reserved<br>0011 = PWM3H is selected as the chop clock source<br>0010 = PWM2H is selected as the chop clock source<br>0001 = PWM1H is selected as the chop clock source<br>0000 = Chop clock generator is selected as the chop clock source |                                                                                                                    |                                                    |                           |                 |                 |           |  |  |  |

| bit 1           | 1 = PWMxH c                                                                                                                                                                                                                                                                                                                                                                                                                        | WMxH Output<br>hopping function                                                                                    | on is enabled                                      | able bit                  |                 |                 |           |  |  |  |

| bit 0           | CHOPLEN: P<br>1 = PWMxL c                                                                                                                                                                                                                                                                                                                                                                                                          | WMxL Output<br>hopping function<br>hopping function                                                                | Chopping Ena<br>on is enabled                      | able bit                  |                 |                 |           |  |  |  |

NOTES:

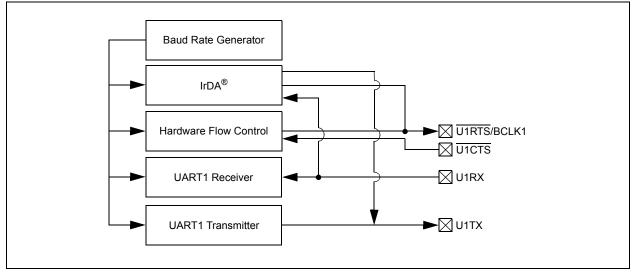

## 18.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXGS202 family of devices contains one UART module.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EPXXGS202 device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the U1CTS and U1RTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UART1 module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the U1TX and U1RX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with U1CTS and U1RTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps in 16x mode at 60 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps in 4x mode at 60 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for all UART1 Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- Support for Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UART1 module is shown in Figure 18-1. The UART1 module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

### FIGURE 18-1: UART1 SIMPLIFIED BLOCK DIAGRAM

## TABLE 22-1: CONFIGURATION REGISTER MAP

| Name    | Address | Device<br>Memory Size<br>(Kbytes) | Bits 23-16 | Bit 15                  | Bit 14    | Bit 13    | Bit 12       | Bit 11 | Bit 10   | Bit 9 | Bit 8    | Bit 7                   | Bit 6 | Bit 5      | Bit 4      | Bit 3 | Bit 2                   | Bit 1     | Bit 0                   |   |   |   |

|---------|---------|-----------------------------------|------------|-------------------------|-----------|-----------|--------------|--------|----------|-------|----------|-------------------------|-------|------------|------------|-------|-------------------------|-----------|-------------------------|---|---|---|

| FSEC    | 002B80  | 16                                |            | AIVTDIS                 | _         | _         | _            | C      | SS <2:0> |       | CWRP     | GSS <1                  | .0>   | GWRP       | _          | BSEN  | BSS <1:                 | 05        | BWRP                    |   |   |   |

| FSEC    | 005780  | 32                                | _          | AIVIDIS                 |           |           |              | ن<br>ا | 55 ~2.0- | -     | CWRF     | 655 ~1                  | .0    | GWRF       | _          | DOEN  | 600 1.                  | 0-        | DWKF                    |   |   |   |

| FBSLIM  | 002B90  | 16                                |            |                         |           |           | BSLIM <12:0> |        |          |       |          |                         |       |            |            |       |                         |           |                         |   |   |   |

| FDOLIN  | 005790  | 32                                |            |                         |           |           |              |        |          |       |          |                         | DOLIN | 1<12.02    |            |       |                         |           |                         |   |   |   |

| FSIGN   | 002B94  | 16                                |            | Reserved <sup>(2)</sup> |           |           |              |        |          |       |          |                         |       |            |            |       |                         |           |                         |   |   |   |

| FSIGN   | 005794  | 32                                | _          | Keserved(2)             | Reserved- | Reserved- | Neserved.    | _      | _        | _     | —        | _                       | —     | _          | _          | —     | _                       | _         | _                       | _ | _ | _ |

| FOSCSEL | 002B98  | 16                                |            |                         |           |           | T1000.000    |        |          |       |          | .0.                     |       |            |            |       |                         |           |                         |   |   |   |

| FUSUSEL | 005798  | 32                                | _          | _                       | _         | _         | _            | _      | _        | —     | _        | IESO                    |       | _          | _          | _     | FNOSC<2:0>              |           | .0>                     |   |   |   |

| FOSC    | 002B9C  | 16                                |            |                         |           |           |              |        |          |       |          | FOKOM                   | 4.05  |            |            |       |                         | DOO       |                         |   |   |   |

| FUSC    | 00579C  | 32                                | _          | _                       | _         | _         | _            |        | _        | -     | PLLKEN   | FCKSM<                  | -1:0> | IOL1WAY    | _          | _     | OSCIOFNC                | P05       | CMD<1:0>                |   |   |   |

| FWDT    | 002BA0  | 16                                |            |                         |           |           |              |        |          |       |          |                         | WDT   |            | WDTDDE     |       |                         |           |                         |   |   |   |

| FWDI    | 0057A0  | 32                                | —          | _                       | _         | _         | _            | _      | —        | VVDIV | VIN<1:0> | WINDIS                  | VVDTE | EN<1:0>    | WDTPRE     |       | WDTPOS                  | 51 < 3:02 | >                       |   |   |   |

| FPOR    | 002BA4  | 16                                |            |                         |           |           |              |        |          |       |          |                         |       |            |            |       |                         |           | D                       |   |   |   |

| FPUR    | 0057A4  | 32                                | —          | _                       | _         | _         | _            | _      | _        | -     | _        | —                       |       | _          | _          | _     | _                       | -         | Reserved <sup>(1)</sup> |   |   |   |

| FICD    | 002BA8  | 16                                |            |                         |           |           |              |        |          |       |          | Reserved <sup>(1)</sup> |       |            |            |       |                         |           | S <1:0>                 |   |   |   |

| FICD    | 0057A8  | 32                                |            | _                       | _         |           | _            |        | _        | _     |          | Reserved                | —     | JTAGEN     | —          | _     | —                       |           | S <1:0>                 |   |   |   |

| FDEVOPT | 002BAC  | 16                                |            |                         |           |           |              |        |          |       |          |                         |       |            |            |       | Reserved <sup>(1)</sup> |           | PWMLOCK                 |   |   |   |

| FDEVOPT | 0057AC  | 32                                | _          | _                       | _         |           | _            |        | _        | _     | —        | _                       | _     | _          | _          | _     | reserved.,              | —         | FVVIVILUUK              |   |   |   |

| FALTREG | 002BB0  | 16                                |            |                         |           |           |              |        |          |       |          |                         |       | OTVT0 -01  | <b>)</b> ~ |       | CT                      | VT1 -0    | .0.                     |   |   |   |

| FALIKEG | 0057B0  | 32                                | —          | _                       | _         | _         | _            | —      | _        | —     | _        | —                       |       | CTXT2 <2:0 | <ر         | _     |                         | XT1 <2:   | .0>                     |   |   |   |

Note 1: These bits are reserved and must be programmed as '1'.

2: This bit is reserved and must be programmed as '0'.

### TABLE 25-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARACTI      | ERISTICS                  |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |        |            |           |  |  |

|------------------|---------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|-----------|--|--|

| Parameter<br>No. | Тур.                      | Max. | Units                                                                                                                                                                                                                                                                                   |        | Conditions |           |  |  |

| Operating Cur    | rent (IDD) <sup>(1)</sup> |      |                                                                                                                                                                                                                                                                                         |        |            |           |  |  |

| DC20d            | 5                         | 10   | mA                                                                                                                                                                                                                                                                                      | -40°C  |            |           |  |  |

| DC20a            | 5                         | 10   | mA                                                                                                                                                                                                                                                                                      | +25°C  | - 3.3V     | 10 MIPS   |  |  |

| DC20b            | 5                         | 10   | mA                                                                                                                                                                                                                                                                                      | +85°C  | 5.5V       | 10 1011-5 |  |  |

| DC20c            | 5                         | 10   | mA                                                                                                                                                                                                                                                                                      | +125°C |            |           |  |  |

| DC22d            | 10                        | 15   | mA                                                                                                                                                                                                                                                                                      | -40°C  |            |           |  |  |

| DC22a            | 10                        | 15   | mA                                                                                                                                                                                                                                                                                      | +25°C  | 2.21/      |           |  |  |

| DC22b            | 10                        | 15   | mA                                                                                                                                                                                                                                                                                      | +85°C  | - 3.3V     | 20 MIPS   |  |  |

| DC22c            | 10                        | 15   | mA                                                                                                                                                                                                                                                                                      | +125°C |            |           |  |  |

| DC24d            | 15                        | 20   | mA                                                                                                                                                                                                                                                                                      | -40°C  |            |           |  |  |

| DC24a            | 15                        | 20   | mA                                                                                                                                                                                                                                                                                      | +25°C  | 3.3V       | 40 MIPS   |  |  |

| DC24b            | 15                        | 20   | mA                                                                                                                                                                                                                                                                                      | +85°C  | - 3.3V     | 40 MIPS   |  |  |

| DC24c            | 15                        | 20   | mA                                                                                                                                                                                                                                                                                      | +125°C |            |           |  |  |

| DC25d            | 20                        | 28   | mA                                                                                                                                                                                                                                                                                      | -40°C  |            |           |  |  |

| DC25a            | 20                        | 28   | mA                                                                                                                                                                                                                                                                                      | +25°C  | 2.21/      |           |  |  |

| DC25b            | 20                        | 28   | mA                                                                                                                                                                                                                                                                                      | +85°C  | - 3.3V     | 60 MIPS   |  |  |

| DC25c            | 20                        | 28   | mA                                                                                                                                                                                                                                                                                      | +125°C |            |           |  |  |

| DC26d            | 30                        | 35   | mA                                                                                                                                                                                                                                                                                      | -40°C  |            |           |  |  |

| DC26a            | 30                        | 35   | mA                                                                                                                                                                                                                                                                                      | +25°C  | 3.3V       | 70 MIPS   |  |  |

| DC26b            | 30                        | 35   | mA                                                                                                                                                                                                                                                                                      | +85°C  |            |           |  |  |

**Note 1:** IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

Oscillator is configured in EC mode with PLL, OSC1 is driven with external square wave from rail-to-rail (EC Clock Overshoot/Undershoot < 250 mV required)</li>

- · CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as outputs and driving low

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating or being clocked (defined PMDx bits are all ones)

- CPU executing:

while(1) {

· JTAG is disabled

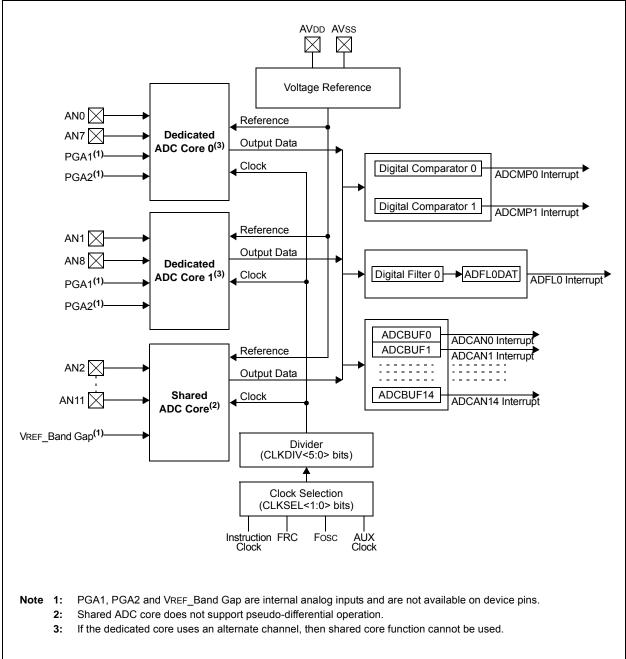

## TABLE 25-35:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| АС СНА       | ARACTERIS             | TICS                                            | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                     |                        |       |                                |  |  |  |

|--------------|-----------------------|-------------------------------------------------|------------------------------------------------------|---------------------|------------------------|-------|--------------------------------|--|--|--|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                   | Min.                                                 | Тур. <sup>(2)</sup> | Max.                   | Units | Conditions                     |  |  |  |

| SP70         | FscP                  | Maximum SCK1 Input<br>Frequency                 | _                                                    | _                   | Lesser of:<br>FP or 15 | MHz   | (Note 3)                       |  |  |  |

| SP72         | TscF                  | SCK1 Input Fall Time                            | —                                                    | —                   | _                      | ns    | See Parameter DO32 (Note 4)    |  |  |  |

| SP73         | TscR                  | SCK1 Input Rise Time                            | —                                                    | _                   | _                      | ns    | See Parameter DO31<br>(Note 4) |  |  |  |

| SP30         | TdoF                  | SDO1 Data Output Fall Time                      | —                                                    | _                   | _                      | ns    | See Parameter DO32<br>(Note 4) |  |  |  |

| SP31         | TdoR                  | SDO1 Data Output Rise Time                      | —                                                    | _                   | _                      | ns    | See Parameter DO31<br>(Note 4) |  |  |  |

| SP35         | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid After<br>SCK1 Edge       | —                                                    | 6                   | 20                     | ns    |                                |  |  |  |

| SP36         | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge    | 30                                                   | —                   | _                      | ns    |                                |  |  |  |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data Input to SCK1 Edge      | 30                                                   | —                   | _                      | ns    |                                |  |  |  |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge       | 30                                                   | _                   | _                      | ns    |                                |  |  |  |

| SP50         | TssL2scH,<br>TssL2scL | $\overline{SS1}$ ↓ to SCK1 ↑ or SCK1 ↓<br>Input | 120                                                  | —                   | _                      | ns    |                                |  |  |  |

| SP51         | TssH2doZ              | SS1 ↑ to SDO1 Output<br>High-Impedance          | 10                                                   | _                   | 50                     | ns    | (Note 4)                       |  |  |  |

| SP52         | TscH2ssH,<br>TscL2ssH | SS1 ↑ after SCK1 Edge                           | 1.5 Tcy + 40                                         | —                   | _                      | ns    | (Note 4)                       |  |  |  |

| SP60         | TssL2doV              | SDO1 Data Output Valid After<br>SS1 Edge        | —                                                    | —                   | 50                     | ns    |                                |  |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 66.7 ns. Therefore, the SCK1 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI1 pins.

### FIGURE 25-16: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

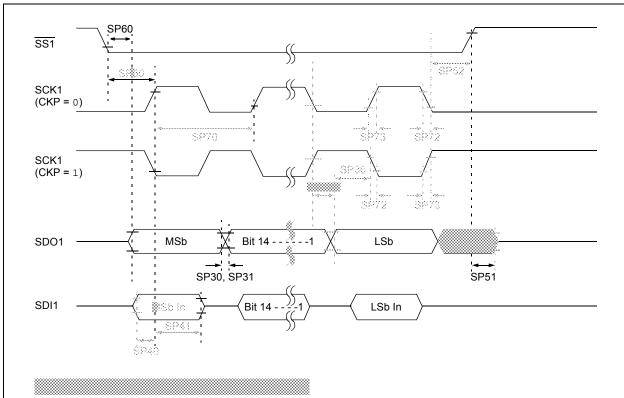

## 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2

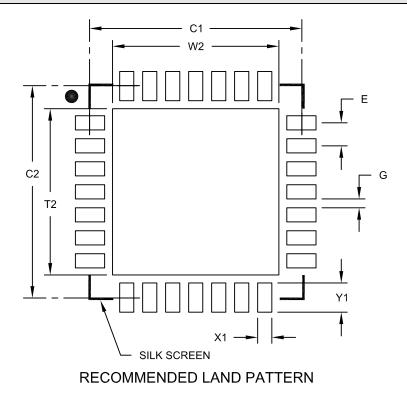

## 28-Lead Plastic Quad Flat, No Lead Package (MM) – 6x6x0.9 mm Body [QFN-S] with 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |          |      |      |  |

|----------------------------|-------------|----------|------|------|--|

| Dimensio                   | on Limits   | MIN      | NOM  | MAX  |  |

| Contact Pitch              | E           | 0.65 BSC |      |      |  |

| Optional Center Pad Width  | W2          |          |      | 4.70 |  |

| Optional Center Pad Length | T2          |          |      | 4.70 |  |

| Contact Pad Spacing        | C1          |          | 6.00 |      |  |

| Contact Pad Spacing        | C2          |          | 6.00 |      |  |

| Contact Pad Width (X28)    | X1          |          |      | 0.40 |  |

| Contact Pad Length (X28)   | Y1          |          |      | 0.85 |  |

| Distance Between Pads      | G           | 0.25     |      |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2124A