#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 2K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x12b, 2x12b                                                                |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep16gs202t-e-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

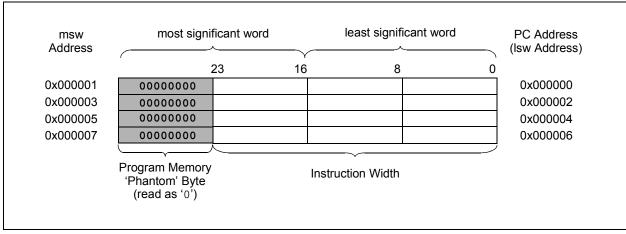

#### 4.2.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-3).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented, or decremented, by two during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

#### 4.2.2 INTERRUPT AND TRAP VECTORS

All dsPIC33EPXXGS202 family devices reserve the addresses between 0x000000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address, 0x000000, of Flash memory, with the actual address for the start of code at address, 0x000002, of Flash memory.

A more detailed discussion of the Interrupt Vector Tables (IVTs) is provided in **Section 7.1** "Interrupt Vector Table".

#### FIGURE 4-3: PROGRAM MEMORY ORGANIZATION

### 4.5 Special Function Register Maps

#### TABLE 4-2: CPU CORE REGISTER MAP

| IADLL 4               | -2.   |                                  |         |        |              |            |              |            |              |            |           |           |             |             |             |         |        |               |

|-----------------------|-------|----------------------------------|---------|--------|--------------|------------|--------------|------------|--------------|------------|-----------|-----------|-------------|-------------|-------------|---------|--------|---------------|

| File<br>Name          | Addr. | Bit 15                           | Bit 14  | Bit 13 | Bit 12       | Bit 11     | Bit 10       | Bit 9      | Bit 8        | Bit 7      | Bit 6     | Bit 5     | Bit 4       | Bit 3       | Bit 2       | Bit 1   | Bit 0  | All<br>Resets |

| W0                    | 0000  |                                  |         |        |              |            |              |            | W0 (WRE      | G)         |           |           |             |             |             |         |        | xxxx          |

| W1                    | 0002  |                                  | W1 xxxx |        |              |            |              |            |              |            | xxxx      |           |             |             |             |         |        |               |

| W2                    | 0004  |                                  |         |        |              |            |              |            | W2           |            |           |           |             |             |             |         |        | xxxx          |

| W3                    | 0006  |                                  |         |        |              |            |              |            | W3           |            |           |           |             |             |             |         |        | xxxx          |

| W4                    | 8000  |                                  |         |        |              |            |              |            | W4           |            |           |           |             |             |             |         |        | xxxx          |

| W5                    | 000A  |                                  |         |        |              |            |              |            | W5           |            |           |           |             |             |             |         |        | xxxx          |

| W6                    | 000C  |                                  |         |        |              |            |              |            | W6           |            |           |           |             |             |             |         |        | xxxx          |

| W7                    | 000E  |                                  |         |        |              |            |              |            | W7           |            |           |           |             |             |             |         |        | xxxx          |

| W8                    | 0010  |                                  |         |        |              |            |              |            | W8           |            |           |           |             |             |             |         |        | xxxx          |

| W9                    | 0012  |                                  |         |        |              |            |              |            | W9           |            |           |           |             |             |             |         |        | xxxx          |

| W10                   | 0014  |                                  |         |        |              |            |              |            | W10          |            |           |           |             |             |             |         |        | xxxx          |

| W11                   | 0016  |                                  |         |        |              |            |              |            | W11          |            |           |           |             |             |             |         |        | xxxx          |

| W12                   | 0018  |                                  |         |        |              |            |              |            | W12          |            |           |           |             |             |             |         |        | xxxx          |

| W13                   | 001A  |                                  |         |        |              |            |              |            | W13          |            |           |           |             |             |             |         |        | xxxx          |

| W14                   | 001C  |                                  |         |        |              |            |              |            | W14          |            |           |           |             |             |             |         |        | xxxx          |

| W15                   | 001E  |                                  |         |        |              |            |              |            | W15          |            |           |           |             |             |             |         |        | xxxx          |

| SPLIM                 | 0020  |                                  |         |        |              |            |              |            | SPLIM        |            |           |           |             |             |             |         |        | 0000          |

| ACCAL                 | 0022  |                                  |         |        |              |            |              |            | ACCAL        |            |           |           |             |             |             |         |        | 0000          |

| ACCAH                 | 0024  |                                  |         |        |              |            |              |            | ACCAH        |            |           |           |             |             |             |         |        | 0000          |

| ACCAU                 | 0026  |                                  |         | Się    | gn Extension | of ACCA<39 | )>           |            |              |            |           |           | ACC         | AU          |             |         |        | 0000          |

| ACCBL                 | 0028  |                                  |         |        |              |            |              |            | ACCBL        |            |           |           |             |             |             |         |        | 0000          |

| ACCBH                 | 002A  |                                  | ACCBH 0 |        |              |            |              |            | 0000         |            |           |           |             |             |             |         |        |               |

| ACCBU                 | 002C  | Sign Extension of ACCB<39> ACCBU |         |        |              |            |              | 0000       |              |            |           |           |             |             |             |         |        |               |

| PCL                   | 002E  | PCL<15:1> —                      |         |        |              |            |              | _          | 0000         |            |           |           |             |             |             |         |        |               |

| PCH                   | 0030  | _                                | _       | _      | _            | —          | —            | _          | _            | _          |           |           |             | PCH<6:0>    |             |         |        | 0000          |

| DSRPAG                | 0032  | _                                | _       | _      | _            | _          | _            |            | E            | Extended D | ata Space | EDS) Read | I Page Reg  | ister (DSRI | PAG<9:0>)   |         |        | 0001          |

| DSWPAG <sup>(1)</sup> | 0034  | _                                |         |        |              |            |              |            | 0001         |            |           |           |             |             |             |         |        |               |

| RCOUNT                | 0036  |                                  |         |        |              |            |              | F          | RCOUNT<1     | 5:0>       |           |           |             |             |             |         |        | 0000          |

| DCOUNT                | 0038  |                                  |         |        |              |            | DO           | Loop Count | er Register  | (DCOUNT«   | <15:0>)   |           |             |             |             |         |        | 0000          |

| DOSTARTL              | 003A  |                                  |         |        |              | DO         | Loop Start A | Address Re | gister Low ( | DOSTARTL   | _<15:1>)  |           |             |             |             |         | —      | 0000          |

| DOSTARTH              | 003C  | —                                | —       | —      | —            | —          | —            | —          | —            | —          | —         | DO LOO    | p Start Add | dress Regis | ter High (D | OSTARTH | <5:0>) | 0000          |

|                       | • •   |                                  |         |        |              |            |              |            |              |            |           | •         |             |             |             |         |        | ·             |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The contents of this register should never be modified. The DSWPAG must always point to the first page.

### 10.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs other than VDD by using external pull-up resistors. The maximum open-drain voltage allowed on any pin is the same as the maximum VIH specification for that particular pin.

See the **"Pin Diagrams"** section for the available 5V tolerant pins and Table 25-11 for the maximum VIH specification for each pin.

#### 10.2 Configuring Analog and Digital Port Pins

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs or outputs must have their corresponding ANSELx and TRISx bits set. In order to use port pins for I/O functionality with digital modules, such as timers, UART, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

Pins with analog functions affected by the ANSELx registers are listed with a buffer type of analog in the Pinout I/O Descriptions (see Table 1-1).

If the TRISx bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or comparator module.

When the PORTx register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin, defined as a digital input (including the ANx pins), can cause the input buffer to consume current that exceeds the device specifications.

#### 10.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP, as shown in Example 10-1.

### **10.3** Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State.

Three control registers are associated with the ICN functionality of each I/O port. The CNENx registers contain the ICN interrupt enable control bits for each of the input pins. Setting any of these bits enables an ICN interrupt for the corresponding pins.

Each I/O pin also has a weak pull-up and a weak pull-down connected to it. The pull-ups and pulldowns act as a current source, or sink source, connected to the pin, and eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups and pull-downs are enabled separately, using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

| Note: | Pull-ups and pull-downs on Input Change  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|

|       | Notification pins should always be       |  |  |  |  |  |  |

|       | disabled when the port pin is configured |  |  |  |  |  |  |

|       | as a digital output.                     |  |  |  |  |  |  |

|  | EXAMPLE 10-1: | PORT WRITE/READ |

|--|---------------|-----------------|

|--|---------------|-----------------|

| MOV  | 0xFF00, W0 | ; Configure PORTB<15:8> |

|------|------------|-------------------------|

|      |            | ; as inputs             |

| MOV  | W0, TRISB  | ; and PORTB<7:0>        |

|      |            | ; as outputs            |

| NOP  |            | ; Delay 1 cycle         |

| BTSS | PORTB, #13 | ; Next Instruction      |

|      |            |                         |

#### 10.7 Peripheral Pin Select Registers

#### REGISTER 10-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

|        |       |       | INT1R | <7:0> |       |       |       |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| U-0    | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   |

| —      | —     | —     | —     | —     | —     | —     | —     |

| bit 7  | ·     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-8 INT1R<7:0>: Assign External Interrupt 1 (INT1) to the Corresponding RPn Pin bits 10110101 = Input tied to RP181 10110100 = Input tied to RP180 . . 00000001 = Input tied to RP1 00000000 = Input tied to Vss

bit 7-0 Unimplemented: Read as '0'

#### REGISTER 10-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0              | U-0                            | U-0              | U-0            | U-0                                | U-0            | U-0             | U-0                |  |  |  |  |  |

|------------------|--------------------------------|------------------|----------------|------------------------------------|----------------|-----------------|--------------------|--|--|--|--|--|

|                  | —                              | —                | _              | —                                  | —              | —               | _                  |  |  |  |  |  |

| bit 15           |                                |                  |                |                                    |                | •<br>•          | bit 8              |  |  |  |  |  |

|                  |                                |                  |                |                                    |                |                 |                    |  |  |  |  |  |

| R/W-0            | R/W-0                          | R/W-0            | R/W-0          | R/W-0                              | R/W-0          | R/W-0           | R/W-0              |  |  |  |  |  |

|                  |                                |                  | INT2           | R<7:0>                             |                |                 |                    |  |  |  |  |  |

| bit 7            |                                |                  |                |                                    |                |                 | bit 0              |  |  |  |  |  |

|                  |                                |                  |                |                                    |                |                 |                    |  |  |  |  |  |

| Legend:          |                                |                  |                |                                    |                |                 |                    |  |  |  |  |  |

| R = Readable bit |                                | W = Writable     | bit            | U = Unimplemented bit, read as '0' |                |                 |                    |  |  |  |  |  |

| -n = Value a     | at POR                         | '1' = Bit is set | t              | '0' = Bit is cle                   | ared           | x = Bit is unkr | x = Bit is unknown |  |  |  |  |  |

|                  |                                |                  |                |                                    |                |                 |                    |  |  |  |  |  |

| bit 15-8         | Unimpleme                      | nted: Read as '  | 0'             |                                    |                |                 |                    |  |  |  |  |  |

| bit 7-0          | INT2R<7:0>                     | : Assign Extern  | al Interrupt 2 | (INT2) to the C                    | orresponding R | Pn Pin bits     |                    |  |  |  |  |  |

|                  | 10110101 = Input tied to RP181 |                  |                |                                    |                |                 |                    |  |  |  |  |  |

|                  | 10110100 = Input tied to RP180 |                  |                |                                    |                |                 |                    |  |  |  |  |  |

|                  | •                              |                  |                |                                    |                |                 |                    |  |  |  |  |  |

|                  | •                              |                  |                |                                    |                |                 |                    |  |  |  |  |  |

|                  | •                              |                  |                |                                    |                |                 |                    |  |  |  |  |  |

|                  | 00000001 =                     | Input tied to R  | P1             |                                    |                |                 |                    |  |  |  |  |  |

|                  |                                |                  |                |                                    |                |                 |                    |  |  |  |  |  |

00000000 = Input tied to Vss

| U-0    | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| _      | _   | RP177R5 | RP177R4 | RP177R3 | RP177R2 | RP177R1 | RP177R0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

|        |     |         |         |         |         |         |         |

| U-0    | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

#### REGISTER 10-24: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | RP176R5 | RP176R4 | RP176R3 | RP176R2 | RP176R1 | RP176R0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP177R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP177 Output Pin bits (see Table 10-2 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                                 |

| bit 5-0   | <b>RP176R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP176 Output Pin bits (see Table 10-2 for peripheral function numbers) |

#### REGISTER 10-25: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0    | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| —      | —   | RP179R5 | RP179R4 | RP179R3 | RP179R2 | RP179R1 | RP179R0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | RP178R5 | RP178R4 | RP178R3 | RP178R2 | RP178R1 | RP178R0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP179R<5:0>:** Peripheral Output Function is Assigned to RP179 Output Pin bits (see Table 10-2 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0' bit 5-0 RP178R<5:0>: Peripheral Output Function is

bit 5-0 **RP178R<5:0>:** Peripheral Output Function is Assigned to RP178 Output Pin bits (see Table 10-2 for peripheral function numbers)

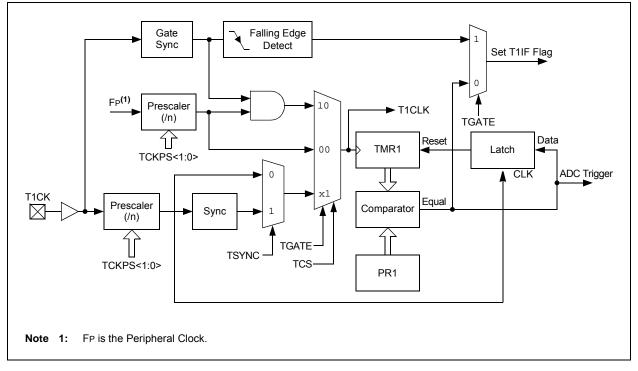

#### 11.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer that can operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be Operated in Asynchronous Counter mode from an External Clock Source

- The External Clock Input (T1CK) can Optionally be Synchronized to the Internal Device Clock and the Clock Synchronization is Performed after the Prescaler

- A block diagram of Timer1 is shown in Figure 11-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- Gated Timer mode

- Synchronous Counter mode

- · Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FcY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

Timer control bit settings for different operating modes are provided in Table 11-1.

| TABLE 11-1: | TIMER MODE SETTINGS |

|-------------|---------------------|

|-------------|---------------------|

| Mode                    | TCS | TGATE | TSYNC |

|-------------------------|-----|-------|-------|

| Timer                   | 0   | 0     | x     |

| Gated Timer             | 0   | 1     | х     |

| Synchronous<br>Counter  | 1   | x     | 1     |

| Asynchronous<br>Counter | 1   | x     | 0     |

#### FIGURE 11-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

| R/W-0              | U-0                                                                               | R/W-0                                                                  | U-0                    | U-0                        | U-0            | U-0                | U-0         |  |  |

|--------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------|----------------------------|----------------|--------------------|-------------|--|--|

| TON <sup>(1)</sup> | —                                                                                 | TSIDL <sup>(2)</sup>                                                   | _                      | —                          | _              |                    | _           |  |  |

| bit 15             |                                                                                   |                                                                        |                        |                            |                |                    | bit         |  |  |

|                    |                                                                                   |                                                                        |                        |                            |                |                    |             |  |  |

| U-0                | R/W-0                                                                             | R/W-0                                                                  | R/W-0                  | U-0                        | U-0            | R/W-0              | U-0         |  |  |

|                    | TGATE <sup>(1)</sup>                                                              | TCKPS1 <sup>(1)</sup>                                                  | TCKPS0 <sup>(1)</sup>  | —                          |                | TCS <sup>(1)</sup> |             |  |  |

| bit 7              |                                                                                   |                                                                        |                        |                            |                |                    | bit         |  |  |

| Legend:            |                                                                                   |                                                                        |                        |                            |                |                    |             |  |  |

| R = Reada          | ble bit                                                                           | W = Writable t                                                         | bit                    | U = Unimplem               | nented bit, re | ad as '0'          |             |  |  |

| -n = Value         | at POR                                                                            | '1' = Bit is set                                                       |                        | '0' = Bit is clea          | ared           | x = Bit is unkno   | own         |  |  |

|                    |                                                                                   |                                                                        |                        |                            |                |                    |             |  |  |

| bit 15             | TON: Timer3                                                                       | On bit <sup>(1)</sup>                                                  |                        |                            |                |                    |             |  |  |

|                    | 1 = Starts 16-                                                                    | bit Timer3                                                             |                        |                            |                |                    |             |  |  |

|                    | 0 = Stops 16-                                                                     | bit Timer3                                                             |                        |                            |                |                    |             |  |  |

| bit 14             | Unimplemen                                                                        | ted: Read as '0                                                        | ,                      |                            |                |                    |             |  |  |

| bit 13             | TSIDL: Timer                                                                      | 3 Stop in Idle M                                                       | ode bit <sup>(2)</sup> |                            |                |                    |             |  |  |

|                    |                                                                                   | ues module ope<br>s module operat                                      |                        |                            | e mode         |                    |             |  |  |

| bit 12-7           | Unimplemen                                                                        | ted: Read as '0                                                        | 2                      |                            |                |                    |             |  |  |

| bit 6              | TGATE: Time                                                                       | <b>TGATE:</b> Timer3 Gated Time Accumulation Enable bit <sup>(1)</sup> |                        |                            |                |                    |             |  |  |

|                    | When TCS =<br>This bit is igno                                                    |                                                                        |                        |                            |                |                    |             |  |  |

|                    | When TCS =                                                                        |                                                                        |                        |                            |                |                    |             |  |  |

|                    | 1 = Gated time accumulation is enabled<br>0 = Gated time accumulation is disabled |                                                                        |                        |                            |                |                    |             |  |  |

| bit 5-4            | TCKPS<1:0>                                                                        | : Timer3 Input C                                                       | lock Prescale          | Select bits <sup>(1)</sup> |                |                    |             |  |  |

|                    | 11 <b>= 1:256</b>                                                                 |                                                                        |                        |                            |                |                    |             |  |  |

|                    | 10 <b>= 1:64</b>                                                                  |                                                                        |                        |                            |                |                    |             |  |  |

|                    | 01 = 1:8                                                                          |                                                                        |                        |                            |                |                    |             |  |  |

|                    | 00 = 1:1                                                                          |                                                                        | ,                      |                            |                |                    |             |  |  |

| bit 3-2            | -                                                                                 | ted: Read as '0                                                        |                        |                            |                |                    |             |  |  |

| bit 1              |                                                                                   | Clock Source S                                                         |                        |                            |                |                    |             |  |  |

|                    | 1 = External o<br>0 = Periphera                                                   | clock is from pin<br>I Clock (FP)                                      | , T3CK (on the         | rising eage)               |                |                    |             |  |  |

| bit 0              | Unimplemen                                                                        | ted: Read as '0                                                        | ,                      |                            |                |                    |             |  |  |

|                    | When 32-bit operative timer functions are                                         |                                                                        |                        | = 1), these bits           | have no effe   | ct on Timer3 ope   | ration; all |  |  |

2: When 32-bit timer operation is enabled (T32 = 1) in the Timer2 Control register (T2CON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

#### REGISTER 15-1: PTCON: PWM TIME BASE CONTROL REGISTER

| R/W-0  | U-0 | R/W-0  | HS/HC-0 | R/W-0 | R/W-0               | R/W-0                  | R/W-0                  |

|--------|-----|--------|---------|-------|---------------------|------------------------|------------------------|

| PTEN   | —   | PTSIDL | SESTAT  | SEIEN | EIPU <sup>(1)</sup> | SYNCPOL <sup>(1)</sup> | SYNCOEN <sup>(1)</sup> |

| bit 15 |     |        |         |       |                     |                        | bit 8                  |

| R/W-0                 | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-----------------------|-------------------------|-------------------------|-------------------------|------------------------|------------------------|------------------------|------------------------|

| SYNCEN <sup>(1)</sup> | SYNCSRC2 <sup>(1)</sup> | SYNCSRC1 <sup>(1)</sup> | SYNCSRC0 <sup>(1)</sup> | SEVTPS3 <sup>(1)</sup> | SEVTPS2 <sup>(1)</sup> | SEVTPS1 <sup>(1)</sup> | SEVTPS0 <sup>(1)</sup> |

| bit 7                 |                         |                         |                         |                        |                        |                        | bit 0                  |

| Legend:    |                        | HC = Hardware Clearable b                                                | it HS = Hardware Settab          | le bit             |

|------------|------------------------|--------------------------------------------------------------------------|----------------------------------|--------------------|

| R = Reada  | able bit               | W = Writable bit                                                         | U = Unimplemented bit            | t, read as '0'     |

| -n = Value | at POR                 | '1' = Bit is set                                                         | '0' = Bit is cleared             | x = Bit is unknown |

| bit 15     |                        | VM Module Enable bit                                                     |                                  |                    |

|            |                        | module is enabled<br>module is disabled                                  |                                  |                    |

| bit 14     | Unimplen               | nented: Read as '0'                                                      |                                  |                    |

| bit 13     | PTSIDL:                | PWM Time Base Stop in Idle Moo                                           | de bit                           |                    |

|            |                        | time base halts in CPU Idle mod time base runs in CPU Idle mode          |                                  |                    |

| bit 12     | SESTAT:                | Special Event Interrupt Status bit                                       |                                  |                    |

|            |                        | al event interrupt is pending<br>al event interrupt is not pending       |                                  |                    |

| bit 11     | SEIEN: S               | pecial Event Interrupt Enable bit                                        |                                  |                    |

|            |                        | al event interrupt is enabled<br>al event interrupt is disabled          |                                  |                    |

| bit 10     | EIPU: Ena              | able Immediate Period Updates b                                          | <sub>oit</sub> (1)               |                    |

|            |                        | Period register is updated imme<br>Period register updates occur of      |                                  |                    |

| bit 9      | SYNCPO                 | L: Synchronize Input and Output                                          | Polarity bit <sup>(1)</sup>      |                    |

|            |                        | Ix/SYNCO1 polarity is inverted (a<br>Ix/SYNCO1 is active-high            | active-low)                      |                    |

| bit 8      | SYNCOE                 | N: Primary Time Base Synchroni                                           | zation Enable bit <sup>(1)</sup> |                    |

|            |                        | O1 output is enabled<br>O1 output is disabled                            |                                  |                    |

| bit 7      | SYNCEN:                | External Time Base Synchroniz                                            | ation Enable bit <sup>(1)</sup>  |                    |

|            |                        | nal synchronization of primary tim<br>nal synchronization of primary tim |                                  |                    |

| bit 6-4    | SYNCSR                 | C<2:0>: Synchronous Source Se                                            | lection bits <sup>(1)</sup>      |                    |

|            | 111 = Re:              |                                                                          |                                  |                    |

|            | 101 = Re:              |                                                                          |                                  |                    |

|            | 100 = Re:<br>011 = Re: |                                                                          |                                  |                    |

|            | 011 = Re:<br>010 = Re: |                                                                          |                                  |                    |

|            | 001 = SY               |                                                                          |                                  |                    |

|            | 000 = SY               | NCI1                                                                     |                                  |                    |

**Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCIx feature, the user application must program the Period register with a value that is slightly larger than the expected period of the external synchronization input signal.

#### REGISTER 15-12: PWMCONx: PWMx CONTROL REGISTER (CONTINUED)

- bit 7-6 **DTC<1:0>:** Dead-Time Control bits

- 11 = Reserved

- 10 = Dead-time function is disabled

- 01 = Negative dead time is actively applied for Complementary Output mode

- 00 = Positive dead time is actively applied for all Output modes

- bit 5-4 Unimplemented: Read as '0'

- bit 3 MTBS: Master Time Base Select bit

- 1 = PWMx generator uses the secondary master time base for synchronization and the clock source for the PWMx generation logic (if secondary time base is available)

- 0 = PWMx generator uses the primary master time base for synchronization and the clock source for the PWMx generation logic

- bit 2 **CAM:** Center-Aligned Mode Enable bit<sup>(2,3,4)</sup> 1 = Center-Aligned mode is enabled

- 0 = Edge-Aligned mode is enabled

- bit 1 XPRES: External PWMx Reset Control bit<sup>(5)</sup>

- 1 = Current-limit source resets the time base for this PWMx generator if it is in Independent Time Base mode

- 0 = External pins do not affect the PWMx time base

- bit 0 IUE: Immediate Update Enable bit

- 1 = Updates to the active Duty Cycle, Phase Offset, Dead-Time and local Time Base Period registers are immediate

- 0 = Updates to the active Duty Cycle, Phase Offset, Dead-Time and local Time Base Period registers are synchronized to the local PWMx time base

- Note 1: Software must clear the interrupt status here and in the corresponding IFSx register in the interrupt controller.

- 2: The Independent Time Base mode (ITB = 1) must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored.

- 3: These bits should not be changed after the PWM is enabled by setting PTEN (PTCON<15>) = 1.

- 4: Center-Aligned mode ignores the Least Significant 3 bits of the Duty Cycle, Phase and Dead-Time registers. The highest Center-Aligned mode resolution available is 8.32 ns with the clock prescaler set to the fastest clock.

- 5: Configure CLMOD (FCLCONx<8>) = 0 and ITB (PWMCONx<9>) = 1 to operate in External Period Reset mode.

#### **REGISTER 15-13: PDCx: PWMx GENERATOR DUTY CYCLE REGISTER**<sup>(1,2,3)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0                                       | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|-----------------|-------|------------------|---------------------------------------------|----------|-------|-------|-------|

|                 |       |                  | PDC                                         | x<15:8>  |       |       |       |

| bit 15          |       |                  |                                             |          |       |       | bit 8 |

|                 |       |                  |                                             |          |       |       |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0                                       | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|                 |       |                  | PDC                                         | \$x<7:0> |       |       |       |

| bit 7           |       |                  |                                             |          |       |       | bit 0 |

|                 |       |                  |                                             |          |       |       |       |

| Legend:         |       |                  |                                             |          |       |       |       |

| R = Readable    | bit   | W = Writable b   | bit U = Unimplemented bit, read as '0'      |          |       |       |       |

| -n = Value at P | OR    | '1' = Bit is set | set '0' = Bit is cleared x = Bit is unknown |          |       |       | nown  |

bit 15-0 PDCx<15:0>: PWMx Generator Duty Cycle Value bits

**Note 1:** In Independent PWM mode, the PDCx register controls the PWMxH duty cycle only. In the Complementary, Redundant and Push-Pull PWM modes, the PDCx register controls the duty cycle of both the PWMxH and PWMxL.

**2:** The smallest pulse width that can be generated on the PWMx output corresponds to a value of 0x0008, while the maximum pulse width generated corresponds to a value of Period – 0x0008.

**3:** As the duty cycle gets closer to 0% or 100% of the PWM period (0 to 40 ns, depending on the mode of operation), PWM duty cycle resolution will increase from 1 to 3 LSBs.

#### REGISTER 15-14: SDCx: PWMx SECONDARY DUTY CYCLE REGISTER<sup>(1,2,3)</sup>

| R/W-0                              | R/W-0                                                           | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|------------------------------------|-----------------------------------------------------------------|-------|-------|-----------------------------------------|-------|-------|-------|

|                                    |                                                                 |       | SDC   | x<15:8>                                 |       |       |       |

| bit 15                             |                                                                 |       |       |                                         |       |       | bit 8 |

|                                    |                                                                 |       |       |                                         |       |       |       |

| R/W-0                              | R/W-0                                                           | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                                    |                                                                 |       | SDC   | \$x<7:0>                                |       |       |       |

| bit 7                              |                                                                 |       |       |                                         |       |       | bit 0 |

|                                    |                                                                 |       |       |                                         |       |       |       |

| Legend:                            |                                                                 |       |       |                                         |       |       |       |

| R = Readable                       | eadable bit W = Writable bit U = Unimplemented bit, read as '0' |       |       |                                         |       |       |       |

| -n = Value at POR '1' = Bit is set |                                                                 |       |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |

|                                    |                                                                 |       |       |                                         |       |       |       |

bit 15-0 SDCx<15:0>: Secondary Duty Cycle for PWMxL Output Pin bits

**Note 1:** The SDCx register is used in Independent PWM mode only. When used in Independent PWM mode, the SDCx register controls the PWMxL duty cycle.

**2:** The smallest pulse width that can be generated on the PWM output corresponds to a value of 0x0008, while the maximum pulse width generated corresponds to a value of Period – 0x0008.

**3:** As the duty cycle gets closer to 0% or 100% of the PWM period (0 to 40 ns, depending on the mode of operation), PWM duty cycle resolution will increase from 1 to 3 LSBs.

## REGISTER 15-24: LEBCONX: PWMx LEADING-EDGE BLANKING (LEB) CONTROL REGISTER (CONTINUED)

- bit 1

BPLH: Blanking in PWMxL High Enable bit

1 = State blanking (of current-limit and/or Fault input signals) when the PWMxL output is high

bit 0

BPLL: Blanking in PWMxL Low Enable bit

1 = State blanking (of current-limit and/or Fault input signals) when the PWMxL output is low

0 = No blanking when the PWMxL Low Enable bit

1 = State blanking (of current-limit and/or Fault input signals) when the PWMxL output is low

0 = No blanking when the PWMxL output is low

- **Note 1:** The blanking signal is selected via the BLANKSEL<3:0> bits in the AUXCONx register.

#### REGISTER 15-25: LEBDLYx: PWMx LEADING-EDGE BLANKING DELAY REGISTER

| U-0             | U-0   | U-0              | U-0   | R/W-0                                   | R/W-0    | R/W-0 | R/W-0 |  |  |

|-----------------|-------|------------------|-------|-----------------------------------------|----------|-------|-------|--|--|

| —               | —     | _                | _     |                                         | LEB<8:5> |       |       |  |  |

| bit 15          |       |                  |       |                                         |          |       | bit 8 |  |  |

|                 |       |                  |       |                                         |          |       |       |  |  |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | U-0      | U-0   | U-0   |  |  |

|                 |       | LEB<4:0>         |       |                                         | —        | —     | —     |  |  |

| bit 7           |       |                  |       |                                         |          |       | bit 0 |  |  |

|                 |       |                  |       |                                         |          |       |       |  |  |

| Legend:         |       |                  |       |                                         |          |       |       |  |  |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplemented bit, read as '0'      |          |       |       |  |  |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |          |       | nown  |  |  |

bit 15-12 Unimplemented: Read as '0'

bit 11-3 **LEB<8:0>:** Leading-Edge Blanking Delay for Current-Limit and Fault Inputs bits The value is in 8.32 ns increments.

bit 2-0 Unimplemented: Read as '0'

| REGISTER 17-2: I2 | 2C1CONH: I2C1 CONTROL | REGISTER HIGH |

|-------------------|-----------------------|---------------|

|-------------------|-----------------------|---------------|

| REGISTE    | R 17-2: I2C1  | CONH: I2C1 C                           | CONTROL R                    | EGISTER HIG                          | H                |                  |                 |

|------------|---------------|----------------------------------------|------------------------------|--------------------------------------|------------------|------------------|-----------------|

| U-0        | U-0           | U-0                                    | U-0                          | U-0                                  | U-0              | U-0              | U-0             |

|            |               |                                        | _                            |                                      | —                | _                | —               |

| bit 15     |               |                                        |                              |                                      |                  |                  | bit 8           |

| U-0        | R/W-0         | R/W-0                                  | R/W-0                        | R/W-0                                | R/W-0            | R/W-0            | R/W-0           |

| _          | PCIE          | SCIE                                   | BOEN                         | SDAHT                                | SBCDE            | AHEN             | DHEN            |

| bit 7      |               |                                        |                              |                                      |                  |                  | bit 0           |

| Legend:    |               |                                        |                              |                                      |                  |                  |                 |

| R = Reada  | ble bit       | W = Writable                           | oit                          | U = Unimplem                         | ented bit, read  | as '0'           |                 |

| -n = Value | at POR        | '1' = Bit is set                       |                              | '0' = Bit is clea                    | ired             | x = Bit is unkr  | nown            |

|            |               |                                        |                              |                                      |                  |                  |                 |

| bit 15-7   | -             | nted: Read as '                        |                              | 0                                    |                  |                  |                 |

| bit 6      | •             |                                        |                              | I <sup>2</sup> C Slave mode          | only)            |                  |                 |

|            |               | interrupt on dete<br>ection interrupts |                              | condition                            |                  |                  |                 |

| bit 5      |               |                                        |                              | I <sup>2</sup> C Slave mode          | onlv)            |                  |                 |

|            |               |                                        | -                            | or Restart condi                     | • ·              |                  |                 |

|            | 0 = Start det | ection interrupts                      | are disabled                 |                                      |                  |                  |                 |

| bit 4      | BOEN: Buffe   | er Overwrite Ena                       | ble bit (I <sup>2</sup> C SI | ave mode only)                       |                  |                  |                 |

|            |               |                                        |                              | enerated for a ree                   | ceived address   | /data byte, igno | oring the state |

|            |               | COV bit only if t<br>V is only update  |                              |                                      |                  |                  |                 |

| bit 3      |               | A1 Hold Time Se                        |                              |                                      |                  |                  |                 |

| DIL D      |               |                                        |                              | after the falling                    | edge of SCI 1    |                  |                 |

|            |               |                                        |                              | after the falling                    |                  |                  |                 |

| bit 2      | SBCDE: Sla    | ve Mode Bus Co                         | ollision Detect              | Enable bit (I <sup>2</sup> C S       | Slave mode on    | ly)              |                 |

|            | 1 = Enables   | slave bus collisi                      | on interrupts                |                                      |                  |                  |                 |

|            |               | s collision interr                     |                              |                                      |                  |                  |                 |

|            |               |                                        |                              | npled low when<br>node is only valid |                  |                  |                 |

| bit 1      |               | ess Hold Enable                        |                              | •                                    |                  |                  | it sequences.   |

|            |               |                                        |                              | CL1 for a match                      | ning received    | address byte.    | the SCLREL      |

|            | (12C1C0       |                                        | ll be cleared a              | and SCL1 will be                     |                  | <b>,</b> ,       |                 |

| bit 0      | DHEN: Data    | Hold Enable bit                        | (I <sup>2</sup> C Slave mo   | ode only)                            |                  |                  |                 |

|            |               |                                        |                              | 1 for a received                     | l data byte, the | e slave hardwa   | are clears the  |

|            |               | L (I2C1CONL<1                          | 2>) bit and S                | CL1 is held low                      |                  |                  |                 |

|            | 0 = Data hol  | ding is disabled                       |                              |                                      |                  |                  |                 |

|            |               |                                        |                              |                                      |                  |                  |                 |

### 19.0 HIGH-SPEED, 12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "12-Bit High-Speed, Multiple SARs A/D Converter (ADC)" (DS70005213) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXGS202 devices have a highspeed, 12-bit Analog-to-Digital Converter (ADC) that features a low conversion latency, high resolution and oversampling capabilities to improve performance in AC/DC, DC/DC power converters.

#### **19.1 Features Overview**

The 12-Bit High Speed Multiple SARs Analog-to-Digital Converter (ADC) includes the following features:

- 12-Bit Resolution

- Up to 3.25 Msps Conversion Rate per ADC Core @ 12-Bit Resolution

- Multiple Dedicated ADC Cores

- One Shared (common) ADC Core

- Up to 12 Analog Input Sources

- Conversion Result can be Formatted as Unsigned or Signed Data on a per Channel Basis for All Channels

- Separate 16-Bit Conversion Result Register for each Analog Input

- Simultaneous Sampling of up to 3 Analog Inputs

- Flexible Trigger Options

- Early Interrupt Generation to Enable Fast Processing of Converted Data

- Two Integrated Digital Comparators:

- Multiple comparison options

- Assignable to specific analog inputs

- · Oversampling Filters:

- Provides increased resolution

- Assignable to a specific analog input

- · Operation During CPU Sleep and Idle modes

Simplified block diagrams of the Multiple SARs 12-Bit ADC are shown in Figure 19-1, Figure 19-2 and Figure 19-3.

The module consists of two independent SAR ADC cores. The analog inputs (channels) are connected through multiplexers and switches to the Sample-and-Hold (S/H) circuit of each ADC core. The core uses the channel information (the output format, the measurement mode and the input number) to process the analog sample. When conversion is complete, the result is stored in the result buffer for the specific analog input and passed to the digital filter and digital comparator if they were configured to use data from this particular channel.

The ADC module can sample up to three inputs at a time (two inputs from the dedicated SAR ADC cores and one from the shared SAR ADC cores). If multiple ADC inputs request conversion, the ADC module will convert them in a sequential manner, starting with the lowest order input.

The ADC provides each analog input the ability to specify its own trigger source. This capability allows the ADC to sample and convert analog inputs that are associated with PWM generators operating on independent time bases.

#### REGISTER 19-6: ADCON3H: ADC CONTROL REGISTER 3 HIGH

| R/W-0                       | R/W-0                                                                                                                                                       | R/W-0                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                               | R/W-0                                    | R/W-0            | R/W-0            |  |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------|------------------|------------------|--|

| CLKSEL1                     | CLKSEL0                                                                                                                                                     | CLKDIV5                                                                                                                                                                                                                                                      | CLKDIV4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CLKDIV3                                                                                             | CLKDIV2                                  | CLKDIV1          | CLKDIV0          |  |