Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 2K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C                                                                     |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-UFQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-UQFN (4x4)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep16gs202t-i-m6 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Pin Diagrams**

| in SSC                                                                                                                                    | ic,<br>DP                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                    | Pins are up to 5V tolerant                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                           | MCLR 1<br>RA0 2<br>RA1 3<br>RA2 4<br>RB0 5<br>RB9 6<br>RB10 7<br>Vss 8<br>RB1 9<br>RB2 10<br>RB2 10<br>RB3 11<br>RB4 12<br>VDD 13<br>RD2 11                                                                                                                                                                                                          | dsPIC33EPXXGS202                                                                                                                                   | 28       AVDD         27       AVSS         26       RA3         25       RA4         24       RB14         23       RB13         22       RB12         21       RB11         20       VCAP         19       VSS         18       RB7         17       RB6         16       RB5                                     |

| PIN FI                                                                                                                                    | RB8                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                    | 15 RB15                                                                                                                                                                                                                                                                                                             |

| PIN FU<br>Pin                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                      | Pin                                                                                                                                                | 15 RB15                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                           | JNCTION DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                    | <b>F</b>                                                                                                                                                                                                                                                                                                            |

| Pin                                                                                                                                       | JNCTION DESCRIPTIONS Pin Function                                                                                                                                                                                                                                                                                                                    | Pin                                                                                                                                                | Pin Function                                                                                                                                                                                                                                                                                                        |

| Pin<br>1                                                                                                                                  | JNCTION DESCRIPTIONS Pin Function MCLR                                                                                                                                                                                                                                                                                                               | <b>Pin</b><br>15                                                                                                                                   | Pin Function PGEC3/RP47/RB15                                                                                                                                                                                                                                                                                        |

| <b>Pin</b> 1 2                                                                                                                            | JNCTION DESCRIPTIONS Pin Function MCLR AN0/PGA1P1/CMP1A/RA0                                                                                                                                                                                                                                                                                          | Pin<br>15<br>16                                                                                                                                    | Pin Function           PGEC3/RP47/RB15           TDO/AN9/PGA2N2/RP37/RB5                                                                                                                                                                                                                                            |

| Pin<br>1<br>2<br>3                                                                                                                        | JNCTION DESCRIPTIONS Pin Function MCLR AN0/PGA1P1/CMP1A/RA0 AN1/PGA1P2/PGA2P1/CMP1B/RA1                                                                                                                                                                                                                                                              | Pin<br>15<br>16<br>17                                                                                                                              | Pin Function           PGEC3/RP47/RB15           TDO/AN9/PGA2N2/RP37/RB5           PGED1/TDI/AN10/SCL1/RP38/RB6                                                                                                                                                                                                     |

| Pin 1 2 3 4                                                                                                                               | JNCTION DESCRIPTIONS<br>Pin Function<br>MCLR<br>AN0/PGA1P1/CMP1A/RA0<br>AN1/PGA1P2/PGA2P1/CMP1B/RA1<br>AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2                                                                                                                                                                                                             | Pin           15           16           17           18                                                                                            | Pin Function           PGEC3/RP47/RB15           TDO/AN9/PGA2N2/RP37/RB5           PGED1/TDI/AN10/SCL1/RP38/RB6           PGEC1/AN11/SDA1/RP39/RB7                                                                                                                                                                  |

| Pin 1 2 3 4 5                                                                                                                             | Pin Function         MCLR         AN0/PGA1P1/CMP1A/RA0         AN1/PGA1P2/PGA2P1/CMP1B/RA1         AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2         AN3/PGA2P3/CMP1D/CMP2B/RP32/RB0                                                                                                                                                                         | Pin           15           16           17           18           19                                                                               | Pin Function           PGEC3/RP47/RB15           TDO/AN9/PGA2N2/RP37/RB5           PGED1/TDI/AN10/SCL1/RP38/RB6           PGEC1/AN11/SDA1/RP39/RB7           Vss                                                                                                                                                    |

| Pin           1           2           3           4           5           6                                                               | JUNCTION DESCRIPTIONS         Pin Function         MCLR         AN0/PGA1P1/CMP1A/RA0         AN1/PGA1P2/PGA2P1/CMP1B/RA1         AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2         AN3/PGA2P3/CMP1D/CMP2B/RP32/RB0         AN4/CMP2C/RP41/RB9                                                                                                                | Pin           15           16           17           18           19           20                                                                  | Pin Function           PGEC3/RP47/RB15           TDO/AN9/PGA2N2/RP37/RB5           PGED1/TDI/AN10/SCL1/RP38/RB6           PGEC1/AN11/SDA1/RP39/RB7           Vss           VcAP                                                                                                                                     |

| Pin 1 2 3 4 5 6 7                                                                                                                         | JNCTION DESCRIPTIONS         Pin Function         MCLR         AN0/PGA1P1/CMP1A/RA0         AN1/PGA1P2/PGA2P1/CMP1B/RA1         AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2         AN3/PGA2P3/CMP1D/CMP2B/RP32/RB0         AN4/CMP2C/RP41/RB9         AN5/CMP2D/RP42/RB10                                                                                     | Pin           15           16           17           18           19           20           21                                                     | Pin Function         PGEC3/RP47/RB15         TDO/AN9/PGA2N2/RP37/RB5         PGED1/TDI/AN10/SCL1/RP38/RB6         PGEC1/AN11/SDA1/RP39/RB7         Vss         Vcap         TMS/PWM3H/RP43/RB11                                                                                                                     |

| Pin           1           2           3           4           5           6           7           8                                       | Pin Function         MCLR         AN0/PGA1P1/CMP1A/RA0         AN1/PGA1P2/PGA2P1/CMP1B/RA1         AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2         AN3/PGA2P3/CMP1D/CMP2B/RP32/RB0         AN4/CMP2C/RP41/RB9         AN5/CMP2D/RP42/RB10         Vss                                                                                                      | Pin           15           16           17           18           19           20           21           22                                        | Pin Function           PGEC3/RP47/RB15           TDO/AN9/PGA2N2/RP37/RB5           PGED1/TDI/AN10/SCL1/RP38/RB6           PGEC1/AN11/SDA1/RP39/RB7           Vss           VCAP           TMS/PWM3H/RP43/RB11           TCK/PWM3L/RP44/RB12                                                                         |

| Pin 1 2 3 4 5 6 7 8 9                                                                                                                     | JNCTION DESCRIPTIONS         Pin Function         MCLR         AN0/PGA1P1/CMP1A/RA0         AN1/PGA1P2/PGA2P1/CMP1B/RA1         AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2         AN3/PGA2P3/CMP1D/CMP2B/RP32/RB0         AN4/CMP2C/RP41/RB9         AN5/CMP2D/RP42/RB10         Vss         OSC1/CLKI/AN6/RP33/RB1                                          | Pin           15           16           17           18           19           20           21           22           23                           | Pin Function           PGEC3/RP47/RB15           TDO/AN9/PGA2N2/RP37/RB5           PGED1/TDI/AN10/SCL1/RP38/RB6           PGEC1/AN11/SDA1/RP39/RB7           Vss           VcAP           TMS/PWM3H/RP43/RB11           TCK/PWM3L/RP44/RB12           PWM2H/RP45/RB13                                               |

| Pin           1           2           3           4           5           6           7           8           9           10              | Pin Function         MCLR         AN0/PGA1P1/CMP1A/RA0         AN1/PGA1P2/PGA2P1/CMP1B/RA1         AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2         AN3/PGA2P3/CMP1D/CMP2B/RP32/RB0         AN4/CMP2C/RP41/RB9         AN5/CMP2D/RP42/RB10         Vss         OSC1/CLKI/AN6/RP33/RB1         OSC2/CLKO/AN7/PGA1N2/RP34/RB2                                 | Pin           15           16           17           18           19           20           21           22           23           24              | Pin Function           PGEC3/RP47/RB15           TDO/AN9/PGA2N2/RP37/RB5           PGED1/TDI/AN10/SCL1/RP38/RB6           PGEC1/AN11/SDA1/RP39/RB7           Vss           Vcap           TMS/PWM3H/RP43/RB11           TCK/PWM3L/RP44/RB12           PWM2H/RP45/RB13           PWM2L/RP46/RB14                     |

| Pin           1           2           3           4           5           6           7           8           9           10           11 | Pin Function         MCLR         AN0/PGA1P1/CMP1A/RA0         AN1/PGA1P2/PGA2P1/CMP1B/RA1         AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2         AN3/PGA2P3/CMP1D/CMP2B/RP32/RB0         AN4/CMP2C/RP41/RB9         AN5/CMP2D/RP42/RB10         Vss         OSC1/CLKI/AN6/RP33/RB1         OSC2/CLKO/AN7/PGA1N2/RP34/RB2         PGED2/AN8/INT0/RP35/RB3 | Pin           15           16           17           18           19           20           21           22           23           24           25 | Pin Function           PGEC3/RP47/RB15           TDO/AN9/PGA2N2/RP37/RB5           PGED1/TDI/AN10/SCL1/RP38/RB6           PGEC1/AN11/SDA1/RP39/RB7           Vss           VCAP           TMS/PWM3H/RP43/RB11           TCK/PWM3L/RP44/RB12           PWM2H/RP45/RB13           PWM2L/RP46/RB14           PWM1H/RA4 |

Legend: Shaded pins are up to 5 VDC tolerant.

Note: RPn represents remappable peripheral functions. See Table 10-1 and Table 10-2 for the complete list of remappable sources.

### TABLE 4-14: ADC REGISTER MAP

| File<br>Name | Addr. | Bit 15  | Bit 14   | Bit 13  | Bit 12  | Bit 11  | Bit 10       | Bit 9     | Bit 8     | Bit 7         | Bit 6    | Bit 5     | Bit 4     | Bit 3     | Bit 2        | Bit 1     | Bit 0     | All<br>Resets |

|--------------|-------|---------|----------|---------|---------|---------|--------------|-----------|-----------|---------------|----------|-----------|-----------|-----------|--------------|-----------|-----------|---------------|

| ADCON1L      | 0300  | ADON    | _        | ADSIDL  | _       | _       | _            | _         | _         | —             | _        | _         | -         | -         | -            | _         | -         | 1000          |

| ADCON1H      | 0302  | _       | _        | _       | _       | _       | _            | _         | _         | FORM          | SHRRES1  | SHRRES0   | -         | _         | _            | _         | -         | 0060          |

| ADCON2L      | 0304  | REFCIE  | REFERCIE | _       | EIEN    | _       | SHREISEL2    | SHREISEL1 | SHREISEL0 | _             | SHRADCS6 | SHRADCS5  | SHRADCS4  | SHRADCS3  | SHRADCS2     | SHRADCS1  | SHRADCS0  | 0000          |

| ADCON2H      | 0306  | REFRDY  | REFERR   | _       | _       | _       | _            | SHRSAMC9  | SHRSAMC8  | SHRSAMC7      | SHRSAMC6 | SHRSAMC5  | SHRSAMC4  | SHRSAMC3  | SHRSAMC2     | SHRSAMC1  | SHRSAMC0  | 0000          |

| ADCON3L      | 0308  | REFSEL2 | REFSEL1  | REFSEL0 | SUSPEND | SUSPCIE | SUSPRDY      | SHRSAMP   | CNVRTCH   | SWLCTRG       | SWCTRG   | CNVCHSEL5 | CNVCHSEL4 | CNVCHSEL3 | CNVCHSEL2    | CNVCHSEL1 | CNVCHSEL0 | 0000          |

| ADCON3H      | 030A  | CLKSEL1 | CLKSEL0  | CLKDIV5 | CLKDIV4 | CLKDIV3 | CLKDIV2      | CLKDIV1   | CLKDIV0   | SHREN         |          | _         | -         | —         | -            | C1EN      | COEN      | 0000          |

| ADCON4L      | 030C  | _       | _        | —       | _       | -       | -            | SYNCTRG1  | SYNCTRG0  | _             | -        | _         | -         | _         | _            | SAMC1EN   | SAMC0EN   | 0000          |

| ADCON4H      | 030E  | _       | -        | _       | _       | _       | _            | -         | -         | _             | -        | _         | _         | C1CHS1    | C1CHS0       | C0CHS1    | C0CHS0    | 0000          |

| ADMOD0L      | 0310  | -       | SIGN7    | —       | SIGN6   | -       | SIGN5        | _         | SIGN4     | _             | SIGN3    | _         | SIGN2     | DIFF1     | SIGN1        | DIFF0     | SIGN0     | 0000          |

| ADMOD0H      | 0312  | _       | _        | DIFF14  | SIGN14  | -       | SIGN13       | -         | SIGN12    | _             | SIGN11   | —         | SIGN10    | _         | SIGN9        | —         | SIGN8     | 0000          |

| ADIEL        | 0320  | -       | IE14     | —       | _       |         |              |           |           |               | IE·      | <11:0     |           |           |              |           |           | 0000          |

| ADSTATL      | 0330  | -       | AN14RDY  | —       | _       | AN11RDY | AN10RDY      | AN9RDY    | AN8RDY    | AN7RDY        | AN6RDY   | AN5RDY    | AN4RDY    | AN3RDY    | AN2RDY       | AN1RDY    | ANORDY    | 0000          |

| ADCMP0ENL    | 0338  | -       | CMPEN14  | —       | _       |         |              |           |           |               | CMPE     | N<11:0>   |           |           |              |           |           | 0000          |

| ADCMP0LO     | 033C  |         |          |         |         |         |              |           | ADC (     | CMPLO Registe | er       |           |           |           |              |           |           | 0000          |

| ADCMP0HI     | 033E  |         |          |         |         |         |              |           | ADC       | CMPHI Registe | er       |           |           |           |              |           |           | 0000          |

| ADCMP1ENL    | 0340  | -       | CMPEN14  | —       | _       |         |              |           |           |               | CMPE     | N<11:0>   |           |           |              |           |           | 0000          |

| ADCMP1LO     | 0344  |         |          |         |         |         |              |           | ADC (     | CMPLO Registe | er       |           |           |           |              |           |           | 0000          |

| ADCMP1HI     | 0346  |         |          |         |         |         |              |           | ADC       | CMPHI Registe | er       |           |           |           |              |           |           | 0000          |

| ADFL0DAT     | 0368  |         |          | -       | -       |         | -            |           | ADC F     | LDATA Regist  | er       | -         | -         |           | -            |           |           | 0000          |

| ADFL0CON     | 036A  | FLEN    | MODE1    | MODE0   | OVRSAM2 | OVRSAM1 | OVRSAM0      | IE        | RDY       | _             | -        | _         | FLCHSEL4  | FLCHSEL3  | FLCHSEL2     | FLCHSEL1  | FLCHSEL0  | 0000          |

| ADTRIG0L     | 0380  | _       | _        | —       |         |         | TRGSRC1<4:0  | >         |           | _             | -        | _         |           |           | TRGSRC0<4:0> | ,         |           | 0000          |

| ADTRIG0H     | 0382  | _       | _        | —       |         |         | TRGSRC3<4:0  | >         |           | _             | -        | _         |           |           | TRGSRC2<4:0> |           |           | 0000          |

| ADTRIG1L     | 0384  | -       | -        | _       |         |         | TRGSRC5<4:0  | >         |           | _             | -        | _         |           |           | TRGSRC4<4:0> | •         |           | 0000          |

| ADTRIG1H     | 0386  | _       | _        | —       |         |         | TRGSRC7<4:0  | >         |           | _             | -        | _         |           |           | TRGSRC6<4:0> |           |           | 0000          |

| ADTRIG2L     | 0388  | _       | _        | —       |         |         | TRGSRC9<4:0  | >         |           | _             | -        | _         |           |           | TRGSRC8<4:0> |           |           | 0000          |

| ADTRIG2H     | 038A  | -       | -        | _       |         |         | TRGSRC11<4:0 | >         |           | _             | -        | _         |           |           | TRGSRC10<4:0 | >         |           | 0000          |

| ADTRIG3L     | 038C  | -       | -        | _       |         |         | TRGSRC13<4:0 | >         |           | _             | -        | _         |           |           | TRGSRC12<4:0 | >         |           | 0000          |

| ADTRIG3H     | 038E  | -       | -        | _       | _       | -       | _            | -         | -         | _             | -        | _         |           |           | TRGSRC14<4:0 | >         |           | 0000          |

| ADCMP0CON    | 03A0  | -       | -        | _       | CHNL4   | CHNL3   | CHNL2        | CHNL1     | CHNL0     | CMPEN         | IE       | STAT      | BTWN      | HIHI      | HILO         | LOHI      | LOLO      | 0000          |

| ADCMP1CON    | 03A4  | _       |          | _       | CHNL4   | CHNL3   | CHNL2        | CHNL1     | CHNL0     | CMPEN         | E        | STAT      | BTWN      | HIHI      | HILO         | LOHI      | LOLO      | 0000          |

| ADLVLTRGL    | 03D0  | -       | LVLEN14  | —       | _       |         |              |           |           |               | LVLE     | N<11:0>   |           |           |              |           |           | 0000          |

| ADCORE0L     | 03D4  | —       |          | _       | _       | _       | _            |           |           |               |          | SAM       | IC<9:0>   |           |              |           |           | 0000          |

| ADCORE0H     | 03D6  | _       | -        | _       | EISEL2  | EISEL1  | EISEL0       | RES1      | RES0      | _             | ADCS6    | ADCS5     | ADCS4     | ADCS3     | ADCS2        | ADCS1     | ADCS0     | 0000          |

| ADCORE1L     | 03D8  | _       | -        | _       | _       | _       | _            |           |           |               |          | SAM       | IC<9:0>   |           |              |           |           | 0000          |

| ADCORE1H     | 03DA  | _       |          | _       | EISEL2  | EISEL1  | EISEL0       | RES1      | RES0      | —             | ADCS6    | ADCS5     | ADCS4     | ADCS3     | ADCS2        | ADCS1     | ADCS0     | 0000          |

| ADEIEL       | 03F0  | _       | EIEN14   | _       | —       |         |              |           |           |               | EIEI     | N<11:0    |           |           |              |           |           | 0000          |

| ADEISTATL    | 03F8  | _       | EISTAT14 | _       | _       |         |              |           |           |               | EISTA    | T<11:0>   |           |           |              |           |           | 0000          |

dsPIC33EPXXGS202 FAMILY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts" (DS70000600) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXGS202 family interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33EPXXGS202 family CPU.

The interrupt controller has the following features:

- Six Processor Exceptions and Software Traps

- Seven User-Selectable Priority Levels

- Interrupt Vector Table (IVT) with a Unique Vector for each Interrupt or Exception Source

- Fixed Priority within a Specified User Priority Level

- Fixed Interrupt Entry and Return Latencies

- Alternate Interrupt Vector Table (AIVT) for Debug Support

## 7.1 Interrupt Vector Table

The dsPIC33EPXXGS202 family Interrupt Vector Table (IVT), shown in Figure 7-1, resides in program memory, starting at location, 000004h. The IVT contains six non-maskable trap vectors and up to fifty sources of interrupts. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

#### 7.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT), shown in Figure 7-2, is available only when the Boot Segment (BS) is defined and the AIVT has been enabled. To enable the Alternate Interrupt Vector Table, the Configuration bit, AIVTDIS in the FSEC register, must be programmed and the AIVTEN bit must be set (INTCON2<8> = 1). When the AIVT is enabled, all interrupt and exception processes use the alternate vectors instead of the default vectors. The AIVT begins at the start of the last page of the Boot Segment, defined by BSLIM<12:0>. The second half of the page is no longer usable space. The Boot Segment must be at least 2 pages to enable the AIVT.

Note: Although the Boot Segment must be enabled in order to enable the AIVT, application code does not need to be present inside of the Boot Segment. The AIVT (and IVT) will inherit the Boot Segment code protection.

The AIVT supports debugging by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time.

## 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33EPXXGS202 family devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

## 8.1 CPU Clocking System

The dsPIC33EPXXGS202 family of devices provides six system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with Phase-Locked Loop (PLL)

- FRC Oscillator with Postscaler

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- Low-Power RC (LPRC) Oscillator

Instruction execution speed or device operating frequency, FCY, is given by Equation 8-1.

### EQUATION 8-1: DEVICE OPERATING FREQUENCY

#### FCY = FOSC/2

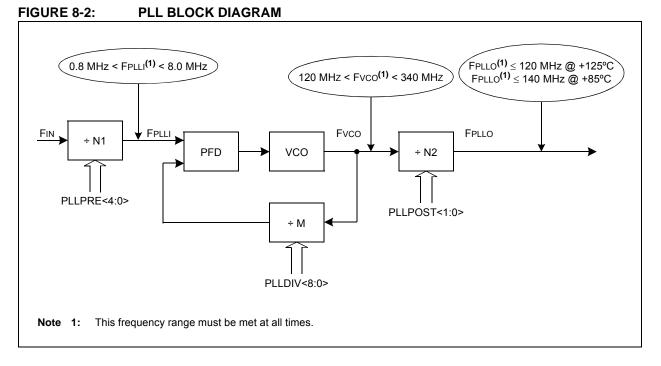

Figure 8-2 is a block diagram of the PLL module.

Equation 8-2 provides the relationship between input frequency (FIN) and output frequency (FPLLO).

Equation 8-3 provides the relationship between input frequency (FIN) and VCO frequency (Fvco).

## EQUATION 8-2: FPLLO CALCULATION

$$FPLLO = FIN \times \left(\frac{M}{N1 \times N2}\right) = FIN \times \left(\frac{(PLLDIV < 8:0 > + 2)}{(PLLPRE < 4:0 > + 2) \times 2(PLLPOST < 1:0 > + 1)}\right)$$

Where: N1 = PLLPRE<4:0> + 2 N2 = 2 x (PLLPOST<1:0> + 1) M = PLLDIV<8:0> + 2

## EQUATION 8-3: Fvco CALCULATION

$$FVCO = FIN \times \left(\frac{M}{N1}\right) = FIN \times \left(\frac{(PLLDIV < 8:0 > + 2)}{(PLLPRE < 4:0 > + 2)}\right)$$

### REGISTER 9-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|---------|-----|-----|-----|-----|-----|-----|-------|

| _       | —   | —   | —   | —   | —   | _   | IC1MD |

| bit 15  |     | •   |     | •   | •   |     | bit 8 |

|         |     |     |     |     |     |     |       |

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

| _       | —   | —   | —   | —   | —   | —   | OC1MD |

| bit 7   |     |     |     |     |     |     | bit 0 |

|         |     |     |     |     |     |     |       |

| Legend: |     |     |     |     |     |     |       |

| Legend:           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 15-9 | Unimplemented: Read as '0'                                                                                                             |

|----------|----------------------------------------------------------------------------------------------------------------------------------------|

| bit 8    | IC1MD: Input Capture 1 Module Disable bit                                                                                              |

|          | <ol> <li>1 = Input Capture 1 module is disabled</li> <li>0 = Input Capture 1 module is enabled</li> </ol>                              |

| bit 7-1  | Unimplemented: Read as '0'                                                                                                             |

| bit 0    | <b>OC1MD:</b> Output Compare 1 Module Disable bit<br>1 = Output Compare 1 module is disabled<br>0 = Output Compare 1 module is enabled |

### REGISTER 9-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-------|-----|-------|

| —      | —   | —   | —   | —   | CMPMD | —   | —     |

| bit 15 |     |     | •   |     | •     |     | bit 8 |

|        |     |     |     |     |       |     |       |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0   | U-0 | U-0   |

| —      | _   | —   | —   | —   | —     | —   | —     |

| bit 7  |     |     |     |     |       |     | bit 0 |

|        |     |     |     |     |       |     |       |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-11 Unimplemented: Read as '0'

bit 10 CMPMD: Comparator Module Disable bit

1 = Comparator module is disabled

0 = Comparator module is enabled

bit 9-0 Unimplemented: Read as '0'

NOTES:

#### REGISTER 15-1: PTCON: PWM TIME BASE CONTROL REGISTER

| R/W-0  | U-0 | R/W-0  | HS/HC-0 | R/W-0 | R/W-0               | R/W-0                  | R/W-0                  |

|--------|-----|--------|---------|-------|---------------------|------------------------|------------------------|

| PTEN   | —   | PTSIDL | SESTAT  | SEIEN | EIPU <sup>(1)</sup> | SYNCPOL <sup>(1)</sup> | SYNCOEN <sup>(1)</sup> |

| bit 15 |     |        |         |       |                     |                        | bit 8                  |

| R/W-0                 | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-----------------------|-------------------------|-------------------------|-------------------------|------------------------|------------------------|------------------------|------------------------|

| SYNCEN <sup>(1)</sup> | SYNCSRC2 <sup>(1)</sup> | SYNCSRC1 <sup>(1)</sup> | SYNCSRC0 <sup>(1)</sup> | SEVTPS3 <sup>(1)</sup> | SEVTPS2 <sup>(1)</sup> | SEVTPS1 <sup>(1)</sup> | SEVTPS0 <sup>(1)</sup> |

| bit 7                 |                         |                         |                         |                        |                        |                        | bit 0                  |

| Legend:    |                                                          | HC = Hardware Clearable b                                                | it HS = Hardware Settab          | le bit             |  |  |  |  |  |  |

|------------|----------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------|--------------------|--|--|--|--|--|--|

| R = Reada  | able bit                                                 | W = Writable bit                                                         | U = Unimplemented bit            | t, read as '0'     |  |  |  |  |  |  |

| -n = Value | at POR                                                   | '1' = Bit is set                                                         | '0' = Bit is cleared             | x = Bit is unknown |  |  |  |  |  |  |

| bit 15     |                                                          | VM Module Enable bit                                                     |                                  |                    |  |  |  |  |  |  |

|            |                                                          | module is enabled<br>module is disabled                                  |                                  |                    |  |  |  |  |  |  |

| bit 14     | Unimplen                                                 | nented: Read as '0'                                                      |                                  |                    |  |  |  |  |  |  |

| bit 13     | PTSIDL:                                                  | PWM Time Base Stop in Idle Moo                                           | de bit                           |                    |  |  |  |  |  |  |

|            |                                                          | time base halts in CPU Idle mod time base runs in CPU Idle mode          |                                  |                    |  |  |  |  |  |  |

| bit 12     | SESTAT:                                                  | Special Event Interrupt Status bit                                       |                                  |                    |  |  |  |  |  |  |

|            |                                                          | al event interrupt is pending<br>al event interrupt is not pending       |                                  |                    |  |  |  |  |  |  |

| bit 11     | SEIEN: S                                                 | pecial Event Interrupt Enable bit                                        |                                  |                    |  |  |  |  |  |  |

|            |                                                          | al event interrupt is enabled<br>al event interrupt is disabled          |                                  |                    |  |  |  |  |  |  |

| bit 10     | EIPU: Enable Immediate Period Updates bit <sup>(1)</sup> |                                                                          |                                  |                    |  |  |  |  |  |  |

|            |                                                          | Period register is updated imme<br>Period register updates occur of      |                                  |                    |  |  |  |  |  |  |

| bit 9      | SYNCPO                                                   | L: Synchronize Input and Output                                          | Polarity bit <sup>(1)</sup>      |                    |  |  |  |  |  |  |

|            |                                                          | Ix/SYNCO1 polarity is inverted (a<br>Ix/SYNCO1 is active-high            | active-low)                      |                    |  |  |  |  |  |  |

| bit 8      | SYNCOE                                                   | N: Primary Time Base Synchroni                                           | zation Enable bit <sup>(1)</sup> |                    |  |  |  |  |  |  |

|            |                                                          | O1 output is enabled<br>O1 output is disabled                            |                                  |                    |  |  |  |  |  |  |

| bit 7      | SYNCEN:                                                  | External Time Base Synchroniz                                            | ation Enable bit <sup>(1)</sup>  |                    |  |  |  |  |  |  |

|            |                                                          | nal synchronization of primary tim<br>nal synchronization of primary tim |                                  |                    |  |  |  |  |  |  |

| bit 6-4    | SYNCSR                                                   | C<2:0>: Synchronous Source Se                                            | lection bits <sup>(1)</sup>      |                    |  |  |  |  |  |  |

|            | -                                                        | 111 = Reserved                                                           |                                  |                    |  |  |  |  |  |  |

|            | 101 = Re:                                                |                                                                          |                                  |                    |  |  |  |  |  |  |

|            | 100 = Re:<br>011 = Re:                                   |                                                                          |                                  |                    |  |  |  |  |  |  |

|            | 011 = Re:<br>010 = Re:                                   |                                                                          |                                  |                    |  |  |  |  |  |  |

|            | 001 = SY                                                 |                                                                          |                                  |                    |  |  |  |  |  |  |

|            | 000 = SY                                                 | NCI1                                                                     |                                  |                    |  |  |  |  |  |  |

**Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCIx feature, the user application must program the Period register with a value that is slightly larger than the expected period of the external synchronization input signal.

### **REGISTER 15-13: PDCx: PWMx GENERATOR DUTY CYCLE REGISTER**<sup>(1,2,3)</sup>

| R/W-0                                                                      | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0           | R/W-0    | R/W-0 |

|----------------------------------------------------------------------------|-------|----------------|-------|--------------|-----------------|----------|-------|

|                                                                            |       |                | PDC   | x<15:8>      |                 |          |       |

| bit 15                                                                     |       |                |       |              |                 |          | bit 8 |

|                                                                            |       |                |       |              |                 |          |       |

| R/W-0                                                                      | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0           | R/W-0    | R/W-0 |

|                                                                            |       |                | PDC   | \$x<7:0>     |                 |          |       |

| bit 7                                                                      |       |                |       |              |                 |          | bit 0 |

|                                                                            |       |                |       |              |                 |          |       |

| Legend:                                                                    |       |                |       |              |                 |          |       |

| R = Readable                                                               | bit   | W = Writable b | bit   | U = Unimplen | nented bit, rea | d as '0' |       |

| -n = Value at POR (1' = Bit is set (0' = Bit is cleared x = Bit is unknown |       |                |       |              | nown            |          |       |

bit 15-0 PDCx<15:0>: PWMx Generator Duty Cycle Value bits

**Note 1:** In Independent PWM mode, the PDCx register controls the PWMxH duty cycle only. In the Complementary, Redundant and Push-Pull PWM modes, the PDCx register controls the duty cycle of both the PWMxH and PWMxL.

**2:** The smallest pulse width that can be generated on the PWMx output corresponds to a value of 0x0008, while the maximum pulse width generated corresponds to a value of Period – 0x0008.

**3:** As the duty cycle gets closer to 0% or 100% of the PWM period (0 to 40 ns, depending on the mode of operation), PWM duty cycle resolution will increase from 1 to 3 LSBs.

### REGISTER 15-14: SDCx: PWMx SECONDARY DUTY CYCLE REGISTER<sup>(1,2,3)</sup>

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |

|-----------------------------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|

|                                   |       |                  | SDC   | x<15:8>                            |       |                 |       |

| bit 15                            |       |                  |       |                                    |       |                 | bit 8 |

|                                   |       |                  |       |                                    |       |                 |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |

|                                   |       |                  | SDC   | \$x<7:0>                           |       |                 |       |

| bit 7                             |       |                  |       |                                    |       |                 | bit 0 |

|                                   |       |                  |       |                                    |       |                 |       |

| Legend:                           |       |                  |       |                                    |       |                 |       |

| R = Readable bit W = Writable bit |       |                  | bit   | U = Unimplemented bit, read as '0' |       |                 |       |

| -n = Value at POR                 |       | '1' = Bit is set |       | '0' = Bit is cle                   | ared  | x = Bit is unki | nown  |

|                                   |       |                  |       |                                    |       |                 |       |

bit 15-0 SDCx<15:0>: Secondary Duty Cycle for PWMxL Output Pin bits

**Note 1:** The SDCx register is used in Independent PWM mode only. When used in Independent PWM mode, the SDCx register controls the PWMxL duty cycle.

**2:** The smallest pulse width that can be generated on the PWM output corresponds to a value of 0x0008, while the maximum pulse width generated corresponds to a value of Period – 0x0008.

**3:** As the duty cycle gets closer to 0% or 100% of the PWM period (0 to 40 ns, depending on the mode of operation), PWM duty cycle resolution will increase from 1 to 3 LSBs.

## REGISTER 15-24: LEBCONX: PWMx LEADING-EDGE BLANKING (LEB) CONTROL REGISTER (CONTINUED)

- bit 1

BPLH: Blanking in PWMxL High Enable bit

1 = State blanking (of current-limit and/or Fault input signals) when the PWMxL output is high

bit 0

BPLL: Blanking in PWMxL Low Enable bit

1 = State blanking (of current-limit and/or Fault input signals) when the PWMxL output is low

0 = No blanking when the PWMxL Low Enable bit

1 = State blanking (of current-limit and/or Fault input signals) when the PWMxL output is low

0 = No blanking when the PWMxL output is low

- **Note 1:** The blanking signal is selected via the BLANKSEL<3:0> bits in the AUXCONx register.

### REGISTER 15-25: LEBDLYx: PWMx LEADING-EDGE BLANKING DELAY REGISTER

| U-0                                | U-0   | U-0      | U-0                                     | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|------------------------------------|-------|----------|-----------------------------------------|-------|-------|-------|-------|

| —                                  | —     | _        | _                                       |       | LEB   | <8:5> |       |

| bit 15                             |       |          |                                         |       |       |       | bit 8 |

|                                    |       |          |                                         |       |       |       |       |

| R/W-0                              | R/W-0 | R/W-0    | R/W-0                                   | R/W-0 | U-0   | U-0   | U-0   |

|                                    |       | LEB<4:0> |                                         |       | —     | —     | —     |

| bit 7                              |       |          |                                         |       |       |       | bit 0 |

|                                    |       |          |                                         |       |       |       |       |

| Legend:                            |       |          |                                         |       |       |       |       |

| R = Readable bit W = Writable bit  |       |          | U = Unimplemented bit, read as '0'      |       |       |       |       |

| -n = Value at POR '1' = Bit is set |       |          | '0' = Bit is cleared x = Bit is unknown |       |       |       |       |

bit 15-12 Unimplemented: Read as '0'

bit 11-3 **LEB<8:0>:** Leading-Edge Blanking Delay for Current-Limit and Fault Inputs bits The value is in 8.32 ns increments.

bit 2-0 Unimplemented: Read as '0'

NOTES:

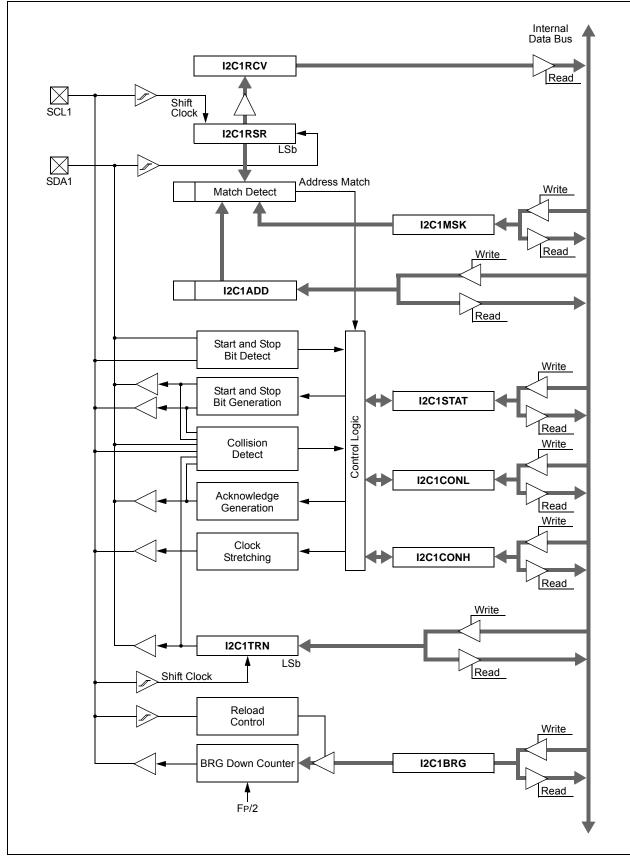

## FIGURE 17-1: I2C1 BLOCK DIAGRAM

| REGISTER 17-2: I2 | 2C1CONH: I2C1 CONTROL | REGISTER HIGH |

|-------------------|-----------------------|---------------|

|-------------------|-----------------------|---------------|

| REGISTER 17-2: I2C1CONH: I2C1 CONTROL REGISTER HIGH |                                                 |                                                                                                                                                                                                            |                              |                                |                  |                  |                 |  |  |  |  |

|-----------------------------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------------|------------------|------------------|-----------------|--|--|--|--|

| U-0                                                 | U-0                                             | U-0                                                                                                                                                                                                        | U-0                          | U-0                            | U-0              | U-0              | U-0             |  |  |  |  |

|                                                     |                                                 |                                                                                                                                                                                                            | _                            |                                | —                | _                | _               |  |  |  |  |

| bit 15                                              |                                                 |                                                                                                                                                                                                            |                              |                                |                  |                  | bit 8           |  |  |  |  |

| U-0                                                 | R/W-0                                           | R/W-0                                                                                                                                                                                                      | R/W-0                        | R/W-0                          | R/W-0            | R/W-0            | R/W-0           |  |  |  |  |

| _                                                   | PCIE                                            | SCIE                                                                                                                                                                                                       | BOEN                         | SDAHT                          | SBCDE            | AHEN             | DHEN            |  |  |  |  |

| bit 7                                               |                                                 |                                                                                                                                                                                                            |                              |                                |                  |                  | bit 0           |  |  |  |  |

| Legend:                                             |                                                 |                                                                                                                                                                                                            |                              |                                |                  |                  |                 |  |  |  |  |

| R = Reada                                           | ble bit                                         | W = Writable                                                                                                                                                                                               | oit                          | U = Unimplem                   | ented bit, read  | as '0'           |                 |  |  |  |  |

| -n = Value                                          | at POR                                          | '1' = Bit is set                                                                                                                                                                                           |                              | '0' = Bit is clea              | ired             | x = Bit is unkr  | nown            |  |  |  |  |

|                                                     |                                                 |                                                                                                                                                                                                            |                              |                                |                  |                  |                 |  |  |  |  |

| bit 15-7                                            | -                                               | nted: Read as '                                                                                                                                                                                            |                              | 0                              |                  |                  |                 |  |  |  |  |

| bit 6                                               | •                                               |                                                                                                                                                                                                            |                              | I <sup>2</sup> C Slave mode    | only)            |                  |                 |  |  |  |  |

|                                                     |                                                 | interrupt on dete<br>ection interrupts                                                                                                                                                                     |                              | condition                      |                  |                  |                 |  |  |  |  |

| bit 5                                               |                                                 |                                                                                                                                                                                                            |                              | I <sup>2</sup> C Slave mode    | onlv)            |                  |                 |  |  |  |  |

|                                                     |                                                 |                                                                                                                                                                                                            | -                            | or Restart condi               | • ·              |                  |                 |  |  |  |  |

|                                                     | 0 = Start det                                   | ection interrupts                                                                                                                                                                                          | are disabled                 |                                |                  |                  |                 |  |  |  |  |

| bit 4                                               | BOEN: Buffe                                     | er Overwrite Ena                                                                                                                                                                                           | ble bit (I <sup>2</sup> C SI | ave mode only)                 |                  |                  |                 |  |  |  |  |

|                                                     |                                                 |                                                                                                                                                                                                            |                              | enerated for a ree             | ceived address   | /data byte, igno | oring the state |  |  |  |  |

|                                                     |                                                 | COV bit only if t<br>V is only update                                                                                                                                                                      |                              |                                |                  |                  |                 |  |  |  |  |

| bit 3                                               |                                                 | A1 Hold Time Se                                                                                                                                                                                            |                              |                                |                  |                  |                 |  |  |  |  |

| DIL D                                               |                                                 |                                                                                                                                                                                                            |                              | after the falling              | edge of SCI 1    |                  |                 |  |  |  |  |

|                                                     |                                                 |                                                                                                                                                                                                            |                              | after the falling              |                  |                  |                 |  |  |  |  |

| bit 2                                               | SBCDE: Sla                                      | ve Mode Bus Co                                                                                                                                                                                             | ollision Detect              | Enable bit (I <sup>2</sup> C S | Slave mode on    | ly)              |                 |  |  |  |  |

|                                                     | 1 = Enables                                     | slave bus collisi                                                                                                                                                                                          | on interrupts                |                                |                  |                  |                 |  |  |  |  |

|                                                     | 0 = Slave bus collision interrupts are disabled |                                                                                                                                                                                                            |                              |                                |                  |                  |                 |  |  |  |  |

|                                                     |                                                 | If the rising edge of SCL1 and SDA1 is sampled low when the module is in a high state, the BCL bit is set and the bus goes Idle. This Detection mode is only valid during data and ACK transmit sequences. |                              |                                |                  |                  |                 |  |  |  |  |

| bit 1                                               |                                                 | ess Hold Enable                                                                                                                                                                                            |                              | •                              |                  |                  | it sequences.   |  |  |  |  |

|                                                     |                                                 |                                                                                                                                                                                                            |                              | CL1 for a match                | ning received    | address byte.    | the SCLREL      |  |  |  |  |

|                                                     | (12C1C0                                         |                                                                                                                                                                                                            | ll be cleared a              | and SCL1 will be               |                  | <b>,</b> ,       |                 |  |  |  |  |

| bit 0                                               | DHEN: Data                                      | Hold Enable bit                                                                                                                                                                                            | (I <sup>2</sup> C Slave mo   | ode only)                      |                  |                  |                 |  |  |  |  |

|                                                     |                                                 |                                                                                                                                                                                                            |                              | 1 for a received               | l data byte, the | e slave hardwa   | are clears the  |  |  |  |  |

|                                                     |                                                 | L (I2C1CONL<1                                                                                                                                                                                              | 2>) bit and S                | CL1 is held low                |                  |                  |                 |  |  |  |  |

|                                                     | 0 = Data hol                                    | ding is disabled                                                                                                                                                                                           |                              |                                |                  |                  |                 |  |  |  |  |

|                                                     |                                                 |                                                                                                                                                                                                            |                              |                                |                  |                  |                 |  |  |  |  |

### REGISTER 19-7: ADCON4L: ADC CONTROL REGISTER 4 LOW

| -n = Value at POR '1' = Bit is    |     | '1' = Bit is set |                                    | '0' = Bit is clea | ared | x = Bit is unkno        | wn                      |

|-----------------------------------|-----|------------------|------------------------------------|-------------------|------|-------------------------|-------------------------|

| R = Readable bit W = Writable bit |     | it               | U = Unimplemented bit, read as '0' |                   |      |                         |                         |

| Legend:                           |     |                  |                                    |                   |      |                         |                         |

|                                   |     |                  |                                    |                   |      |                         | bit o                   |

| bit 7                             |     |                  |                                    |                   |      |                         | bit 0                   |

| _                                 |     | —                |                                    |                   |      | SAMC1EN                 | SAMC0EN                 |

| U-0                               | U-0 | U-0              | U-0                                | U-0               | U-0  | R/W-0                   | R/W-0                   |

|                                   |     |                  |                                    |                   |      |                         |                         |

| bit 15                            |     |                  |                                    | ·                 |      |                         | bit 8                   |

| —                                 | _   | —                | —                                  | —                 | _    | SYNCTRG1 <sup>(1)</sup> | SYNCTRG0 <sup>(1)</sup> |

| U-0                               | U-0 | U-0              | U-0                                | U-0               | U-0  | R/W-0                   | R/W-0                   |

bit 15-10 Unimplemented: Read as '0'

bit 9-8 **SYNCTRG<1:0>** Dedicated ADC Core x Trigger Synchronization bits<sup>(1)</sup> 1 = All triggers are synchronized with the Core Source Clock (TCORESRC) 0 = The ADC core triggers are not synchronized

#### bit 7-2 Unimplemented: Read as '0'

### bit 1-0 SAMC1EN:SAMC0EN: Dedicated ADC Core x Conversion Delay Enable bits

1 = After trigger, the conversion will be delayed and the ADC core will continue sampling during the time specified by the SAMC<9:0> bits in the ADCORExL register

- 0 = After trigger, the sampling will be stopped immediately and the conversion will be started on the next core clock cycle.

- **Note 1:** For proper ADC performance, this bit must be set when using level-sensitive triggers and cleared for edge-sensitive triggers.

### REGISTER 19-21: ADTRIGXH: ADC CHANNEL TRIGGER x SELECTION REGISTER HIGH (x = 0 to 3) (CONTINUED)

- bit 4-0 TRGSRC(4x+2)<4:0>: Trigger Source Selection for Corresponding Analog Inputs bits

- 11111 = ADTRG31

- 11110 = Reserved

- 11101 = Reserved

- 11100 = Reserved

- 11011 = Reserved

- 11010 = PWM Generator 3 current-limit trigger

- 11001 = PWM Generator 2 current-limit trigger

- 11000 = PWM Generator 1 current-limit trigger

- 10111 = Reserved

- 10110 = Output Compare 1 trigger

- 10101 = Reserved

- 10100 = Reserved

- 10011 = Reserved

- 10010 = Reserved

- 10001 = PWM Generator 3 secondary trigger

- 10000 = PWM Generator 2 secondary trigger

- 01111 = PWM Generator 1 secondary trigger

- 01110 = PWM secondary Special Event Trigger

- 01101 = Timer2 period match

- 01100 = Timer1 period match

- 01011 = Reserved

- 01010 = Reserved

- 01001 = Reserved

- 01000 = Reserved

- 00111 = PWM Generator 3 primary trigger

- 00110 = PWM Generator 2 primary trigger

- 00101 = PWM Generator 1 primary trigger

- 00100 = PWM Special Event Trigger

- 00011 = Reserved

- 00010 = Level software trigger

- 00001 = Common software trigger

- 00000 = No trigger is enabled

### **REGISTER 21-1: PGAxCON: PGAx CONTROL REGISTER (x = 1,2) (CONTINUED)**

- bit 2-0 GAIN<2:0>: PGAx Gain Selection bits

- 111 = Reserved

- 110 = Gain of 64 101 = Gain of 32

- 101 = Gain of 32100 = Gain of 16

- 011 = Gain of 8

- 010 = Gain of 4

- 001 = Reserved

- 000 = Reserved

## **REGISTER 21-2: PGAxCAL: PGAx CALIBRATION REGISTER (x = 1,2)**

| U-0                               | U-0                                                                     | U-0   | U-0         | U-0                                | U-0   | U-0   | U-0   |  |

|-----------------------------------|-------------------------------------------------------------------------|-------|-------------|------------------------------------|-------|-------|-------|--|

| —                                 | _                                                                       | —     | —           | —                                  | —     | —     | —     |  |

| bit 15                            |                                                                         |       |             |                                    |       |       | bit 8 |  |

|                                   |                                                                         |       |             |                                    |       |       |       |  |

| U-0                               | U-0                                                                     | R/W-0 | R/W-0       | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

| —                                 | —                                                                       |       | PGACAL<5:0> |                                    |       |       |       |  |

| bit 7                             |                                                                         |       |             |                                    |       |       | bit 0 |  |

|                                   |                                                                         |       |             |                                    |       |       |       |  |

| Legend:                           |                                                                         |       |             |                                    |       |       |       |  |

| R = Readable bit W = Writable bit |                                                                         |       | bit         | U = Unimplemented bit, read as '0' |       |       |       |  |

| -n = Value at F                   | = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknowr |       |             |                                    | nown  |       |       |  |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **PGACAL<5:0>:** PGAx Offset Calibration bits

The calibration values for PGA1 and PGA2 must be copied from Flash addresses, 0x800E48 and 0x800E4C, respectively, into these bits before the module is enabled. Refer to the Device Calibration Addresses table (Table 22-3) in **Section 22.0** "**Special Features**" for more information.

### TABLE 23-2: INSTRUCTION SET OVERVIEW

| Base<br>Instr<br># | Assembly<br>Mnemonic | Assembly Syntax |                | Description                              | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|-----------------|----------------|------------------------------------------|---------------|----------------|--------------------------|

| 1 ADD              | ADD                  | ADD             | Acc            | Add Accumulators                         | 1             | 1              | OA,OB,SA,SB              |

|                    |                      | ADD             | f              | f = f + WREG                             | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD             | f,WREG         | WREG = f + WREG                          | 1             | 1              | C,DC,N,OV,Z              |