#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 2K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C                                                                     |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep16gs202t-i-ss |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

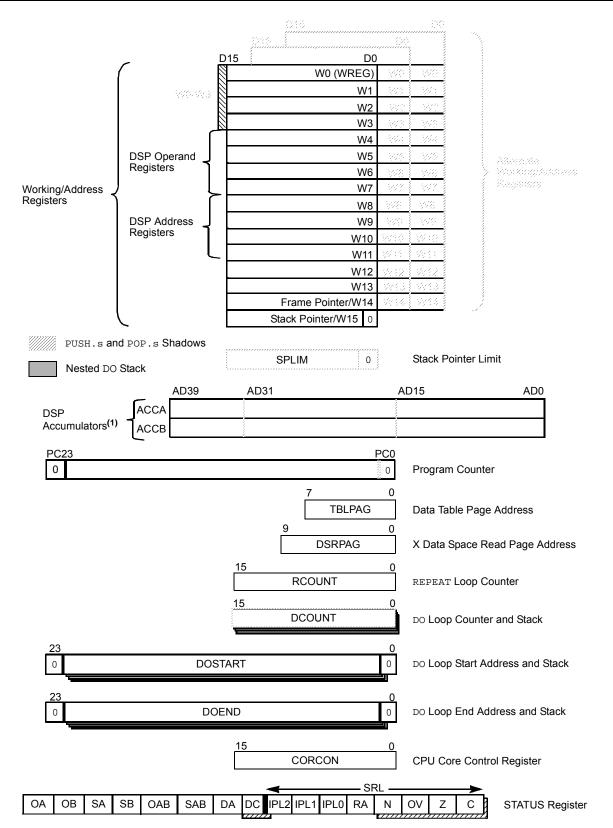

### 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

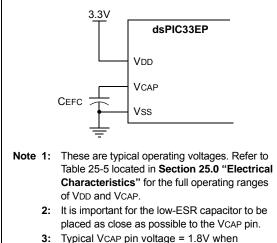

### 2.1 Basic Connection Requirements

Getting started with the dsPIC33EPXXGS202 family requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins regardless if ADC module is not used (see Section 2.2 "Decoupling Capacitors")

- VCAP (see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.5 "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used (see Section 2.6 "External Oscillator Pins")

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSs is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended to use ceramic capacitors.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, above tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

# 4.6.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions, and the DSP accumulator class of instructions, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically, only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- · Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- · Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

- Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

### 4.6.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The two-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the MAC class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

### 4.6.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

### 5.4 Flash Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 5.4.1 KEY RESOURCES

- "Flash Programming" (DS70609) in the "dsPIC33/ PIC24 Family Reference Manual",

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### 5.5 Control Registers

Five SFRs are used to write and erase the Program Flash Memory: NVMCON, NVMKEY, NVMADR, NVMADRU and NVMSRCADR.

The NVMCON register (Register 5-1) selects the operation to be performed (page erase, word/row program) and initiates the program/erase cycle.

NVMKEY (Register 5-4) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register.

There are two NVM Address registers: NVMADRU and NVMADR. These two registers, when concatenated, form the 24-bit Effective Address (EA) of the selected word/row for programming operations, or the selected page for erase operations. The NVMADRU register is used to hold the upper 8 bits of the EA, while the NVMADR register is used to hold the lower 16 bits of the EA.

For row programming operation, data to be written to Program Flash Memory is written into data memory space (RAM) at an address defined by the NVMSRCADR register (location of first element in row programming data).

## 8.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator Module" (DS70005131) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com)

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXGS202 family oscillator system provides:

- On-Chip Phase-Locked Loop (PLL) to Boost Internal Operating Frequency on Select Internal and External Oscillator Sources

- On-the-Fly Clock Switching between Various Clock Sources

- Doze mode for System Power Savings

- Fail-Safe Clock Monitor (FSCM) that Detects Clock Failure and Permits Safe Application Recovery or Shutdown

- Configuration bits for Clock Source Selection

- Auxiliary PLL for ADC and PWM

A simplified diagram of the oscillator system is shown in Figure 8-1.

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0           |

|--------|-----|--------|--------|--------|--------|--------|-----------------|

| —      | —   | RP41R5 | RP41R4 | RP41R3 | RP41R2 | RP41R1 | RP41R0          |

| bit 15 |     |        |        |        |        |        | bit 8           |

|        |     |        |        |        |        |        |                 |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0           |

|        | 00  |        |        |        | -      |        | -               |

| _      | -   | RP40R5 | RP40R4 | RP40R3 | RP40R2 | RP40R1 | RP40R0          |

|        | -   |        | RP40R4 | RP40R3 | RP40R2 | RP40R1 | RP40R0<br>bit 0 |

| Legend:           |                                                                      |                      |                    |  |  |  |

|-------------------|----------------------------------------------------------------------|----------------------|--------------------|--|--|--|

| R = Readable bit  | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                                                     | '0' = Bit is cleared | x = Bit is unknown |  |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP41R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP41 Output Pin bits (see Table 10-2 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP40R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP40 Output Pin bits (see Table 10-2 for peripheral function numbers) |

### REGISTER 10-21: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP43R5 | RP43R4 | RP43R3 | RP43R2 | RP43R1 | RP43R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP42R5 | RP42R4 | RP42R3 | RP42R2 | RP42R1 | RP42R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8**RP43R<5:0>:** Peripheral Output Function is Assigned to RP43 Output Pin bits<br/>(see Table 10-2 for peripheral function numbers)bit 7-6**Unimplemented:** Read as '0'

bit 5-0 **RP42R<5:0>:** Peripheral Output Function is Assigned to RP42 Output Pin bits (see Table 10-2 for peripheral function numbers)

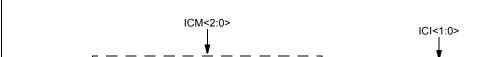

## 13.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Input Capture with Dedicated Timer" (DS70000352) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurements. The dsPIC33EPXXGS202 family devices support one input capture channel.

Key features of the input capture module include:

**FIGURE 13-1:**

Hardware-Configurable for 32-Bit Operation in all modes by Cascading Two Adjacent Modules

- Synchronous and Trigger modes of Output Compare Operation, with up to 6 User-Selectable Trigger/Sync Sources Available

- A 4-Level FIFO Buffer for Capturing and Holding Timer Values for Several Events

- Configurable Interrupt Generation

- Up to Four Clock Sources Available, Driving a Separate Internal 16-Bit Counter

### 13.1 Input Capture Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 13.1.1 KEY RESOURCES

- "Input Capture with Dedicated Timer" (DS70000352) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

INPUT CAPTURE MODULE BLOCK DIAGRAM

**Note 1:** The trigger/sync source is enabled by default and is set to Timer3 as a source. This timer must be enabled for proper IC1 module operation or the trigger/sync source must be changed to another source option.

### REGISTER 15-12: PWMCONx: PWMx CONTROL REGISTER (CONTINUED)

- bit 7-6 DTC<1:0>: Dead-Time Control bits

- 11 = Reserved

- 10 = Dead-time function is disabled

- 01 = Negative dead time is actively applied for Complementary Output mode

- 00 = Positive dead time is actively applied for all Output modes

- bit 5-4 Unimplemented: Read as '0'

- bit 3 MTBS: Master Time Base Select bit

- 1 = PWMx generator uses the secondary master time base for synchronization and the clock source for the PWMx generation logic (if secondary time base is available)

- 0 = PWMx generator uses the primary master time base for synchronization and the clock source for the PWMx generation logic

- bit 2 **CAM:** Center-Aligned Mode Enable bit<sup>(2,3,4)</sup> 1 = Center-Aligned mode is enabled

- 0 = Edge-Aligned mode is enabled

- bit 1 XPRES: External PWMx Reset Control bit<sup>(5)</sup>

- 1 = Current-limit source resets the time base for this PWMx generator if it is in Independent Time Base mode

- 0 = External pins do not affect the PWMx time base

- bit 0 IUE: Immediate Update Enable bit

- 1 = Updates to the active Duty Cycle, Phase Offset, Dead-Time and local Time Base Period registers are immediate

- 0 = Updates to the active Duty Cycle, Phase Offset, Dead-Time and local Time Base Period registers are synchronized to the local PWMx time base

- Note 1: Software must clear the interrupt status here and in the corresponding IFSx register in the interrupt controller.

- 2: The Independent Time Base mode (ITB = 1) must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored.

- 3: These bits should not be changed after the PWM is enabled by setting PTEN (PTCON<15>) = 1.

- 4: Center-Aligned mode ignores the Least Significant 3 bits of the Duty Cycle, Phase and Dead-Time registers. The highest Center-Aligned mode resolution available is 8.32 ns with the clock prescaler set to the fastest clock.

- 5: Configure CLMOD (FCLCONx<8>) = 0 and ITB (PWMCONx<9>) = 1 to operate in External Period Reset mode.

x = Bit is unknown

### **REGISTER 15-15: PHASEx: PWMx PRIMARY PHASE-SHIFT REGISTER**<sup>(1,2)</sup>

| R/W-0        | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0  | R/W-0 |

|--------------|-------|------------------|-------|--------------|------------------|--------|-------|

|              |       |                  | PHAS  | Ex<15:8>     |                  |        |       |

| bit 15       |       |                  |       |              |                  |        | bit 8 |

|              |       |                  |       |              |                  |        |       |

| R/W-0        | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0  | R/W-0 |

|              |       |                  | PHAS  | SEx<7:0>     |                  |        |       |

| bit 7        |       |                  |       |              |                  |        | bit 0 |

|              |       |                  |       |              |                  |        |       |

| Legend:      |       |                  |       |              |                  |        |       |

| R = Readable | bit   | W = Writable bit |       | U = Unimpler | nented bit, read | as '0' |       |

bit 15-0 PHASEx<15:0>: PWMx Phase-Shift Value or Independent Time Base Period for the PWMx Generator bits

**Note 1:** If PWMCONx<9> = 0, the following applies based on the mode of operation:

'1' = Bit is set

- Complementary, Redundant and Push-Pull Output mode (IOCONx<11:10> = 00, 01 or 10); PHASEx<15:0> = Phase-shift value for PWMxH and PWMxL outputs

- True Independent Output mode (IOCONx<11:10> = 11); PHASEx<15:0> = Phase-shift value for PWMxH only

- When the PHASEx/SPHASEx registers provide the phase shift with respect to the master time base; therefore, the valid range is 0x0000 through period

'0' = Bit is cleared

- **2:** If PWMCONx<9> = 1, the following applies based on the mode of operation:

- Complementary, Redundant, and Push-Pull Output mode (IOCONx<11:10> = 00, 01 or 10); PHASEx<15:0> = Independent time base period value for PWMxH and PWMxL

- True Independent Output mode (IOCONx<11:10> = 11); PHASEx<15:0> = Independent time base period value for PWMxH only

- When the PHASEx/SPHASEx registers provide the local period, the valid range is 0x0000 through 0xFFF8

-n = Value at POR

## REGISTER 15-24: LEBCONX: PWMx LEADING-EDGE BLANKING (LEB) CONTROL REGISTER

|                            | ILCI3      |                                                                                                                                                                                                   |                    |                                     |                   |                      |                  |  |  |  |  |

|----------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------------|-------------------|----------------------|------------------|--|--|--|--|

| R/W-0                      | R/W-0      | R/W-0                                                                                                                                                                                             | R/W-0              | R/W-0                               | R/W-0             | U-0                  | U-0              |  |  |  |  |

| PHR                        | PHF        | PLR                                                                                                                                                                                               | PLF                | FLTLEBEN                            | CLLEBEN           | —                    | _                |  |  |  |  |

| bit 15                     |            |                                                                                                                                                                                                   |                    |                                     |                   |                      | bit 8            |  |  |  |  |

|                            |            |                                                                                                                                                                                                   |                    |                                     |                   |                      |                  |  |  |  |  |

| U-0                        | U-0        | R/W-0                                                                                                                                                                                             | R/W-0              | R/W-0                               | R/W-0             | R/W-0                | R/W-0            |  |  |  |  |

| _                          | —          | BCH <sup>(1)</sup>                                                                                                                                                                                | BCL <sup>(1)</sup> | BPHH                                | BPHL              | BPLH                 | BPLL             |  |  |  |  |

| bit 7                      |            |                                                                                                                                                                                                   |                    |                                     |                   |                      | bit 0            |  |  |  |  |

|                            |            |                                                                                                                                                                                                   |                    |                                     |                   |                      |                  |  |  |  |  |

| Legend:                    | la hit     |                                                                                                                                                                                                   | L:1                |                                     | nonted bit read   | aa (0)               |                  |  |  |  |  |

| R = Readab<br>-n = Value a |            | W = Writable<br>'1' = Bit is set                                                                                                                                                                  |                    | 0 = Unimpler<br>'0' = Bit is cle    | nented bit, read  | x = Bit is unkr      | 201/12           |  |  |  |  |

|                            | IL FOR     | I – DILISSEL                                                                                                                                                                                      |                    |                                     | aleu              | X - DILIS UNKI       | IOWII            |  |  |  |  |

| bit 15                     | PHR: PWMxH | H Rising Edge <sup>-</sup>                                                                                                                                                                        | Trigger Enab       | le bit                              |                   |                      |                  |  |  |  |  |

|                            |            |                                                                                                                                                                                                   |                    |                                     | Blanking count    | er                   |                  |  |  |  |  |

|                            |            |                                                                                                                                                                                                   |                    | sing edge of PV                     |                   |                      |                  |  |  |  |  |

| bit 14                     |            | H Falling Edge                                                                                                                                                                                    |                    |                                     |                   |                      |                  |  |  |  |  |

|                            |            |                                                                                                                                                                                                   |                    |                                     | e Blanking coun   | ter                  |                  |  |  |  |  |

| bit 13                     | -          | _ Rising Edge T                                                                                                                                                                                   | -                  | alling edge of P\                   |                   |                      |                  |  |  |  |  |

| DIL 15                     |            |                                                                                                                                                                                                   |                    |                                     | Blanking count    | ≏r                   |                  |  |  |  |  |

|                            | Ų          | 0                                                                                                                                                                                                 | 00                 | sing edge of PV                     | U U               | 51                   |                  |  |  |  |  |

| bit 12                     | PLF: PWMxL | . Falling Edge T                                                                                                                                                                                  | rigger Enabl       | e bit                               |                   |                      |                  |  |  |  |  |

|                            | •          | •                                                                                                                                                                                                 |                    | • •                                 | Blanking count    | er                   |                  |  |  |  |  |

| 1.11.4.4                   | -          |                                                                                                                                                                                                   | -                  | alling edge of P                    |                   |                      |                  |  |  |  |  |

| bit 11                     |            | •                                                                                                                                                                                                 | • •                | anking Enable I<br>the selected Fai |                   |                      |                  |  |  |  |  |

|                            |            |                                                                                                                                                                                                   |                    | to the selected Par                 |                   |                      |                  |  |  |  |  |

| bit 10                     | CLLEBEN: C | Current-Limit Le                                                                                                                                                                                  | ading-Edge I       | Blanking Enable                     | e bit             |                      |                  |  |  |  |  |

|                            |            |                                                                                                                                                                                                   |                    | the selected cur                    |                   |                      |                  |  |  |  |  |

|                            |            |                                                                                                                                                                                                   |                    | l to the selected                   | current-limit inp | out                  |                  |  |  |  |  |

| bit 9-6                    | -          | ted: Read as '                                                                                                                                                                                    |                    |                                     | (1)               |                      |                  |  |  |  |  |

| bit 5                      |            |                                                                                                                                                                                                   |                    | al High Enable                      |                   | le ete el blevelviou | n ainmal ia hiah |  |  |  |  |

|                            |            | <ul> <li>1 = State blanking (of current-limit and/or Fault input signals) when the selected blanking signal is high</li> <li>0 = No blanking when the selected blanking signal is high</li> </ul> |                    |                                     |                   |                      |                  |  |  |  |  |

| bit 4                      |            | -                                                                                                                                                                                                 |                    | al Low Enable b                     |                   |                      |                  |  |  |  |  |

|                            |            |                                                                                                                                                                                                   |                    |                                     | als) when the se  | elected blankin      | ig signal is low |  |  |  |  |

|                            |            | -                                                                                                                                                                                                 |                    | ing signal is low                   | ,                 |                      |                  |  |  |  |  |

| bit 3                      |            | ing in PWMxH                                                                                                                                                                                      | -                  |                                     |                   |                      |                  |  |  |  |  |

|                            |            | nking (of curren                                                                                                                                                                                  |                    |                                     | als) when the F   | WMxH output          | is high          |  |  |  |  |

| bit 2                      |            | ing in PWMxH                                                                                                                                                                                      | -                  | -                                   |                   |                      |                  |  |  |  |  |

|                            |            | -                                                                                                                                                                                                 |                    |                                     | als) when the F   | WMxH output          | is low           |  |  |  |  |

|                            |            | ing when the P                                                                                                                                                                                    |                    |                                     |                   | •                    |                  |  |  |  |  |

|                            |            |                                                                                                                                                                                                   |                    |                                     |                   |                      |                  |  |  |  |  |

Note 1: The blanking signal is selected via the BLANKSEL<3:0> bits in the AUXCONx register.

### REGISTER 15-27: PWMCAPx: PWMx PRIMARY TIME BASE CAPTURE REGISTER

| R-0              | R-0                           | R-0                        | R-0    | R-0                         | R-0                                | R-0 | R-0   |  |

|------------------|-------------------------------|----------------------------|--------|-----------------------------|------------------------------------|-----|-------|--|

|                  |                               |                            | PWMCAP | <12:5> <sup>(1,2,3,4)</sup> |                                    |     |       |  |

| bit 15           |                               |                            |        |                             |                                    |     | bit 8 |  |

|                  |                               |                            |        |                             |                                    |     |       |  |

| R-0              | R-0                           | R-0                        | R-0    | R-0                         | U-0                                | U-0 | U-0   |  |

|                  | PW                            | /MCAP<4:0> <sup>(1,2</sup> | ,3,4)  |                             | —                                  | —   | —     |  |

| bit 7            |                               |                            |        |                             |                                    |     | bit 0 |  |

|                  |                               |                            |        |                             |                                    |     |       |  |

| Legend:          |                               |                            |        |                             |                                    |     |       |  |

| R = Readable bit | Readable bit W = Writable bit |                            |        |                             | U = Unimplemented bit, read as '0' |     |       |  |

R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-3 **PWMCAP<12:0>:** Captured PWMx Time Base Value bits<sup>(1,2,3,4)</sup> The value in this register represents the captured PWMx time base value when a leading edge is detected on the current-limit input.

### bit 2-0 Unimplemented: Read as '0'

- **Note 1:** The capture feature is only available on a primary output (PWMxH).

- 2: This feature is active only after LEB processing on the current-limit input signal is complete.

- **3:** The minimum capture resolution is 8.32 ns.

- 4: This feature can be used when the XPRES bit (PWMCONx<1>) is set to '0'.

### 18.1 UART Helpful Tips

- In multi-node, direct connect UART networks, UART receive inputs react to the complementary logic level defined by the URXINV bit (U1MODE<4>), which defines the Idle state, the default of which is logic high (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a Start bit detection and will cause the first byte received, after the device has been initialized, to be invalid. To avoid this situation, the user should use a pullup or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If UR1INV = 0, use a pull-up resistor on the UxRX pin.

- b) If UR1INV = 1, use a pull-down resistor on the UxRX pin.

- 2. The first character received on a wake-up from Sleep mode, caused by activity on the U1RX pin of the UART1 module, will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock, relative to the incoming U1RX bit timing, is no longer synchronized, resulting in the first character being invalid; this is to be expected.

### 18.2 UART Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 18.2.1 KEY RESOURCES

- "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

### REGISTER 19-22: ADCAL0L: ADC CALIBRATION REGISTER 0 LOW

| bit 15         bit           R-0, HC, HS         U-0         U-0         R/W-0         R/W-0         R/W-0         R/W-0         R/W-0         CALORDY         —         —         CALOSKIP         CALODIFF         CALOEN         CALORUN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R-0, HC, HS   | U-0          | U-0                 | U-0              | R/W-0             | R/W-0              | R/W-0          | R/W-0            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------|---------------------|------------------|-------------------|--------------------|----------------|------------------|

| R-0, HC, HS       U-0       U-0       U-0       RW-0       RW-0       RW-0       RW-0       RW-0       RW-0         CALORDY       —       —       CALOSKIP       CALODIFF       CALOEN       CALORUP         bit7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CAL1RDY       | _            | —                   | _                | CAL1SKIP          | CAL1DIFF           | CAL1EN         | CAL1RUN          |

| CALORDY       —       —       CALOSKIP       CALOBIFF       CALOEN       CALORUM         bit 7       bit       bit       bit       bit         Legend:       HS = Hardware Settable bit       HC = Hardware Clearable bit       bit       Bit         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 15        | ~            |                     |                  |                   |                    |                | bit 8            |

| CALORDY       —       —       CALOSKIP       CALODIFF       CALOEN       CALORUM         bit 7       bit       bit       bit       bit       bit         Legend:       HS = Hardware Settable bit       HC = Hardware Clearable bit       Bit       bit       Bit       Settion       Setio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               | 11-0         | 11-0                | 11-0             | R/M-0             | R/M-0              | R/W/-0         | R/W-0            |

| bit 7            |               | 0-0          |                     |                  | -                 | -                  | -              | -                |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       CAL1RDY: Dedicated ADC Core 1 calibration Status Flag bit       1       = Dedicated ADC Core 1 calibration is in progress         bit 14       I = Dedicated ADC Core 1 calibration is in progress       bit 11       CAL1SKIP: Dedicated ADC Core 1 calibration Bypass bit         1       = After power-up, the dedicated ADC Core 1 will be calibrated       0 = After power-up, the dedicated ADC Core 1 will be calibrated         bit 10       CAL1DIFF: Dedicated ADC Core 1 Null be calibrated in Pseudo-Differential Input Mode Calibration bit       1 = Dedicated ADC Core 1 will be calibrated in Single-Ended Input mode         0 = Dedicated ADC Core 1 will be calibrated in Single-Ended Input mode       0 = Dedicated ADC Core 1 calibration Enable bit         1 = Dedicated ADC Core 1 calibration bits (CALXRDY, CALXSKIP, CALxDIFF and CALxRUN) can b accessed by software, the dedicated ADC Core 1 calibration cycle is started; this bit automatically cleared by hardware       0 = Dedicated ADC Core 0 Calibration Start bit         1 = If this bit is set by software, the dedicated ADC Core 1 calibrated       0 = Dedicated ADC Core 0 Calibration starts Flag bit         1 = Dedicated ADC Core 0 Calibration starts Flag bit       1 = Dedicated ADC Core 0 Calibration starts Flag bit         1 = Dedicated ADC Core 0 Calibration Start bit       1 = Dedicated ADC Core 0 Calibrati                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |              |                     |                  | OALOONI           | OALODITT           | OALULIN        | bit 0            |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       CAL1RDY: Dedicated ADC Core 1 calibration Status Flag bit       1       = Dedicated ADC Core 1 calibration is in progress         bit 14       Dedicated ADC Core 1 calibration is in progress       bit       1       CAL1SKIP: Dedicated ADC Core 1 calibration Bypass bit         1       = After power-up, the dedicated ADC Core 1 will be calibrated       0 = After power-up, the dedicated ADC Core 1 will be calibrated         bit 10       CAL1DIFF: Dedicated ADC Core 1 will be calibrated in Pseudo-Differential Input Mode Calibration bit       1 = Dedicated ADC Core 1 will be calibrated in Single-Ended Input mode         0 = Dedicated ADC Core 1 will be calibrated in Single-Ended Input mode       0 = Dedicated ADC Core 1 calibration Enable bit         1 = Dedicated ADC Core 1 calibration bits (CALxRDY, CALxSKIP, CALxDIFF and CALxRUN) can b accessed by software, the dedicated ADC Core 1 calibration cycle is started; this bit automatically cleared by hardware         0 = Dedicated ADC Core 0 calibration is in progress       0 = Dedicated ADC Core 0 Calibration starts Flag bit         1 = Dedicated ADC Core 0 Calibration starts Flag bit       1 = Dedicated ADC Core 0 Calibration starts Flag bit         1 = Dedicated ADC Core 0 Calibration starts Flag bit       1 = Dedicated ADC Core 0 Calibration starts Flag bit         1 = Dedicated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |              |                     |                  |                   |                    |                |                  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       CAL1RDY: Dedicated ADC Core 1 Calibration Status Flag bit       1 = Dedicated ADC Core 1 calibration is finished         0 = Dedicated ADC Core 1 calibration is finished       0 = Dedicated ADC Core 1 calibration is in progress         bit 14-12       Unimplemented: Read as '0'         bit 11       CAL1SKIP: Dedicated ADC Core 1 Calibration Bypass bit         1 = After power-up, the dedicated ADC Core 1 will be calibrated       0 = After power-up, the dedicated ADC Core 1 will be calibrated         bit 10       CAL1DIFF: Dedicated ADC Core 1 Pseudo-Differential Input Mode Calibration bit       1 = Dedicated ADC Core 1 will be calibrated in Single-Ended Input mode         0 = Dedicated ADC Core 1 vill be calibrated in Single-Ended Input mode       0 = Dedicated ADC Core 1 calibration bits (CALxRDY, CALxSKIP, CALxDIFF and CALxRUN) can be accessed by software         0 = Dedicated ADC Core 1 calibration bits are disabled       1 = Dedicated ADC Core 1 calibration start bit         1 = If this bit is set by software, the dedicated ADC Core 1 calibration cycle is started; this bit automatically cleared by hardware         0 = Software can start the next calibration Starts Flag bit       1 = Dedicated ADC Core 0 calibration starts Flag bit         1 = Dedicated ADC Core 0 calibration is finished       0 = Dedicated ADC Core 0 calibration starts Flag bit         1 = Dedicated ADC Core 0 calibration is finished       0 = Dedicate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | •             |              |                     |                  |                   |                    | . (0)          |                  |

| bit 15       CAL1RDY: Dedicated ADC Core 1 Calibration Status Flag bit         1 = Dedicated ADC Core 1 calibration is finished         0 = Dedicated ADC Core 1 calibration is progress         bit 14-12       Unimplemented: Read as '0'         bit 11       CAL1SKIP: Dedicated ADC Core 1 Calibration Bypass bit         1 = After power-up, the dedicated ADC Core 1 will be calibrated       0 = After power-up, the dedicated ADC Core 1 will be calibrated         bit 10       CAL1DIFF: Dedicated ADC Core 1 Pseudo-Differential Input Mode Calibration bit         1 = Dedicated ADC Core 1 will be calibrated in Pseudo-Differential Input mode         0 = Dedicated ADC Core 1 calibration Enable bit         1 = Dedicated ADC Core 1 calibration Enable bit         1 = Dedicated ADC Core 1 calibration bits (CALXRDY, CALXSKIP, CALXDIFF and CALXRUN) can be accessed by software         0 = Dedicated ADC Core 1 calibration bits are disabled         bit 8       CAL1RUN: Dedicated ADC Core 1 Calibration Status Flag bit         1 = If this bit is set by software, the dedicated ADC Core 1 calibration cycle is started; this bit automatically cleared by hardware         0 = Software can start the next calibration status Flag bit         1 = Dedicated ADC Core 0 calibration is in progress         bit 6-4       Unimplemented: Read as '0'         bit 3       CALOSKIP: Dedicated ADC Core 0 Calibration Status Flag bit         1 = Dedicated ADC Core 0 will be calibrated in Single-Ende                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |              |                     | τ                | •                 |                    |                |                  |

| <ul> <li>1 = Dedicated ADC Core 1 calibration is finished</li> <li>0 = Dedicated ADC Core 1 calibration is in progress</li> <li>bit 112</li> <li>Unimplemented: Read as '0'</li> <li>cAL1SKIP: Dedicated ADC Core 1 Calibration Bypass bit</li> <li>1 = After power-up, the dedicated ADC Core 1 will not be calibrated</li> <li>0 = After power-up, the dedicated ADC Core 1 will be calibrated</li> <li>0 = After power-up, the dedicated ADC Core 1 will be calibrated</li> <li>0 = After power-up, the dedicated ADC Core 1 will be calibrated</li> <li>0 = After power-up, the dedicated ADC Core 1 will be calibrated</li> <li>0 = Dedicated ADC Core 1 will be calibrated in Pseudo-Differential Input Mode Calibration bit</li> <li>1 = Dedicated ADC Core 1 calibration Enable bit</li> <li>1 = Dedicated ADC Core 1 calibration bits (CALXRDY, CALXSKIP, CALXDIFF and CALXRUN) can b accessed by software</li> <li>0 = Dedicated ADC Core 1 calibration bits are disabled</li> <li>bit 8</li> <li>CAL1RUN: Dedicated ADC Core 1 Calibration Start bit</li> <li>1 = 1 f this bit is set by software, the dedicated ADC Core 1 calibration cycle is started; this bit automatically cleared by hardware</li> <li>0 = Software can start the next calibration starts Flag bit</li> <li>1 = Dedicated ADC Core 0 calibration is finished</li> <li>0 = Dedicated ADC Core 0 calibration starts Flag bit</li> <li>1 = Dedicated ADC Core 0 calibration spress</li> <li>bit 6-4</li> <li>Unimplemented: Read as '0'</li> <li>bit 3</li> <li>CAL0SKIP: Dedicated ADC Core 0 Calibration Bypass bit</li> <li>1 = After power-up, the dedicated ADC Core 0 will not be calibrated</li> <li>0 = Dedicated ADC Core 0 will be calibrated</li> <li>0 = After power-up, the dedicated ADC Core 0 will not be calibrated</li> <li>0 = Dedicated ADC Core 0 will be calibrated</li> <li>0 = Dedicated ADC Core 0 will be calibrated in Single-Ended Input mode</li> <li>0 = Dedicated ADC Core 0 will be</li></ul>                                                                                                                             | -n = Value at | t POR        | '1' = Bit is set    |                  | "0" = Bit is clea | red                | x = Bit is unk | nown             |

| <ul> <li>1 = Dedicated ADC Core 1 calibration is finished</li> <li>0 = Dedicated ADC Core 1 calibration is in progress</li> <li>bit 112</li> <li>Unimplemented: Read as '0'</li> <li>cAL1SKIP: Dedicated ADC Core 1 Calibration Bypass bit</li> <li>1 = After power-up, the dedicated ADC Core 1 will not be calibrated</li> <li>0 = After power-up, the dedicated ADC Core 1 will be calibrated</li> <li>0 = After power-up, the dedicated ADC Core 1 will be calibrated</li> <li>0 = After power-up, the dedicated ADC Core 1 will be calibrated</li> <li>0 = After power-up, the dedicated ADC Core 1 will be calibrated</li> <li>0 = Dedicated ADC Core 1 will be calibrated in Pseudo-Differential Input Mode Calibration bit</li> <li>1 = Dedicated ADC Core 1 calibration Enable bit</li> <li>1 = Dedicated ADC Core 1 calibration bits (CALXRDY, CALXSKIP, CALXDIFF and CALXRUN) can b accessed by software</li> <li>0 = Dedicated ADC Core 1 calibration bits are disabled</li> <li>bit 8</li> <li>CAL1RUN: Dedicated ADC Core 1 Calibration Start bit</li> <li>1 = 1 f this bit is set by software, the dedicated ADC Core 1 calibration cycle is started; this bit automatically cleared by hardware</li> <li>0 = Software can start the next calibration starts Flag bit</li> <li>1 = Dedicated ADC Core 0 calibration is finished</li> <li>0 = Dedicated ADC Core 0 calibration starts Flag bit</li> <li>1 = Dedicated ADC Core 0 calibration spress</li> <li>bit 6-4</li> <li>Unimplemented: Read as '0'</li> <li>bit 3</li> <li>CAL0SKIP: Dedicated ADC Core 0 Calibration Bypass bit</li> <li>1 = After power-up, the dedicated ADC Core 0 will not be calibrated</li> <li>0 = Dedicated ADC Core 0 will be calibrated</li> <li>0 = After power-up, the dedicated ADC Core 0 will not be calibrated</li> <li>0 = Dedicated ADC Core 0 will be calibrated</li> <li>0 = Dedicated ADC Core 0 will be calibrated in Single-Ended Input mode</li> <li>0 = Dedicated ADC Core 0 will be</li></ul>                                                                                                                             | bit 15        | CAL1RDY:     | Dedicated ADC 0     | Core 1 Calibra   | ation Status Flac | ıbit               |                |                  |

| bit 14-12       Unimplemented: Read as '0'         bit 11       CAL1SKIP: Dedicated ADC Core 1 Calibration Bypass bit         1 = After power-up, the dedicated ADC Core 1 will not be calibrated         0 = After power-up, the dedicated ADC Core 1 will not be calibrated         bit 10       CAL1DIFF: Dedicated ADC Core 1 Pseudo-Differential Input Mode Calibration bit         1 = Dedicated ADC Core 1 will be calibrated in Pseudo-Differential Input mode         0 = Dedicated ADC Core 1 calibration Enable bit         1 = Dedicated ADC Core 1 calibration bits (CALxRDY, CALxSKIP, CALxDIFF and CALxRUN) can be accessed by software         0 = Dedicated ADC Core 1 calibration bits (CALxRDY, CALxSKIP, CALxDIFF and CALxRUN) can be accessed by software         0 = Dedicated ADC Core 1 calibration Start bit         1 = If this bit is set by software, the dedicated ADC Core 1 calibration cycle is started; this bit automatically cleared by hardware         0 = Software can start the next calibration Status Flag bit         1 = Dedicated ADC Core 0 calibration is in progress         bit 3       CALORDY: Dedicated ADC Core 0 Calibration Bypass bit         1 = After power-up, the dedicated ADC Core 0 will not be calibrated         0 = After power-up, the dedicated ADC Core 0 will not be calibrated         0 = After power-up, the dedicated ADC Core 0 will not be calibrated         0 = After power-up, the dedicated ADC Core 0 will not be calibrated         0 = After power-up, the dedicated ADC Core 0 will                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |              |                     |                  | •                 | ,                  |                |                  |

| bit 11       CAL1SKIP: Dedicated ADC Core 1 Calibration Bypass bit         1 = After power-up, the dedicated ADC Core 1 will not be calibrated         0 = After power-up, the dedicated ADC Core 1 will be calibrated         bit 10       CAL1DIFF: Dedicated ADC Core 1 Pseudo-Differential Input Mode Calibration bit         1 = Dedicated ADC Core 1 will be calibrated in Pseudo-Differential Input mode         0 = Dedicated ADC Core 1 will be calibrated in Single-Ended Input mode         0 = Dedicated ADC Core 1 calibration Enable bit         1 = Dedicated ADC Core 1 calibration bits (CALxRDY, CALxSKIP, CALxDIFF and CALxRUN) can be accessed by software         0 = Dedicated ADC Core 1 calibration bits are disabled         bit 8       CAL1RUN: Dedicated ADC Core 1 Calibration Start bit         1 = If this bit is set by software, the dedicated ADC Core 1 calibration cycle is started; this bit automatically cleared by hardware         0 = Software can start the next calibration starts Flag bit         1 = Dedicated ADC Core 0 Calibration Starts Flag bit         1 = Dedicated ADC Core 0 Calibration Bypass bit         1 = Dedicated ADC Core 0 Calibration Bypass bit         1 = After power-up, the dedicated ADC Core 0 will not be calibrated         0 = Dedicated ADC Core 0 Calibration Bypass bit         1 = Dedicated ADC Core 0 Vill be calibrated         0 = After power-up, the dedicated ADC Core 0 will not be calibrated         0 = After power-up, the dedicated ADC Core 0 will not                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               | 0 = Dedicat  | ted ADC Core 1 c    | alibration is in | progress          |                    |                |                  |

| <ul> <li>1 = After power-up, the dedicated ADC Core 1 will not be calibrated</li> <li>0 = After power-up, the dedicated ADC Core 1 will be calibrated</li> <li>bit 10</li> <li>CAL1DIFF: Dedicated ADC Core 1 Pseudo-Differential Input Mode Calibration bit</li> <li>1 = Dedicated ADC Core 1 will be calibrated in Pseudo-Differential Input mode</li> <li>0 = Dedicated ADC Core 1 calibration Enable bit</li> <li>1 = Dedicated ADC Core 1 calibration is Sigle-Ended Input mode</li> <li>bit 9</li> <li>CAL1EN: Dedicated ADC Core 1 calibration bits (CALxRDY, CALxSKIP, CALxDIFF and CALxRUN) can be accessed by software</li> <li>0 = Dedicated ADC Core 1 calibration bits are disabled</li> <li>bit 8</li> <li>CAL1RUN: Dedicated ADC Core 1 Calibration Start bit</li> <li>1 = If this bit is set by software, the dedicated ADC Core 1 calibration cycle is started; this bit automatically cleared by hardware</li> <li>0 = Software can start the next calibration starts Flag bit</li> <li>1 = Dedicated ADC Core 0 calibration is finished</li> <li>0 = Dedicated ADC Core 0 calibration is in progress</li> <li>bit 3</li> <li>CALOSKIP: Dedicated ADC Core 0 Calibration Bypass bit</li> <li>1 = After power-up, the dedicated ADC Core 0 will not be calibrated</li> <li>0 = After power-up, the dedicated ADC Core 0 will be calibrated</li> <li>0 = After power-up, the dedicated ADC Core 0 will be calibrated</li> <li>0 = After power-up, the dedicated ADC Core 0 will be calibrated</li> <li>0 = Dedicated ADC Core 0 will be calibrated in Single-Ended Input mode</li> <li>0 = Dedicated ADC Core 0 calibration is finished</li> <li>0 = Dedicated ADC Core 0 will be calibrated in Single-Ended Input mode</li> <li>0 = Dedicated ADC Core 0 will be calibrated</li> <li>0 = After power-up, the dedicated ADC Core 0 will not be calibrated</li> <li>0 = After power-up, the dedicated ADC Core 0 will be calibrated</li> <li>0 = Dedicated ADC Core 0 alibration in Single-</li></ul>                                                                                                                     | bit 14-12     | Unimplem     | ented: Read as '0   | 3                |                   |                    |                |                  |

| <ul> <li>0 = After power-up, the dedicated ADC Core 1 will be calibrated</li> <li>bit 10</li> <li>CAL1DIFF: Dedicated ADC Core 1 Pseudo-Differential Input Mode Calibration bit         <ol> <li>Dedicated ADC Core 1 will be calibrated in Pseudo-Differential Input mode</li> <li>0 = Dedicated ADC Core 1 calibration Enable bit</li> <li>1 = Dedicated ADC Core 1 calibration bits (CALxRDY, CALxSKIP, CALxDIFF and CALxRUN) can b             accessed by software             0 = Dedicated ADC Core 1 calibration bits (CALxRDY, CALxSKIP, CALxDIFF and CALxRUN) can b             accessed by software             0 = Dedicated ADC Core 1 calibration bits are disabled</li> </ol> </li> <li>bit 8</li> <li>CAL1RUN: Dedicated ADC Core 1 Calibration Start bit         <ol> <li>a If this bit is set by software, the dedicated ADC Core 1 calibration cycle is started; this bit automatically cleared by hardware             0 = Software can start the next calibration Starts Flag bit</li> <li>Dedicated ADC Core 0 calibration is in progress</li> <li>bit 6-4</li> <li>Unimplemented: Read as '0'</li> <li>bit 3</li> <li>CAL0SIP: Dedicated ADC Core 0 Calibration Bypass bit             1 = After power-up, the dedicated ADC Core 0 will not be calibrated             0 = After power-up, the dedicated ADC Core 0 will be calibrated             bit 2</li> <li>CAL0DIFF: Dedicated ADC Core 0 Seudo-Differential Input Mode             0 = Dedicated ADC Core 0 will be calibrated in Pseudo-Differential Input mode             0 = Dedicated ADC Core 0 calibration is ingle-Ended Input mode             0 = Dedicated ADC Core 0 vill be calibrated             0 = After power-up, the dedicated ADC Core 0 will not be calibrated             0 = After power-up, the dedicated ADC Core 0 will not be calibrated             0 = Dedicated ADC Core 0 will be calibrated in Pseudo-Differential Input mode             0 = Dedicated</li></ol></li></ul>                                                                                                                                               | bit 11        | CAL1SKIP     | : Dedicated ADC     | Core 1 Calibr    | ation Bypass bit  |                    |                |                  |

| <ul> <li>bit 10</li> <li>CAL1DIFF: Dedicated ADC Core 1 Pseudo-Differential Input Mode Calibration bit</li> <li>1 = Dedicated ADC Core 1 will be calibrated in Pseudo-Differential Input mode</li> <li>0 = Dedicated ADC Core 1 Calibration Enable bit</li> <li>1 = Dedicated ADC Core 1 calibration bits (CALxRDY, CALxSKIP, CALxDIFF and CALxRUN) can b accessed by software</li> <li>0 = Dedicated ADC Core 1 calibration bits are disabled</li> <li>bit 8</li> <li>CAL1RUN: Dedicated ADC Core 1 Calibration Start bit</li> <li>1 = If this bit is set by software, the dedicated ADC Core 1 calibration cycle is started; this bit automatically cleared by hardware</li> <li>0 = Software can start the next calibration starts bit</li> <li>1 = Dedicated ADC Core 0 calibration is finished</li> <li>0 = Dedicated ADC Core 0 calibration is in progress</li> <li>bit 6.4</li> <li>Unimplemented: Read as '0'</li> <li>bit 3</li> <li>CAL0SKIP: Dedicated ADC Core 0 Seudo-Differential Input Mode Calibration bit</li> <li>1 = After power-up, the dedicated ADC Core 0 will not be calibrated</li> <li>0 = After power-up, the dedicated ADC Core 0 will be calibrated</li> <li>0 = Dedicated ADC Core 0 will be calibrated in Single-Ended Input mode</li> <li>0 = Dedicated ADC Core 0 Calibration Enable bit</li> <li>1 = Dedicated ADC Core 0 will be calibrated in Single-Ended Input mode</li> <li>0 = Dedicated ADC Core 0 vill be calibrated in Decalibrated</li> <li>0 = Dedicated ADC Core 0 calibration Enable bit</li> <li>1 = Dedicated ADC Core 0 calibration Enable bit</li> <li>1 = Dedicated ADC Core 0 calibration Enable bit</li> <li>1 = Dedicated ADC Core 0 calibration bits (CALxRDY, CALxSKIP, CALxDIFF and CALxRUN) can b accessed by software</li> <li>0 = Dedicated ADC Core 0 calibration bits (CALxRDY, CALxSKIP, CALxDIFF and CALxRUN) can b accessed by software</li> <li>0 = Dedicated ADC Core 0 calibration bits are disabled</li> <li>bit 0</li> <li>CALORUN: Dedicated ADC Core 0 Calibration Start bit</li> <li>1 = If this bit is set by software, the dedicated ADC Core 0 ca</li></ul> |               |              |                     |                  |                   |                    |                |                  |