Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 12x12b; D/A 2x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C                                                                   |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gs202-e-mm |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

28-Pin UQFN 4x4 mm, 28-Pin UQFN 6x6 mm, 28-Pin QFN-S 6x6 mm

= Pins are up to 5V tolerant

#### PIN FUNCTION DESCRIPTIONS

| Pin | Pin Function                      | Pin | Pin Function                 |

|-----|-----------------------------------|-----|------------------------------|

| 1   | AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2 | 15  | PGEC1/AN11/SDA1/RP39/RB7     |

| 2   | AN3/PGA2P3/CMP1D/ CMP28/RP32/RB0  | 16  | Vss                          |

| 3   | AN4/CMP2C/RP41/RB9                | 17  | VCAP                         |

| 4   | AN5/CMP2D/ <b>RP42</b> /RB10      | 18  | TMS/PWM3H/ <b>RP43</b> /RB11 |

| 5   | Vss                               | 19  | TCK/PWM3L/ <b>RP44</b> /RB12 |

| 6   | OSC1/CLKI/AN6/RP33/RB1            | 20  | PWM2H/ <b>RP45</b> /RB13     |

| 7   | OSC2/CLKO/AN7/PGA1N2/RP34/RB2     | 21  | PWM2L/ <b>RP46</b> /RB14     |

| 8   | PGED2/AN8/INT0/RP35/RB3           | 22  | PWM1H/RA4                    |

| 9   | PGEC2/ADTRG31/ <b>RP36</b> /RB4   | 23  | PWM1L/RA3                    |

| 10  | VDD                               | 24  | AVss                         |

| 11  | PGED3/ <b>RP40</b> /RB8           | 25  | AVDD                         |

| 12  | PGEC3/ <b>RP47</b> /RB15          | 26  | MCLR                         |

| 13  | TDO/AN9/PGA2N2/ <b>RP37</b> /RB5  | 27  | AN0/PGA1P1/CMP1A/RA0         |

| 14  | PGED1/TDI/AN10/SCL1/RP38/RB6      | 28  | AN1/PGA1P2/PGA2P1/CMP1B/RA1  |

Legend: Shaded pins are up to 5 VDC tolerant.

Note: RPn represents remappable peripheral functions. See Table 10-1 and Table 10-2 for the complete list of remappable sources.

## 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS202 family of devices. It is not intended to be a comprehensive resource. To complement the information in this data sheet, refer to the related section in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device-specific information for the dsPIC33EPXXGS202 Digital Signal Controller (DSC) devices.

The dsPIC33EPXXGS202 devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit MCU architecture.

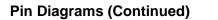

Figure 1-1 shows a general block diagram of the core and peripheral modules. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

### FIGURE 1-1: dsPIC33EPXXGS202 FAMILY BLOCK DIAGRAM

## TABLE 7-1: INTERRUPT VECTOR DETAILS

| Interrupt Source                     | Vector  | IRQ       | IVT Address         | Inte     | errupt Bit Lo | cation       |

|--------------------------------------|---------|-----------|---------------------|----------|---------------|--------------|

| Interrupt Source                     | #       | #         | IVI Address         | Flag     | Enable        | Priority     |

|                                      | Hi      | ghest Nat | ural Order Priority |          |               |              |

| INT0 – External Interrupt 0          | 8       | 0         | 0x000014            | IFS0<0>  | IEC0<0>       | IPC0<2:0>    |

| IC1 – Input Capture 1                | 9       | 1         | 0x000016            | IFS0<1>  | IEC0<1>       | IPC0<6:4>    |

| OC1 – Output Compare 1               | 10      | 2         | 0x000018            | IFS0<2>  | IEC0<2>       | IPC0<10:8>   |

| T1 – Timer1                          | 11      | 3         | 0x00001A            | IFS0<3>  | IEC0<3>       | IPC0<14:12>  |

| Reserved                             | 12–14   | 4–6       | 0x00001C-0x000020   | _        | _             | _            |

| T2 – Timer2                          | 15      | 7         | 0x000022            | IFS0<7>  | IEC0<7>       | IPC1<14:12>  |

| T3 – Timer3                          | 16      | 8         | 0x000024            | IFS0<8>  | IEC0<8>       | IPC2<2:0>    |

| SPI1E – SPI1 Error                   | 17      | 9         | 0x000026            | IFS0<9>  | IEC0<9>       | IPC2<6:4>    |

| SPI1 – SPI1 Transfer Done            | 18      | 10        | 0x000028            | IFS0<10> | IEC0<10>      | IPC2<10:8>   |

| U1RX – UART1 Receiver                | 19      | 11        | 0x00002A            | IFS0<11> | IEC0<11>      | IPC2<14:12>  |

| U1TX – UART1 Transmitter             | 20      | 12        | 0x00002C            | IFS0<12> | IEC0<12>      | IPC3<2:0>    |

| ADC – ADC Global Convert Done        | 21      | 13        | 0x00002E            | IFS0<13> | IEC0<13>      | IPC3<6:4>    |

| Reserved                             | 22      | 14        | 0x000030            | _        | _             | _            |

| NVM – NVM Write Complete             | 23      | 15        | 0x000032            | IFS0<15> | IEC0<15>      | IPC3<14:12>  |

| SI2C1 – I2C1 Slave Event             | 24      | 16        | 0x000034            | IFS1<0>  | IEC1<0>       | IPC4<2:0>    |

| MI2C1 – I2C1 Master Event            | 25      | 17        | 0x000036            | IFS1<1>  | IEC1<1>       | IPC4<6:4>    |

| CMP1 – Analog Comparator 1 Interrupt | 26      | 18        | 0x000038            | IFS1<2>  | IEC1<2>       | IPC4<10:8>   |

| CN – Input Change Interrupt          | 27      | 19        | 0x00003A            | IFS1<3>  | IEC1<3>       | IPC4<14:12>  |

| INT1 – External Interrupt 1          | 28      | 20        | 0x00003C            | IFS1<4>  | IEC1<4>       | IPC5<2:0>    |

| Reserved                             | 29-36   | 21-28     | 0x00003E-0x00004C   | _        | _             | _            |

| INT2 – External Interrupt 2          | 37      | 29        | 0x00004E            | IFS1<13> | IEC1<13>      | IPC7<6:4>    |

| Reserved                             | 38-64   | 30-56     | 0x000050-0x000084   | _        | _             | _            |

| PSEM – PWM Special Event Match       | 65      | 57        | 0x000086            | IFS3<9>  | IEC3<9>       | IPC14<6:4>   |

| Reserved                             | 63-72   | 55-64     | 0x000088-0x000094   | _        | _             | _            |

| U1E – UART1 Error Interrupt          | 73      | 65        | 0x000096            | IFS4<1>  | IEC4<1>       | IPC16<6:4>   |

| Reserved                             | 74-80   | 66-72     | 0x000098-0x0000A4   | _        | _             | _            |

| PWM Secondary Special Event Match    | 81      | 73        | 0x0000A6            | IFS4<9>  | IEC4<9>       | IPC18<6:4>   |

| Reserved                             | 82-101  | 74-93     | 0x0000A8-0x0000CE   | _        | _             | _            |

| PWM1 – PWM1 Interrupt                | 102     | 94        | 0x0000D0            | IFS5<14> | IEC5<14>      | IPC23<10:8>  |

| PWM2 – PWM2 Interrupt                | 103     | 95        | 0x0000D2            | IFS5<15> | IEC5<15>      | IPC23<14:12> |

| PWM3 – PWM3 Interrupt                | 104     | 96        | 0x0000D4            | IFS6<0>  | IEC6<0>       | IPC24<2:0>   |

| Reserved                             | 105-110 | 97-102    | 0x0000D6-0x0000E0   | _        | _             | _            |

| CMP2 – Analog Comparator 2 Interrupt | 111     | 103       | 0x0000E2            | IFS6<7>  | IEC6<7>       | IPC25<14:12> |

| Reserved                             | 112-117 | 104-109   | 0x0000E4-0x0000EE   | _        | _             | _            |

| AN0 Conversion Done                  | 118     | 110       | 0x0000F0            | IFS6<14> | IEC6<14>      | IPC27<10:8>  |

| AN1 Conversion Done                  | 119     | 111       | 0x0000F2            | IFS6<15> | IEC6<15>      | IPC27<14:12> |

| AN2 Conversion Done                  | 120     | 112       | 0x0000F4            | IFS7<0>  | IEC7<0>       | IPC28<2:0>   |

| AN3 Conversion Done                  | 121     | 113       | 0x0000F6            | IFS7<1>  | IEC7<1>       | IPC28<6:4>   |

| AN4 Conversion Done                  | 122     | 114       | 0x0000F8            | IFS7<2>  | IEC7<2>       | IPC28<10:8>  |

| AN5 Conversion Done                  | 123     | 115       | 0x0000FA            | IFS7<3>  | IEC7<3>       | IPC28<14:12> |

| AN6 Conversion Done                  | 124     | 116       | 0x0000FC            | IFS7<4>  | IEC7<4>       | IPC29<2:0>   |

| AN7 Conversion Done                  | 125     | 117       | 0x0000FE            | IFS7<5>  | IEC7<5>       | IPC29<6:4>   |

### REGISTER 10-18: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

| U-0           | U-0        | R/W-0                             | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|---------------|------------|-----------------------------------|--------|------------------|------------------|-----------------|--------|

|               | —          | RP37R5                            | RP37R4 | RP37R3           | RP37R2           | RP37R1          | RP37R0 |

| bit 15        |            |                                   |        |                  |                  |                 | bit 8  |

|               |            |                                   |        |                  |                  |                 |        |

| U-0           | U-0        | R/W-0                             | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| _             | —          | RP36R5                            | RP36R4 | RP36R3           | RP36R2           | RP36R1          | RP36R0 |

| bit 7         |            |                                   |        | ·                |                  |                 | bit 0  |

|               |            |                                   |        |                  |                  |                 |        |

| Legend:       |            |                                   |        |                  |                  |                 |        |

| R = Readabl   | e bit      | W = Writable                      | bit    | U = Unimpler     | mented bit, read | l as '0'        |        |

| -n = Value at | POR        | '1' = Bit is set                  |        | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

|               |            |                                   |        |                  |                  |                 |        |

| bit 15-14     | Unimplemen | ted: Read as '                    | 0'     |                  |                  |                 |        |

| bit 13-8      |            | Peripheral Ou<br>-2 for periphera |        | •                | RP37 Output F    | Pin bits        |        |

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 **RP36R<5:0>:** Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 10-2 for peripheral function numbers)

#### REGISTER 10-19: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP39R5 | RP39R4 | RP39R3 | RP39R2 | RP39R1 | RP39R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP38R5 | RP38R4 | RP38R3 | RP38R2 | RP38R1 | RP38R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP39R<5:0>:** Peripheral Output Function is Assigned to RP39 Output Pin bits (see Table 10-2 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP38R<5:0>:** Peripheral Output Function is Assigned to RP38 Output Pin bits (see Table 10-2 for peripheral function numbers)

NOTES:

## 12.0 TIMER2/3

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer2/3 module is a 32-bit timer, which can also be configured as two independent 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2 and Timer3 operate in three modes:

- Two Independent 16-Bit Timers (e.g., Timer2 and Timer3) with all 16-Bit Operating modes (except Asynchronous Counter mode)

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- · Interrupt on a 32-Bit Period Register Match

- Time Base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

Individually, both of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed previously, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON and T3CON registers. T2CON details are in Register 12-1. T3CON details are in Register 12-2.

For 32-bit timer/counter operation, Timer2 is the least significant word (lsw); Timer3 is the most significant word (msw) of the 32-bit timers.

Note: For 32-bit operation, T3CON control bits are ignored. Only T2CON control bits are used for setup and control. Timer2 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 interrupt flag.

A block diagram for an example 32-bit timer pair (Timer2/3) is shown in Figure 12-2.

## 12.1 Timer Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 12.1.1 KEY RESOURCES

- **"Timers"** (DS70362) in the *"dsPIC33/PIC24 Family Reference Manual"*

- Code Samples

- · Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## REGISTER 15-8: SSEVTCMP: PWM SECONDARY SPECIAL EVENT COMPARE REGISTER<sup>(1)</sup>

| R/W-0   | R/W-0 | R/W-0       | R/W-0   | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|---------|-------|-------------|---------|----------|-------|-------|-------|

|         |       |             | SSEVTCI | MP<12:5> |       |       |       |

| bit 15  |       |             |         |          |       |       | bit 8 |

|         |       |             |         |          |       |       |       |

| R/W-0   | R/W-0 | R/W-0       | R/W-0   | R/W-0    | U-0   | U-0   | U-0   |

|         | SS    | EVTCMP<4:0> | >       |          | —     | —     | _     |

| bit 7   |       |             |         |          |       |       | bit 0 |

|         |       |             |         |          |       |       |       |

| Legend: |       |             |         |          |       |       |       |

| U                 |                  |                        |                    |  |

|-------------------|------------------|------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

bit 15-3 SSEVTCMP<12:0>: Special Event Compare Count Value bits

bit 2-0 Unimplemented: Read as '0'

**Note 1:** One LSB = 1.04 ns (at fastest auxiliary clock rate); therefore, the minimum SEVTCMP resolution is 8.32 ns.

## **REGISTER 15-9:** CHOP: PWM CHOP CLOCK GENERATOR REGISTER<sup>(1)</sup>

| R/W-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0    | R/W-0    |

|----------|-----|-----|-----|-----|-----|----------|----------|

| CHPCLKEN | —   | —   | —   | —   | —   | CHOPCLK6 | CHOPCLK5 |

| bit 15   |     |     |     |     |     |          | bit 8    |

| R/W-0       | R/W-0    | R/W-0    | R/W-0    | R/W-0    | U-0 | U-0 | U-0 |  |

|-------------|----------|----------|----------|----------|-----|-----|-----|--|

| CHOPCLK4    | CHOPCLK3 | CHOPCLK2 | CHOPCLK1 | CHOPCLK0 | —   | _   | —   |  |

| bit 7 bit 0 |          |          |          |          |     |     |     |  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15               | <b>CHPCLKEN:</b> Enable Chop Clock Generator bit<br>1 = Chop clock generator is enabled<br>0 = Chop clock generator is disabled |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------|

| bit 14-10<br>bit 9-3 | Unimplemented: Read as '0'<br>CHOPCLK<6:0>: Chop Clock Divider bits                                                             |

|                      | Value is in 8.32 ns increments. The frequency of the chop clock signal is given by the following expression:                    |

| hit 2-0              | Chop Frequency = $1/(16.64 * (CHOPCLK < 6:0 > + 1) * Primary Master PWM Input Clock Period)$                                    |

| bit 2-0              | Unimplemented: Read as '0'                                                                                                      |

**Note 1:** The chop clock generator operates with the primary PWM clock prescaler (PCLKDIV<2:0>) in the PTCON2 register (Register 15-2).

## REGISTER 15-10: MDC: PWM MASTER DUTY CYCLE REGISTER<sup>(1,2)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | MDC   | <15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | MDO   | C<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimpler     | nented bit, rea | id as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unki | nown  |

bit 15-0 MDC<15:0>: Master PWM Duty Cycle Value bits

**Note 1:** The smallest pulse width that can be generated on the PWMx output corresponds to a value of 0x0008, while the maximum pulse width generated corresponds to a value of Period – 0x0008.

**2:** As the duty cycle gets closer to 0% or 100% of the PWM period (0 to 40 ns, depending on the mode of operation), PWM duty cycle resolution will increase from 1 to 3 LSBs.

#### REGISTER 15-11: PWMKEY: PWM PROTECTION LOCK/UNLOCK KEY REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0          | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|----------------|-----------------|-------|

|                 |       |                  | PWMK  | EY<15:8>          |                |                 |       |

| bit 15          |       |                  |       |                   |                |                 | bit 8 |

|                 |       |                  |       |                   |                |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0          | R/W-0           | R/W-0 |

|                 |       |                  | PWM   | <ey<7:0></ey<7:0> |                |                 |       |

| bit 7           |       |                  |       |                   |                |                 | bit 0 |

| Legend:         |       |                  |       |                   |                |                 |       |

| R = Readable I  | bit   | W = Writable bit | t     | U = Unimplem      | ented bit, rea | ad as '0'       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | red            | x = Bit is unkr | nown  |

bit 15-0 PWMKEY<15:0>: PWM Protection Lock/Unlock Key Value bits

## REGISTER 15-24: LEBCONX: PWMx LEADING-EDGE BLANKING (LEB) CONTROL REGISTER (CONTINUED)

- bit 1

BPLH: Blanking in PWMxL High Enable bit

1 = State blanking (of current-limit and/or Fault input signals) when the PWMxL output is high

bit 0

BPLL: Blanking in PWMxL Low Enable bit

1 = State blanking (of current-limit and/or Fault input signals) when the PWMxL output is low

0 = No blanking when the PWMxL Low Enable bit

1 = State blanking (of current-limit and/or Fault input signals) when the PWMxL output is low

0 = No blanking when the PWMxL output is low

- **Note 1:** The blanking signal is selected via the BLANKSEL<3:0> bits in the AUXCONx register.

### REGISTER 15-25: LEBDLYx: PWMx LEADING-EDGE BLANKING DELAY REGISTER

| U-0             | U-0   | U-0                                                 | U-0   | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|-----------------|-------|-----------------------------------------------------|-------|-----------------------------------------|-------|-------|-------|

| —               | —     | _                                                   | _     |                                         | LEB   | <8:5> |       |

| bit 15          |       |                                                     |       |                                         |       |       | bit 8 |

|                 |       |                                                     |       |                                         |       |       |       |

| R/W-0           | R/W-0 | R/W-0                                               | R/W-0 | R/W-0                                   | U-0   | U-0   | U-0   |

|                 |       | LEB<4:0>                                            |       |                                         | —     | —     | —     |

| bit 7           |       |                                                     |       |                                         |       |       | bit 0 |

|                 |       |                                                     |       |                                         |       |       |       |

| Legend:         |       |                                                     |       |                                         |       |       |       |

| R = Readable    | bit   | W = Writable bit U = Unimplemented bit, read as '0' |       |                                         |       |       |       |

| -n = Value at P | POR   | '1' = Bit is set                                    |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |

bit 15-12 Unimplemented: Read as '0'

bit 11-3 **LEB<8:0>:** Leading-Edge Blanking Delay for Current-Limit and Fault Inputs bits The value is in 8.32 ns increments.

bit 2-0 Unimplemented: Read as '0'

## **REGISTER 19-11:** ADCOREXL: DEDICATED ADC CORE x CONTROL REGISTER LOW (x = 0,1)

|              |          |                   |              |                   |                | •                     |               |

|--------------|----------|-------------------|--------------|-------------------|----------------|-----------------------|---------------|

| U-0          | U-0      | U-0               | U-0          | U-0               | U-0            | R/W-0                 | R/W-0         |

| _            | _        | —                 | _            | —                 |                | SAMC<                 | 9:8>          |

| bit 15       |          |                   |              | •                 |                |                       | bit 8         |

|              |          |                   |              |                   |                |                       |               |

| R/W-0        | R/W-0    | R/W-0             | R/W-0        | R/W-0             | R/W-0          | R/W-0                 | R/W-0         |

|              |          |                   | SA           | MC<7:0>           |                |                       |               |

| bit 7        |          |                   |              |                   |                |                       | bit 0         |

|              |          |                   |              |                   |                |                       |               |

| Legend:      |          |                   |              |                   |                |                       |               |

| R = Readal   | ble bit  | W = Writable bit  |              | U = Unimplem      | ented bit, rea | d as '0'              |               |

| -n = Value a | at POR   | '1' = Bit is set  |              | '0' = Bit is clea | ared           | x = Bit is unknow     | /n            |

| bit 15-10    | Unimplem | ented: Read as '0 | ,            |                   |                |                       |               |

|              | •        |                   |              |                   | alaatian hita  |                       |               |

| bit 9-0      |          | D>: Dedicated ADC |              | ,                 |                |                       |               |

|              |          |                   |              |                   |                | f conversion in the r |               |

|              | ADC Core | Clock (TADCORE)   | periods. Dur | ing this time, th | ne ADC Core    | x still continues sa  | ampling. This |

0000000000 = 2 TADCORE

DS70005208D-page 212

### REGISTER 19-26: ADFL0CON: ADC DIGITAL FILTER 0 CONTROL REGISTER

| R/W-0        | R/W-0                                                                                                                                                              | R/W-0              | R/W-0                          | R/W-0             | R/W-0             | R/W-0            |                    |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------|-------------------|-------------------|------------------|--------------------|--|--|

| FLEN         | MODE1                                                                                                                                                              | MODE0              | OVRSAM2                        | OVRSAM1           | OVRSAM0           | R/W-U            | R-0, HC, HS<br>RDY |  |  |

|              | MODET                                                                                                                                                              | MODEU              | OVRSAIVIZ                      | OVRSAINT          | OVRSAIVIU         | IE               |                    |  |  |

| bit 15       |                                                                                                                                                                    |                    |                                |                   |                   |                  | bit 8              |  |  |

|              |                                                                                                                                                                    |                    | DAMO                           |                   | DAMA              | DAMA             | DAMO               |  |  |

| U-0          | U-0                                                                                                                                                                | U-0                | R/W-0                          | R/W-0             | R/W-0             | R/W-0            | R/W-0              |  |  |

|              | _                                                                                                                                                                  | _                  | FLCHSEL4                       | FLCHSEL3          | FLCHSEL2          | FLCHSEL1         | FLCHSEL0           |  |  |

| bit 7        |                                                                                                                                                                    |                    |                                |                   |                   |                  | bit 0              |  |  |

| Lonondi      |                                                                                                                                                                    |                    | e Clearable bit                |                   | o Cottoblo bit    |                  |                    |  |  |

| Legend:      | 1. 1.14                                                                                                                                                            |                    | e Clearable bit                | HS = Hardwar      |                   | (0)              |                    |  |  |

| R = Readab   |                                                                                                                                                                    | W = Writable       |                                | •                 | ented bit, read   |                  |                    |  |  |

| -n = Value a | t POR                                                                                                                                                              | '1' = Bit is set   |                                | '0' = Bit is clea | ared              | x = Bit is unkn  | iown               |  |  |

|              |                                                                                                                                                                    |                    |                                |                   |                   |                  |                    |  |  |

| bit 15       | FLEN: Filter                                                                                                                                                       |                    |                                |                   |                   |                  |                    |  |  |

|              | 1 = Filter is                                                                                                                                                      |                    | e RDY bit is clea              | arad              |                   |                  |                    |  |  |

| bit 14-13    |                                                                                                                                                                    | Silter Mode b      |                                | areu              |                   |                  |                    |  |  |

| 511 14-15    | 11 = Averag                                                                                                                                                        |                    | 115                            |                   |                   |                  |                    |  |  |

|              | 10 = Reserv                                                                                                                                                        |                    |                                |                   |                   |                  |                    |  |  |

|              | 01 = Reserv                                                                                                                                                        |                    |                                |                   |                   |                  |                    |  |  |

|              | 00 = Oversa                                                                                                                                                        | ampling mode       |                                |                   |                   |                  |                    |  |  |

| bit 12-10    | OVRSAM<2                                                                                                                                                           | 2:0>: Filter Aver  | aging/Oversam                  | pling Ratio bits  |                   |                  |                    |  |  |

|              | If MODE<1:                                                                                                                                                         |                    |                                |                   |                   |                  |                    |  |  |

|              |                                                                                                                                                                    |                    | the ADFL0DAT                   |                   |                   |                  |                    |  |  |

|              | •                                                                                                                                                                  |                    | he ADFLODAT r                  | •                 | ,                 |                  |                    |  |  |

|              |                                                                                                                                                                    |                    | e ADFL0DAT re<br>e ADFL0DAT re |                   |                   |                  |                    |  |  |

|              |                                                                                                                                                                    |                    | the ADFL0DAT                   |                   |                   |                  |                    |  |  |

|              | 010 <b>= 64x (</b>                                                                                                                                                 | 15-bit result in t | he ADFL0DAT r                  | egister is in 12. | 3 format)         |                  |                    |  |  |

|              |                                                                                                                                                                    |                    | he ADFL0DAT r                  |                   |                   |                  |                    |  |  |

|              |                                                                                                                                                                    |                    | e ADFL0DAT re                  | •                 | ,                 |                  |                    |  |  |

|              | <u>If MODE&lt;1:</u><br>111 = 256x                                                                                                                                 |                    | result in the AD               | FLODAT registe    | <u>r):</u>        |                  |                    |  |  |

|              | 111 = 230x<br>110 = 128x                                                                                                                                           |                    |                                |                   |                   |                  |                    |  |  |

|              | 101 <b>= 64x</b>                                                                                                                                                   |                    |                                |                   |                   |                  |                    |  |  |

|              | 100 <b>= 32x</b>                                                                                                                                                   |                    |                                |                   |                   |                  |                    |  |  |

|              | 011 = 16x                                                                                                                                                          |                    |                                |                   |                   |                  |                    |  |  |

|              | 010 = 8x<br>001 = 4x                                                                                                                                               |                    |                                |                   |                   |                  |                    |  |  |

|              | 001 - 4x<br>000 = 2x                                                                                                                                               |                    |                                |                   |                   |                  |                    |  |  |

| bit 9        |                                                                                                                                                                    | mmon ADC Int       | errupt Enable bi               | t                 |                   |                  |                    |  |  |

|              |                                                                                                                                                                    |                    | -                              |                   | er result will be | readv            |                    |  |  |

|              | <ol> <li>Common ADC interrupt will be generated when the filter result will be ready</li> <li>Common ADC interrupt will not be generated for the filter</li> </ol> |                    |                                |                   |                   |                  |                    |  |  |

| bit 8        | RDY: Overs                                                                                                                                                         | ampling Filter D   | Data Ready Flag                | bit               |                   |                  |                    |  |  |

|              |                                                                                                                                                                    |                    | are when the re                |                   | n the ADFL0DA     | T register.      |                    |  |  |

|              |                                                                                                                                                                    |                    | register is ready              |                   |                   |                  |                    |  |  |

|              |                                                                                                                                                                    | -                  | r has been read                | and new data i    | n the ADFL0DA     | T register is no | t ready            |  |  |

| bit 7-5      | Unimplemented: Read as '0'                                                                                                                                         |                    |                                |                   |                   |                  |                    |  |  |

### **REGISTER 21-1: PGAxCON: PGAx CONTROL REGISTER (x = 1,2) (CONTINUED)**

- bit 2-0 GAIN<2:0>: PGAx Gain Selection bits

- 111 = Reserved

- 110 = Gain of 64 101 = Gain of 32

- 101 = Gain of 32100 = Gain of 16

- 011 = Gain of 8

- 010 = Gain of 4

- 001 = Reserved

- 000 = Reserved

## **REGISTER 21-2: PGAxCAL: PGAx CALIBRATION REGISTER (x = 1,2)**

| U-0             | U-0 | U-0              | U-0                                             | U-0   | U-0      | U-0   | U-0   |  |

|-----------------|-----|------------------|-------------------------------------------------|-------|----------|-------|-------|--|

| —               | _   | —                | —                                               | —     | —        | —     | —     |  |

| bit 15          |     |                  |                                                 |       |          |       | bit 8 |  |

|                 |     |                  |                                                 |       |          |       |       |  |

| U-0             | U-0 | R/W-0            | R/W-0                                           | R/W-0 | R/W-0    | R/W-0 | R/W-0 |  |

| —               | —   |                  |                                                 | PGAC  | CAL<5:0> |       |       |  |

| bit 7           |     |                  |                                                 |       |          |       | bit 0 |  |

|                 |     |                  |                                                 |       |          |       |       |  |

| Legend:         |     |                  |                                                 |       |          |       |       |  |

| R = Readable    | bit | W = Writable     | /ritable bit U = Unimplemented bit, read as '0' |       |          |       |       |  |

| -n = Value at F | POR | '1' = Bit is set | •                                               |       |          |       |       |  |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **PGACAL<5:0>:** PGAx Offset Calibration bits

The calibration values for PGA1 and PGA2 must be copied from Flash addresses, 0x800E48 and 0x800E4C, respectively, into these bits before the module is enabled. Refer to the Device Calibration Addresses table (Table 22-3) in **Section 22.0** "**Special Features**" for more information.

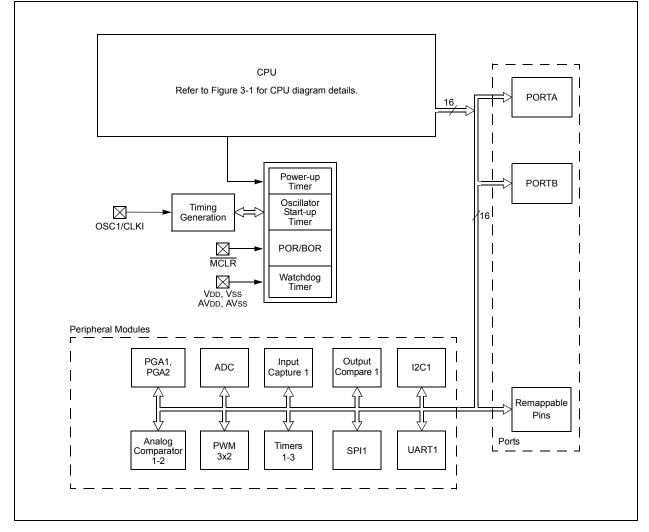

## 22.6 Watchdog Timer (WDT)

For dsPIC33EPXXGS202 family devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

#### 22.6.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a WDT Timeout Period (TWDT), as shown in Parameter SY12 in Table 25-23.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>), which allow the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods, ranges from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSCx bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

### FIGURE 22-2: WDT BLOCK DIAGRAM

### 22.6.2 SLEEP AND IDLE MODES

If the WDT is enabled, it continues to run during Sleep or Idle modes. When the WDT time-out occurs, the device wakes and code execution continues from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bit (RCON<3:2>) needs to be cleared in software after the device wakes up.

### 22.6.3 ENABLING WDT

The WDT is enabled or disabled by the WDTEN<1:0> Configuration bits in the FWDT Configuration register. When the WDTEN<1:0> Configuration bits have been programmed to '0b11', the WDT is always enabled.

The WDT can be optionally controlled in software when the WDTEN<1:0> Configuration bits have been programmed to '0b10'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical Code Segments and disables the WDT during non-critical segments for maximum power savings.

The WDT Time-out flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

### 22.6.4 WDT WINDOW

The Watchdog Timer has an optional Windowed mode, enabled by programming the WINDIS bit in the WDT Configuration register (FWDT<7>). In the Windowed mode (WINDIS = 0), the WDT should be cleared based on the settings in the programmable Watchdog Timer Window select bits (WDTWIN<1:0>).

© 2015-2016 Microchip Technology Inc.

## 24.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16 and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

## 24.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

### 24.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 24.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

| DC CHARACTE       | ERISTICS            | S Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industr<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Exten |       |            |        |            |  |  |

|-------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|--------|------------|--|--|

| Parameter<br>No.  | Тур.                | Max.                                                                                                                                                                                                        | Units | Conditions |        |            |  |  |

| Idle Current (III | dle) <sup>(1)</sup> |                                                                                                                                                                                                             |       |            |        |            |  |  |

| DC40d             | 1                   | 3                                                                                                                                                                                                           | mA    | -40°C      |        |            |  |  |

| DC40a             | 1                   | 3                                                                                                                                                                                                           | mA    | +25°C      | 3.3V   | 10 MIPS    |  |  |

| DC40b             | 1                   | 3                                                                                                                                                                                                           | mA    | +85°C      | 3.3V   | 10 1011-5  |  |  |

| DC40c             | 1                   | 3                                                                                                                                                                                                           | mA    | +125°C     |        |            |  |  |

| DC42d             | 3                   | 5                                                                                                                                                                                                           | mA    | -40°C      |        |            |  |  |

| DC42a             | 3                   | 5                                                                                                                                                                                                           | mA    | +25°C      | - 3.3V | 20 MIPS    |  |  |

| DC42b             | 3                   | 5                                                                                                                                                                                                           | mA    | +85°C      | 3.3V   | 20 10117-5 |  |  |

| DC42c             | 3                   | 5                                                                                                                                                                                                           | mA    | +125°C     |        |            |  |  |

| DC44d             | 5                   | 7                                                                                                                                                                                                           | mA    | -40°C      |        | 40 MIPS    |  |  |

| DC44a             | 5                   | 7                                                                                                                                                                                                           | mA    | +25°C      | 3.3V   |            |  |  |

| DC44b             | 5                   | 7                                                                                                                                                                                                           | mA    | +85°C      | 3.3V   | 40 1011-5  |  |  |

| DC44c             | 5                   | 7                                                                                                                                                                                                           | mA    | +125°C     |        |            |  |  |

| DC45d             | 7                   | 9                                                                                                                                                                                                           | mA    | -40°C      |        |            |  |  |

| DC45a             | 7                   | 9                                                                                                                                                                                                           | mA    | +25°C      | - 3.3V | 60 MIPS    |  |  |

| DC45b             | 7                   | 9                                                                                                                                                                                                           | mA    | +85°C      | 3.3V   |            |  |  |

| DC45c             | 7                   | 9                                                                                                                                                                                                           | mA    | +125°C     | ]      |            |  |  |

| DC46d             | 9                   | 12                                                                                                                                                                                                          | mA    | -40°C      |        |            |  |  |

| DC46a             | 9                   | 12                                                                                                                                                                                                          | mA    | +25°C      | 3.3V   | 70 MIPS    |  |  |

| DC46b             | 9                   | 12                                                                                                                                                                                                          | mA    | +85°C      | ]      |            |  |  |

#### TABLE 25-7: DC CHARACTERISTICS: IDLE CURRENT (lidle)

**Note 1:** Base Idle current (IIDLE) is measured as follows:

CPU core is off, oscillator is configured in EC mode and external clock is active; OSC1 is driven with

external square wave from rail-to-rail (EC Clock Overshoot/Undershoot < 250 mV required)</li>

- CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as outputs and driving low

- $\overline{\text{MCLR}}$  = VDD, WDT and FSCM are disabled

- No peripheral modules are operating or being clocked (defined PMDx bits are all ones)

- The NVMSIDL bit (NVMCON<12>) = 1 (i.e., Flash regulator is set to standby while the device is in Idle mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- JTAG is disabled

## TABLE 25-23:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMERTIMING REQUIREMENTS

| AC CHARACTERISTICS |           |                                                                | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                                                                                                                   |  |

|--------------------|-----------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol    | Characteristic <sup>(1)</sup>                                  | Min.                                                                                                                                                                                                                                                                                    | Тур. <sup>(2)</sup> | Max. | Units | Conditions                                                                                                        |  |

| SY00               | Τρυ       | Power-up Period                                                | _                                                                                                                                                                                                                                                                                       | 400                 | 600  | μS    |                                                                                                                   |  |

| SY10               | Tost      | Oscillator Start-up Time                                       |                                                                                                                                                                                                                                                                                         | 1024 Tosc           | _    | _     | Tosc = OSC1 Period                                                                                                |  |

| SY12               | Twdt      | Watchdog Timer<br>Time-out Period                              | 0.81                                                                                                                                                                                                                                                                                    | _                   | 1.22 | ms    | WDTPRE = 0,<br>WDTPOST<3:0> = 0000,<br>using LPRC tolerances indicated in<br>F21a/F21b (see Table 25-21) at +85°C |  |

|                    |           |                                                                | 3.25                                                                                                                                                                                                                                                                                    | _                   | 4.88 | ms    | WDTPRE = 1,<br>WDTPOST<3:0> = 0000,<br>using LPRC tolerances indicated in<br>F21a/F21b (see Table 25-21) at +85°C |  |

| SY13               | Tioz      | I/O High-Impedance from<br>MCLR Low or Watchdog<br>Timer Reset | 0.68                                                                                                                                                                                                                                                                                    | 0.72                | 1.2  | μS    |                                                                                                                   |  |

| SY20               | TMCLR     | MCLR Pulse Width (low)                                         | 2                                                                                                                                                                                                                                                                                       | _                   | _    | μS    |                                                                                                                   |  |

| SY30               | TBOR      | BOR Pulse Width (low)                                          | 1                                                                                                                                                                                                                                                                                       | _                   | _    | μS    |                                                                                                                   |  |

| SY35               | TFSCM     | Fail-Safe Clock Monitor<br>Delay                               | _                                                                                                                                                                                                                                                                                       | 500                 | 900  | μS    | -40°C to +85°C                                                                                                    |  |

| SY36               | Tvreg     | Voltage Regulator<br>Standby-to-Active mode<br>Transition Time |                                                                                                                                                                                                                                                                                         | _                   | 30   | μS    |                                                                                                                   |  |

| SY37               | Toscdfrc  | FRC Oscillator Start-up<br>Delay                               |                                                                                                                                                                                                                                                                                         | _                   | 29   | μS    |                                                                                                                   |  |

| SY38               | TOSCDLPRC | LPRC Oscillator Start-up<br>Delay                              |                                                                                                                                                                                                                                                                                         | —                   | 70   | μS    |                                                                                                                   |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

NOTES:

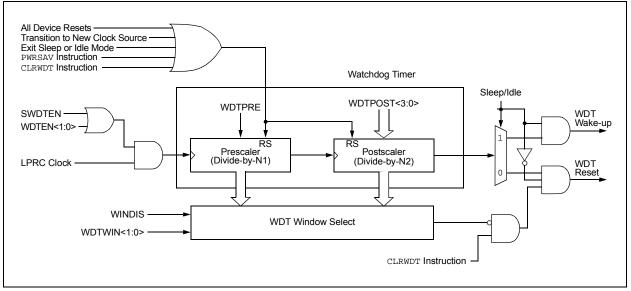

### 27.2 Package Details

## 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    | MILLIMETERS |          |       |  |

|--------------------------|----------|-------------|----------|-------|--|

| Dimensio                 | n Limits | MIN         | NOM      | MAX   |  |

| Number of Pins           | Ν        |             | 28       |       |  |

| Pitch                    | е        |             | 0.65 BSC |       |  |

| Overall Height           | А        | -           | -        | 2.00  |  |

| Molded Package Thickness | A2       | 1.65        | 1.75     | 1.85  |  |

| Standoff                 | A1       | 0.05        | -        | -     |  |

| Overall Width            | Е        | 7.40        | 7.80     | 8.20  |  |

| Molded Package Width     | E1       | 5.00        | 5.30     | 5.60  |  |

| Overall Length           | D        | 9.90        | 10.20    | 10.50 |  |

| Foot Length              | L        | 0.55        | 0.75     | 0.95  |  |

| Footprint                | L1       |             | 1.25 REF |       |  |

| Lead Thickness           | С        | 0.09        | _        | 0.25  |  |

| Foot Angle               | φ        | 0°          | 4°       | 8°    |  |

| Lead Width               | b        | 0.22        | -        | 0.38  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

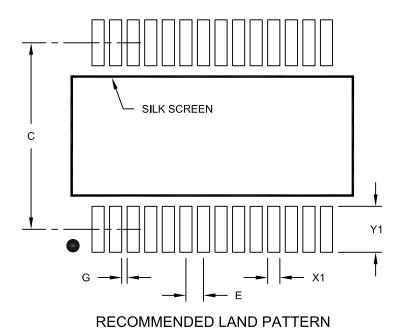

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |      |          |      |  |

|--------------------------|------------------|------|----------|------|--|

| Dimensio                 | Dimension Limits |      |          | MAX  |  |

| Contact Pitch            | E                |      | 0.65 BSC |      |  |

| Contact Pad Spacing      | С                |      | 7.20     |      |  |

| Contact Pad Width (X28)  | X1               |      |          | 0.45 |  |

| Contact Pad Length (X28) | Y1               |      |          | 1.75 |  |

| Distance Between Pads    | G                | 0.20 |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

NOTES: