Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 12x12b; D/A 2x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C                                                                   |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-UQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-UQFN (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gs202-e-mx |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(1,2)</sup>                                                        |

|---------|----------------------------------------------------------------------------------------------------------------------------|

|         | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled                                                 |

|         | 110 = CPU Interrupt Priority Level is 6 (14)                                                                               |

|         | 101 = CPU Interrupt Priority Level is 5 (13)                                                                               |

|         | 100 = CPU Interrupt Priority Level is 4 (12)                                                                               |

|         | 011 = CPU Interrupt Priority Level is 3 (11)                                                                               |

|         | 010 = CPU Interrupt Priority Level is 2 (10)                                                                               |

|         | 001 = CPU Interrupt Priority Level is 1 (9)                                                                                |

|         | 000 = CPU Interrupt Priority Level is 0 (8)                                                                                |

| bit 4   | RA: REPEAT Loop Active bit                                                                                                 |

|         | 1 = REPEAT loop is in progress                                                                                             |

|         | 0 = REPEAT loop is not in progress                                                                                         |

| bit 3   | N: MCU ALU Negative bit                                                                                                    |

|         | 1 = Result was negative                                                                                                    |

|         | 0 = Result was non-negative (zero or positive)                                                                             |

| bit 2   | OV: MCU ALU Overflow bit                                                                                                   |

|         | This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that                    |

|         | causes the sign bit to change state.                                                                                       |

|         | 1 = Overflow occurred for signed arithmetic (in this arithmetic operation)                                                 |

|         | 0 = No overflow occurred                                                                                                   |

| bit 1   | Z: MCU ALU Zero bit                                                                                                        |

|         | 1 = An operation that affects the Z bit has set it at some time in the past                                                |

|         | 0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)                              |

| bit 0   | C: MCU ALU Carry/Borrow bit                                                                                                |

|         | 1 = A carry-out from the Most Significant bit of the result occurred                                                       |

|         | 0 = No carry-out from the Most Significant bit of the result occurred                                                      |

| Note 1: | The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority                      |

|         | Level The value is parentheses indicates the $ \mathbf{P} $ if $ \mathbf{P}  < 2 > -1$ . User interrupts are disabled when |

- Note 1: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priorit Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 2: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **3:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

| File<br>Name | Addr. | Bit 15 | Bit 14    | Bit 13    | Bit 12    | Bit 11  | Bit 10     | Bit 9      | Bit 8      | Bit 7    | Bit 6      | Bit 5      | Bit 4      | Bit 3   | Bit 2     | Bit 1     | Bit 0     | All<br>Resets |

|--------------|-------|--------|-----------|-----------|-----------|---------|------------|------------|------------|----------|------------|------------|------------|---------|-----------|-----------|-----------|---------------|

| IPC16        | 0860  | _      | —         | —         | —         | —       | —          | —          | _          | —        | U1EIP2     | U1EIP1     | U1EIP0     | —       | _         | —         | —         | 0040          |

| IPC18        | 0864  | _      | _         | _         | _         | —       | _          | -          | _          | _        | PSESIP2    | PSESIP1    | PSESIP0    | _       | _         | —         | _         | 0040          |

| IPC23        | 086E  | _      | PWM2IP2   | PWM2IP1   | PWM2IP0   | _       | PWM1IP2    | PWM1IP1    | PWM1IP0    | _        | _          | _          | _          | _       | —         | _         | _         | 4400          |

| IPC24        | 0870  | _      | _         | _         | _         | _       | _          | _          | _          | _        | _          | _          | _          | _       | PWM3IP2   | PWM3IP1   | PWM3IP0   | 0004          |

| IPC25        | 0872  | _      | AC2IP2    | AC2IP1    | AC2IP0    | —       | _          | -          | _          | _        | _          | _          | _          | _       | _         | —         | _         | 4000          |

| IPC27        | 0876  | _      | ADCAN1IP2 | ADCAN1IP1 | ADCAN1IP0 | _       | ADCAN0IP2  | ADCAN0IP1  | ADCAN0IP0  | _        | _          | _          | _          | _       | —         | _         | _         | 4400          |

| IPC28        | 0878  | _      | ADCAN5IP2 | ADCAN5IP1 | ADCAN5IP0 | _       | ADCAN4IP2  | ADCAN4IP1  | ADCAN4IP0  | _        | ADCAN3IP2  | ADCAN3IP1  | ADCAN3IP0  | _       | ADCAN2IP2 | ADCAN2IP1 | ADCAN2IP0 | 4444          |

| IPC29        | 087A  | _      | _         | _         | _         | _       | _          | _          | _          | _        | ADCAN7IP2  | ADCAN7IP1  | ADCAN7IP0  | _       | ADCAN6IP2 | ADCAN6IP1 | ADCAN6IP0 | 0044          |

| IPC35        | 0886  | _      | _         | _         | _         | _       | ICDIP2     | ICDIP1     | ICDIP0     | _        | _          | _          | _          | _       | —         | —         | _         | 0400          |

| IPC37        | 088A  | _      | ADCAN8IP2 | ADCAN8IP1 | ADCAN8IP0 | _       | _          | -          | _          | _        | _          | _          | -          | _       | _         | -         | _         | 4000          |

| IPC38        | 088C  | _      | _         | _         | _         | _       | ADCAN11IP2 | ADCAN11IP1 | ADCAN11IP0 | _        | ADCAN10IP2 | ADCAN10IP1 | ADCAN10IP0 | _       | ADCAN9IP2 | ADCAN9IP1 | ADCAN9IP0 | 0444          |

| IPC39        | 088E  | _      | _         | _         | _         | —       | _          | -          | _          | _        | ADCAN14IP2 | ADCAN14IP1 | ADCAN14IP0 | _       | _         | —         | _         | 0040          |

| IPC43        | 0896  | _      | _         | _         | _         | _       | _          | -          | _          | _        | I2C1BCIP2  | I2C1BCIP1  | I2C1BCIP0  | _       | _         | -         | _         | 0040          |

| IPC44        | 0898  | _      | ADFL0IP2  | ADFL0IP1  | ADFL0IP0  | _       | ADCMP1IP2  | ADCMP1IP1  | ADCMP1IP0  | _        | ADCMP1IP2  | ADCMP1IP1  | ADCMP1IP0  | _       | _         | _         | _         | 4440          |

| INTCON1      | 08C0  | NSTDIS | OVAERR    | OVBERR    | COVAERR   | COVBERR | OVATE      | OVBTE      | COVTE      | SFTACERR | DIV0ERR    | _          | MATHERR    | ADDRERR | STKERR    | OSCFAIL   | _         | 0000          |

| INTCON2      | 08C2  | GIE    | DISI      | SWTRAP    | _         | _       | _          | _          | AIVTEN     | _        | _          | _          | _          | _       | INT2EP    | INT1EP    | INT0EP    | 8000          |

| INTCON3      | 08C4  | _      | _         | _         | _         | —       | _          | _          | NAE        | _        | _          | _          | DOOVR      | _       | _         | —         | APLL      | 0000          |

| INTCON4      | 08C6  | _      | _         | _         | _         | _       | _          | _          | _          | _        | _          | _          | _          | _       | —         | —         | SGHT      | 0000          |

| INTTREG      | 08C8  | _      | _         | _         | _         | ILR3    | ILR2       | ILR1       | ILR0       | VECNUM7  | VECNUM6    | VECNUM5    | VECNUM4    | VECNUM3 | VECNUM2   | VECNUM1   | VECNUM0   | 0000          |

# TABLE 4-3: INTERRUPT CONTROLLER REGISTER MAP (CONTINUED)

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-14: ADC REGISTER MAP

| File<br>Name | Addr. | Bit 15             | Bit 14             | Bit 13  | Bit 12  | Bit 11  | Bit 10       | Bit 9     | Bit 8     | Bit 7         | Bit 6    | Bit 5     | Bit 4     | Bit 3     | Bit 2        | Bit 1     | Bit 0     | All<br>Resets |

|--------------|-------|--------------------|--------------------|---------|---------|---------|--------------|-----------|-----------|---------------|----------|-----------|-----------|-----------|--------------|-----------|-----------|---------------|

| ADCON1L      | 0300  | ADON               | _                  | ADSIDL  | _       | _       | _            | _         | _         | —             | _        | _         | -         | -         | -            | _         | -         | 1000          |

| ADCON1H      | 0302  | _                  | _                  | _       | _       | _       | _            | _         | _         | FORM          | SHRRES1  | SHRRES0   | -         | _         | _            | _         | -         | 0060          |

| ADCON2L      | 0304  | REFCIE             | REFERCIE           | _       | EIEN    | _       | SHREISEL2    | SHREISEL1 | SHREISEL0 | _             | SHRADCS6 | SHRADCS5  | SHRADCS4  | SHRADCS3  | SHRADCS2     | SHRADCS1  | SHRADCS0  | 0000          |

| ADCON2H      | 0306  | REFRDY             | REFERR             | _       | _       | _       | _            | SHRSAMC9  | SHRSAMC8  | SHRSAMC7      | SHRSAMC6 | SHRSAMC5  | SHRSAMC4  | SHRSAMC3  | SHRSAMC2     | SHRSAMC1  | SHRSAMC0  | 0000          |

| ADCON3L      | 0308  | REFSEL2            | REFSEL1            | REFSEL0 | SUSPEND | SUSPCIE | SUSPRDY      | SHRSAMP   | CNVRTCH   | SWLCTRG       | SWCTRG   | CNVCHSEL5 | CNVCHSEL4 | CNVCHSEL3 | CNVCHSEL2    | CNVCHSEL1 | CNVCHSEL0 | 0000          |

| ADCON3H      | 030A  | CLKSEL1            | CLKSEL0            | CLKDIV5 | CLKDIV4 | CLKDIV3 | CLKDIV2      | CLKDIV1   | CLKDIV0   | SHREN         |          | _         | -         | —         | -            | C1EN      | COEN      | 0000          |

| ADCON4L      | 030C  | _                  | _                  | —       | _       | -       | -            | SYNCTRG1  | SYNCTRG0  | _             | -        | _         | -         | _         | _            | SAMC1EN   | SAMC0EN   | 0000          |

| ADCON4H      | 030E  | _                  | -                  | _       | _       | _       | _            | -         | -         | _             | -        | _         | _         | C1CHS1    | C1CHS0       | C0CHS1    | C0CHS0    | 0000          |

| ADMOD0L      | 0310  | -                  | SIGN7              | _       | SIGN6   | -       | SIGN5        | -         | SIGN4     | _             | SIGN3    | _         | SIGN2     | DIFF1     | SIGN1        | DIFF0     | SIGN0     | 0000          |

| ADMOD0H      | 0312  | _                  | _                  | DIFF14  | SIGN14  | -       | SIGN13       | -         | SIGN12    | _             | SIGN11   | —         | SIGN10    | _         | SIGN9        | —         | SIGN8     | 0000          |

| ADIEL        | 0320  | -                  | IE14               | _       | _       |         |              |           |           |               | IE·      | <11:0     |           |           |              |           |           | 0000          |

| ADSTATL      | 0330  | -                  | AN14RDY            | _       | _       | AN11RDY | AN10RDY      | AN9RDY    | AN8RDY    | AN7RDY        | AN6RDY   | AN5RDY    | AN4RDY    | AN3RDY    | AN2RDY       | AN1RDY    | ANORDY    | 0000          |

| ADCMP0ENL    | 0338  | -                  | CMPEN14            | _       | _       |         |              |           |           |               | CMPE     | N<11:0>   |           |           |              |           |           | 0000          |

| ADCMP0LO     | 033C  |                    | ADC CMPLO Register |         |         |         |              |           |           |               |          |           |           | 0000      |              |           |           |               |

| ADCMP0HI     | 033E  | ADC CMPHI Register |                    |         |         |         |              |           |           |               |          |           | 0000      |           |              |           |           |               |

| ADCMP1ENL    | 0340  | CMPEN14 CMPEN11:0> |                    |         |         |         |              |           |           |               |          |           | 0000      |           |              |           |           |               |

| ADCMP1LO     | 0344  | ADC CMPLO Register |                    |         |         |         |              |           |           |               |          |           | 0000      |           |              |           |           |               |

| ADCMP1HI     | 0346  |                    |                    |         |         |         |              |           | ADC       | CMPHI Registe | er       |           |           |           |              |           |           | 0000          |

| ADFL0DAT     | 0368  |                    |                    | -       | -       |         | -            |           | ADC F     | LDATA Regist  | er       | -         | -         |           | -            |           |           | 0000          |

| ADFL0CON     | 036A  | FLEN               | MODE1              | MODE0   | OVRSAM2 | OVRSAM1 | OVRSAM0      | IE        | RDY       | _             | -        | _         | FLCHSEL4  | FLCHSEL3  | FLCHSEL2     | FLCHSEL1  | FLCHSEL0  | 0000          |

| ADTRIG0L     | 0380  | _                  | _                  | —       |         |         | TRGSRC1<4:0  | >         |           | _             | -        | _         |           |           | TRGSRC0<4:0> | ,         |           | 0000          |

| ADTRIG0H     | 0382  | _                  | _                  | —       |         |         | TRGSRC3<4:0  | >         |           | _             | -        | _         |           |           | TRGSRC2<4:0> |           |           | 0000          |

| ADTRIG1L     | 0384  | -                  | -                  | _       |         |         | TRGSRC5<4:0  | >         |           | _             | -        | _         |           |           | TRGSRC4<4:0> | •         |           | 0000          |

| ADTRIG1H     | 0386  | _                  | _                  | —       |         |         | TRGSRC7<4:0  | >         |           | _             | -        | _         |           |           | TRGSRC6<4:0> |           |           | 0000          |

| ADTRIG2L     | 0388  | _                  | _                  | —       |         |         | TRGSRC9<4:0  | >         |           | _             | -        | _         |           |           | TRGSRC8<4:0> |           |           | 0000          |

| ADTRIG2H     | 038A  | -                  | -                  | _       |         |         | TRGSRC11<4:0 | >         |           | _             | -        | _         |           |           | TRGSRC10<4:0 | >         |           | 0000          |

| ADTRIG3L     | 038C  | -                  | -                  | _       |         |         | TRGSRC13<4:0 | >         |           | _             | -        | _         |           |           | TRGSRC12<4:0 | >         |           | 0000          |

| ADTRIG3H     | 038E  | -                  | -                  | _       | _       | -       | _            | -         | -         | _             | -        | _         |           |           | TRGSRC14<4:0 | >         |           | 0000          |

| ADCMP0CON    | 03A0  | -                  | -                  | _       | CHNL4   | CHNL3   | CHNL2        | CHNL1     | CHNL0     | CMPEN         | IE       | STAT      | BTWN      | HIHI      | HILO         | LOHI      | LOLO      | 0000          |

| ADCMP1CON    | 03A4  | _                  |                    | _       | CHNL4   | CHNL3   | CHNL2        | CHNL1     | CHNL0     | CMPEN         | E        | STAT      | BTWN      | HIHI      | HILO         | LOHI      | LOLO      | 0000          |

| ADLVLTRGL    | 03D0  | -                  | LVLEN14            | _       | _       |         |              |           |           |               | LVLE     | N<11:0>   |           |           |              |           |           | 0000          |

| ADCORE0L     | 03D4  | —                  |                    | _       | _       | _       | _            |           |           |               |          | SAM       | IC<9:0>   |           |              |           |           | 0000          |

| ADCORE0H     | 03D6  | _                  | -                  | _       | EISEL2  | EISEL1  | EISEL0       | RES1      | RES0      | _             | ADCS6    | ADCS5     | ADCS4     | ADCS3     | ADCS2        | ADCS1     | ADCS0     | 0000          |

| ADCORE1L     | 03D8  | _                  | -                  | _       | _       | _       | _            |           |           |               |          | SAM       | IC<9:0>   |           |              |           |           | 0000          |

| ADCORE1H     | 03DA  | _                  |                    | _       | EISEL2  | EISEL1  | EISEL0       | RES1      | RES0      | —             | ADCS6    | ADCS5     | ADCS4     | ADCS3     | ADCS2        | ADCS1     | ADCS0     | 0000          |

| ADEIEL       | 03F0  | _                  | EIEN14             | _       | —       |         |              |           |           |               | EIEI     | N<11:0    |           |           |              |           |           | 0000          |

| ADEISTATL    | 03F8  | _                  | EISTAT14           | _       | _       |         |              |           |           |               | EISTA    | T<11:0>   |           |           |              |           |           | 0000          |

dsPIC33EPXXGS202 FAMILY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

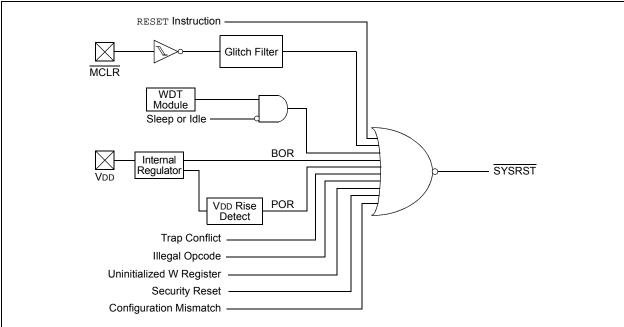

# 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Time-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

# A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state, and some are unaffected.

Note: Refer to the specific peripheral section or Section 4.0 "Memory Organization" of this manual for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the BOR and POR bits (RCON<1:0>) that are set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

Note: The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

For all Resets, the default clock source is determined by the FNOSC<2:0> bits in the FOSCSEL Configuration register. The value of the FNOSCx bits is loaded into the NOSC<2:0> (OSCCON<10:8>) bits on Reset, which in turn, initializes the system clock.

# FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

# TABLE 8-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

| Oscillator Mode                                            | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Notes |

|------------------------------------------------------------|-------------------|-------------|------------|--------------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)              | Internal          | xx          | 111        | 1, 2         |

| Fast RC Oscillator with Divide-by-16                       | Internal          | xx          | 110        | 1            |

| Low-Power RC Oscillator (LPRC)                             | Internal          | xx          | 101        | 1            |

| Primary Oscillator (HS) with PLL (HSPLL)                   | Primary           | 10          | 011        |              |

| Primary Oscillator (XT) with PLL (XTPLL)                   | Primary           | 01          | 011        |              |

| Primary Oscillator (EC) with PLL (ECPLL)                   | Primary           | 0.0         | 011        | 1            |

| Primary Oscillator (HS)                                    | Primary           | 10          | 010        |              |

| Primary Oscillator (XT)                                    | Primary           | 01          | 010        |              |

| Primary Oscillator (EC)                                    | Primary           | 00          | 010        | 1            |

| Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL) | Internal          | XX          | 001        | 1            |

| Fast RC Oscillator (FRC)                                   | Internal          | xx          | 000        | 1            |

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

## 8.2 Auxiliary Clock Generation

The auxiliary clock generation is used for peripherals that need to operate at a frequency unrelated to the system clock, such as PWM or ADC.

The primary oscillator and internal FRC oscillator sources can be used with an Auxiliary PLL (APLL) to obtain the auxiliary clock. The Auxiliary PLL has a fixed 16x multiplication factor.

The auxiliary clock has the following configuration restrictions:

- For proper PWM operation, auxiliary clock generation must be configured for 120 MHz (see Parameter OS56 in Section 25.0 "Electrical Characteristics"). If a slower frequency is desired, the PWM Input Clock Prescaler (Divider) Select bits (PCLKDIV<2:0>) should be used.

- To achieve 1.04 ns PWM resolution, the auxiliary clock must use the 16x Auxiliary PLL (APLL). All other clock sources will have a minimum PWM resolution of 8 ns.

- If the primary PLL is used as a source for the auxiliary clock, the primary PLL should be configured up to a maximum operation of 30 MIPS or less.

# 8.3 Oscillator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 8.3.1 KEY RESOURCES

- "Oscillator Module" (DS70005131) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

| Input Name <sup>(1)</sup> | Function Name | Register | Configuration Bits |

|---------------------------|---------------|----------|--------------------|

| External Interrupt 1      | INT1          | RPINR0   | INT1R<7:0>         |

| External Interrupt 2      | INT2          | RPINR1   | INT2R<7:0>         |

| Timer1 External Clock     | T1CK          | RPINR2   | T1CKR<7:0>         |

| Timer2 External Clock     | T2CK          | RPINR3   | T2CKR<7:0>         |

| Timer3 External Clock     | T3CK          | RPINR3   | T3CKR<7:0>         |

| Input Capture 1           | IC1           | RPINR7   | IC1R<7:0>          |

| Output Compare Fault A    | OCFA          | RPINR11  | OCFAR<7:0>         |

| PWM Fault 1               | FLT1          | RPINR12  | FLT1R<7:0>         |

| PWM Fault 2               | FLT2          | RPINR12  | FLT2R<7:0>         |

| PWM Fault 3               | FLT3          | RPINR13  | FLT3R<7:0>         |

| PWM Fault 4               | FLT4          | RPINR13  | FLT4R<7:0>         |

| UART1 Receive             | U1RX          | RPINR18  | U1RXR<7:0>         |

| UART1 Clear-to-Send       | U1CTS         | RPINR18  | U1CTSR<7:0>        |

| SPI1 Data Input           | SDI1          | RPINR20  | SDI1R<7:0>         |

| SPI1 Clock Input          | SCK1          | RPINR20  | SCK1R<7:0>         |

| SPI1 Slave Select         | SS1           | RPINR21  | SS1R<7:0>          |

| PWM Synchronous Input 1   | SYNCI1        | RPINR37  | SYNCI1R<7:0>       |

| PWM Synchronous Input 2   | SYNCI2        | RPINR38  | SYNCI2R<7:0>       |

| PWM Fault 5               | FLT5          | RPINR42  | FLT5R<7:0>         |

| PWM Fault 6               | FLT6          | RPINR42  | FLT6R<7:0>         |

| PWM Fault 7               | FLT7          | RPINR43  | FLT7R<7:0>         |

| PWM Fault 8               | FLT8          | RPINR43  | FLT8R<7:0>         |

#### TABLE 10-1: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION)

Note 1: Unless otherwise noted, all inputs use the Schmitt Trigger input buffers.

# 10.5 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 25-11 under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device, that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD - 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristics specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the Absolute Maximum Ratings in **Section 25.0 "Electrical Characteristics"**of this data sheet. For example:

VOH = 2.4V @ IOH = -8 mA and VDD = 3.3VThe maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted.

| U-0    | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| _      | _   | RP177R5 | RP177R4 | RP177R3 | RP177R2 | RP177R1 | RP177R0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

|        |     |         |         |         |         |         |         |

| U-0    | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

#### REGISTER 10-24: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | RP176R5 | RP176R4 | RP176R3 | RP176R2 | RP176R1 | RP176R0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP177R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP177 Output Pin bits (see Table 10-2 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                                 |

| bit 5-0   | <b>RP176R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP176 Output Pin bits (see Table 10-2 for peripheral function numbers) |

### REGISTER 10-25: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0    | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| —      | —   | RP179R5 | RP179R4 | RP179R3 | RP179R2 | RP179R1 | RP179R0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | RP178R5 | RP178R4 | RP178R3 | RP178R2 | RP178R1 | RP178R0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP179R<5:0>:** Peripheral Output Function is Assigned to RP179 Output Pin bits (see Table 10-2 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0' bit 5-0 RP178R<5:0>: Peripheral Output Function is

bit 5-0 **RP178R<5:0>:** Peripheral Output Function is Assigned to RP178 Output Pin bits (see Table 10-2 for peripheral function numbers)

| R/W-0              | U-0                                       | R/W-0                             | U-0                    | U-0                        | U-0            | U-0                | U-0         |

|--------------------|-------------------------------------------|-----------------------------------|------------------------|----------------------------|----------------|--------------------|-------------|

| TON <sup>(1)</sup> | —                                         | TSIDL <sup>(2)</sup>              | _                      | —                          | _              |                    | _           |

| bit 15             |                                           |                                   |                        |                            |                |                    | bit         |

|                    |                                           |                                   |                        |                            |                |                    |             |

| U-0                | R/W-0                                     | R/W-0                             | R/W-0                  | U-0                        | U-0            | R/W-0              | U-0         |

|                    | TGATE <sup>(1)</sup>                      | TCKPS1 <sup>(1)</sup>             | TCKPS0 <sup>(1)</sup>  | —                          |                | TCS <sup>(1)</sup> | —           |

| bit 7              |                                           |                                   |                        |                            |                |                    | bit         |

| Legend:            |                                           |                                   |                        |                            |                |                    |             |

| R = Reada          | ble bit                                   | W = Writable t                    | bit                    | U = Unimplem               | nented bit, re | ad as '0'          |             |

| -n = Value         | at POR                                    | '1' = Bit is set                  |                        | '0' = Bit is clea          | ared           | x = Bit is unkno   | own         |

|                    |                                           |                                   |                        |                            |                |                    |             |

| bit 15             | TON: Timer3                               | On bit <sup>(1)</sup>             |                        |                            |                |                    |             |

|                    | 1 = Starts 16-                            | bit Timer3                        |                        |                            |                |                    |             |

|                    | 0 = Stops 16-                             | bit Timer3                        |                        |                            |                |                    |             |

| bit 14             | Unimplemen                                | ted: Read as '0                   | ,                      |                            |                |                    |             |

| bit 13             | TSIDL: Timer                              | 3 Stop in Idle M                  | ode bit <sup>(2)</sup> |                            |                |                    |             |

|                    |                                           | ues module ope<br>s module operat |                        |                            | e mode         |                    |             |

| bit 12-7           | Unimplemen                                | ted: Read as '0                   | 2                      |                            |                |                    |             |

| bit 6              | TGATE: Time                               | r3 Gated Time                     | Accumulation I         | Enable bit <sup>(1)</sup>  |                |                    |             |

|                    | When TCS =<br>This bit is igno            |                                   |                        |                            |                |                    |             |

|                    | When TCS =                                |                                   |                        |                            |                |                    |             |

|                    | 1 = Gated tim                             | e accumulation<br>e accumulation  |                        |                            |                |                    |             |

| bit 5-4            | TCKPS<1:0>                                | : Timer3 Input C                  | lock Prescale          | Select bits <sup>(1)</sup> |                |                    |             |

|                    | 11 <b>= 1:256</b>                         |                                   |                        |                            |                |                    |             |

|                    | 10 <b>= 1:64</b>                          |                                   |                        |                            |                |                    |             |

|                    | 01 = 1:8                                  |                                   |                        |                            |                |                    |             |

|                    | 00 = 1:1                                  |                                   | ,                      |                            |                |                    |             |

| bit 3-2            | -                                         | ted: Read as '0                   |                        |                            |                |                    |             |

| bit 1              |                                           | Clock Source S                    |                        |                            |                |                    |             |

|                    | 1 = External o<br>0 = Periphera           | clock is from pin<br>I Clock (FP) | , T3CK (on the         | rising eage)               |                |                    |             |

| bit 0              | Unimplemen                                | ted: Read as '0                   | ,                      |                            |                |                    |             |

|                    | When 32-bit operative timer functions are |                                   |                        | = 1), these bits           | have no effe   | ct on Timer3 ope   | ration; all |

2: When 32-bit timer operation is enabled (T32 = 1) in the Timer2 Control register (T2CON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

x = Bit is unknown

# **REGISTER 15-15: PHASEx: PWMx PRIMARY PHASE-SHIFT REGISTER**<sup>(1,2)</sup>

| R/W-0        | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0  | R/W-0 |

|--------------|-------|------------------|-------|--------------|------------------|--------|-------|

|              |       |                  | PHAS  | Ex<15:8>     |                  |        |       |

| bit 15       |       |                  |       |              |                  |        | bit 8 |

|              |       |                  |       |              |                  |        |       |

| R/W-0        | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0  | R/W-0 |

|              |       |                  | PHAS  | SEx<7:0>     |                  |        |       |

| bit 7        |       |                  |       |              |                  |        | bit 0 |

|              |       |                  |       |              |                  |        |       |

| Legend:      |       |                  |       |              |                  |        |       |

| R = Readable | bit   | W = Writable bit |       | U = Unimpler | nented bit, read | as '0' |       |

bit 15-0 PHASEx<15:0>: PWMx Phase-Shift Value or Independent Time Base Period for the PWMx Generator bits

**Note 1:** If PWMCONx<9> = 0, the following applies based on the mode of operation:

'1' = Bit is set

- Complementary, Redundant and Push-Pull Output mode (IOCONx<11:10> = 00, 01 or 10); PHASEx<15:0> = Phase-shift value for PWMxH and PWMxL outputs

- True Independent Output mode (IOCONx<11:10> = 11); PHASEx<15:0> = Phase-shift value for PWMxH only

- When the PHASEx/SPHASEx registers provide the phase shift with respect to the master time base; therefore, the valid range is 0x0000 through period

'0' = Bit is cleared

- **2:** If PWMCONx<9> = 1, the following applies based on the mode of operation:

- Complementary, Redundant, and Push-Pull Output mode (IOCONx<11:10> = 00, 01 or 10); PHASEx<15:0> = Independent time base period value for PWMxH and PWMxL

- True Independent Output mode (IOCONx<11:10> = 11); PHASEx<15:0> = Independent time base period value for PWMxH only

- When the PHASEx/SPHASEx registers provide the local period, the valid range is 0x0000 through 0xFFF8

-n = Value at POR

# 18.3 UART Control Registers

# REGISTER 18-1: U1MODE: UART1 MODE REGISTER

| R/W-0                 | U-0                          | R/W-0                                                             | R/W-0                         | R/W-0                                        | U-0                        | R/W-0            | R/W-0          |

|-----------------------|------------------------------|-------------------------------------------------------------------|-------------------------------|----------------------------------------------|----------------------------|------------------|----------------|

| UARTEN <sup>(1)</sup> |                              | USIDL                                                             | IREN <sup>(2)</sup>           | RTSMD                                        |                            | UEN1             | UEN0           |

| bit 15                |                              |                                                                   |                               |                                              |                            |                  | bit 8          |

|                       | 5444.6                       |                                                                   |                               | 5444.0                                       | 5444.6                     |                  |                |

| R/W-0, HC             | R/W-0                        | R/W-0, HC                                                         | R/W-0                         | R/W-0                                        | R/W-0                      | R/W-0            | R/W-0          |

| WAKE                  | LPBACK                       | ABAUD                                                             | URXINV                        | BRGH                                         | PDSEL1                     | PDSEL0           | STSEL          |

| pit 7                 |                              |                                                                   |                               |                                              |                            |                  | bit C          |

| Legend:               |                              | HC = Hardwar                                                      | e Clearable b                 | it                                           |                            |                  |                |

| R = Readable          | e bit                        | W = Writable b                                                    | it                            | U = Unimplem                                 | ented bit, read            | as '0'           |                |

| -n = Value at         | POR                          | '1' = Bit is set                                                  |                               | '0' = Bit is clea                            | ired                       | x = Bit is unkn  | own            |

| bit 15                | UARTEN: UA                   | ART1 Enable bit                                                   | (1)                           |                                              |                            |                  |                |

|                       |                              | s enabled; all UA                                                 |                               | controlled by U                              | ART1, as defir             | ned by UEN<1:0   | >              |

|                       |                              | s disabled; all U                                                 |                               |                                              |                            |                  |                |

| bit 14                | Unimplemen                   | ted: Read as '0                                                   | ,                             |                                              |                            |                  |                |

| oit 13                | USIDL: UAR                   | T1 Stop in Idle M                                                 | lode bit                      |                                              |                            |                  |                |

|                       |                              | ues module ope                                                    |                               |                                              | le mode                    |                  |                |

|                       |                              | s module opera                                                    |                               |                                              |                            |                  |                |

| oit 12                |                              | Encoder and De                                                    |                               |                                              |                            |                  |                |

|                       |                              | oder and decod                                                    |                               |                                              |                            |                  |                |

| bit 11                |                              | le Selection for                                                  |                               |                                              |                            |                  |                |

|                       | 1 = U1RTS p                  | in is in Simplex<br>in is in Flow Co                              | mode                          | ·                                            |                            |                  |                |

| bit 10                | •                            | ted: Read as '0                                                   |                               |                                              |                            |                  |                |

| bit 9-8               | UEN<1:0>: U                  | ART1 Pin Enab                                                     | le bits                       |                                              |                            |                  |                |

|                       | 10 = U1TX, U<br>01 = U1TX, U | J1RX and BCLK<br>J1RX, U1CTS a<br>J1RX and U1RT<br>nd U1RX pins a | nd U1RTS pir<br>S pins are en | ns are enabled a<br>abled an <u>d used</u> ; | ind used<br>; U1CTS pin is | controlled by P  | ORT latches    |

| bit 7                 |                              | e-up on Start bit                                                 | Detect During                 | Sleen Mode Er                                | able bit                   |                  |                |

|                       | 1 = UART1 c                  | continues to sam<br>are on the follow                             | ple the U1RX                  | pin, interrupt is                            |                            | the falling edge | bit is cleared |

|                       |                              | -up is enabled                                                    |                               | ,-                                           |                            |                  |                |

| oit 6                 | LPBACK: UA                   | RT1 Loopback                                                      | Mode Select                   | bit                                          |                            |                  |                |

|                       |                              | Loopback mode<br>k mode is disabl                                 |                               |                                              |                            |                  |                |

| oit 5                 | ABAUD: Auto                  | o-Baud Enable b                                                   | bit                           |                                              |                            |                  |                |

|                       | before ot                    | baud rate meas<br>her data; cleare<br>e measurement               | d in hardware                 | upon completio                               |                            | eception of a Sy | nc field (55h  |

|                       | efer to "Univers             | emeasurement                                                      |                               | completed                                    |                            |                  |                |

**2:** This feature is only available for the 16x BRG mode (BRGH = 0).

# 19.0 HIGH-SPEED, 12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "12-Bit High-Speed, Multiple SARs A/D Converter (ADC)" (DS70005213) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXGS202 devices have a highspeed, 12-bit Analog-to-Digital Converter (ADC) that features a low conversion latency, high resolution and oversampling capabilities to improve performance in AC/DC, DC/DC power converters.

# **19.1 Features Overview**

The 12-Bit High Speed Multiple SARs Analog-to-Digital Converter (ADC) includes the following features:

- 12-Bit Resolution

- Up to 3.25 Msps Conversion Rate per ADC Core @ 12-Bit Resolution

- Multiple Dedicated ADC Cores

- One Shared (common) ADC Core

- Up to 12 Analog Input Sources

- Conversion Result can be Formatted as Unsigned or Signed Data on a per Channel Basis for All Channels

- Separate 16-Bit Conversion Result Register for each Analog Input

- Simultaneous Sampling of up to 3 Analog Inputs

- Flexible Trigger Options

- Early Interrupt Generation to Enable Fast Processing of Converted Data

- Two Integrated Digital Comparators:

- Multiple comparison options

- Assignable to specific analog inputs

- · Oversampling Filters:

- Provides increased resolution

- Assignable to a specific analog input

- · Operation During CPU Sleep and Idle modes

Simplified block diagrams of the Multiple SARs 12-Bit ADC are shown in Figure 19-1, Figure 19-2 and Figure 19-3.

The module consists of two independent SAR ADC cores. The analog inputs (channels) are connected through multiplexers and switches to the Sample-and-Hold (S/H) circuit of each ADC core. The core uses the channel information (the output format, the measurement mode and the input number) to process the analog sample. When conversion is complete, the result is stored in the result buffer for the specific analog input and passed to the digital filter and digital comparator if they were configured to use data from this particular channel.

The ADC module can sample up to three inputs at a time (two inputs from the dedicated SAR ADC cores and one from the shared SAR ADC cores). If multiple ADC inputs request conversion, the ADC module will convert them in a sequential manner, starting with the lowest order input.

The ADC provides each analog input the ability to specify its own trigger source. This capability allows the ADC to sample and convert analog inputs that are associated with PWM generators operating on independent time bases.

#### REGISTER 19-5: ADCON3L: ADC CONTROL REGISTER 3 LOW

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R-0, HS, HC | R/W-0   | R-0, HS, HC |

|---------|---------|---------|---------|---------|-------------|---------|-------------|

| REFSEL2 | REFSEL1 | REFSEL0 | SUSPEND | SUSPCIE | SUSPRDY     | SHRSAMP | CNVRTCH     |

| bit 15  |         |         |         |         |             |         | bit 8       |

| R/W-0   | R-0, HS, HC | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     |

|---------|-------------|-----------|-----------|-----------|-----------|-----------|-----------|

| SWLCTRG | SWCTRG      | CNVCHSEL5 | CNVCHSEL4 | CNVCHSEL3 | CNVCHSEL2 | CNVCHSEL1 | CNVCHSEL0 |

| bit 7   |             |           |           |           |           |           | bit 0     |

| Legend:           | HS = Hardware Settable bit | HC = Hardware Clearable bit |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 15-13 REFSEL<2:0>: ADC Reference Voltage Selection bits

|        | Value                            | VREFH                                                      | VREFL        |                                                                                                                                 |  |  |  |  |

|--------|----------------------------------|------------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|        | 000                              | AVdd                                                       | AVss         |                                                                                                                                 |  |  |  |  |

|        | 001-111 <b>= U</b> I             | nimplement                                                 | ed: Should   | not be used                                                                                                                     |  |  |  |  |

| bit 12 | SUSPEND: A                       | II ADC Core                                                | s Triggers D | visable bit                                                                                                                     |  |  |  |  |

|        | 1 = All new tri<br>0 = All ADC c |                                                            |              | Cores are disabled                                                                                                              |  |  |  |  |

| bit 11 | SUSPCIE: Su                      | SUSPCIE: Suspend All ADC Cores Common Interrupt Enable bit |              |                                                                                                                                 |  |  |  |  |

|        | and all pr                       | evious conv                                                | ersions are  | ed when ADC cores triggers are suspended (SUSPEND bit =<br>finished (SUSPRDY bit becomes set)<br>ed for suspend ADC cores event |  |  |  |  |

| bit 10 | SUSPRDY: A                       | II ADC Cores                                               | s Suspende   | d Flag bit                                                                                                                      |  |  |  |  |

|        |                                  |                                                            | •            | ISPEND bit = 1) and have no conversions in progress<br>sions in progress                                                        |  |  |  |  |

| bit 9  | SHRSAMP: S                       | Shared ADC                                                 | Core Samp    | ling Direct Control bit                                                                                                         |  |  |  |  |

|        |                                  |                                                            |              | dual channel conversion trigger controlled by the CNVRTCH bit                                                                   |  |  |  |  |

| bit 9 | SHRSAMP: Shared ADC Core Sampling Direct Control bit                                                                                                                                                                                                                                                                                                 |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | This bit should be used with the individual channel conversion trigger controlled by the CNVRTCH bit. It connects an analog input, specified by CNVCHSEL<5:0> bits, to the shared ADC core and allows extending the sampling time. This bit is not controlled by hardware and must be cleared before the conversion starts (setting CNVRTCH to '1'). |

|       | <ul> <li>1 = Shared ADC core samples an analog input specified by the CNVCHSEL&lt;5:0&gt; bits</li> <li>0 = Sampling is controlled by the shared ADC core hardware</li> </ul>                                                                                                                                                                        |

| bit 8 | CNVRTCH: Software Individual Channel Conversion Trigger bit                                                                                                                                                                                                                                                                                          |

|       | 1 = Single trigger is generated for an analog input specified by the CNVCHSEL<5:0> bits. When the bit                                                                                                                                                                                                                                                |

- is set, it is automatically cleared by hardware on the next instruction cycle.

- 0 = Next individual channel conversion trigger can be generated

- bit 7 SWLCTRG: Software Level-Sensitive Common Trigger bit

- 1 = Triggers are continuously generated for all channels with the software, level-sensitive, common trigger selected as a source in the ADTRIGxL and ADTRIGxH registers

- 0 = No software, level-sensitive, common triggers are generated

- bit 6 SWCTRG: Software Common Trigger bit

- 1 = Single trigger is generated for all channels with the software, common trigger selected as a source in the ADTRIGxL and ADTRIGxH registers. When the bit is set, it is automatically cleared by hardware on the next instruction cycle

- 0 = Ready to generate the next software, common trigger

- bit 5-0 **CNVCHSEL <5:0>:** Channel Number Selection for Software Individual Channel Conversion Trigger bits These bits define a channel to be converted when the CNVRTCH bit is set.

| R-0, HC, HS   | U-0                      | U-0                                    | U-0            | U-0                                     | U-0            | R-0, HC, HS | R-0, HC, HS |  |

|---------------|--------------------------|----------------------------------------|----------------|-----------------------------------------|----------------|-------------|-------------|--|

| SHRRDY        | —                        | —                                      | —              | —                                       | —              | C1RDY       | CORDY       |  |

| bit 15        |                          |                                        |                |                                         |                |             | bit 8       |  |

|               |                          |                                        |                |                                         |                |             |             |  |

| R/W-0         | U-0                      | U-0                                    | U-0            | U-0                                     | U-0            | R/W-0       | R/W-0       |  |

| SHRPWR        | —                        | _                                      | _              |                                         | —              | C1PWR       | COPWR       |  |

| bit 7         |                          |                                        |                |                                         |                |             | bit 0       |  |

|               |                          |                                        |                |                                         |                |             |             |  |

| Legend:       |                          | HS = Hardware                          | e Settable bit | HC = Hardwa                             | re Clearable b | it          |             |  |

| R = Readable  | e bit                    | W = Writable b                         | it             | U = Unimplemented bit, read as '0'      |                |             |             |  |

| -n = Value at | POR                      | '1' = Bit is set                       |                | '0' = Bit is cleared x = Bit is unknown |                |             |             |  |

|               |                          |                                        |                |                                         |                |             |             |  |

| bit 15        | SHRRDY: S                | Shared ADC Core                        | e Ready Flag b | bit                                     |                |             |             |  |

|               |                          | re is powered an                       |                | eration                                 |                |             |             |  |

|               |                          | re is not ready fo                     |                |                                         |                |             |             |  |

| bit 14-10     |                          | ented: Read as '                       |                |                                         |                |             |             |  |

| bit 9-8       |                          | RDY: Dedicated                         |                | , ,                                     |                |             |             |  |

|               |                          | ore x is powered<br>ore x is not ready |                | operation                               |                |             |             |  |

| bit 7         | SHRPWR:                  | Shared ADC Cor                         | e x Power Ena  | able bit                                |                |             |             |  |

|               | 1 = ADC Co               | ore x is powered                       |                |                                         |                |             |             |  |

|               | 0 = ADC Co               | ore x is off                           |                |                                         |                |             |             |  |

| bit 6-2       | Unimpleme                | ented: Read as '                       | 0'             |                                         |                |             |             |  |

| bit 1-0       | C1PWR:C0                 | PWR: Dedicated                         | I ADC Core x F | Power Enable bi                         | ts             |             |             |  |

|               | 1 = ADC Co<br>0 = ADC Co | ore x is powered<br>ore x is off       |                |                                         |                |             |             |  |

|               |                          |                                        |                |                                         |                |             |             |  |

# REGISTER 19-9: ADCON5L: ADC CONTROL REGISTER 5 LOW

## REGISTER 19-21: ADTRIGXH: ADC CHANNEL TRIGGER x SELECTION REGISTER HIGH

(x = 0 to 3)

| 1      |     |     |       |       |               |       |       |

|--------|-----|-----|-------|-------|---------------|-------|-------|

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0         | R/W-0 | R/W-0 |

| _      | _   | —   |       | TR    | RGSRC(4x+3)<4 | :0>   |       |

| bit 15 |     |     |       |       |               |       | bit 8 |

|        |     |     |       |       |               |       |       |

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0         | R/W-0 | R/W-0 |

| _      | —   | —   |       | TR    | GSRC(4x+2)<4  | :0>   |       |

| bit 7  |     |     |       |       |               |       | bit 0 |

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read a | as 'O'             |

|-------------------|------------------|-------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared          | x = Bit is unknown |

#### bit 15-13 Unimplemented: Read as '0'

| bit 12-8 | TRGSRC(4x+3)<4:0>: Trigger Source Selection for Corresponding Analog Inputs bits |

|----------|----------------------------------------------------------------------------------|

|----------|----------------------------------------------------------------------------------|

| 12-0 | TRUSRC(4x+3)<4.0>. Thyyer Source Selection to |

|------|-----------------------------------------------|

|      | 11111 = ADTRG31                               |

|      | 11110 = Reserved                              |

|      | 11101 = Reserved                              |

|      | 11100 = Reserved                              |

|      | 11011 = Reserved                              |

|      | 11010 = PWM Generator 3 current-limit trigger |

|      | 11001 = PWM Generator 2 current-limit trigger |

|      | 11000 = PWM Generator 1 current-limit trigger |

|      | 10111 = Reserved                              |

|      | 10110 = Output Compare 1 trigger              |

|      | 10101 = Reserved                              |

|      | 10100 = Reserved                              |

|      | 10011 = Reserved                              |

|      | 10010 = Reserved                              |

|      | 10001 = PWM Generator 3 secondary trigger     |

|      | 10000 = PWM Generator 2 secondary trigger     |

|      | 01111 = PWM Generator 1 secondary trigger     |

|      | 01110 = PWM secondary Special Event Trigger   |

|      | 01101 = Timer2 period match                   |

|      | 01100 = Timer1 period match                   |

|      | 01011 = Reserved                              |

|      | 01010 = Reserved                              |

|      | 01001 = Reserved                              |

|      | 01000 = Reserved                              |

|      | 00111 = PWM Generator 3 primary trigger       |

|      | 00110 = PWM Generator 2 primary trigger       |

|      | 00101 = PWM Generator 1 primary trigger       |

|      | 00100 = PWM Special Event Trigger             |

|      | 00011 = Reserved                              |

|      | 00010 = Level software trigger                |

|      | 00001 = Common software trigger               |

|      | 00000 = No trigger is enabled                 |

| 7-5  | Unimplemented: Read as '0'                    |

# TABLE 25-35:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                 | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |                        |       |                                |

|--------------------|-----------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------|-------|--------------------------------|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                   | Min.                                                                                                                                                                                                                                                                                  | Тур. <sup>(2)</sup> | Max.                   | Units | Conditions                     |

| SP70               | FscP                  | Maximum SCK1 Input<br>Frequency                 | _                                                                                                                                                                                                                                                                                     | _                   | Lesser of:<br>FP or 15 | MHz   | (Note 3)                       |