Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (32K × 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 12x12b; D/A 2x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C                                                                   |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gs202-e-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0   | Device Overview                                                       | 7   |

|-------|-----------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-Bit Digital Signal Controllers | 11  |

| 3.0   | CPU                                                                   | 17  |

| 4.0   | Memory Organization                                                   |     |

| 5.0   | Flash Program Memory                                                  |     |

| 6.0   | Resets                                                                |     |

| 7.0   | Interrupt Controller                                                  |     |

| 8.0   | Oscillator Configuration                                              |     |

| 9.0   | Power-Saving Features                                                 |     |

| 10.0  | I/O Ports                                                             | 107 |

| 11.0  | Timer1                                                                | 133 |

| 12.0  | Timer2/3                                                              | 137 |

| 13.0  | Input Capture                                                         | 141 |

| 14.0  | Output Compare                                                        |     |

| 15.0  | High-Speed PWM                                                        | 151 |

| 16.0  | Serial Peripheral Interface (SPI)                                     |     |

| 17.0  | Inter-Integrated Circuit (I <sup>2</sup> C)                           |     |

| 18.0  | Universal Asynchronous Receiver Transmitter (UART)                    |     |

| 19.0  | High-Speed, 12-Bit Analog-to-Digital Converter (ADC)                  |     |

| 20.0  | High-Speed Analog Comparator                                          |     |

| 21.0  | Programmable Gain Amplifier (PGA)                                     |     |

| 22.0  | Special Features                                                      | 239 |

| 23.0  | Instruction Set Summary                                               |     |

| 24.0  | Development Support                                                   |     |

| 25.0  | Electrical Characteristics                                            |     |

| 26.0  | DC and AC Device Characteristics Graphs                               |     |

|       | Packaging Information                                                 |     |

| Appe  | ndix A: Revision History                                              | 331 |

| Index | ۲                                                                     |     |

| The N | Vicrochip Web Site                                                    |     |

| Custo | omer Change Notification Service                                      |     |

|       | omer Support                                                          |     |

| Produ | uct Identification System                                             |     |

## 3.7 CPU Control Registers

## REGISTER 3-1: SR: CPU STATUS REGISTER

| R/W-0                | R/W-0                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                              | R/W-0                             | R/C-0            | R/C-0            | R-0             | R/W-0 |  |  |  |  |  |  |  |  |

|----------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------|------------------|-----------------|-------|--|--|--|--|--|--|--|--|

| OA                   | OB                                                             | SA <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                  | SB <sup>(3)</sup>                 | OAB              | SAB              | DA              | DC    |  |  |  |  |  |  |  |  |

| bit 15               |                                                                |                                                                                                                                                                                                                                                                                                                                                    |                                   |                  |                  |                 | bit 8 |  |  |  |  |  |  |  |  |

|                      |                                                                |                                                                                                                                                                                                                                                                                                                                                    |                                   |                  |                  |                 |       |  |  |  |  |  |  |  |  |

| R/W-0 <sup>(2)</sup> | R/W-0 <sup>(2)</sup>                                           | R/W-0 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                               | R-0                               | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |  |  |  |  |

| IPL2 <sup>(1)</sup>  | IPL1 <sup>(1)</sup>                                            | IPL0 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                | RA                                | Ν                | OV               | Z               | С     |  |  |  |  |  |  |  |  |

| bit 7                |                                                                |                                                                                                                                                                                                                                                                                                                                                    |                                   |                  |                  |                 | bit ( |  |  |  |  |  |  |  |  |

| Legend:              |                                                                | C = Clearable                                                                                                                                                                                                                                                                                                                                      | e bit                             |                  |                  |                 |       |  |  |  |  |  |  |  |  |

| R = Readable         | e bit                                                          | W = Writable                                                                                                                                                                                                                                                                                                                                       | bit                               | U = Unimpler     | mented bit, read | d as '0'        |       |  |  |  |  |  |  |  |  |

| -n = Value at        | POR                                                            | '1'= Bit is set                                                                                                                                                                                                                                                                                                                                    |                                   | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |  |  |  |  |  |  |

| bit 14<br>bit 13     | 1 = Accumul<br>0 = Accumul<br><b>SA:</b> Accumu<br>1 = Accumul | <ul> <li>0 = Accumulator A has not overflowed</li> <li>OB: Accumulator B Overflow Status bit</li> <li>1 = Accumulator B has overflowed</li> <li>0 = Accumulator B has not overflowed</li> <li>SA: Accumulator A Saturation 'Sticky' Status bit<sup>(3)</sup></li> <li>1 = Accumulator A is saturated or has been saturated at some time</li> </ul> |                                   |                  |                  |                 |       |  |  |  |  |  |  |  |  |

| bit 12               | SB: Accumu<br>1 = Accumul                                      | ator A is not sa<br>lator B Saturati<br>ator B is satura<br>ator B is not sa                                                                                                                                                                                                                                                                       | on 'Sticky' Sta<br>ted or has bee |                  | some time        |                 |       |  |  |  |  |  |  |  |  |

| bit 11               | 1 = Accumul                                                    | DB Combined A<br>ators A or B ha<br>Accumulators A                                                                                                                                                                                                                                                                                                 | ve overflowed                     |                  | bit              |                 |       |  |  |  |  |  |  |  |  |

| bit 10               | 1 = Accumul                                                    | B Combined A<br>ators A or B are<br>Accumulator A c                                                                                                                                                                                                                                                                                                | e saturated, or                   | have been sat    |                  | time            |       |  |  |  |  |  |  |  |  |

| bit 9                | <b>DA:</b> DO Loop<br>1 = DO loop i<br>0 = DO loop r           |                                                                                                                                                                                                                                                                                                                                                    |                                   |                  |                  |                 |       |  |  |  |  |  |  |  |  |

| bit 8                | -                                                              | U Half Carry/B                                                                                                                                                                                                                                                                                                                                     | orrow bit                         |                  |                  |                 |       |  |  |  |  |  |  |  |  |

|                      |                                                                |                                                                                                                                                                                                                                                                                                                                                    |                                   |                  |                  |                 |       |  |  |  |  |  |  |  |  |

1 = A carry-out from the 4th low-order bit (for byte-sized data) or 8th low-order bit (for word-sized data) of the result occurred

- 0 = No carry-out from the 4th low-order bit (for byte-sized data) or 8th low-order bit (for word-sized data) of the result occurred

- **Note 1:** The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 2: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **3:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

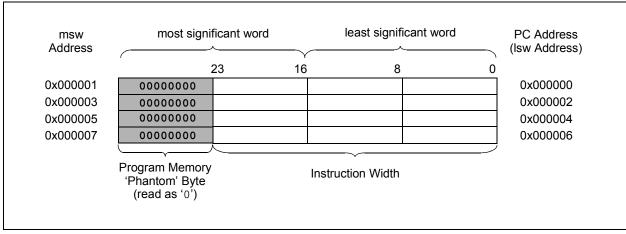

### 4.2.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-3).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented, or decremented, by two during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

# 4.2.2 INTERRUPT AND TRAP VECTORS

All dsPIC33EPXXGS202 family devices reserve the addresses between 0x000000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address, 0x000000, of Flash memory, with the actual address for the start of code at address, 0x000002, of Flash memory.

A more detailed discussion of the Interrupt Vector Tables (IVTs) is provided in **Section 7.1** "Interrupt Vector Table".

#### FIGURE 4-3: PROGRAM MEMORY ORGANIZATION

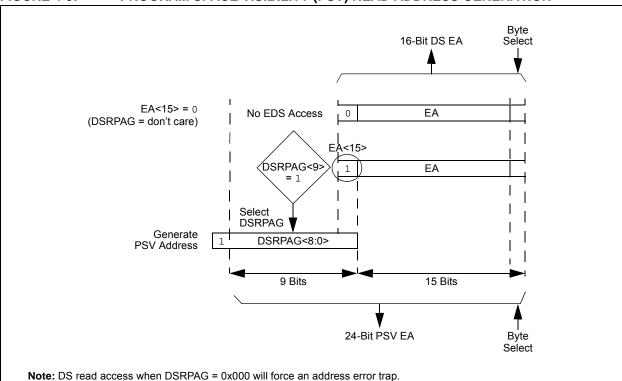

### 4.5.1 PAGED MEMORY SCHEME

The dsPIC33EPXXGS202 architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre- and post-modified Effective Addresses (EAs). The upper half of the base Data Space address is used in conjunction with the Data Space Read Page (DSRPAG) register to form the Program Space Visibility (PSV) address.

The Data Space Read Page (DSRPAG) register is located in the SFR space. Construction of the PSV address is shown in Figure 4-5. When DSRPAG<9> = 1 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit PSV read address. The paged memory scheme provides access to multiple 32-Kbyte windows in the PSV memory. The Data Space Read Page register (DSRPAG), in combination with the upper half of the Data Space address, can provide up to 8 Mbytes of PSV address space. The paged data memory space is shown in Figure 4-6.

The Program Space (PS) can be accessed with a DSRPAG of 0x200 or greater. Only reads from PS are supported using the DSRPAG.

#### FIGURE 4-5: PROGRAM SPACE VISIBILITY (PSV) READ ADDRESS GENERATION

| R/W-0      | ) R/W-0              | U-0                                                                                                                                             | U-0             | R/W-0                 | U-0               | R/W-0            | R/W-0         |  |  |  |  |

|------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|-------------------|------------------|---------------|--|--|--|--|

| TRAP       | R IOPUWR             | —                                                                                                                                               | _               | VREGSF                |                   | CM               | VREGS         |  |  |  |  |

| bit 15     |                      |                                                                                                                                                 |                 |                       |                   |                  | bit 8         |  |  |  |  |

|            |                      |                                                                                                                                                 |                 |                       |                   |                  |               |  |  |  |  |

| R/W-0      | R/W-0                | R/W-0                                                                                                                                           | R/W-0           | R/W-0                 | R/W-0             | R/W-1            | R/W-1         |  |  |  |  |

| EXTR       | SWR                  | SWDTEN <sup>(2)</sup>                                                                                                                           | WDTO            | SLEEP                 | IDLE              | BOR              | POR           |  |  |  |  |

| bit 7      |                      |                                                                                                                                                 |                 |                       |                   |                  | bit (         |  |  |  |  |

| Legend:    |                      |                                                                                                                                                 |                 |                       |                   |                  |               |  |  |  |  |

| R = Read   | able bit             | W = Writable                                                                                                                                    | bit             | U = Unimpler          | mented bit, read  | d as '0'         |               |  |  |  |  |

| -n = Value | e at POR             | '1' = Bit is set                                                                                                                                |                 | '0' = Bit is cle      |                   | x = Bit is unki  | nown          |  |  |  |  |

|            |                      |                                                                                                                                                 |                 |                       |                   |                  |               |  |  |  |  |

| bit 15     | TRAPR: Trap          | Reset Flag bit                                                                                                                                  |                 |                       |                   |                  |               |  |  |  |  |

|            |                      | onflict Reset ha                                                                                                                                |                 |                       |                   |                  |               |  |  |  |  |

|            | •                    | onflict Reset ha                                                                                                                                |                 |                       |                   |                  |               |  |  |  |  |

| bit 14     |                      |                                                                                                                                                 |                 | -                     | cess Reset Flag   |                  | r used as ar  |  |  |  |  |

|            | •                    | 1 = An illegal opcode detection, an illegal address mode or Uninitialized W register used as ar<br>Address Pointer caused a Reset               |                 |                       |                   |                  |               |  |  |  |  |

|            | 0 = An illega        | I opcode or Uni                                                                                                                                 | nitialized W r  | register Reset h      | as not occurred   | t                |               |  |  |  |  |

| bit 13-12  | Unimplemen           | ted: Read as '                                                                                                                                  | כ'              |                       |                   |                  |               |  |  |  |  |

| bit 11     | VREGSF: Fla          | VREGSF: Flash Voltage Regulator Standby During Sleep bit                                                                                        |                 |                       |                   |                  |               |  |  |  |  |

|            |                      | <ul> <li>1 = Flash voltage regulator is active during Sleep</li> <li>0 = Flash voltage regulator goes into Standby mode during Sleep</li> </ul> |                 |                       |                   |                  |               |  |  |  |  |

|            |                      |                                                                                                                                                 | -               | ndby mode dur         | ing Sleep         |                  |               |  |  |  |  |

| bit 10     | -                    | ted: Read as '                                                                                                                                  |                 |                       |                   |                  |               |  |  |  |  |

| bit 9      | •                    | <b>CM:</b> Configuration Mismatch Flag bit<br>1 = A Configuration Mismatch Reset has occurred.                                                  |                 |                       |                   |                  |               |  |  |  |  |

|            |                      |                                                                                                                                                 |                 |                       |                   |                  |               |  |  |  |  |

| bit 8      | •                    | <ul> <li>0 = A Configuration Mismatch Reset has not occurred</li> <li>VREGS: Voltage Regulator Standby During Sleep bit</li> </ul>              |                 |                       |                   |                  |               |  |  |  |  |

|            |                      | 1 = Voltage regulator is active during Sleep                                                                                                    |                 |                       |                   |                  |               |  |  |  |  |

|            | 0 = Voltage r        | egulator goes i                                                                                                                                 | nto Standby i   | mode during SI        | еер               |                  |               |  |  |  |  |

| bit 7      | EXTR: Extern         | EXTR: External Reset (MCLR) Pin bit                                                                                                             |                 |                       |                   |                  |               |  |  |  |  |

|            |                      | Clear (pin) Res                                                                                                                                 |                 |                       |                   |                  |               |  |  |  |  |

| h:1 0      |                      | Clear (pin) Res                                                                                                                                 |                 |                       |                   |                  |               |  |  |  |  |

| bit 6      |                      | SWR: Software RESET (Instruction) Flag bit<br>1 = A RESET instruction has been executed                                                         |                 |                       |                   |                  |               |  |  |  |  |

|            |                      | instruction has                                                                                                                                 |                 |                       |                   |                  |               |  |  |  |  |

| bit 5      | SWDTEN: So           | oftware Enable/                                                                                                                                 | Disable of W    | DT bit <sup>(2)</sup> |                   |                  |               |  |  |  |  |

|            | 1 = WDT is e         | nabled                                                                                                                                          |                 |                       |                   |                  |               |  |  |  |  |

|            | 0 = WDT is d         | isabled                                                                                                                                         |                 |                       |                   |                  |               |  |  |  |  |

| bit 4      |                      | hdog Timer Tin                                                                                                                                  | -               | it                    |                   |                  |               |  |  |  |  |

|            |                      | e-out has occur<br>e-out has not o                                                                                                              |                 |                       |                   |                  |               |  |  |  |  |

| Note 1:    | All of the Reset sta | atus bits can be                                                                                                                                | set or cleare   | d in software. S      | Setting one of th | ese bits in soft | ware does not |  |  |  |  |

|            | cause a device Re    |                                                                                                                                                 |                 |                       |                   |                  |               |  |  |  |  |

| 2:         | If the WDTEN<1:0     | > Configuratior                                                                                                                                 | n bits are '11' | (unprogramme          | ed), the WDT is   | always enable    | d, regardless |  |  |  |  |

### REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

If the WDTEN<1:0> Configuration bits are '11' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

# **REGISTER 6-1:** RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

| bit 3 | <b>SLEEP:</b> Wake-up from Sleep Flag bit<br>1 = Device has been in Sleep mode<br>0 = Device has not been in Sleep mode |

|-------|-------------------------------------------------------------------------------------------------------------------------|

| bit 2 | IDLE: Wake-up from Idle Flag bit                                                                                        |

|       | <ol> <li>1 = Device has been in Idle mode</li> <li>0 = Device has not been in Idle mode</li> </ol>                      |

| bit 1 | BOR: Brown-out Reset Flag bit                                                                                           |

|       | <ul><li>1 = A Brown-out Reset has occurred</li><li>0 = A Brown-out Reset has not occurred</li></ul>                     |

| bit 0 | POR: Power-on Reset Flag bit                                                                                            |

|       | <ul><li>1 = A Power-on Reset has occurred</li><li>0 = A Power-on Reset has not occurred</li></ul>                       |

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the WDTEN<1:0> Configuration bits are '11' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| R/W-0           | R/W-0                                                                                                                                   | R/W-0                                                                                                              | R/W-0                                                                                                                               | R/W-0                                                       | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------|-----------------|-------|--|--|--|--|

| NSTDIS          | OVAERR                                                                                                                                  | OVBERR                                                                                                             | COVAERR                                                                                                                             | COVBERR                                                     | OVATE           | OVBTE           | COVTE |  |  |  |  |

| bit 15          |                                                                                                                                         |                                                                                                                    |                                                                                                                                     |                                                             |                 |                 | bit 8 |  |  |  |  |

|                 |                                                                                                                                         |                                                                                                                    |                                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |

| R/W-0           | R/W-0                                                                                                                                   | U-0                                                                                                                | R/W-0                                                                                                                               | R/W-0                                                       | R/W-0           | R/W-0           | U-0   |  |  |  |  |

| SFTACERR        | DIV0ERR                                                                                                                                 |                                                                                                                    | MATHERR                                                                                                                             | ADDRERR                                                     | STKERR          | OSCFAIL         | _     |  |  |  |  |

| bit 7           |                                                                                                                                         |                                                                                                                    |                                                                                                                                     |                                                             |                 |                 | bit   |  |  |  |  |

| Legend:         |                                                                                                                                         |                                                                                                                    |                                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |

| R = Readable    | bit                                                                                                                                     | W = Writable                                                                                                       | bit                                                                                                                                 | U = Unimpleme                                               | ented bit, read | as '0'          |       |  |  |  |  |

| -n = Value at F | POR                                                                                                                                     | '1' = Bit is set                                                                                                   |                                                                                                                                     | '0' = Bit is clear                                          | -               | x = Bit is unkr | nown  |  |  |  |  |

|                 |                                                                                                                                         |                                                                                                                    |                                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |

| bit 15          | NSTDIS: Inte                                                                                                                            | errupt Nesting                                                                                                     | Disable bit                                                                                                                         |                                                             |                 |                 |       |  |  |  |  |

|                 | 1 = Interrupt                                                                                                                           | nesting is disa                                                                                                    | abled                                                                                                                               |                                                             |                 |                 |       |  |  |  |  |

|                 | 0 = Interrupt                                                                                                                           | nesting is ena                                                                                                     | bled                                                                                                                                |                                                             |                 |                 |       |  |  |  |  |

| bit 14          |                                                                                                                                         |                                                                                                                    | Overflow Trap F                                                                                                                     | -                                                           |                 |                 |       |  |  |  |  |

|                 |                                                                                                                                         |                                                                                                                    | erflow of Accur                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |

|                 | 0 = Trap was not caused by overflow of Accumulator A                                                                                    |                                                                                                                    |                                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |

| bit 13          | OVBERR: Accumulator B Overflow Trap Flag bit                                                                                            |                                                                                                                    |                                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |

|                 | <ul> <li>1 = Trap was caused by overflow of Accumulator B</li> <li>0 = Trap was not caused by overflow of Accumulator B</li> </ul>      |                                                                                                                    |                                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |

| bit 12          |                                                                                                                                         |                                                                                                                    |                                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |

|                 | <b>COVAERR:</b> Accumulator A Catastrophic Overflow Trap Flag bit<br>1 = Trap was caused by catastrophic overflow of Accumulator A      |                                                                                                                    |                                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |

|                 | <ul> <li>0 = Trap was not caused by catastrophic overflow of Accumulator A</li> </ul>                                                   |                                                                                                                    |                                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |

| bit 11          | <b>COVBERR:</b> Accumulator B Catastrophic Overflow Trap Flag bit                                                                       |                                                                                                                    |                                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |

|                 | 1 = Trap was caused by catastrophic overflow of Accumulator B                                                                           |                                                                                                                    |                                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |

|                 | 0 = Trap was                                                                                                                            | = Trap was not caused by catastrophic overflow of Accumulator B                                                    |                                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |

| bit 10          | OVATE: Acc                                                                                                                              | umulator A Ov                                                                                                      | erflow Trap Ena                                                                                                                     | able bit                                                    |                 |                 |       |  |  |  |  |

|                 | 1 = Trap overflow of Accumulator A                                                                                                      |                                                                                                                    |                                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |

|                 | 0 = Trap is disabled                                                                                                                    |                                                                                                                    |                                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |

| bit 9           |                                                                                                                                         |                                                                                                                    | erflow Trap En                                                                                                                      | able bit                                                    |                 |                 |       |  |  |  |  |

|                 | 1 = Trap overflow of Accumulator B                                                                                                      |                                                                                                                    |                                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |

| bit 8           | •                                                                                                                                       | 0 = Trap is disabled                                                                                               |                                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |

| DILO            |                                                                                                                                         | -                                                                                                                  | -                                                                                                                                   | <b>COVTE:</b> Catastrophic Overflow Trap Enable bit         |                 |                 |       |  |  |  |  |

|                 | <ol> <li>Trap on catastrophic overflow of Accumulator A or B is enabled</li> <li>Trap is disabled</li> </ol>                            |                                                                                                                    |                                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |

|                 |                                                                                                                                         |                                                                                                                    |                                                                                                                                     | nulator A or B is                                           | enabled         |                 |       |  |  |  |  |

| bit 7           | 0 = Trap is d                                                                                                                           | lisabled                                                                                                           |                                                                                                                                     |                                                             | enabled         |                 |       |  |  |  |  |

| bit 7           | 0 = Trap is d                                                                                                                           | lisabled<br>: Shift Accumu                                                                                         | lator Error Statu                                                                                                                   |                                                             |                 |                 |       |  |  |  |  |

| bit 7           | 0 = Trap is d<br>SFTACERR:<br>1 = Math err                                                                                              | lisabled<br>: Shift Accumu<br>or trap was ca                                                                       | lator Error Statu<br>used by an inva                                                                                                | ıs bit                                                      | shift           |                 |       |  |  |  |  |

| bit 7<br>bit 6  | 0 = Trap is d<br>SFTACERR:<br>1 = Math err<br>0 = Math err                                                                              | lisabled<br>Shift Accumu<br>or trap was ca<br>or trap was no                                                       | lator Error Statu<br>used by an inva                                                                                                | us bit<br>Ilid accumulator                                  | shift           |                 |       |  |  |  |  |

|                 | 0 = Trap is d<br>SFTACERR:<br>1 = Math erro<br>0 = Math erro<br>DIV0ERR: D<br>1 = Math erro                                             | lisabled<br>: Shift Accumu<br>or trap was ca<br>or trap was no<br>)ivide-by-Zero<br>or trap was ca                 | lator Error Statu<br>used by an inva<br>t caused by an<br>Error Status bit<br>used by a divide                                      | us bit<br>Ilid accumulator<br>invalid accumula<br>e-by-zero | shift           |                 |       |  |  |  |  |

|                 | 0 = Trap is d<br>SFTACERR:<br>1 = Math err<br>0 = Math err<br>DIV0ERR: D<br>1 = Math err<br>0 = Math err                                | lisabled<br>Shift Accumu<br>or trap was ca<br>or trap was no<br>Divide-by-Zero<br>or trap was ca<br>or trap was no | lator Error Statu<br>used by an inva<br>t caused by an<br>Error Status bit<br>used by a divide<br>t caused by a d                   | us bit<br>Ilid accumulator<br>invalid accumula<br>e-by-zero | shift           |                 |       |  |  |  |  |

|                 | 0 = Trap is d<br>SFTACERR:<br>1 = Math err<br>0 = Math err<br>DIV0ERR: D<br>1 = Math err<br>0 = Math err                                | lisabled<br>: Shift Accumu<br>or trap was ca<br>or trap was no<br>)ivide-by-Zero<br>or trap was ca                 | lator Error Statu<br>used by an inva<br>t caused by an<br>Error Status bit<br>used by a divide<br>t caused by a d                   | us bit<br>Ilid accumulator<br>invalid accumula<br>e-by-zero | shift           |                 |       |  |  |  |  |

| bit 6           | 0 = Trap is d<br>SFTACERR:<br>1 = Math erro<br>0 = Math erro<br>DIV0ERR: D<br>1 = Math erro<br>0 = Math erro<br>Unimplement<br>MATHERR: | lisabled<br>Shift Accumu<br>or trap was ca<br>or trap was no<br>Divide-by-Zero<br>or trap was ca<br>or trap was no | lator Error Statu<br>used by an inva<br>t caused by an<br>Error Status bit<br>used by a divide<br>t caused by a d<br>'0'<br>tus bit | us bit<br>Ilid accumulator<br>invalid accumula<br>e-by-zero | shift           |                 |       |  |  |  |  |

# REGISTER 10-13: RPINR38: PERIPHERAL PIN SELECT INPUT REGISTER 38

| U-0           | U-0        | U-0                     | U-0          | U-0                                | U-0           | U-0                | U-0   |

|---------------|------------|-------------------------|--------------|------------------------------------|---------------|--------------------|-------|

| _             | —          | —                       | —            | —                                  | —             | —                  | —     |

| bit 15        |            |                         |              |                                    |               |                    | bit 8 |

|               |            |                         |              |                                    |               |                    |       |

| R/W-0         | R/W-0      | R/W-0                   | R/W-0        | R/W-0                              | R/W-0         | R/W-0              | R/W-0 |

|               |            |                         | SYNCI        | 2R<7:0>                            |               |                    |       |

| bit 7         |            |                         |              |                                    |               |                    | bit 0 |

|               |            |                         |              |                                    |               |                    |       |

| Legend:       |            |                         |              |                                    |               |                    |       |

| R = Readabl   | e bit      | W = Writable bit        |              | U = Unimplemented bit, read as '0' |               |                    |       |

| -n = Value at | POR        | '1' = Bit is set        |              | '0' = Bit is cleared               |               | x = Bit is unknown |       |

|               |            |                         |              |                                    |               |                    |       |

| bit 15-8      | Unimplemen | ted: Read as '          | כ'           |                                    |               |                    |       |

| bit 7-0       | SYNCI2R<7: | <b>0&gt;:</b> Assign PW | M Synchroniz | ation Input 2 to                   | the Correspon | ding RPn Pin b     | oits  |

|               | 10110101 = | Input tied to RF        | P181         |                                    |               |                    |       |

|               | 10110100 = | Input tied to RF        | P180         |                                    |               |                    |       |

|               | •          |                         |              |                                    |               |                    |       |

|               | •          |                         |              |                                    |               |                    |       |

|               | •          |                         |              |                                    |               |                    |       |

|               | 0000001=   | Input tied to RF        | P1           |                                    |               |                    |       |

|               | 00000000 = | Input tied to Vs        | S            |                                    |               |                    |       |

|               |            |                         |              |                                    |               |                    |       |

NOTES:

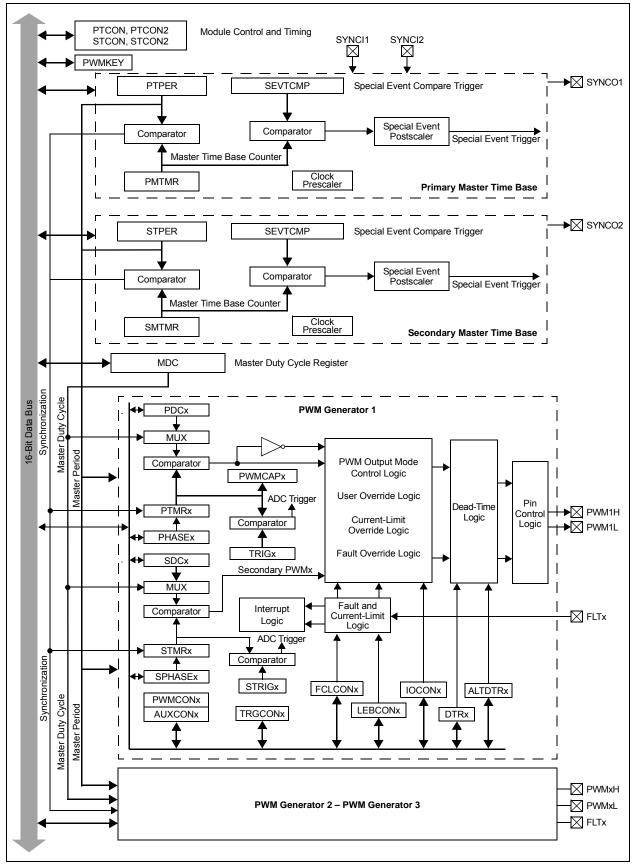

#### FIGURE 15-2: SIMPLIFIED CONCEPTUAL BLOCK DIAGRAM OF THE HIGH-SPEED PWM

#### R/W-0 R/W-0 R/W-0 U-0 U-0 U-0 R/W-0 U-0 TRGDIV3 TRGDIV2 TRGDIV1 **TRGDIV0** bit 15 bit 8 R/W-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 DTM<sup>(1)</sup> TRGSTRT5 TRGSTRT4 TRGSTRT3 TRGSTRT2 TRGSTRT1 **TRGSTRT0** bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '0' = Bit is cleared '1' = Bit is set x = Bit is unknown bit 15-12 TRGDIV<3:0>: Trigger # Output Divider bits 1111 = Trigger output for every 16th trigger event 1110 = Trigger output for every 15th trigger event 1101 = Trigger output for every 14th trigger event 1100 = Trigger output for every 13th trigger event 1011 = Trigger output for every 12th trigger event 1010 = Trigger output for every 11th trigger event 1001 = Trigger output for every 10th trigger event 1000 = Trigger output for every 9th trigger event 0111 = Trigger output for every 8th trigger event 0110 = Trigger output for every 7th trigger event 0101 = Trigger output for every 6th trigger event 0100 = Trigger output for every 5th trigger event 0011 = Trigger output for every 4th trigger event 0010 = Trigger output for every 3rd trigger event 0001 = Trigger output for every 2nd trigger event 0000 = Trigger output for every trigger event Unimplemented: Read as '0' bit 11-8 bit 7 DTM: Dual Trigger Mode bit<sup>(1)</sup> 1 = Secondary trigger event is combined with the primary trigger event to create a PWM trigger 0 = Secondary trigger event is not combined with the primary trigger event to create a PWM trigger; two separate PWM triggers are generated bit 6 Unimplemented: Read as '0' bit 5-0 TRGSTRT<5:0>: Trigger Postscaler Start Enable Select bits 111111 = Wait 63 PWM cycles before generating the first trigger event after the module is enabled 000010 = Wait 2 PWM cycles before generating the first trigger event after the module is enabled 000001 = Wait 1 PWM cycle before generating the first trigger event after the module is enabled 000000 = Wait 0 PWM cycles before generating the first trigger event after the module is enabled

# REGISTER 15-19: TRGCONx: PWMx TRIGGER CONTROL REGISTER

### REGISTER 15-22: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER (CONTINUED)

bit 7-3 **FLTSRC<4:0>:** Fault Control Signal Source Select for PWMx Generator # bits

|         | 11111 = Reserved<br>10001 = Reserved<br>10000 = Reserved<br>01111 = Reserved<br>01110 = Analog Comparator 2<br>01101 = Analog Comparator 1<br>01100 = Reserved                                     |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 01011 = Reserved                                                                                                                                                                                   |

|         | 01010 = Reserved                                                                                                                                                                                   |

|         | 01001 = Reserved                                                                                                                                                                                   |

|         | 01000 = Fault 8<br>00111 = Fault 7                                                                                                                                                                 |

|         | 00110 = Fault 6                                                                                                                                                                                    |

|         | 00101 = Fault 5                                                                                                                                                                                    |

|         | 00100 = Fault 4                                                                                                                                                                                    |

|         | 00011 <b>= Fault 3</b>                                                                                                                                                                             |

|         | 00010 = Fault 2                                                                                                                                                                                    |

|         | 00001 <b>= Fault 1</b>                                                                                                                                                                             |

|         | 00000 = Reserved                                                                                                                                                                                   |

| bit 2   | FLTPOL: Fault Polarity for PWMx Generator # bit <sup>(1)</sup>                                                                                                                                     |

|         | <ul><li>1 = The selected Fault source is active-low</li><li>0 = The selected Fault source is active-high</li></ul>                                                                                 |

| bit 1-0 | FLTMOD<1:0>: Fault Mode for PWMx Generator # bits                                                                                                                                                  |

|         | 11 = Fault input is disabled                                                                                                                                                                       |

|         | 10 = Reserved                                                                                                                                                                                      |

|         | 01 = The selected Fault source forces the PWMxH, PWMxL pins to the FLTDATx values (cycle)<br>00 = The selected Fault source forces the PWMxH, PWMxL pins to the FLTDATx values (latched condition) |

**Note 1:** These bits should be changed only when PTEN (PTCON<15>) = 0.

# REGISTER 15-23: STRIGX: PWMx SECONDARY TRIGGER COMPARE VALUE REGISTER<sup>(1)</sup>

| R/W-0        | R/W-0          | R/W-0                      | R/W-0          | R/W-0             | R/W-0              | R/W-0              | R/W-0        |

|--------------|----------------|----------------------------|----------------|-------------------|--------------------|--------------------|--------------|

|              |                |                            | STRGC          | VIP<12:5>         |                    |                    |              |

| bit 15       |                |                            |                |                   |                    |                    | bit 8        |

|              |                |                            |                |                   |                    |                    |              |

| R/W-0        | R/W-0          | R/W-0                      | R/W-0          | R/W-0             | U-0                | U-0                | U-0          |

|              |                | STRGCMP<4:0                | >              |                   | —                  | —                  | —            |

| bit 7        |                |                            |                |                   |                    |                    | bit 0        |

|              |                |                            |                |                   |                    |                    |              |

| Legend:      |                |                            |                |                   |                    |                    |              |

| R = Readab   | le bit         | W = Writable I             | oit            | U = Unimpler      | nented bit, read   | as '0'             |              |

| -n = Value a | It POR         | '1' = Bit is set           |                | '0' = Bit is cle  | ared               | x = Bit is unknown |              |

|              |                |                            |                |                   |                    |                    |              |

| bit 15-3     | STRGCMP<       | : <b>12:0&gt;:</b> Seconda | ry Trigger Cor | npare Value bits  | 6                  |                    |              |

|              |                | condary PWMx f             |                | e local time base | e, this register c | ontains the cor    | mpare values |

|              | that can trigg | ger the ADC mod            | lule.          |                   |                    |                    |              |

| bit 2-0      | Unimpleme      | nted: Read as '0           | ,              |                   |                    |                    |              |

|              |                |                            |                |                   |                    |                    |              |

**Note 1:** STRIGx cannot generate the PWMx trigger interrupts.

### REGISTER 18-1: U1MODE: UART1 MODE REGISTER (CONTINUED)

| bit 4   | URXINV: UART1 Receive Polarity Inversion bit<br>1 = U1RX Idle state is '0'<br>0 = U1RX Idle state is '1'                                                                           |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                    |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul> |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                         |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                      |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                                      |

|         | 1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                              |

- **Note 1:** Refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UART1 module for receive or transmit operation.

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

## REGISTER 19-8: ADCON4H: ADC CONTROL REGISTER 4 HIGH

| U-0        | U-0                                                     | U-0              | U-0              | U-0            | U-0                  | U-0    | U-0                |  |  |  |  |

|------------|---------------------------------------------------------|------------------|------------------|----------------|----------------------|--------|--------------------|--|--|--|--|

| —          |                                                         | —                | —                | _              | _                    | —      | —                  |  |  |  |  |

| bit 15     |                                                         |                  |                  |                |                      |        | bit 8              |  |  |  |  |

|            |                                                         |                  |                  |                |                      | =      |                    |  |  |  |  |

| U-0        | U-0                                                     | U-0              | U-0              | R/W-0          | R/W-0                | R/W-0  | R/W-0              |  |  |  |  |

|            | —                                                       | —                | —                | C1CHS1         | C1CHS0               | C0CHS1 | C0CHS0             |  |  |  |  |

| bit 7      |                                                         |                  |                  |                |                      |        | bit 0              |  |  |  |  |

|            |                                                         |                  |                  |                |                      |        |                    |  |  |  |  |

| Legend:    |                                                         |                  |                  |                |                      |        |                    |  |  |  |  |

| R = Reada  | able bit                                                | W = Writable     | bit              | U = Unimplen   | as '0'               |        |                    |  |  |  |  |

| -n = Value | at POR                                                  | '1' = Bit is set | '1' = Bit is set |                | '0' = Bit is cleared |        | x = Bit is unknown |  |  |  |  |

|            |                                                         |                  |                  |                |                      |        |                    |  |  |  |  |

| bit 15-4   | Unimpleme                                               | ented: Read as   | '0'              |                |                      |        |                    |  |  |  |  |

| bit 3-2    | C1CHS<1:0                                               | D>: Dedicated A  | DC Core 1 Inp    | ut Channel Sel | ection bits          |        |                    |  |  |  |  |

|            | 11 = PGA2                                               |                  |                  |                |                      |        |                    |  |  |  |  |

|            | 10 = PGA1                                               |                  |                  |                |                      |        |                    |  |  |  |  |

|            | 01 <b>= AN8</b>                                         |                  |                  |                |                      |        |                    |  |  |  |  |

|            | 00 <b>= AN1</b>                                         | 00 <b>= AN1</b>  |                  |                |                      |        |                    |  |  |  |  |

|            | AN8 is a ne                                             | gative input wh  | en DIFF1 (ADN    | /IOD0L<3>) = 1 |                      |        |                    |  |  |  |  |

| bit 1-0    | C0CHS<1:0                                               | D>: Dedicated A  | DC Core 0 Inp    | ut Channel Sel | ection bits          |        |                    |  |  |  |  |

|            | 11 = PGA2                                               |                  |                  |                |                      |        |                    |  |  |  |  |

|            | 10 = PGA1                                               |                  |                  |                |                      |        |                    |  |  |  |  |

|            | 01 <b>= AN7</b>                                         |                  |                  |                |                      |        |                    |  |  |  |  |

|            | 00 <b>= AN0</b>                                         |                  |                  |                |                      |        |                    |  |  |  |  |

|            | ANZ is a negative input when DIEEO (ADMODOL $<1>$ ) = 1 |                  |                  |                |                      |        |                    |  |  |  |  |

AN7 is a negative input when DIFF0 (ADMOD0L<1>) = 1.

#### REGISTER 19-16: ADMODOL: ADC INPUT MODE CONTROL REGISTER 0 LOW

| -n = Value at | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|---------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

| R = Readable  | e bit | W = Writable     | bit   | U = Unimplem      | ented bit, read | l as '0'        |       |

| Legend:       |       |                  |       |                   |                 |                 |       |

|               |       |                  |       |                   |                 |                 |       |

| bit 7         |       |                  |       | 1                 |                 | •               | bit   |

|               | SIGN3 |                  | SIGN2 | DIFF1             | SIGN1           | DIFF0           | SIGN0 |

| U-0           | R/W-0 | U-0              | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|               |       |                  |       |                   |                 |                 |       |

| bit 15        |       |                  |       |                   |                 |                 | bit   |

| —             | SIGN7 | _                | SIGN6 | —                 | SIGN5           | —               | SIGN4 |

| U-0           | R/W-0 | U-0              | R/W-0 | U-0               | R/W-0           | U-0             | R/W-0 |

bit (odd)15-5 Unimplemented: Read as '0'

bit (3,1) **DIFF<x>:** Pseudo-Differential Mode for Corresponding Analog Inputs bits 1 = Channel is pseudo-differential 0 = Channel is single-ended

bit (even) **SIGNx:** Output Data Sign for Corresponding Analog Inputs bits

1 = Channel output data is signed

0 = Channel output data is unsigned

### REGISTER 19-17: ADMOD0H: ADC INPUT MODE CONTROL REGISTER 0 HIGH

| U-0     | U-0    | U-0 | R/W-0  | U-0 | R/W-0  | U-0 | R/W-0  |

|---------|--------|-----|--------|-----|--------|-----|--------|

| _       | —      | —   | SIGN14 | —   | SIGN13 | —   | SIGN12 |