Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 2K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gs202t-e-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Pin Diagrams**

| in SSC                                                                                                                                    | ic,<br>DP                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                    | Pins are up to 5V tolerant                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                           | MCLR 1<br>RA0 2<br>RA1 3<br>RA2 4<br>RB0 5<br>RB9 6<br>RB10 7<br>Vss 8<br>RB1 9<br>RB2 10<br>RB2 10<br>RB3 11<br>RB4 12<br>VDD 13<br>RD2 11                                                                                                                                                                                                          | dsPIC33EPXXGS202                                                                                                                                   | 28       AVDD         27       AVSS         26       RA3         25       RA4         24       RB14         23       RB13         22       RB12         21       RB11         20       VCAP         19       VSS         18       RB7         17       RB6         16       RB5                                     |

| PIN FI                                                                                                                                    | RB8                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                    | 15 RB15                                                                                                                                                                                                                                                                                                             |

| PIN FU<br>Pin                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                      | Pin                                                                                                                                                | 15 RB15                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                           | JNCTION DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                    | <b>F</b>                                                                                                                                                                                                                                                                                                            |

| Pin                                                                                                                                       | JNCTION DESCRIPTIONS Pin Function                                                                                                                                                                                                                                                                                                                    | Pin                                                                                                                                                | Pin Function                                                                                                                                                                                                                                                                                                        |

| Pin<br>1                                                                                                                                  | JNCTION DESCRIPTIONS Pin Function MCLR                                                                                                                                                                                                                                                                                                               | <b>Pin</b><br>15                                                                                                                                   | Pin Function PGEC3/ <b>RP47</b> /RB15                                                                                                                                                                                                                                                                               |

| <b>Pin</b> 1 2                                                                                                                            | JNCTION DESCRIPTIONS Pin Function MCLR AN0/PGA1P1/CMP1A/RA0                                                                                                                                                                                                                                                                                          | Pin<br>15<br>16                                                                                                                                    | Pin Function           PGEC3/RP47/RB15           TDO/AN9/PGA2N2/RP37/RB5                                                                                                                                                                                                                                            |

| Pin<br>1<br>2<br>3                                                                                                                        | JNCTION DESCRIPTIONS Pin Function MCLR AN0/PGA1P1/CMP1A/RA0 AN1/PGA1P2/PGA2P1/CMP1B/RA1                                                                                                                                                                                                                                                              | Pin<br>15<br>16<br>17                                                                                                                              | Pin Function           PGEC3/RP47/RB15           TDO/AN9/PGA2N2/RP37/RB5           PGED1/TDI/AN10/SCL1/RP38/RB6                                                                                                                                                                                                     |

| Pin 1 2 3 4                                                                                                                               | JNCTION DESCRIPTIONS<br>Pin Function<br>MCLR<br>AN0/PGA1P1/CMP1A/RA0<br>AN1/PGA1P2/PGA2P1/CMP1B/RA1<br>AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2                                                                                                                                                                                                             | Pin           15           16           17           18                                                                                            | Pin Function           PGEC3/RP47/RB15           TDO/AN9/PGA2N2/RP37/RB5           PGED1/TDI/AN10/SCL1/RP38/RB6           PGEC1/AN11/SDA1/RP39/RB7                                                                                                                                                                  |

| Pin 1 2 3 4 5                                                                                                                             | Pin Function         MCLR         AN0/PGA1P1/CMP1A/RA0         AN1/PGA1P2/PGA2P1/CMP1B/RA1         AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2         AN3/PGA2P3/CMP1D/CMP2B/RP32/RB0                                                                                                                                                                         | Pin           15           16           17           18           19                                                                               | Pin Function           PGEC3/RP47/RB15           TDO/AN9/PGA2N2/RP37/RB5           PGED1/TDI/AN10/SCL1/RP38/RB6           PGEC1/AN11/SDA1/RP39/RB7           Vss                                                                                                                                                    |

| Pin           1           2           3           4           5           6                                                               | JUNCTION DESCRIPTIONS         Pin Function         MCLR         AN0/PGA1P1/CMP1A/RA0         AN1/PGA1P2/PGA2P1/CMP1B/RA1         AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2         AN3/PGA2P3/CMP1D/CMP2B/RP32/RB0         AN4/CMP2C/RP41/RB9                                                                                                                | Pin           15           16           17           18           19           20                                                                  | Pin Function           PGEC3/RP47/RB15           TDO/AN9/PGA2N2/RP37/RB5           PGED1/TDI/AN10/SCL1/RP38/RB6           PGEC1/AN11/SDA1/RP39/RB7           Vss           VcAP                                                                                                                                     |

| Pin           1           2           3           4           5           6           7                                                   | JNCTION DESCRIPTIONS         Pin Function         MCLR         AN0/PGA1P1/CMP1A/RA0         AN1/PGA1P2/PGA2P1/CMP1B/RA1         AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2         AN3/PGA2P3/CMP1D/CMP2B/RP32/RB0         AN4/CMP2C/RP41/RB9         AN5/CMP2D/RP42/RB10                                                                                     | Pin           15           16           17           18           19           20           21                                                     | Pin Function         PGEC3/RP47/RB15         TDO/AN9/PGA2N2/RP37/RB5         PGED1/TDI/AN10/SCL1/RP38/RB6         PGEC1/AN11/SDA1/RP39/RB7         Vss         Vcap         TMS/PWM3H/RP43/RB11                                                                                                                     |

| Pin           1           2           3           4           5           6           7           8                                       | Pin Function         MCLR         AN0/PGA1P1/CMP1A/RA0         AN1/PGA1P2/PGA2P1/CMP1B/RA1         AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2         AN3/PGA2P3/CMP1D/CMP2B/RP32/RB0         AN4/CMP2C/RP41/RB9         AN5/CMP2D/RP42/RB10         Vss                                                                                                      | Pin           15           16           17           18           19           20           21           22                                        | Pin Function           PGEC3/RP47/RB15           TDO/AN9/PGA2N2/RP37/RB5           PGED1/TDI/AN10/SCL1/RP38/RB6           PGEC1/AN11/SDA1/RP39/RB7           Vss           VCAP           TMS/PWM3H/RP43/RB11           TCK/PWM3L/RP44/RB12                                                                         |

| Pin 1 2 3 4 5 6 7 8 9                                                                                                                     | JNCTION DESCRIPTIONS         Pin Function         MCLR         AN0/PGA1P1/CMP1A/RA0         AN1/PGA1P2/PGA2P1/CMP1B/RA1         AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2         AN3/PGA2P3/CMP1D/CMP2B/RP32/RB0         AN4/CMP2C/RP41/RB9         AN5/CMP2D/RP42/RB10         Vss         OSC1/CLKI/AN6/RP33/RB1                                          | Pin           15           16           17           18           19           20           21           22           23                           | Pin Function           PGEC3/RP47/RB15           TDO/AN9/PGA2N2/RP37/RB5           PGED1/TDI/AN10/SCL1/RP38/RB6           PGEC1/AN11/SDA1/RP39/RB7           Vss           VcAP           TMS/PWM3H/RP43/RB11           TCK/PWM3L/RP44/RB12           PWM2H/RP45/RB13                                               |

| Pin           1           2           3           4           5           6           7           8           9           10              | Pin Function         MCLR         AN0/PGA1P1/CMP1A/RA0         AN1/PGA1P2/PGA2P1/CMP1B/RA1         AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2         AN3/PGA2P3/CMP1D/CMP2B/RP32/RB0         AN4/CMP2C/RP41/RB9         AN5/CMP2D/RP42/RB10         Vss         OSC1/CLKI/AN6/RP33/RB1         OSC2/CLKO/AN7/PGA1N2/RP34/RB2                                 | Pin           15           16           17           18           19           20           21           22           23           24              | Pin Function           PGEC3/RP47/RB15           TDO/AN9/PGA2N2/RP37/RB5           PGED1/TDI/AN10/SCL1/RP38/RB6           PGEC1/AN11/SDA1/RP39/RB7           Vss           Vcap           TMS/PWM3H/RP43/RB11           TCK/PWM3L/RP44/RB12           PWM2H/RP45/RB13           PWM2L/RP46/RB14                     |

| Pin           1           2           3           4           5           6           7           8           9           10           11 | Pin Function         MCLR         AN0/PGA1P1/CMP1A/RA0         AN1/PGA1P2/PGA2P1/CMP1B/RA1         AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2         AN3/PGA2P3/CMP1D/CMP2B/RP32/RB0         AN4/CMP2C/RP41/RB9         AN5/CMP2D/RP42/RB10         Vss         OSC1/CLKI/AN6/RP33/RB1         OSC2/CLKO/AN7/PGA1N2/RP34/RB2         PGED2/AN8/INT0/RP35/RB3 | Pin           15           16           17           18           19           20           21           22           23           24           25 | Pin Function           PGEC3/RP47/RB15           TDO/AN9/PGA2N2/RP37/RB5           PGED1/TDI/AN10/SCL1/RP38/RB6           PGEC1/AN11/SDA1/RP39/RB7           Vss           VCAP           TMS/PWM3H/RP43/RB11           TCK/PWM3L/RP44/RB12           PWM2H/RP45/RB13           PWM2L/RP46/RB14           PWM1H/RA4 |

Legend: Shaded pins are up to 5 VDC tolerant.

Note: RPn represents remappable peripheral functions. See Table 10-1 and Table 10-2 for the complete list of remappable sources.

When a PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the PSV pages can occur at the page boundaries when:

- The initial address, prior to modification, addresses the PSV page

- The EA calculation uses Pre- or Post-Modified Register Indirect Addressing; however, this does not include Register Offset Addressing

In general, when an overflow is detected, the DSRPAG register is incremented and the EA<15> bit is set to keep the base address within the PSV window. When an underflow is detected, the DSRPAG register is decremented and the EA<15> bit is set to keep the

base address within the PSV window. This creates a linear PSV address space, but only when using Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0 and PSV spaces. Table 4-24 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when overflow or underflow occurs, the EA<15> bit is set and the DSRPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- Register Indirect with Register Offset Addressing

- Modulo Addressing

- Bit-Reversed Addressing

## TABLE 4-24:OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0 AND<br/>PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

| O/U,        |                    |                | Before       |                        | After          |              |                       |  |

|-------------|--------------------|----------------|--------------|------------------------|----------------|--------------|-----------------------|--|

| 0/0,<br>R/W | Operation          | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page<br>Description   |  |

| O,<br>Read  | [++Wn]             | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>page  | DSRPAG = 0x300 | 1            | PSV: First MSB page   |  |

| O,<br>Read  | Or<br>[Wn++]       | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>page  | DSRPAG = 0x3FF | 0            | See Note 1            |  |

| U,<br>Read  | 5 m l              | DSRPAG = 0x001 | 1            | PSV page               | DSRPAG = 0x001 | 0            | See Note 1            |  |

| U,<br>Read  | [Wn]<br>Or<br>[Wn] | DSRPAG = 0x200 | 1            | PSV: First Isw<br>page | DSRPAG = 0x200 | 0            | See Note 1            |  |

| U,<br>Read  |                    | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>page |  |

**Legend:** O = Overflow, U = Underflow, R = Read, W = Write

Note 1: The Register Indirect Addressing now addresses a location in the base Data Space (0x0000-0x7FFF).

2: An EDS access, when DSRPAG = 0x000, will generate an address error trap.

3: Only reads from PS are supported using DSRPAG.

4: Pseudolinear Addressing is not supported for large offsets.

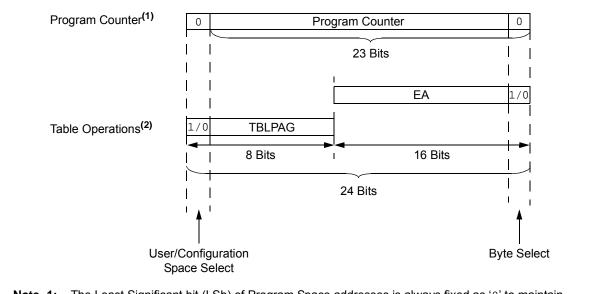

## 4.9 Interfacing Program and Data Memory Spaces

The dsPIC33EPXXGS202 family architecture uses a 24-bit wide Program Space (PS) and a 16-bit wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the Program Space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the architecture of the dsPIC33EPXXGS202 family devices provides two methods by which Program Space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the Program Space

- Remapping a portion of the Program Space into the Data Space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

## TABLE 4-27: PROGRAM SPACE ADDRESS CONSTRUCTION

|                        | Access        | Program Space Address         |                           |                    |                |     |  |

|------------------------|---------------|-------------------------------|---------------------------|--------------------|----------------|-----|--|

| Access Type            | Space         | <23>                          | <22:16>                   | <15>               | <14:1>         | <0> |  |

| Instruction Access     | User          | 0                             | PC<22:1> 0                |                    |                | 0   |  |

| (Code Execution)       |               | 0xxx xxxx xxxx xxxx xxxx xxx0 |                           |                    |                |     |  |

| TBLRD/TBLWT            | User          | TB                            | LPAG<7:0>                 | 7:0> Data EA<15:0> |                |     |  |

| (Byte/Word Read/Write) |               | 0                             | xxx xxxx                  | xxxx               | xxxx xxxx xx   | xx  |  |

|                        | Configuration | TB                            | TBLPAG<7:0> Data EA<15:0> |                    |                |     |  |

|                        |               | 1                             | xxx xxxx                  | xxxx               | . xxxx xxxx xx | xx  |  |

### FIGURE 4-10: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

- **Note 1:** The Least Significant bit (LSb) of Program Space addresses is always fixed as '0' to maintain word alignment of data in the Program and Data Spaces.

- **2:** Table operations are not required to be word-aligned. Table Read operations are permitted in the configuration memory space.

NOTES:

## 5.2 RTSP Operation

The dsPIC33EPXXGS202 family Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a single page (8 rows or 512 instructions) of memory at a time and to program one row at a time. It is possible to program two instructions at a time as well.

The page erase and single row write blocks are edge-aligned, from the beginning of program memory on boundaries of 1536 bytes and 192 bytes, respectively. Figure 25-14 in **Section 25.0 "Electrical Characteristics**" lists the typical erase and programming times.

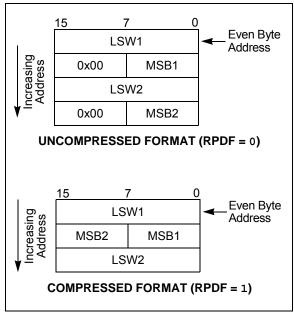

Row programming is performed by loading 192 bytes into data memory and then loading the address of the first byte in that row into the NVMSRCADR register. Once the write has been initiated, the device will automatically load the write latches and increment the NVMSRCADR and the NVMADR(U) registers until all bytes have been programmed. The RPDF bit (NVMCON<9>) selects the format of the stored data in RAM to be either compressed or uncompressed. See Figure 5-2 for data formatting. Compressed data helps to reduce the amount of required RAM by using the upper byte of the second word for the MSB of the second instruction.

The basic sequence for RTSP word programming is to use the TBLWTL and TBLWTH instructions to load two of the 24-bit instructions into the write latches found in configuration memory space. Refer to Figure 4-1 through Figure 4-3 for write latch addresses. Programming is performed by unlocking and setting the control bits in the NVMCON register.

All erase and program operations may optionally use the NVM interrupt to signal the successful completion of the operation.

#### FIGURE 5-2: UNCOMPRESSED/ COMPRESSED FORMAT

## 5.3 **Programming Operations**

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of Program Flash Memory (PFM) at a time on every other word address boundary (0x000000, 0x000004, 0x000008, etc.). To do this, it is necessary to erase the page that contains the desired address of the location the user wants to change. For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

## REGISTER 7-5: INTCON3: INTERRUPT CONTROL REGISTER 3

| U-0          | U-0           | U-0                                  | U-0                                   | U-0                                     | U-0              | U-0      | R/W-0 |  |  |  |  |

|--------------|---------------|--------------------------------------|---------------------------------------|-----------------------------------------|------------------|----------|-------|--|--|--|--|

|              |               | _                                    | —                                     | —                                       | —                | —        | NAE   |  |  |  |  |

| bit 15       |               |                                      |                                       |                                         |                  |          | bit 8 |  |  |  |  |

|              |               |                                      |                                       |                                         |                  |          |       |  |  |  |  |

| U-0          | U-0           | U-0                                  | R/W-0                                 | U-0                                     | U-0              | U-0      | R/W-0 |  |  |  |  |

|              |               |                                      | DOOVR                                 |                                         |                  |          | APLL  |  |  |  |  |

| bit 7        |               |                                      |                                       |                                         |                  |          | bit 0 |  |  |  |  |

|              |               |                                      |                                       |                                         |                  |          |       |  |  |  |  |

| Legend:      |               |                                      |                                       |                                         |                  |          |       |  |  |  |  |

| R = Readab   | ole bit       | W = Writable                         | bit                                   | U = Unimplei                            | mented bit, read | l as '0' |       |  |  |  |  |

| -n = Value a | at POR        | '1' = Bit is se                      | t                                     | '0' = Bit is cleared x = Bit is unknown |                  |          |       |  |  |  |  |

|              |               |                                      |                                       |                                         |                  |          |       |  |  |  |  |

| bit 15-9     | Unimplemen    | ted: Read as                         | '0'                                   |                                         |                  |          |       |  |  |  |  |

| bit 8        | NAE: NVM A    | ddress Error S                       | Soft Trap Statu                       | s bit                                   |                  |          |       |  |  |  |  |

|              | 1 = NVM add   | ress error sof                       | t trap has occu                       | rred                                    |                  |          |       |  |  |  |  |

|              | 0 = NVM add   | ress error sof                       | t trap has not o                      | ccurred                                 |                  |          |       |  |  |  |  |

| bit 7-5      | Unimplemen    | ted: Read as                         | '0'                                   |                                         |                  |          |       |  |  |  |  |

| bit 4        | DOOVR: DO     | Stack Overflov                       | v Soft Trap Sta                       | itus bit                                |                  |          |       |  |  |  |  |

|              | 1 = DO stack  | overflow soft t                      | rap has occurr                        | ed                                      |                  |          |       |  |  |  |  |

|              |               |                                      | rap has not oc                        |                                         |                  |          |       |  |  |  |  |

| bit 3-1      | Unimplemen    | ted: Read as                         | '0'                                   |                                         |                  |          |       |  |  |  |  |

| bit 0        | APLL: Auxilia | ary PLL Loss o                       | of Lock Soft Tra                      | ap Status bit                           |                  |          |       |  |  |  |  |

|              | 1 = APLL loc  | 1 = APLL lock soft trap has occurred |                                       |                                         |                  |          |       |  |  |  |  |

|              |               | k coft tran hac                      | - A PL Lock off trap has not occurred |                                         |                  |          |       |  |  |  |  |

0 = APLL lock soft trap has not occurred

### REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0             | U-0                                           | U-0                                           | U-0            | U-0              | U-0              | U-0             | U-0   |  |  |

|-----------------|-----------------------------------------------|-----------------------------------------------|----------------|------------------|------------------|-----------------|-------|--|--|

| —               | —                                             | —                                             | —              | —                | —                | —               | —     |  |  |

| bit 15          |                                               |                                               |                |                  |                  |                 | bit 8 |  |  |

|                 |                                               |                                               |                |                  |                  |                 |       |  |  |

| U-0             | U-0                                           | U-0                                           | U-0            | U-0              | U-0              | U-0             | R/W-0 |  |  |

| —               | —                                             | —                                             | —              | —                | —                | —               | SGHT  |  |  |

| bit 7           |                                               |                                               |                | •                |                  | •               | bit 0 |  |  |

|                 |                                               |                                               |                |                  |                  |                 |       |  |  |

| Legend:         |                                               |                                               |                |                  |                  |                 |       |  |  |

| R = Readable    | bit                                           | W = Writable                                  | bit            | U = Unimpler     | mented bit, read | as '0'          |       |  |  |

| -n = Value at F | POR                                           | '1' = Bit is set                              |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |

|                 |                                               |                                               |                |                  |                  |                 |       |  |  |

| bit 15-1        | Unimplemen                                    | ted: Read as '                                | 0'             |                  |                  |                 |       |  |  |

| bit 0           | SGHT: Softwa                                  | SGHT: Software Generated Hard Trap Status bit |                |                  |                  |                 |       |  |  |

|                 | 1 = Software generated hard trap has occurred |                                               |                |                  |                  |                 |       |  |  |

|                 | 0 = Software                                  | generated har                                 | d trap has not | occurred         |                  |                 |       |  |  |

|                 |                                               |                                               |                |                  |                  |                 |       |  |  |

## REGISTER 8-4: OSCTUN: FRC OSCILLATOR TUNING REGISTER

| -             |                          |                                                    |              |                                         |                 |          |        |  |

|---------------|--------------------------|----------------------------------------------------|--------------|-----------------------------------------|-----------------|----------|--------|--|

| U-0           | U-0                      | U-0                                                | U-0          | U-0                                     | U-0             | U-0      | U-0    |  |

| —             | _                        |                                                    | —            |                                         | —               | —        |        |  |

| bit 15        |                          |                                                    |              |                                         |                 |          | bit 8  |  |

| U-0           | U-0                      | R/W-0                                              | R/W-0        | R/W-0                                   | R/W-0           | R/W-0    | R/W-0  |  |

| 0-0           | 0-0                      | R/W-0                                              | R/W-0        | -                                       | N<5:0>          | R/W-U    | R/W-0  |  |

|               |                          |                                                    |              | 101                                     | N<5.0>          |          | 1.11.0 |  |

| bit 7         |                          |                                                    |              |                                         |                 |          | bit 0  |  |

|               |                          |                                                    |              |                                         |                 |          |        |  |

| Legend:       |                          |                                                    |              |                                         |                 |          |        |  |

| R = Readable  | e bit                    | W = Writable                                       | bit          | U = Unimple                             | mented bit, rea | d as '0' |        |  |

| -n = Value at | POR                      | '1' = Bit is set                                   |              | '0' = Bit is cleared x = Bit is unknown |                 |          |        |  |

|               |                          |                                                    |              |                                         |                 |          |        |  |

| bit 15-6      | Unimplemen               | ted: Read as '                                     | כי           |                                         |                 |          |        |  |

| bit 5-0       | <b>TUN&lt;5:0&gt;:</b> F | RC Oscillator T                                    | uning bits   |                                         |                 |          |        |  |

|               |                          | aximum frequer<br>nter frequency                   |              |                                         | 77 MHz)         |          |        |  |

|               | 000000 <b>= Ce</b>       | nter frequency<br>nter frequency<br>nter frequency | (7.37 MHz no | minal)                                  |                 |          |        |  |

|               |                          | nter frequency<br>nimum frequen                    | •            | ,                                       | ) MHz)          |          |        |  |

| U-0    | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| _      | _   | RP177R5 | RP177R4 | RP177R3 | RP177R2 | RP177R1 | RP177R0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

|        |     |         |         |         |         |         |         |

| U-0    | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

#### REGISTER 10-24: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | RP176R5 | RP176R4 | RP176R3 | RP176R2 | RP176R1 | RP176R0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP177R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP177 Output Pin bits (see Table 10-2 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                                 |

| bit 5-0   | <b>RP176R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP176 Output Pin bits (see Table 10-2 for peripheral function numbers) |

### REGISTER 10-25: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0    | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| —      | —   | RP179R5 | RP179R4 | RP179R3 | RP179R2 | RP179R1 | RP179R0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | RP178R5 | RP178R4 | RP178R3 | RP178R2 | RP178R1 | RP178R0 |

| bit 7 |     |         |         |         |         | bit 0   |         |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP179R<5:0>:** Peripheral Output Function is Assigned to RP179 Output Pin bits (see Table 10-2 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0' bit 5-0 RP178R<5:0>: Peripheral Output Function is

bit 5-0 **RP178R<5:0>:** Peripheral Output Function is Assigned to RP178 Output Pin bits (see Table 10-2 for peripheral function numbers)

#### REGISTER 14-2: OC1CON2: OUTPUT COMPARE CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits

- 11111 = OC1RS compare event is used for synchronization

- 11110 = INT2 pin synchronizes or triggers OC1

- 11101 = INT1 pin synchronizes or triggers OC1

- 11100 = Reserved

- 11011 = Reserved

- 11010 = Reserved

- $11001 = CMP2 \text{ module triggers OC1}^{(1)}$  $11000 = CMP1 \text{ module triggers OC1}^{(1)}$

- 10111 = Reserved

- 10111 = Reserved

- 101101 = Reserved

- 10100 = Reserved

- 10011 = Reserved

- 10010 = Reserved

- 10001 = Reserved

- 10000 = IC1 input capture interrupt event synchronizes or triggers OC1

- 01111 = Reserved

- 01110 = Reserved

- 01101 = Timer3 synchronizes or triggers OC1

- 01100 = Timer2 synchronizes or triggers OC1 (default)

- 01011 = Timer1 synchronizes or triggers OC1

- 01010 = Reserved

- 01001 = Reserved

- 01000 = Reserved

- 00111 = Reserved

- 00110 = Reserved

- 00101 = IC1 input capture event synchronizes or triggers OC1

- 00100 = Reserved

- 00011 = Reserved

- 00010 = Reserved

- 00001 = Reserved

- 00000 = No sync or trigger source for OC1

- **Note 1:** This option should only be selected as a trigger source and not as a synchronization source.

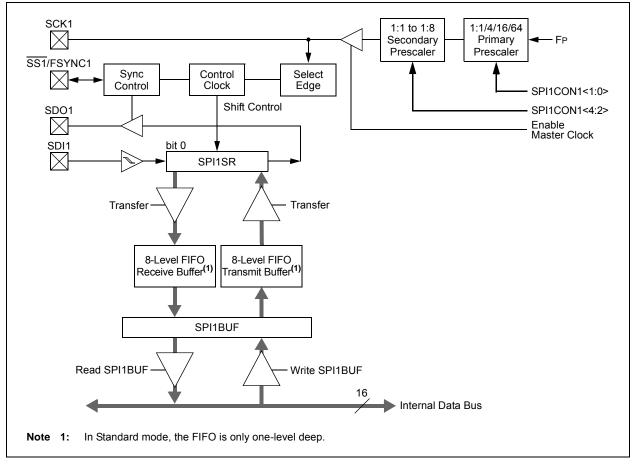

## 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI)" (DS7005185) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The SPI module is a synchronous serial interface, useful for communicating with other peripherals or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, ADC Converters, etc. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces. The dsPIC33EPXXGS202 device family offers one SPI module on a single device.

The SPI1 module takes advantage of the Peripheral Pin Select (PPS) feature to allow for greater flexibility in pin configuration.

The SPI1 serial interface consists of four pins, as follows:

- · SDI1: Serial Data Input

- SDO1: Serial Data Output

- SCK1: Shift Clock Input or Output

- SS1/FSYNC1: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPI1 module can be configured to operate with two, three or four pins. In 3-Pin mode, SS1 is not used. In 2-Pin mode, neither SDO1 nor SS1 is used.

Figure 16-1 illustrates the block diagram of the SPI1 module in Standard and Enhanced modes.

#### FIGURE 16-1: SPI1 MODULE BLOCK DIAGRAM

#### REGISTER 19-16: ADMODOL: ADC INPUT MODE CONTROL REGISTER 0 LOW

| -n = Value at                     | POR   | '1' = Bit is set |                                    | '0' = Bit is clea | ared  | x = Bit is unkr | nown  |

|-----------------------------------|-------|------------------|------------------------------------|-------------------|-------|-----------------|-------|

| R = Readable bit W = Writable bit |       |                  | U = Unimplemented bit, read as '0' |                   |       |                 |       |

| Legend:                           |       |                  |                                    |                   |       |                 |       |

|                                   |       |                  |                                    |                   |       |                 |       |

| bit 7                             |       |                  |                                    | 1                 |       | •               | bit   |

|                                   | SIGN3 |                  | SIGN2                              | DIFF1             | SIGN1 | DIFF0           | SIGN0 |

| U-0                               | R/W-0 | U-0              | R/W-0                              | R/W-0             | R/W-0 | R/W-0           | R/W-0 |

|                                   |       |                  |                                    |                   |       |                 |       |

| bit 15                            |       |                  |                                    |                   |       |                 | bit   |

| —                                 | SIGN7 | _                | SIGN6                              | —                 | SIGN5 | —               | SIGN4 |

| U-0                               | R/W-0 | U-0              | R/W-0                              | U-0               | R/W-0 | U-0             | R/W-0 |

bit (odd)15-5 Unimplemented: Read as '0'

bit (3,1) **DIFF<x>:** Pseudo-Differential Mode for Corresponding Analog Inputs bits 1 = Channel is pseudo-differential 0 = Channel is single-ended

bit (even) **SIGNx:** Output Data Sign for Corresponding Analog Inputs bits

1 = Channel output data is signed

0 = Channel output data is unsigned

### REGISTER 19-17: ADMOD0H: ADC INPUT MODE CONTROL REGISTER 0 HIGH

| U-0     | U-0    | U-0 | R/W-0  | U-0 | R/W-0  | U-0 | R/W-0  |

|---------|--------|-----|--------|-----|--------|-----|--------|

| _       | —      | —   | SIGN14 | —   | SIGN13 | —   | SIGN12 |

| bit 15  |        |     |        |     | ·      | ·   | bit 8  |

|         |        |     |        |     |        |     |        |

| U-0     | R/W-0  | U-0 | R/W-0  | U-0 | R/W-0  | U-0 | R/W-0  |

| _       | SIGN11 | —   | SIGN10 | —   | SIGN9  | —   | SIGN8  |

| bit 7   |        |     | •      | •   |        | •   | bit 0  |

|         |        |     |        |     |        |     |        |

| Logondi |        |     |        |     |        |     |        |

| Legena.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 15-13 **Unimplemented:** Read as '0'

bit (odd) Unimplemented: Read as '0'

bit (even) SIGN<x>: Output Data Sign for Corresponding Analog Inputs bits

1 = Channel output data is signed

0 = Channel output data is unsigned

## REGISTER 19-25: ADCMPxENL: ADC DIGITAL COMPARATOR x CHANNEL ENABLE REGISTER LOW (x = 0,1)

| U-0    | R/W-0   | U-0   | U-0   | R/W-0       | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|--------|---------|-------|-------|-------------|-------|-------|-------|--|--|--|

| _      | CMPEN14 | _     | —     | CMPEN<11:8> |       |       |       |  |  |  |

| bit 15 |         |       |       |             |       |       | bit 8 |  |  |  |

|        |         |       |       |             |       |       |       |  |  |  |

| R/W/0  | R/W-0   | R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|        |         |       | CN    | /IPEN<7:0>  |       |       |       |  |  |  |

| bit 7  |         |       |       |             |       |       | bit 0 |  |  |  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15 Unimplemented: Read as '0'

bit 14 **CMPEN14:** Comparator Enable for Corresponding Input Channel bit 1 = Conversion result for corresponding channel is used by the comparator

0 = Conversion result for corresponding channel is not used by the comparator

- bit 13-12 Unimplemented: Read as '0'

- bit 11-0 **CMPEN<11:0>:** Comparator Enable for Corresponding Input Channels bits

1 = Conversion result for corresponding channel is used by the comparator

$\ensuremath{\scriptscriptstyle 0}$  = Conversion result for corresponding channel is not used by the comparator

## 24.11 Demonstration/Development Boards, Evaluation Kits and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 24.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

## 25.2 AC Characteristics and Timing Parameters

This section defines the dsPIC33EPXXGS202 family AC characteristics and timing parameters.

### TABLE 25-15: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)                                                                                                    |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AC CHARACTERISTICS | $\begin{array}{ll} Operating \ temperature & -40^\circ C \leq TA \leq +85^\circ C \ for \ Industrial \\ -40^\circ C \leq TA \leq +125^\circ C \ for \ Extended \end{array}$ |

|                    | Operating voltage VDD range as described in Section 25.1 "DC Characteristics".                                                                                              |

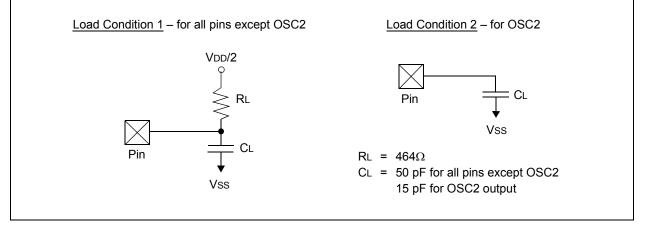

## FIGURE 25-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

### TABLE 25-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min. | Тур. | Max. | Units | Conditions                                                          |

|--------------|--------|-----------------------|------|------|------|-------|---------------------------------------------------------------------|

| DO50         | Cosco  | OSC2 Pin              | _    | —    | 15   |       | In XT and HS modes, when<br>external clock is used to drive<br>OSC1 |

| DO56         | Сю     | All I/O Pins and OSC2 | —    | —    | 50   | pF    | EC mode                                                             |

| DO58         | Св     | SCL1, SDA1            | _    | —    | 400  | pF    | In I <sup>2</sup> C mode                                            |

## TABLE 25-23:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMERTIMING REQUIREMENTS

| AC CHARACTERISTICS |           |                                                                |      | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |      |       |                                                                                                                   |  |  |

|--------------------|-----------|----------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.       | Symbol    | Characteristic <sup>(1)</sup>                                  | Min. | Тур. <sup>(2)</sup>                                                                                                                                                                                  | Max. | Units | Conditions                                                                                                        |  |  |

| SY00               | Τρυ       | Power-up Period                                                | _    | 400                                                                                                                                                                                                  | 600  | μS    |                                                                                                                   |  |  |

| SY10               | Tost      | Oscillator Start-up Time                                       |      | 1024 Tosc                                                                                                                                                                                            | _    | _     | Tosc = OSC1 Period                                                                                                |  |  |

| SY12               | Twdt      | Watchdog Timer<br>Time-out Period                              | 0.81 | _                                                                                                                                                                                                    | 1.22 | ms    | WDTPRE = 0,<br>WDTPOST<3:0> = 0000,<br>using LPRC tolerances indicated in<br>F21a/F21b (see Table 25-21) at +85°C |  |  |

|                    |           |                                                                | 3.25 | _                                                                                                                                                                                                    | 4.88 | ms    | WDTPRE = 1,<br>WDTPOST<3:0> = 0000,<br>using LPRC tolerances indicated in<br>F21a/F21b (see Table 25-21) at +85°C |  |  |

| SY13               | Tioz      | I/O High-Impedance from<br>MCLR Low or Watchdog<br>Timer Reset | 0.68 | 0.72                                                                                                                                                                                                 | 1.2  | μS    |                                                                                                                   |  |  |

| SY20               | TMCLR     | MCLR Pulse Width (low)                                         | 2    | _                                                                                                                                                                                                    | _    | μS    |                                                                                                                   |  |  |

| SY30               | TBOR      | BOR Pulse Width (low)                                          | 1    | _                                                                                                                                                                                                    | _    | μS    |                                                                                                                   |  |  |

| SY35               | TFSCM     | Fail-Safe Clock Monitor<br>Delay                               | _    | 500                                                                                                                                                                                                  | 900  | μS    | -40°C to +85°C                                                                                                    |  |  |

| SY36               | TVREG     | Voltage Regulator<br>Standby-to-Active mode<br>Transition Time | _    | _                                                                                                                                                                                                    | 30   | μS    |                                                                                                                   |  |  |

| SY37               | Toscdfrc  | FRC Oscillator Start-up<br>Delay                               |      | _                                                                                                                                                                                                    | 29   | μS    |                                                                                                                   |  |  |

| SY38               | TOSCDLPRC | LPRC Oscillator Start-up<br>Delay                              |      | —                                                                                                                                                                                                    | 70   | μS    |                                                                                                                   |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

### TABLE 25-31: SPI1 MAXIMUM DATA/CLOCK RATE SUMMARY

| AC CHARACTERISTICS |             |                                            | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |     |     |     |  |  |

|--------------------|-------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--|--|

| Data Rato          |             | Slave<br>Transmit/Receive<br>(Full-Duplex) | CKE                                                                                                                                                                                                                                                                                     | СКР | SMP |     |  |  |

| 15 MHz             | Table 25-31 | _                                          | —                                                                                                                                                                                                                                                                                       | 0,1 | 0,1 | 0,1 |  |  |

| 9 MHz              | —           | Table 25-32                                | —                                                                                                                                                                                                                                                                                       | 1   | 0,1 | 1   |  |  |

| 9 MHz              | —           | Table 25-33                                | —                                                                                                                                                                                                                                                                                       | 0   | 0,1 | 1   |  |  |

| 15 MHz             | —           | —                                          | Table 25-34                                                                                                                                                                                                                                                                             | 1   | 0   | 0   |  |  |

| 11 MHz             | —           | —                                          | Table 25-35                                                                                                                                                                                                                                                                             | 1   | 1   | 0   |  |  |

| 15 MHz             |             | _                                          | Table 25-36                                                                                                                                                                                                                                                                             | 0   | 1   | 0   |  |  |

| 11 MHz             | _           |                                            | Table 25-37                                                                                                                                                                                                                                                                             | 0   | 0   | 0   |  |  |

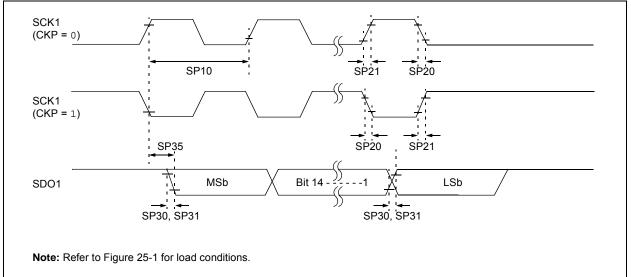

### FIGURE 25-11: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

## TABLE 25-37:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industr $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |   |    |       |                                |

|--------------------|-----------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|-------|--------------------------------|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                | Min. Typ. <sup>(2)</sup> Max.                                                                                                                                                                     |   |    | Units | Conditions                     |

| SP70               | FscP                  | Maximum SCK1 Input Frequency                 | —                                                                                                                                                                                                 | _ | 15 | MHz   | (Note 3)                       |

| SP72               | TscF                  | SCK1 Input Fall Time                         | —                                                                                                                                                                                                 | — |    | ns    | See Parameter DO32 (Note 4)    |

| SP73               | TscR                  | SCK1 Input Rise Time                         | —                                                                                                                                                                                                 | _ | _  | ns    | See Parameter DO31<br>(Note 4) |

| SP30               | TdoF                  | SDO1 Data Output Fall Time                   | —                                                                                                                                                                                                 | — | _  | ns    | See Parameter DO32<br>(Note 4) |

| SP31               | TdoR                  | SDO1 Data Output Rise Time                   | —                                                                                                                                                                                                 | _ | _  | ns    | See Parameter DO31<br>(Note 4) |

| SP35               | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid After<br>SCK1 Edge    | —                                                                                                                                                                                                 | 6 | 20 | ns    |                                |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge | 30                                                                                                                                                                                                | _ |    | ns    |                                |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data Input to SCK1 Edge   | 30                                                                                                                                                                                                | — |    | ns    |                                |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge    | 30                                                                                                                                                                                                | — |    | ns    |                                |

| SP50               | TssL2scH,<br>TssL2scL | SS1 ↓ to SCK1 ↑ or SCK1 ↓<br>Input           | 120                                                                                                                                                                                               | — | _  | ns    |                                |

| SP51               | TssH2doZ              | SS1 ↑ to SDO1 Output<br>High-Impedance       | 10                                                                                                                                                                                                | _ | 50 | ns    | (Note 4)                       |

| SP52               | TscH2ssH,<br>TscL2ssH | SS1 ↑ After SCK1 Edge                        | 1.5 Tcy + 40                                                                                                                                                                                      | — |    | ns    | (Note 4)                       |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 66.7 ns. Therefore, the SCK1 clock generated by the master must not violate this specification.

**4:** Assumes 50 pF load on all SPI1 pins.

NOTES:

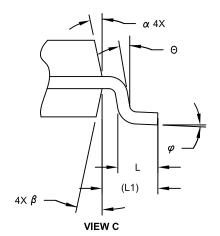

## 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                    |           | MILLIMETERS |     |      |

|--------------------------|-----------|-------------|-----|------|

| Dimension Limits         |           | MIN         | NOM | MAX  |

| Number of Pins           | N         | 28          |     |      |

| Pitch                    | е         | 1.27 BSC    |     |      |

| Overall Height           | Α         | -           | -   | 2.65 |

| Molded Package Thickness | A2        | 2.05        | -   | -    |

| Standoff §               | A1        | 0.10        | -   | 0.30 |

| Overall Width            | E         | 10.30 BSC   |     |      |

| Molded Package Width     | E1        | 7.50 BSC    |     |      |

| Overall Length           | D         | 17.90 BSC   |     |      |

| Chamfer (Optional)       | h         | 0.25        | -   | 0.75 |

| Foot Length              | L         | 0.40        | -   | 1.27 |

| Footprint                | L1        | 1.40 REF    |     |      |

| Lead Angle               | Θ         | 0°          | -   | -    |

| Foot Angle               | $\varphi$ | 0°          | -   | 8°   |

| Lead Thickness           | С         | 0.18        | -   | 0.33 |

| Lead Width               | b         | 0.31        | -   | 0.51 |

| Mold Draft Angle Top     | α         | 5°          | -   | 15°  |

| Mold Draft Angle Bottom  | β         | 5°          | -   | 15°  |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2

NOTES: