Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 2K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-UQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-UQFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gs202t-e-mx |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

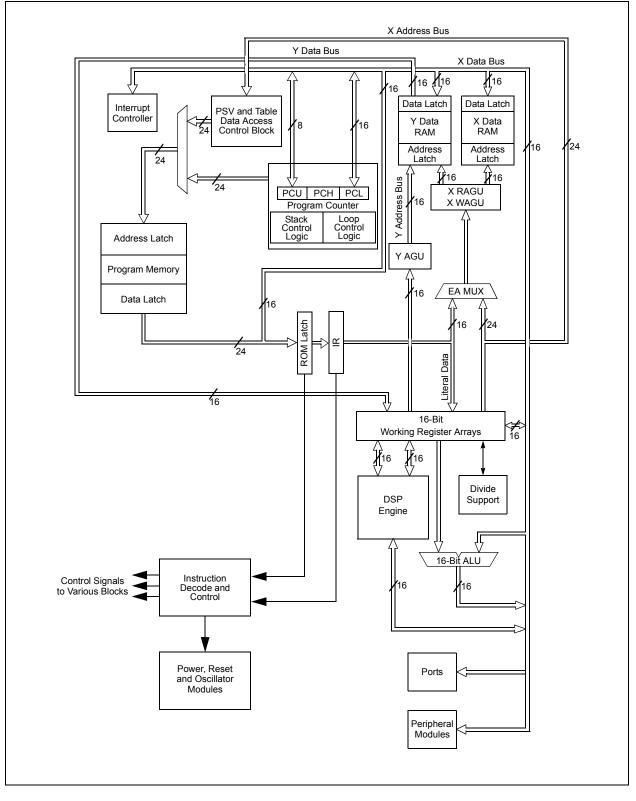

### FIGURE 3-1: dsPIC33EPXXGS202 CPU BLOCK DIAGRAM

#### 3.6 CPU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 3.6.1 KEY RESOURCES

- "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### TABLE 4-14: ADC REGISTER MAP (CONTINUED)

| File<br>Name | Addr. | Bit 15  | Bit 14                 | Bit 13 | Bit 12 | Bit 11    | Bit 10    | Bit 9     | Bit 8     | Bit 7          | Bit 6 | Bit 5 | Bit 4 | Bit 3    | Bit 2    | Bit 1  | Bit 0   | All<br>Resets |

|--------------|-------|---------|------------------------|--------|--------|-----------|-----------|-----------|-----------|----------------|-------|-------|-------|----------|----------|--------|---------|---------------|

| ADCON5L      | 0400  | SHRRDY  | _                      | _      | _      | -         | _         | C1RDY     | CORDY     | SHRPWR         | —     | -     | _     | _        | _        | C1PWR  | C0PWR   | 0000          |

| ADCON5H      | 0402  | -       | -                      | -      | -      | WARMTIME3 | WARMTIME2 | WARMTIME1 | WARMTIME0 | SHRCIE         | -     | -     | -     | -        | -        | C1CIE  | COCIE   | 0000          |

| ADCAL0L      | 0404  | CAL1RDY | -                      | _      | -      | CAL1SKIP  | CAL1DIFF  | CAL1EN    | CAL1RUN   | CALORDY        | _     | -     | -     | CALOSKIP | CAL0DIFF | CAL0EN | CALORUN | 0000          |

| ADCAL1H      | 040A  | CSHRRDY | -                      | _      | -      | CSHRSKIP  | CSHRDIFF  | CSHREN    | CSHRRUN   | -              | _     | -     | -     | -        | -        | _      | -       | 0000          |

| ADCBUF0      | 040C  |         | ADC Data Buffer 0 0000 |        |        |           |           |           |           | 0000           |       |       |       |          |          |        |         |               |

| ADCBUF1      | 040E  |         | ADC Data Buffer 1 0000 |        |        |           |           |           |           | 0000           |       |       |       |          |          |        |         |               |

| ADCBUF2      | 0410  |         | ADC Data Buffer 2      |        |        |           |           |           | 0000      |                |       |       |       |          |          |        |         |               |

| ADCBUF3      | 0412  |         |                        |        |        |           |           |           | ADC       | Data Buffer 3  |       |       |       |          |          |        |         | 0000          |

| ADCBUF4      | 0414  |         |                        |        |        |           |           |           | ADC       | Data Buffer 4  |       |       |       |          |          |        |         | 0000          |

| ADCBUF5      | 0416  |         |                        |        |        |           |           |           | ADC       | Data Buffer 5  |       |       |       |          |          |        |         | 0000          |

| ADCBUF6      | 0418  |         |                        |        |        |           |           |           | ADC       | Data Buffer 6  |       |       |       |          |          |        |         | 0000          |

| ADCBUF7      | 041A  |         |                        |        |        |           |           |           | ADC       | Data Buffer 7  |       |       |       |          |          |        |         | 0000          |

| ADCBUF8      | 041C  |         |                        |        |        |           |           |           | ADC       | Data Buffer 8  |       |       |       |          |          |        |         | 0000          |

| ADCBUF9      | 041E  |         |                        |        |        |           |           |           | ADC       | Data Buffer 9  |       |       |       |          |          |        |         | 0000          |

| ADCBUF10     | 0420  |         | ADC Data Buffer 10     |        |        |           |           |           | 0000      |                |       |       |       |          |          |        |         |               |

| ADCBUF11     | 0422  |         |                        |        |        |           |           |           | ADC       | Data Buffer 11 |       |       |       |          |          |        |         | 0000          |

| ADCBUF14     | 0428  |         |                        |        |        |           |           |           | ADC       | Data Buffer 14 |       |       |       |          |          |        |         | 0000          |

dsPIC33EPXXGS202 FAMILY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| FIGURE 7-1:                       | dsPIC33EPXXGS202 FAMIL      | ( INTERRUPT V | ECTOR TABLE              |

|-----------------------------------|-----------------------------|---------------|--------------------------|

|                                   |                             |               |                          |

|                                   | Reset – GOTO Instruction    | 0x000000      |                          |

| orit                              | Reset – GOTO Address        | 0x000002      |                          |

| P                                 | Oscillator Fail Trap Vector | 0x000004      |                          |

| der                               | Address Error Trap Vector   | 0x000006      |                          |

| ō                                 | Generic Hard Trap Vector    | 0x000008      |                          |

| Decreasing Natural Order Priority | Stack Error Trap Vector     | 0x00000A      |                          |

| Vat                               | Math Error Trap Vector      | 0x00000C      |                          |

| - DC                              | Reserved                    | 0x00000E      |                          |

| asii                              | Generic Soft Trap Vector    | 0x000010      |                          |

| cre                               | Reserved                    | 0x000012      |                          |

| De                                | Interrupt Vector 0          | 0x000014      |                          |

| Ę                                 | Interrupt Vector 1          | 0x000016      |                          |

| 2                                 | :                           | :             |                          |

|                                   | :                           | :             |                          |

|                                   | :                           | :             |                          |

|                                   | Interrupt Vector 52         | 0x00007C      |                          |

|                                   | Interrupt Vector 53         | 0x00007E      |                          |

|                                   | Interrupt Vector 54         | 0x000080      | See Table 7-1 for        |

|                                   | :                           | :             | Interrupt Vector Details |

|                                   | :                           | :             | ,                        |

|                                   | :                           | :             |                          |

|                                   | Interrupt Vector 116        | 0x0000FC      |                          |

|                                   | Interrupt Vector 117        | 0x0000FE      |                          |

|                                   | Interrupt Vector 118        | 0x000100      |                          |

|                                   | Interrupt Vector 119        | 0x000102      |                          |

|                                   | Interrupt Vector 120        | 0x000104      |                          |

|                                   | :                           | :             |                          |

|                                   | :                           | :             |                          |

|                                   | :                           | :             |                          |

|                                   | Interrupt Vector 244        | 0x0001FC      |                          |

| ▼                                 | Interrupt Vector 245        | 0x0001FE      | <b>y</b>                 |

|                                   | START OF CODE               | 0x000200      |                          |

|                                   |                             |               |                          |

|                                   |                             |               |                          |

| Reserved<br>Oscillator Fail Trap Vector<br>Address Error Trap Vector<br>Generic Hard Trap Vector<br>Stack Error Trap Vector<br>Math Error Trap Vector<br>Reserved<br>Generic Soft Trap Vector<br>Reserved | BSLIM<12:0>(1) + 0x000002<br>BSLIM<12:0>(1) + 0x000004<br>BSLIM<12:0>(1) + 0x000006<br>BSLIM<12:0>(1) + 0x000008<br>BSLIM<12:0>(1) + 0x00000A<br>BSLIM<12:0>(1) + 0x00000C<br>BSLIM<12:0>(1) + 0x00000E<br>BSLIM<12:0>(1) + 0x00000E |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address Error Trap Vector<br>Generic Hard Trap Vector<br>Stack Error Trap Vector<br>Math Error Trap Vector<br>Reserved<br>Generic Soft Trap Vector                                                        | BSLIM<12:0> <sup>(1)</sup> + 0x000006<br>BSLIM<12:0> <sup>(1)</sup> + 0x000008<br>BSLIM<12:0> <sup>(1)</sup> + 0x00000A<br>BSLIM<12:0> <sup>(1)</sup> + 0x00000C<br>BSLIM<12:0> <sup>(1)</sup> + 0x00000E                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Generic Hard Trap Vector<br>Stack Error Trap Vector<br>Math Error Trap Vector<br>Reserved<br>Generic Soft Trap Vector                                                                                     | BSLIM<12:0> <sup>(1)</sup> + 0x000008<br>BSLIM<12:0> <sup>(1)</sup> + 0x00000A<br>BSLIM<12:0> <sup>(1)</sup> + 0x00000C<br>BSLIM<12:0> <sup>(1)</sup> + 0x00000E                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Stack Error Trap Vector<br>Math Error Trap Vector<br>Reserved<br>Generic Soft Trap Vector                                                                                                                 | BSLIM<12:0> <sup>(1)</sup> + 0x00000A<br>BSLIM<12:0> <sup>(1)</sup> + 0x00000C<br>BSLIM<12:0> <sup>(1)</sup> + 0x00000E                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Math Error Trap Vector<br>Reserved<br>Generic Soft Trap Vector                                                                                                                                            | BSLIM<12:0> <sup>(1)</sup> + 0x00000C<br>BSLIM<12:0> <sup>(1)</sup> + 0x00000E                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Reserved<br>Generic Soft Trap Vector                                                                                                                                                                      | BSLIM<12:0>(1) + 0x00000E                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Generic Soft Trap Vector                                                                                                                                                                                  |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| •                                                                                                                                                                                                         |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Bosonvod                                                                                                                                                                                                  | BSLIM<12:0>(*) + 0x000010                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Reserveu                                                                                                                                                                                                  | BSLIM<12:0> <sup>(1)</sup> + 0x000012                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Interrupt Vector 0                                                                                                                                                                                        | BSLIM<12:0> <sup>(1)</sup> + 0x000014                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Interrupt Vector 1                                                                                                                                                                                        | BSLIM<12:0> <sup>(1)</sup> + 0x000016                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| :                                                                                                                                                                                                         | :                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| :                                                                                                                                                                                                         | :                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| :                                                                                                                                                                                                         | :                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Interrupt Vector 52                                                                                                                                                                                       |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Interrupt Vector 53                                                                                                                                                                                       |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Interrupt Vector 54                                                                                                                                                                                       | BSLIM<12:0> <sup>(1)</sup> + 0x000080                                                                                                                                                                                                | See Table 7-1 for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| :                                                                                                                                                                                                         | :                                                                                                                                                                                                                                    | Interrupt Vector Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| :                                                                                                                                                                                                         | :                                                                                                                                                                                                                                    | /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| :                                                                                                                                                                                                         | :                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Interrupt Vector 116                                                                                                                                                                                      |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Interrupt Vector 117                                                                                                                                                                                      |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Interrupt Vector 118                                                                                                                                                                                      |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Interrupt Vector 119                                                                                                                                                                                      |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Interrupt Vector 120                                                                                                                                                                                      | BSLIM<12:0> <sup>(1)</sup> + 0x000104                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| :                                                                                                                                                                                                         | :                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| :                                                                                                                                                                                                         | :                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| :                                                                                                                                                                                                         | :                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                           |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Interrupt Vector 245                                                                                                                                                                                      | BSLIM<12:0> <sup>(1)</sup> + 0x0001FE                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                           | Interrupt Vector 53<br>Interrupt Vector 54<br>:<br>Interrupt Vector 116<br>Interrupt Vector 117<br>Interrupt Vector 118<br>Interrupt Vector 119<br>Interrupt Vector 120<br>:<br>Interrupt Vector 244                                 | Interrupt Vector 53         BSLIM<12:0> <sup>(1)</sup> + 0x00007E           Interrupt Vector 54         BSLIM<12:0> <sup>(1)</sup> + 0x000080           :         :           :         :           :         :           :         :           :         :           :         :           :         :           :         :           :         :           :         :           :         :           :         :           :         :           :         :           :         :           :         :           :         :           :         :           :         :           :         :           :         :           :         :           :         :           :         :           :         :           :         :           :         :           :         :           :         :           :         :           :         : <td:< td="">         :           <t< td=""></t<></td:<> |

### **REGISTER 8-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

- bit 4 Unimplemented: Read as '0'

- bit 3 **CF:** Clock Fail Detect bit<sup>(3)</sup>

- 1 = FSCM has detected a clock failure

- 0 = FSCM has not detected a clock failure

- bit 2-1 Unimplemented: Read as '0'

- bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Requests oscillator switch to selection specified by the NOSC<2:0> bits

- 0 = Oscillator switch is complete

- **Note 1:** Writes to this register require an unlock sequence.

- 2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- **3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

| REGISTER     | R 9-4: PMD6 | : PERIPHER       |             | E DISABLE C                             | ONTROL RE        | GISTER 6 |        |

|--------------|-------------|------------------|-------------|-----------------------------------------|------------------|----------|--------|

| U-0          | U-0         | U-0              | U-0         | U-0                                     | R/W-0            | R/W-0    | R/W-0  |

| —            | —           | _                | —           | —                                       | PWM3MD           | PWM2MD   | PWM1MD |

| bit 15       |             |                  |             |                                         |                  |          | bit 8  |

|              |             |                  |             |                                         |                  |          |        |

| U-0          | U-0         | U-0              | U-0         | U-0                                     | U-0              | U-0      | U-0    |

|              | _           |                  | —           | —                                       |                  | —        | —      |

| bit 7        |             |                  |             |                                         |                  |          | bit 0  |

|              |             |                  |             |                                         |                  |          |        |

| Legend:      |             |                  |             |                                         |                  |          |        |

| R = Readal   | ole bit     | W = Writable     | bit         | U = Unimplen                            | nented bit, read | 1 as '0' |        |

| -n = Value a | at POR      | '1' = Bit is set | t           | '0' = Bit is cleared x = Bit is unknown |                  |          | iown   |

|              |             |                  |             |                                         |                  |          |        |

| bit 15-11    | Unimplement | ted: Read as '   | 0'          |                                         |                  |          |        |

| bit 10       | PWM3MD: P\  | VM3 Module [     | Disable bit |                                         |                  |          |        |

|              | 1 = PWM3 mo |                  |             |                                         |                  |          |        |

|              | 0 = PWM3 mo | odule is enable  | ed          |                                         |                  |          |        |

| bit 9        | PWM2MD: P\  | VM2 Module [     | Disable bit |                                         |                  |          |        |

|              | 1 = PWM2 mo |                  |             |                                         |                  |          |        |

|              | 0 = PWM2 mo |                  |             |                                         |                  |          |        |

| bit 8        | PWM1MD: P\  | VM1 Module [     | Disable bit |                                         |                  |          |        |

|              | 1 = PWM1 mo |                  |             |                                         |                  |          |        |

|              | 0 = PWM1 mc |                  |             |                                         |                  |          |        |

| bit 7-0      | Unimplement | ted: Read as '   | 0'          |                                         |                  |          |        |

|              |             |                  |             |                                         |                  |          |        |

#### REGISTER 15-27: PWMCAPx: PWMx PRIMARY TIME BASE CAPTURE REGISTER

| R-0              | R-0 | R-0                        | R-0    | R-0                         | R-0              | R-0      | R-0   |

|------------------|-----|----------------------------|--------|-----------------------------|------------------|----------|-------|

|                  |     |                            | PWMCAP | <12:5> <sup>(1,2,3,4)</sup> |                  |          |       |

| bit 15           |     |                            |        |                             |                  |          | bit 8 |

|                  |     |                            |        |                             |                  |          |       |

| R-0              | R-0 | R-0                        | R-0    | R-0                         | U-0              | U-0      | U-0   |

|                  | PW  | /MCAP<4:0> <sup>(1,2</sup> | ,3,4)  |                             | —                | —        | —     |

| bit 7            |     |                            |        |                             |                  |          | bit 0 |

|                  |     |                            |        |                             |                  |          |       |

| Legend:          |     |                            |        |                             |                  |          |       |

| R = Readable bit |     | W = Writable I             | bit    | U = Unimplen                | nented bit, read | l as '0' |       |

R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-3 **PWMCAP<12:0>:** Captured PWMx Time Base Value bits<sup>(1,2,3,4)</sup> The value in this register represents the captured PWMx time base value when a leading edge is detected on the current-limit input.

#### bit 2-0 Unimplemented: Read as '0'

- **Note 1:** The capture feature is only available on a primary output (PWMxH).

- 2: This feature is active only after LEB processing on the current-limit input signal is complete.

- **3:** The minimum capture resolution is 8.32 ns.

- 4: This feature can be used when the XPRES bit (PWMCONx<1>) is set to '0'.

NOTES:

### REGISTER 17-1: I2C1CONL: I2C1 CONTROL REGISTER LOW (CONTINUED)

| bit 6 | STREN: SCL1 Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)                                                                                                          |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Used in conjunction with the SCLREL bit.                                                                                                                                                 |

|       | 1 = Enables software or receives clock stretching                                                                                                                                        |

|       | 0 = Disables software or receives clock stretching                                                                                                                                       |

| bit 5 | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                |

|       | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge                                                                      |

|       | 0 = Sends ACK during Acknowledge                                                                                                                                                         |

| bit 4 | ACKEN: Acknowledge Sequence Enable bit                                                                                                                                                   |

|       | (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                            |

|       | <ul> <li>1 = Initiates Acknowledge sequence on the SDA1 and SCL1 pins and transmits the ACKDT data bit.<br/>Hardware clears it at the end of the master Acknowledge sequence.</li> </ul> |

|       | 0 = Acknowledge sequence is not in progress                                                                                                                                              |

| bit 3 | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                              |

|       | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware clears it at the end of the eighth bit of the master receive<br/>data byte.</li> </ul>                                    |

|       | 0 = Receive sequence is not in progress                                                                                                                                                  |

| bit 2 | <b>PEN:</b> Stop Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                        |

|       | <ul> <li>1 = Initiates Stop condition on the SDA1 and SCL1 pins. Hardware clears it at the end of the master<br/>Stop sequence.</li> </ul>                                               |

|       | 0 = Stop condition is not in progress                                                                                                                                                    |

| bit 1 | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                             |

|       | 1 = Initiates Repeated Start condition on the SDA1 and SCL1 pins. Hardware clears it at the end of the<br>master Repeated Start sequence.                                                |

|       | 0 = Repeated Start condition is not in progress                                                                                                                                          |

| bit 0 | SEN: Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                              |

|       | 1 = Initiates Start condition on the SDA1 and SCL1 pins. Hardware clears it at the end of the master Start sequence.                                                                     |

0 = Start condition is not in progress

#### REGISTER 17-4: I2C1MSK: I2C1 SLAVE MODE ADDRESS MASK REGISTER

|                 | -     |                  | -     |                  |                 |                 |       |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

| U-0             | U-0   | U-0              | U-0   | U-0              | U-0             | R/W-0           | R/W-0 |

|                 | _     | —                |       | —                | —               | AMSK            | <9:8> |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | AMSł  | <<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimple      | mented bit, rea | ad as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | eared           | x = Bit is unkr | iown  |

bit 15-10 Unimplemented: Read as '0'

bit 9-0

AMSK<9:0>: Address Mask Select bits

For 10-Bit Address:

1 = Enables masking for bit Ax of incoming message address; bit match is not required in this position

0 = Disables masking for bit Ax; bit match is required in this position

For 7-Bit Address (I2C1MSK<6:0> only):

1 = Enables masking for bit Ax + 1 of incoming message address; bit match is not required in this position

0 = Disables masking for bit Ax + 1; bit match is required in this position

#### REGISTER 19-2: ADCON1H: ADC CONTROL REGISTER 1 HIGH

| U-0                               | U-0                   | U-0              | U-0           | U-0                | U-0             | U-0    | U-0   |

|-----------------------------------|-----------------------|------------------|---------------|--------------------|-----------------|--------|-------|

|                                   | —                     | —                | —             | —                  | —               | —      | —     |

| bit 15                            |                       |                  |               |                    |                 |        | bit 8 |

|                                   |                       |                  |               |                    |                 |        |       |

| R/W-0                             | R/W-1                 | R/W-1            | U-0           | U-0                | U-0             | U-0    | U-0   |

| FORM                              | SHRRES1               | SHRRES0          |               | _                  | —               |        | —     |

| bit 7                             |                       |                  |               |                    |                 |        | bit 0 |

|                                   |                       |                  |               |                    |                 |        |       |

| Legend:                           |                       |                  |               |                    |                 |        |       |

| R = Readable bit W = Writable bit |                       |                  | it            | U = Unimpleme      | ented bit, read | as '0' |       |

| -n = Value at                     | POR                   | '1' = Bit is set |               | '0' = Bit is clear | nown            |        |       |

|                                   |                       |                  |               |                    |                 |        |       |

| bit 15-8                          | Unimplemen            | ted: Read as '0' |               |                    |                 |        |       |

| bit 7                             | FORM: Fracti          | onal Data Outpu  | ut Format bit | t                  |                 |        |       |

|                                   | 1 = Fractional        | l                |               |                    |                 |        |       |

|                                   | 0 = Integer           |                  |               |                    |                 |        |       |

| bit 6-5                           | SHRRES<1:0            | >: Shared ADC    | Core Resol    | ution Selection b  | oits            |        |       |

|                                   | 11 = 12-bit re        |                  |               |                    |                 |        |       |

|                                   | 10 = 10-bit re        |                  |               |                    |                 |        |       |

|                                   | 01 = 8-bit res        |                  |               |                    |                 |        |       |

|                                   | 00 <b>= 6-bit res</b> |                  |               |                    |                 |        |       |

| bit 4-0                           | Unimplemen            | ted: Read as '0' |               |                    |                 |        |       |

|                                   |                       |                  |               |                    |                 |        |       |

#### REGISTER 19-20: ADTRIGXL: ADC CHANNEL TRIGGER x SELECTION REGISTER LOW

(x = 0 to 3)

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0         | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|---------------|-------|-------|

|        |     | _   |       | TR    | GSRC(4x+1)<4  | :0>   |       |

| bit 15 |     |     |       |       |               |       | bit 8 |

|        |     |     |       |       |               |       |       |

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0         | R/W-0 | R/W-0 |

| _      |     | —   |       | TF    | RGSRC(4x)<4:0 | )>    |       |

| bit 7  |     |     |       |       |               |       | bit 0 |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 15-13 Unimplemented: Read as '0'

| bit 12-8 | TRGSRC(4x+1)<4:0>: Trigger Source Selection for Corresponding Analog Inputs bits   |

|----------|------------------------------------------------------------------------------------|

|          | 11111 = ADTRG31                                                                    |

|          | 11110 = Reserved                                                                   |

|          | 11101 = Reserved                                                                   |

|          | 11100 = Reserved                                                                   |

|          | 11011 = Reserved                                                                   |

|          | 11010 = PWM Generator 3 current-limit trigger                                      |

|          | 11001 = PWM Generator 2 current-limit trigger                                      |

|          | 11000 = PWM Generator 1 current-limit trigger                                      |

|          | 10111 = Reserved                                                                   |

|          | 10110 = Output Compare 1 trigger                                                   |

|          | 10101 = Reserved                                                                   |

|          | 10100 = Reserved                                                                   |

|          | 10011 = Reserved                                                                   |

|          | 10010 = Reserved                                                                   |

|          | 10001 = PWM Generator 3 secondary trigger                                          |

|          | 10000 = PWM Generator 2 secondary trigger                                          |

|          | 01111 = PWM Generator 1 secondary trigger                                          |

|          | 01110 = PWM secondary Special Event Trigger                                        |

|          | 01101 = Timer2 period match                                                        |

|          | 01100 = Timer1 period match                                                        |

|          | 01011 = Reserved                                                                   |

|          | 01010 = Reserved                                                                   |

|          | 01001 = Reserved                                                                   |

|          | 01000 = Reserved                                                                   |

|          | 00111 = PWM Generator 3 primary trigger                                            |

|          | 00110 = PWM Generator 2 primary trigger<br>00101 = PWM Generator 1 primary trigger |

|          | 00100 = PWM Secial Event Trigger                                                   |

|          | 00011 = Reserved                                                                   |

|          | 00010 = Level software trigger                                                     |

|          | 00001 = Common software trigger                                                    |

|          | 00000 = No trigger is enabled                                                      |

| bit 7-5  | Unimplemented: Read as '0'                                                         |

| DIL 7-0  | Uninpienteu. Nedu as U                                                             |

#### REGISTER 19-23: ADCAL1H: ADC CALIBRATION REGISTER 1 HIGH

| R/W-0, HS | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0  | R/W-0   |

|-----------|-----|-----|-----|----------|----------|--------|---------|

| CSHRRDY   |     | —   | —   | CSHRSKIP | CSHRDIFF | CSHREN | CSHRRUN |

| bit 15    |     |     |     |          |          |        | bit 8   |

|           |     |     |     |          |          |        |         |