#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 2K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gs202t-e-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**CORCON: CORE CONTROL REGISTER**

REGISTER 3-2:

|                     | U-0                             | R/W-0                                                 | R/W-0                               | R/W-0               | R-0              | R-0             | R-0   |

|---------------------|---------------------------------|-------------------------------------------------------|-------------------------------------|---------------------|------------------|-----------------|-------|

| VAR                 | _                               | US1                                                   | US0                                 | EDT <sup>(1)</sup>  | DL2              | DL1             | DL0   |

| bit 15              |                                 |                                                       |                                     |                     |                  |                 | bit   |

| R/W-0               | R/W-0                           | R/W-1                                                 | R/W-0                               | R/C-0               | R-0              | R/W-0           | R/W-0 |

| SATA                | SATB                            | SATDW                                                 | ACCSAT                              | IPL3 <sup>(2)</sup> | SFA              | RND             | IF    |

| bit 7               |                                 |                                                       |                                     |                     |                  |                 | bit   |

| Legend:             |                                 | C = Clearable                                         | e bit                               |                     |                  |                 |       |

| R = Readable        | bit                             | W = Writable                                          | bit                                 | U = Unimplem        | nented bit, read | d as '0'        |       |

| -n = Value at P     | POR                             | '1' = Bit is set                                      | t                                   | '0' = Bit is clea   |                  | x = Bit is unkn | iown  |

| bit 15              | 1 = Variable e<br>0 = Fixed exc | exception process                                     | sing latency                        | ncy Control bit     |                  |                 |       |

| bit 14<br>bit 13-12 | -                               | ted: Read as '                                        | o<br>igned/Signed (                 |                     |                  |                 |       |

| bit 11              | 01 = DSP eng<br>00 = DSP eng    | gine multiplies<br>gine multiplies<br>gine multiplies |                                     |                     |                  |                 |       |

|                     |                                 |                                                       |                                     | nd of current lo    | op iteration     |                 |       |

| bit 10-8            | <b>DL&lt;2:0&gt;:</b> DO        | Loop Nesting                                          | Level Status bi                     | ts                  |                  |                 |       |

|                     | 111 <b>= 7</b> DO <b>lo</b>     | ops are active                                        |                                     |                     |                  |                 |       |

|                     | •                               |                                                       |                                     |                     |                  |                 |       |

|                     | •                               |                                                       |                                     |                     |                  |                 |       |

|                     | 001 = 1 DO lo<br>000 = 0 DO lo  | op is active<br>ops are active                        |                                     |                     |                  |                 |       |

| bit 7               | SATA: ACCA                      | Saturation En                                         | able bit                            |                     |                  |                 |       |

|                     |                                 | ator A saturatio<br>ator A saturatio                  |                                     |                     |                  |                 |       |

| bit 6               | SATB: ACCB                      | Saturation En                                         | able bit                            |                     |                  |                 |       |

|                     |                                 | ator B saturatio<br>ator B saturatio                  |                                     |                     |                  |                 |       |

| bit 5               | SATDW: Data                     | a Space Write                                         | from DSP Engi                       | ine Saturation I    | Enable bit       |                 |       |

|                     |                                 |                                                       | tion is enabled<br>tion is disabled |                     |                  |                 |       |

| bit 4               | ACCSAT: Acc                     | cumulator Satu                                        | ration Mode S                       | elect bit           |                  |                 |       |

|                     |                                 | ration (super s                                       |                                     |                     |                  |                 |       |

|                     | 0 = 1.31 satu                   | ration (normal                                        | saturation)                         |                     |                  |                 |       |

| bit 3               |                                 | •                                                     | Level Status b                      | it 3 <b>(2)</b>     |                  |                 |       |

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

| File<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8     | Bit 7       | Bit 6    | Bit 5       | Bit 4        | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|---------|--------|---------|--------|--------|--------|--------|-----------|-------------|----------|-------------|--------------|--------------|-------|-------|-------|---------------|

| I2C1CONL     | 0200  | I2CEN   | _      | I2CSIDL | SCLREL | STRICT | A10M   | DISSLW | SMEN      | GCEN        | STREN    | ACKDT       | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1CONH     | 0202  | _       | _      | _       | _      | _      | _      | _      | _         | _           | PCIE     | SCIE        | BOEN         | SDAHT        | SBCDE | AHEN  | DHEN  | 0000          |

| I2C1STAT     | 0204  | ACKSTAT | TRSTAT | ACKTIM  | _      | _      | BCL    | GCSTAT | ADD10     | IWCOL       | I2COV    | D_A         | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD      | 0206  |         |        | _       | —      | _      | -      |        |           |             |          | I2C1 Addr   | ess Register | r            |       |       |       | 0000          |

| I2C1MSK      | 0208  |         | _      | _       | —      | _      |        |        |           |             | Ľ        | 2C1 Address | Mask Regis   | ster         |       |       |       | 0000          |

| I2C1BRG      | 020A  |         |        |         |        |        |        | E      | Baud Rate | Generator F | Register |             |              |              |       |       |       | 0000          |

| I2C1TRN      | 020C  |         | _      | _       | —      | _      |        | —      |           |             |          |             | I2C1 Transr  | mit Register |       |       |       | 00FF          |

| I2C1RCV      | 020E  | -       | -      | —       | _      | _      |        | _      |           |             |          |             | I2C1 Recei   | ve Register  |       |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-12: UART1 REGISTER MAP

| File<br>Name | Addr. | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8      | Bit 7        | Bit 6    | Bit 5   | Bit 4       | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|----------|--------|----------|--------|--------|--------|-----------|------------|--------------|----------|---------|-------------|--------|--------|--------|-------|---------------|

| U1MODE       | 0220  | UARTEN   |        | USIDL    | IREN   | RTSMD  | _      | UEN1      | UEN0       | WAKE         | LPBACK   | ABAUD   | URXINV      | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA        | 0222  | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF     | TRMT       | URXISEL1     | URXISEL0 | ADDEN   | RIDLE       | PERR   | FERR   | OERR   | URXDA | 0110          |

| U1TXREG      | 0224  | -        | _      | _        | _      | _      | _      | _         |            |              |          | UART1 1 | ransmit Re  | gister |        |        |       | xxxx          |

| U1RXREG      | 0226  | -        | _      | _        | _      | _      | _      | _         |            |              |          | UART1 F | Receive Reg | gister |        |        |       | 0000          |

| U1BRG        | 0228  |          |        |          |        |        |        | Baud Rate | e Generato | or Prescaler | Register |         |             |        |        |        |       | 0000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-13: SPI1 REGISTER MAP

|    | File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10  | Bit 9    | Bit 8       | Bit 7       | Bit 6       | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|----|--------------|-------|--------|--------|---------|--------|--------|---------|----------|-------------|-------------|-------------|--------|--------|--------|--------|--------|--------|---------------|

| \$ | SPI1STAT     | 0240  | SPIEN  | _      | SPISIDL |        | —      | SPIBEC2 | SPIBEC1  | SPIBEC0     | SRMPT       | SPIROV      | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| Ś  | SPI1CON1     | 0242  | _      | _      | —       | DISSCK | DISSDO | MODE16  | SMP      | CKE         | SSEN        | CKP         | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| ŝ  | SPI1CON2     | 0244  | FRMEN  | SPIFSD | FRMPOL  | _      | _      | _       | _        | _           | _           |             | _      | _      | _      | _      | FRMDLY | SPIBEN | 0000          |

| ŝ  | SPI1BUF      | 0248  |        |        |         |        |        |         | SPI1 Tra | nsmit and R | eceive Buff | er Register | r      |        |        |        |        |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-15: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|--------------|-------|--------|--------|---------|---------|---------|---------|---------|---------|-------|-------|---------|---------|---------|---------|---------|---------|---------------|

| RPOR0        | 0670  | —      | —      | RP33R5  | RP33R4  | RP33R3  | RP33R2  | RP33R1  | RP33R0  | _     | _     | RP32R5  | RP32R4  | RP32R3  | RP32R2  | RP32R1  | RP32R0  | 0000          |

| RPOR1        | 0672  | _      | —      | RP35R5  | RP35R4  | RP35R3  | RP35R2  | RP35R1  | RP35R0  |       | _     | RP34R5  | RP34R4  | RP34R3  | RP34R2  | RP34R1  | RP34R0  | 0000          |

| RPOR2        | 0674  | _      | _      | RP37R5  | RP37R4  | RP37R3  | RP37R2  | RP37R1  | RP37R0  | _     | _     | RP36R5  | RP36R4  | RP36R3  | RP36R2  | RP36R1  | RP36R0  | 0000          |

| RPOR3        | 0676  | _      | _      | RP39R5  | RP39R4  | RP39R3  | RP39R2  | RP39R1  | RP39R0  | _     | _     | RP38R5  | RP38R4  | RP38R3  | RP38R2  | RP38R1  | RP38R0  | 0000          |

| RPOR4        | 0678  | _      | _      | RP41R5  | RP41R4  | RP41R3  | RP41R2  | RP41R1  | RP41R0  | _     | _     | RP40R5  | RP40R4  | RP40R3  | RP40R2  | RP40R1  | RP40R0  | 0000          |

| RPOR5        | 067A  | _      | _      | RP43R5  | RP43R4  | RP43R3  | RP43R2  | RP43R1  | RP43R0  | _     | _     | RP42R5  | RP42R4  | RP42R3  | RP42R2  | RP42R1  | RP42R0  | 0000          |

| RPOR6        | 067C  | _      | _      | RP45R5  | RP45R4  | RP45R3  | RP45R2  | RP45R1  | RP45R0  | _     | _     | RP44R5  | RP44R4  | RP44R3  | RP44R2  | RP44R1  | RP44R0  | 0000          |

| RPOR7        | 067E  | _      | _      | RP47R5  | RP47R4  | RP47R3  | RP47R2  | RP47R1  | RP47R0  | _     | _     | RP46R5  | RP46R4  | RP46R3  | RP46R2  | RP46R1  | RP46R0  | 0000          |

| RPOR8        | 0680  | _      | —      | RP177R5 | RP177R4 | RP177R3 | RP177R2 | RP177R1 | RP177R0 | _     | _     | RP176R5 | RP176R4 | RP176R3 | RP176R2 | RP176R1 | RP176R0 | 0000          |

| RPOR9        | 0682  | _      | —      | RP179R5 | RP179R4 | RP179R3 | RP179R2 | RP179R1 | RP179R0 | _     | _     | RP178R5 | RP178R4 | RP178R3 | RP178R2 | RP178R1 | RP178R0 | 0000          |

| RPOR10       | 0684  | _      | —      | RP181R5 | RP181R4 | RP181R3 | RP181R2 | RP181R1 | RP181R0 | _     | _     | RP180R5 | RP180R4 | RP180R3 | RP180R2 | RP180R1 | RP180R0 | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-16: PERIPHERAL PIN SELECT INPUT REGISTER MAP

| File<br>Name | Addr. | Bit 15   | Bit 14   | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|----------|----------|----------|----------|----------|----------|----------|----------|--------|--------|--------|--------|---------|--------|--------|--------|---------------|

| RPINR0       | 06A0  |          |          |          | INT1R    | <7:0>    |          |          |          | _      | _      | _      |        | _       | -      | _      |        | 0000          |

| RPINR1       | 06A2  | -        | _        | _        | _        | _        | _        | _        | _        |        |        |        | INT2F  | <7:0>   |        |        |        | 0000          |

| RPINR2       | 06A4  |          |          |          | T1CKF    | R<7:0>   |          |          |          | _      | _      | _      | _      | _       | _      | _      | _      | 0000          |

| RPINR3       | 06A6  | T3CKR7   | T3CKR6   | T3CKR5   | T3CKR4   | T3CKR3   | T3CKR2   | T3CKR1   | T3CKR0   | T2CKR7 | T2CKR6 | T2CKR5 | T2CKR4 | T2CKR3  | T2CKR2 | T2CKR1 | T2CKR0 | 0000          |

| RPINR7       | 06AE  | -        | _        | _        | _        | _        | _        | _        | _        |        |        |        | IC1R   | <7:0>   |        |        |        | 0000          |

| RPINR11      | 06B6  | _        | _        | _        | _        | _        | _        | _        | —        |        |        |        | OCFA   | R<7:0>  |        |        |        | 0000          |

| RPINR12      | 06B8  | FLT2R7   | FLT2R6   | FLT2R5   | FLT2R4   | FLT2R3   | FLT2R2   | FLT2R1   | FLT2R0   | FLT1R7 | FLT1R6 | FLT1R5 | FLT1R4 | FLT1R3  | FLT1R2 | FLT1R1 | FLT1R0 | 0000          |

| RPINR13      | 06BA  | FLT4R7   | FLT4R6   | FLT4R5   | FLT4R4   | FLT4R3   | FLT4R2   | FLT4R1   | FLT4R0   | FLT3R7 | FLT3R6 | FLT3R5 | FLT3R4 | FLT3R3  | FLT3R2 | FLT3R1 | FLT3R0 | 0000          |

| RPINR18      | 06C4  | U1CTSR7  | U1CTSR6  | U1CTSR5  | U1CTSR4  | U1CTSR3  | U1CTSR2  | U1CTSR1  | U1CTS0   | U1RXR7 | U1RXR6 | U1RXR5 | U1RXR4 | U1RXR3  | U1RXR2 | U1RXR1 | U1RXR0 | 0000          |

| RPINR20      | 06C8  | SCK1INR7 | SCK1INR6 | SCK1INR5 | SCK1INR4 | SCK1INR3 | SCK1INR2 | SCK1INR1 | SCK1INR0 | SDI1R7 | SDI1R6 | SDI1R5 | SDI1R4 | SDI1R3  | SDI1R2 | SDI1R1 | SDI1R0 | 0000          |

| RPINR21      | 06CA  | _        | _        | _        | _        | _        | _        | _        | —        |        |        |        | SS1R   | <7:0>   |        |        |        | 0000          |

| RPINR37      | 06EA  |          |          |          | SYNCI1   | R<7:0>   |          |          |          | _      | _      | _      | _      | _       | _      | _      | _      | 0000          |

| RPINR38      | 06EC  | _        | —        | _        | _        | _        | _        | _        | —        |        |        |        | SYNCI2 | 2R<7:0> |        |        |        | 0000          |

| RPINR42      | 06F4  | FLT6R7   | FLT6R6   | FLT6R5   | FLT6R4   | FLT6R3   | FLT6R2   | FLT6R1   | FLT6R0   | FLT5R7 | FLT5R6 | FLT5R5 | FLT5R4 | FLT5R3  | FLT5R2 | FLT5R1 | FLT5R0 | 0000          |

| RPINR43      | 06F6  | FLT8R7   | FLT8R6   | FLT8R5   | FLT8R4   | FLT8R3   | FLT8R2   | FLT8R1   | FLT8R0   | FLT7R7 | FLT7R6 | FLT7R5 | FLT7R4 | FLT7R3  | FLT7R2 | FLT7R1 | FLT7R0 | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## **REGISTER 8-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

- bit 4 Unimplemented: Read as '0'

- bit 3 **CF:** Clock Fail Detect bit<sup>(3)</sup>

- 1 = FSCM has detected a clock failure

- 0 = FSCM has not detected a clock failure

- bit 2-1 Unimplemented: Read as '0'

- bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Requests oscillator switch to selection specified by the NOSC<2:0> bits

- 0 = Oscillator switch is complete

- **Note 1:** Writes to this register require an unlock sequence.

- 2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- **3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

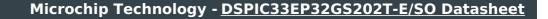

## 10.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "I/O Ports" (DS70000598) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Many of the device pins are shared among the peripherals and the Parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

## 10.1 Parallel I/O (PIO) Ports

Generally, a Parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 10-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have eight registers directly associated with their operation as digital I/Os. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx), read the latch. Writes to the latch, write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device are disabled. This means the corresponding LATx and TRISx registers, and the port pin are read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

#### FIGURE 10-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

© 2015-2016 Microchip Technology Inc.

## 10.5 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 25-11 under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device, that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD - 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristics specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the Absolute Maximum Ratings in **Section 25.0 "Electrical Characteristics"**of this data sheet. For example:

VOH = 2.4V @ IOH = -8 mA and VDD = 3.3VThe maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted.

| R/W-0             | R/W-0                                    | R/W-0                                                                       | R/W-0             | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

|-------------------|------------------------------------------|-----------------------------------------------------------------------------|-------------------|-------------------|------------------|-----------------|--------|

| T3CKR7            | T3CKR6                                   | T3CKR5                                                                      | T3CKR4            | T3CKR3            | T3CKR2           | T3CKR1          | T3CKR0 |

| bit 15            |                                          |                                                                             | ·                 |                   |                  |                 | bit 8  |

| R/W-0             | R/W-0                                    | R/W-0                                                                       | R/W-0             | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

| T2CKR7            | T2CKR6                                   | T2CKR5                                                                      | T2CKR4            | T2CKR3            | T2CKR2           | T2CKR1          | T2CKR0 |

| bit 7             |                                          |                                                                             |                   |                   |                  |                 | bit C  |

| Legend:           |                                          |                                                                             |                   |                   |                  |                 |        |

| R = Readable      | bit                                      | W = Writable                                                                | bit               | U = Unimplen      | nented bit, read | d as '0'        |        |

| -n = Value at POR |                                          | '1' = Bit is set                                                            |                   | '0' = Bit is clea | ared             | x = Bit is unkr | nown   |

|                   | 10110101 =                               | 0                                                                           |                   |                   | ne Correspondi   |                 | ò      |

|                   | 10110100 =<br>•<br>•<br>•<br>•<br>•<br>• | Input tied to RI<br>Input tied to RI<br>nput tied to RP<br>nput tied to Vss | ⊃181<br>⊃180<br>1 |                   | ie Correspondi   |                 | 5      |

#### REGISTER 10-4: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0           |

|--------|-----|--------|--------|--------|--------|--------|-----------------|

| _      | —   | RP41R5 | RP41R4 | RP41R3 | RP41R2 | RP41R1 | RP41R0          |

| bit 15 |     |        |        |        |        |        | bit 8           |

|        |     |        |        |        |        |        |                 |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0           |

|        | 00  |        |        |        | -      |        | -               |

| _      | -   | RP40R5 | RP40R4 | RP40R3 | RP40R2 | RP40R1 | RP40R0          |

|        | -   |        | RP40R4 | RP40R3 | RP40R2 | RP40R1 | RP40R0<br>bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP41R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP41 Output Pin bits (see Table 10-2 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP40R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP40 Output Pin bits (see Table 10-2 for peripheral function numbers) |

#### REGISTER 10-21: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP43R5 | RP43R4 | RP43R3 | RP43R2 | RP43R1 | RP43R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP42R5 | RP42R4 | RP42R3 | RP42R2 | RP42R1 | RP42R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8**RP43R<5:0>:** Peripheral Output Function is Assigned to RP43 Output Pin bits<br/>(see Table 10-2 for peripheral function numbers)bit 7-6**Unimplemented:** Read as '0'

bit 5-0 **RP42R<5:0>:** Peripheral Output Function is Assigned to RP42 Output Pin bits (see Table 10-2 for peripheral function numbers)

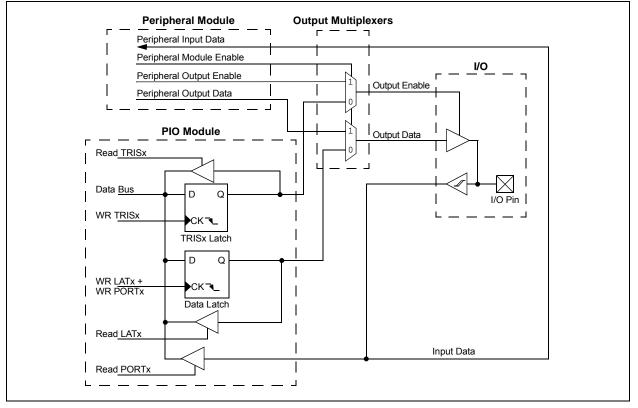

## 14.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Output Compare with Dedicated Timer" (DS70005159) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The output compare module can select one of four available clock sources for its time base. The module compares the value of the timer with the value of one or two Compare registers, depending on the operating mode selected. The state of the output pin changes when the timer value matches the Compare register value. The output compare module generates either a single output pulse, or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events.

## 14.1 Output Compare Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 14.1.1 KEY RESOURCES

- "Output Compare with Dedicated Timer" (DS70005159) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

#### FIGURE 14-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

### REGISTER 14-2: OC1CON2: OUTPUT COMPARE CONTROL REGISTER 2

| R/W-0         | R/W-0                                                                                                                                           | R/W-0             | R/W-0                             | U-0               | U-0              | U-0             | U-0           |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------|-------------------|------------------|-----------------|---------------|--|--|--|

| FLTMD         | FLTOUT                                                                                                                                          | FLTTRIEN          | OCINV                             | _                 | _                | _               | _             |  |  |  |

| bit 15        |                                                                                                                                                 |                   |                                   |                   |                  |                 | bit 8         |  |  |  |

|               |                                                                                                                                                 |                   |                                   |                   |                  |                 |               |  |  |  |

| R/W-0         | R/W-0, HS                                                                                                                                       | R/W-0             | R/W-0                             | R/W-1             | R/W-0            |                 |               |  |  |  |

| OCTRIG        | G TRIGSTAT OCTRIS SYNCSEL4 SYNCSEL3 SYNCSEL2 SYNCSEL1 SY                                                                                        |                   |                                   |                   |                  |                 |               |  |  |  |

| bit 7 k       |                                                                                                                                                 |                   |                                   |                   |                  |                 |               |  |  |  |

|               |                                                                                                                                                 |                   |                                   |                   |                  |                 |               |  |  |  |

| Legend:       |                                                                                                                                                 |                   | re Settable bit                   |                   |                  |                 |               |  |  |  |

| R = Readable  |                                                                                                                                                 | W = Writable      |                                   | -                 | nented bit, read |                 |               |  |  |  |

| -n = Value at | POR                                                                                                                                             | '1' = Bit is set  |                                   | '0' = Bit is clea | ared             | x = Bit is unkr | iown          |  |  |  |

| bit 15        |                                                                                                                                                 | t Mode Select t   | .it                               |                   |                  |                 |               |  |  |  |

| DIL 15        |                                                                                                                                                 |                   |                                   | ult source is r   | emoved; the c    | orresponding    | OCELTA hit is |  |  |  |

|               |                                                                                                                                                 |                   | a new PWM pe                      |                   | enioved, the c   |                 |               |  |  |  |

|               |                                                                                                                                                 |                   |                                   |                   | noved and a ne   | w PWM period    | starts        |  |  |  |

| bit 14        | FLTOUT: Fau                                                                                                                                     | lt Out bit        |                                   |                   |                  |                 |               |  |  |  |

|               |                                                                                                                                                 | put is driven hi  |                                   |                   |                  |                 |               |  |  |  |

| 1:140         |                                                                                                                                                 | put is driven lo  |                                   |                   |                  |                 |               |  |  |  |

| bit 13        |                                                                                                                                                 | ault Output Sta   | te Select bit<br>a Fault conditic |                   |                  |                 |               |  |  |  |

|               |                                                                                                                                                 |                   | ned by the FLT                    |                   | ault condition   |                 |               |  |  |  |

| bit 12        | -                                                                                                                                               | ut Compare Inv    | •                                 |                   |                  |                 |               |  |  |  |

|               | 1 = OC1 outp                                                                                                                                    | •                 |                                   |                   |                  |                 |               |  |  |  |

|               | 0 = OC1 outp                                                                                                                                    | out is not invert | ed                                |                   |                  |                 |               |  |  |  |

| bit 11-8      | Unimplemen                                                                                                                                      | ted: Read as '    | כי                                |                   |                  |                 |               |  |  |  |

| bit 7         |                                                                                                                                                 |                   | rigger/Sync Se                    |                   |                  |                 |               |  |  |  |

|               | 00                                                                                                                                              |                   | •                                 |                   | ICSEL<4:0> bit   |                 |               |  |  |  |

| h# 0          | 0 = Synchronizes OC1 with the source designated by the SYNCSEL<4:0> bits                                                                        |                   |                                   |                   |                  |                 |               |  |  |  |

| bit 6         | TRIGSTAT: Timer Trigger Status bit                                                                                                              |                   |                                   |                   |                  |                 |               |  |  |  |

|               | <ul> <li>1 = Timer source has been triggered and is running</li> <li>0 = Timer source has not been triggered and is being held clear</li> </ul> |                   |                                   |                   |                  |                 |               |  |  |  |

| bit 5         |                                                                                                                                                 |                   | Output Pin Direc                  | •                 |                  |                 |               |  |  |  |

| · · · ·       |                                                                                                                                                 | ompare is tri-sta | -                                 |                   |                  |                 |               |  |  |  |

|               | 0 = Output compare module drives the OCx pin                                                                                                    |                   |                                   |                   |                  |                 |               |  |  |  |

|               |                                                                                                                                                 |                   |                                   |                   |                  |                 |               |  |  |  |

**Note 1:** This option should only be selected as a trigger source and not as a synchronization source.

## **REGISTER 19-11:** ADCOREXL: DEDICATED ADC CORE x CONTROL REGISTER LOW (x = 0,1)

|              |          |                   |              |                   |                | •                     |               |

|--------------|----------|-------------------|--------------|-------------------|----------------|-----------------------|---------------|

| U-0          | U-0      | U-0               | U-0          | U-0               | U-0            | R/W-0                 | R/W-0         |

| _            | _        | —                 | _            | —                 |                | SAMC<                 | 9:8>          |

| bit 15       |          |                   |              | •                 |                |                       | bit 8         |

|              |          |                   |              |                   |                |                       |               |

| R/W-0        | R/W-0    | R/W-0             | R/W-0        | R/W-0             | R/W-0          | R/W-0                 | R/W-0         |

|              |          |                   | SA           | MC<7:0>           |                |                       |               |

| bit 7        |          |                   |              |                   |                |                       | bit 0         |

|              |          |                   |              |                   |                |                       |               |

| Legend:      |          |                   |              |                   |                |                       |               |

| R = Readal   | ble bit  | W = Writable bit  |              | U = Unimplem      | ented bit, rea | d as '0'              |               |

| -n = Value a | at POR   | '1' = Bit is set  |              | '0' = Bit is clea | ared           | x = Bit is unknow     | /n            |

| bit 15-10    | Unimplem | ented: Read as '0 | ,            |                   |                |                       |               |

|              | •        |                   |              |                   | alaatian hita  |                       |               |

| bit 9-0      |          | D>: Dedicated ADC |              | ,                 |                |                       |               |

|              |          |                   |              |                   |                | f conversion in the r |               |

|              | ADC Core | Clock (TADCORE)   | periods. Dur | ing this time, th | ne ADC Core    | x still continues sa  | ampling. This |

0000000000 = 2 TADCORE

DS70005208D-page 212

### REGISTER 19-13: ADLVLTRGL: ADC LEVEL-SENSITIVE TRIGGER CONTROL REGISTER LOW

| U-0          | R/W-0                                          | U-0                                           | U-0               | R/W-0             | R/W-0           | R/W-0            | R/W-0 |  |  |  |

|--------------|------------------------------------------------|-----------------------------------------------|-------------------|-------------------|-----------------|------------------|-------|--|--|--|

| _            | LVLEN14                                        | —                                             | —                 | LVLEN<11:8>       |                 |                  |       |  |  |  |

| bit 15       |                                                |                                               |                   |                   |                 |                  | bit 8 |  |  |  |

|              |                                                |                                               |                   |                   |                 |                  |       |  |  |  |

| R/W-0        | R/W-0                                          | R/W-0                                         | R/W-0             | R/W-0             | R/W-0           | R/W-0            | R/W-0 |  |  |  |

|              |                                                |                                               | LVL               | .EN<7:0>          |                 |                  |       |  |  |  |

| bit 7        |                                                |                                               |                   |                   |                 |                  | bit 0 |  |  |  |

|              |                                                |                                               |                   |                   |                 |                  |       |  |  |  |

| Legend:      |                                                |                                               |                   |                   |                 |                  |       |  |  |  |

| R = Readab   | ole bit                                        | W = Writable                                  | bit               | U = Unimplem      | nented bit, rea | d as '0'         |       |  |  |  |

| -n = Value a | at POR                                         | '1' = Bit is set                              |                   | '0' = Bit is clea | ared            | x = Bit is unkno | wn    |  |  |  |

|              |                                                |                                               |                   |                   |                 |                  |       |  |  |  |

| bit 15       | Unimpleme                                      | nted: Read as                                 | '0'               |                   |                 |                  |       |  |  |  |

| bit 14       | LVLEN14: L                                     | evel Trigger 14                               | Enable bit        |                   |                 |                  |       |  |  |  |

|              | 1 = Input Ch                                   | annel 14 trigge                               | er is level-sensi | tive              |                 |                  |       |  |  |  |

|              | 0 = Input Ch                                   | annel 14 trigge                               | er is edge-sensi  | itive             |                 |                  |       |  |  |  |

| bit 13-12    | Unimpleme                                      | nted: Read as                                 | '0'               |                   |                 |                  |       |  |  |  |

| bit 11-0     | LVLEN<11:0                                     | >: Level Trigg                                | er x Enable bits  | 3                 |                 |                  |       |  |  |  |

|              | 1 = Input Channel x trigger is level-sensitive |                                               |                   |                   |                 |                  |       |  |  |  |

|              | 0 = Input Ch                                   | 0 = Input Channel x trigger is edge-sensitive |                   |                   |                 |                  |       |  |  |  |

|              |                                                |                                               |                   |                   |                 |                  |       |  |  |  |

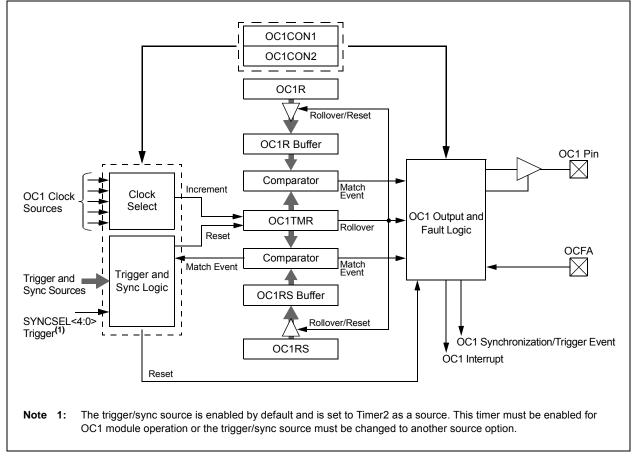

The different device security segments are shown in Figure 22-3. Here, all three segments are shown but are not required. If only basic code protection is required, then the GS can be enabled independently or combined with the CS if desired.

#### FIGURE 22-3:

#### dsPIC33EPXXGS202 SECURITY SEGMENTS EXAMPLE

| Base<br>Instr<br># | Assembly<br>Mnemonic |         | Assembly Syntax             | Description                                       | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|---------|-----------------------------|---------------------------------------------------|---------------|----------------|--------------------------|

| 47                 | MAC                  | MAC     | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd,AWB | Multiply and Accumulate                           | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | MAC     | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd     | Square and Accumulate                             | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 48                 | MOV                  | MOV     | f,Wn                        | Move f to Wn                                      | 1             | 1              | None                     |

|                    |                      | MOV     | f                           | Move f to f                                       | 1             | 1              | None                     |

|                    |                      | MOV     | f,WREG                      | Move f to WREG                                    | 1             | 1              | None                     |

|                    |                      | MOV     | #lit16,Wn                   | Move 16-bit literal to Wn                         | 1             | 1              | None                     |

|                    |                      | MOV.b   | #lit8,Wn                    | Move 8-bit literal to Wn                          | 1             | 1              | None                     |

|                    |                      | MOV     | Wn,f                        | Move Wn to f                                      | 1             | 1              | None                     |

|                    |                      | MOV     | Wso,Wdo                     | Move Ws to Wd                                     | 1             | 1              | None                     |

|                    |                      | MOV     | WREG, f                     | Move WREG to f                                    | 1             | 1              | None                     |

|                    |                      | MOV.D   | Wns,Wd                      | Move Double from W(ns):W(ns + 1) to Wd            | 1             | 2              | None                     |

|                    |                      | MOV.D   | Ws,Wnd                      | Move Double from Ws to<br>W(nd + 1):W(nd)         | 1             | 2              | None                     |

| 49                 | MOVPAG               | MOVPAG  | #lit10,DSRPAG               | Move 10-bit literal to DSRPAG                     | 1             | 1              | None                     |

|                    |                      | MOVPAG  | #lit8,TBLPAG                | Move 8-bit literal to TBLPAG                      | 1             | 1              | None                     |

|                    |                      | MOVPAGW | Ws, DSRPAG                  | Move Ws<9:0> to DSRPAG                            | 1             | 1              | None                     |

|                    |                      | MOVPAGW | Ws, TBLPAG                  | Move Ws<7:0> to TBLPAG                            | 1             | 1              | None                     |

| 50                 | MOVSAC               | MOVSAC  | Acc,Wx,Wxd,Wy,Wyd,AWB       | Prefetch and store accumulator                    | 1             | 1              | None                     |

| 51                 | MPY                  | MPY     | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd     | Multiply Wm by Wn to Accumulator                  | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | MPY     | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd     | Square Wm to Accumulator                          | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 52                 | MPY.N                | MPY.N   | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd     | -(Multiply Wm by Wn) to Accumulator               | 1             | 1              | None                     |

| 53                 | MSC                  | MSC     | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd,AWB | Multiply and Subtract from Accumulator            | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 54                 | MUL                  | MUL.SS  | Wb,Ws,Wnd                   | {Wnd + 1, Wnd} = signed(Wb) * signed(Ws)          | 1             | 1              | None                     |

|                    |                      | MUL.SS  | Wb,Ws,Acc                   | Accumulator = signed(Wb) * signed(Ws)             | 1             | 1              | None                     |

|                    |                      | MUL.SU  | Wb,Ws,Wnd                   | {Wnd + 1, Wnd} = signed(Wb) * unsigned(Ws)        | 1             | 1              | None                     |

|                    |                      | MUL.SU  | Wb,Ws,Acc                   | Accumulator = signed(Wb) * unsigned(Ws)           | 1             | 1              | None                     |

|                    |                      | MUL.SU  | Wb,#lit5,Acc                | Accumulator = signed(Wb) * unsigned(lit5)         | 1             | 1              | None                     |

|                    |                      | MUL.US  | Wb,Ws,Wnd                   | {Wnd + 1, Wnd} = unsigned(Wb) * signed(Ws)        | 1             | 1              | None                     |

|                    |                      | MUL.US  | Wb,Ws,Acc                   | Accumulator = unsigned(Wb) * signed(Ws)           | 1             | 1              | None                     |

|                    |                      | MUL.UU  | Wb,Ws,Wnd                   | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(Ws)   | 1             | 1              | None                     |

|                    |                      | MUL.UU  | Wb,#lit5,Acc                | Accumulator = unsigned(Wb) *<br>unsigned(lit5)    | 1             | 1              | None                     |

|                    |                      | MUL.UU  | Wb,Ws,Acc                   | Accumulator = unsigned(Wb) *<br>unsigned(Ws)      | 1             | 1              | None                     |

|                    |                      | MULW.SS | Wb,Ws,Wnd                   | Wnd = signed(Wb) * signed(Ws)                     | 1             | 1              | None                     |

|                    |                      | MULW.SU | Wb,Ws,Wnd                   | Wnd = signed(Wb) * unsigned(Ws)                   | 1             | 1              | None                     |

|                    |                      | MULW.US | Wb,Ws,Wnd                   | Wnd = unsigned(Wb) * signed(Ws)                   | 1             | 1              | None                     |

|                    |                      | MULW.UU | Wb,Ws,Wnd                   | Wnd = unsigned(Wb) * unsigned(Ws)                 | 1             | 1              | None                     |

|                    |                      | MUL.SU  | Wb,#lit5,Wnd                | {Wnd + 1, Wnd} = signed(Wb) *<br>unsigned(lit5)   | 1             | 1              | None                     |

|                    |                      | MUL.SU  | Wb,#lit5,Wnd                | Wnd = signed(Wb) * unsigned(lit5)                 | 1             | 1              | None                     |

|                    |                      | MUL.UU  | Wb,#lit5,Wnd                | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(lit5) | 1             | 1              | None                     |

|                    |                      | MUL.UU  | Wb,#lit5,Wnd                | Wnd = unsigned(Wb) * unsigned(lit5)               | 1             | 1              | None                     |

|                    |                      | MUL     | f                           | W3:W2 = f * WREG                                  | 1             | 1              | None                     |

#### TABLE 23-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

### 24.11 Demonstration/Development Boards, Evaluation Kits and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 24.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

#### TABLE 25-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

| DC CH        | ARACTE | RISTICS                                                       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                     |         |            |                        |  |

|--------------|--------|---------------------------------------------------------------|------------------------------------------------------|---------------------|---------|------------|------------------------|--|

| Param<br>No. | Symbol | Characteristic                                                | Min.                                                 | Тур. <sup>(1)</sup> | Max.    | Conditions |                        |  |

|              | VIL    | Input Low Voltage                                             |                                                      |                     |         |            |                        |  |

| DI10         |        | Any I/O Pin and MCLR                                          | Vss                                                  | —                   | 0.2 Vdd | V          |                        |  |

| DI18         |        | I/O Pins with SDA1, SCL1                                      | Vss                                                  | —                   | 0.3 Vdd | V          | SMBus disabled         |  |

| DI19         |        | I/O Pins with SDA1, SCL1                                      | Vss                                                  | —                   | 0.8     | V          | SMBus enabled          |  |

|              | Vih    | Input High Voltage                                            |                                                      |                     |         |            |                        |  |

| DI20         |        | I/O Pins Not 5V Tolerant <sup>(4)</sup>                       | 0.8 Vdd                                              | —                   | Vdd     | V          |                        |  |

|              |        | I/O Pins 5V Tolerant and MCLR <sup>(4)</sup>                  | 0.8 VDD                                              | —                   | 5.5     | V          |                        |  |

|              |        | 5V Tolerant I/O Pins with SDA1, SCL1 <sup>(4)</sup>           | 0.8 Vdd                                              | —                   | 5.5     | V          | SMBus disabled         |  |

|              |        | 5V I/O Pins with SDA1, SCL1 <sup>(4)</sup>                    | 2.1                                                  | —                   | 5.5     | V          | SMBus enabled          |  |

|              |        | I/O Pins with SDA1, SCL1 Not<br>5V Tolerant <sup>(4)</sup>    | 0.8 Vdd                                              | —                   | Vdd     | V          | SMBus disabled         |  |

|              |        | I/O Pins with SDA1, SCL1 Not<br>5V Tolerant <sup>(4)</sup>    | 2.1                                                  | —                   | Vdd     | V          | SMBus enabled          |  |

| DI30         | ICNPU  | Input Change Notification<br>Pull-up Current                  | 50                                                   | 250                 | 600     | μA         | VDD = 3.3V, VPIN = VSS |  |

| DI31         | ICNPD  | Input Change Notification<br>Pull-Down Current <sup>(5)</sup> | —                                                    | 50                  |         | μA         | VDD = 3.3V, VPIN = VDD |  |

**Note 1:** Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

- 4: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 5: VIL Source < (Vss 0.3). Characterized but not tested.

- **6:** VIH source > (VDD + 0.3) for non-5V tolerant pins only.

- 7: Digital 5V tolerant pins do not have an internal high side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

- 8: |Injection Currents| > 0 can affect the ADC results by approximately 4-6 counts.

- **9:** Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted, provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

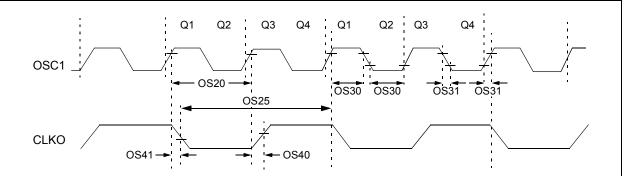

### FIGURE 25-2: EXTERNAL CLOCK TIMING

| АС СНА       | AC CHARACTERISTICS |                                                                                    |             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |             |            |                               |  |  |  |

|--------------|--------------------|------------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|-------------------------------|--|--|--|

| Param<br>No. | Symb               | Characteristic                                                                     | Min.        | Тур. <sup>(1)</sup>                                                                                                                                                                                                                                                                     | Max.        | Units      | Conditions                    |  |  |  |

| OS10         | Fin                | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC          | —                                                                                                                                                                                                                                                                                       | 60          | MHz        | EC                            |  |  |  |

|              |                    | Oscillator Crystal Frequency                                                       | 3.5<br>10   | _                                                                                                                                                                                                                                                                                       | 10<br>40    | MHz<br>MHz | XT<br>HS                      |  |  |  |

| OS20         | Tosc               | Tosc = 1/Fosc                                                                      | 8.33        |                                                                                                                                                                                                                                                                                         | DC          | ns         | +125°C                        |  |  |  |

|              |                    | Tosc = 1/Fosc                                                                      | 7.14        |                                                                                                                                                                                                                                                                                         | DC          | ns         | +85°C                         |  |  |  |

| OS25         | Тсү                | Instruction Cycle Time <sup>(2)</sup>                                              | 16.67       |                                                                                                                                                                                                                                                                                         | DC          | ns         | +125°C                        |  |  |  |

|              |                    | Instruction Cycle Time <sup>(2)</sup>                                              | 14.28       |                                                                                                                                                                                                                                                                                         | DC          | ns         | +85°C                         |  |  |  |

| OS30         | TosL,<br>TosH      | External Clock in (OSC1)<br>High or Low Time                                       | 0.45 x Tosc | —                                                                                                                                                                                                                                                                                       | 0.55 x Tosc | ns         | EC                            |  |  |  |

| OS31         | TosR,<br>TosF      | External Clock in (OSC1)<br>Rise or Fall Time                                      | _           | —                                                                                                                                                                                                                                                                                       | 20          | ns         | EC                            |  |  |  |

| OS40         | TckR               | CLKO Rise Time <sup>(3,4)</sup>                                                    | _           | 5.2                                                                                                                                                                                                                                                                                     |             | ns         |                               |  |  |  |

| OS41         | TckF               | CLKO Fall Time <sup>(3,4)</sup>                                                    | _           | 5.2                                                                                                                                                                                                                                                                                     | _           | ns         |                               |  |  |  |

| OS42         | Gм                 | External Oscillator<br>Transconductance <sup>(4)</sup>                             | —           | 12                                                                                                                                                                                                                                                                                      | _           | mA/V       | HS, VDD = 3.3V,<br>TA = +25°C |  |  |  |

|              |                    |                                                                                    | _           | 6                                                                                                                                                                                                                                                                                       | —           | mA/V       | XT, VDD = 3.3V,<br>TA = +25°C |  |  |  |

#### TABLE 25-17: EXTERNAL CLOCK TIMING REQUIREMENTS

Note 1: Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

2: Instruction cycle period (TCY) equals two times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type, under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Minimum" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "Maximum" cycle time limit is "DC" (no clock) for all devices.

- 3: Measurements are taken in EC mode. The CLKO signal is measured on the OSC2 pin.