Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XF

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 2K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C                                                                     |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gs202t-i-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

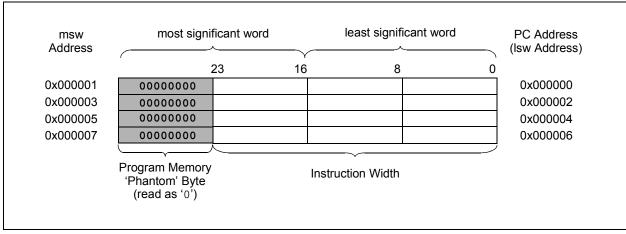

#### 4.2.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-3).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented, or decremented, by two during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

# 4.2.2 INTERRUPT AND TRAP VECTORS

All dsPIC33EPXXGS202 family devices reserve the addresses between 0x000000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address, 0x000000, of Flash memory, with the actual address for the start of code at address, 0x000002, of Flash memory.

A more detailed discussion of the Interrupt Vector Tables (IVTs) is provided in **Section 7.1** "Interrupt Vector Table".

#### FIGURE 4-3: PROGRAM MEMORY ORGANIZATION

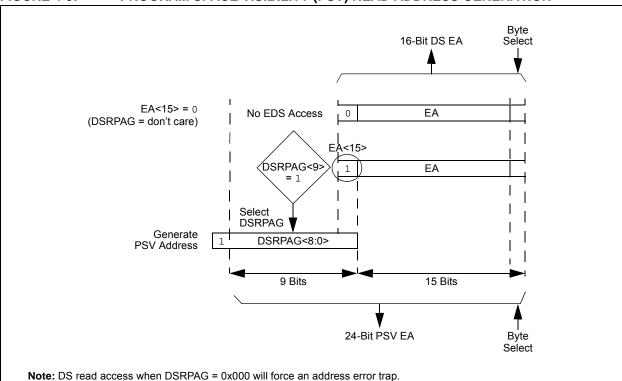

### 4.5.1 PAGED MEMORY SCHEME

The dsPIC33EPXXGS202 architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre- and post-modified Effective Addresses (EAs). The upper half of the base Data Space address is used in conjunction with the Data Space Read Page (DSRPAG) register to form the Program Space Visibility (PSV) address.

The Data Space Read Page (DSRPAG) register is located in the SFR space. Construction of the PSV address is shown in Figure 4-5. When DSRPAG<9> = 1 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit PSV read address. The paged memory scheme provides access to multiple 32-Kbyte windows in the PSV memory. The Data Space Read Page register (DSRPAG), in combination with the upper half of the Data Space address, can provide up to 8 Mbytes of PSV address space. The paged data memory space is shown in Figure 4-6.

The Program Space (PS) can be accessed with a DSRPAG of 0x200 or greater. Only reads from PS are supported using the DSRPAG.

#### FIGURE 4-5: PROGRAM SPACE VISIBILITY (PSV) READ ADDRESS GENERATION

NOTES:

# **REGISTER 7-1:** SR: CPU STATUS REGISTER<sup>(1)</sup>

| R/W-0                | R/W-0                | R/W-0                | R/W-0 | R/C-0 | R/C-0 | R-0   | R/W-0 |

|----------------------|----------------------|----------------------|-------|-------|-------|-------|-------|

| OA                   | OB                   | SA                   | SB    | OAB   | SAB   | DA    | DC    |

| bit 15               |                      | •                    |       |       |       |       | bit 8 |

|                      |                      |                      |       |       |       |       |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA    | N     | OV    | Z     | С     |

| bit 7                | •                    | •                    |       | •     |       |       | bit 0 |

|                      |                      |                      |       |       |       |       |       |

| Legend:           | C = Clearable bit |                             |                    |

|-------------------|-------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2,3)</sup> 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled 110 = CPU Interrupt Priority Level is 6 (14) 101 = CPU Interrupt Priority Level is 5 (13) 100 = CPU Interrupt Priority Level is 4 (12) 011 = CPU Interrupt Priority Level is 3 (11) 010 = CPU Interrupt Priority Level is 2 (10) 001 = CPU Interrupt Priority Level is 2 (10)

- 001 = CPU Interrupt Priority Level is 1 (9)

- 000 = CPU Interrupt Priority Level is 0 (8)

**Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

# TABLE 8-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

| Oscillator Mode                                            | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Notes |

|------------------------------------------------------------|-------------------|-------------|------------|--------------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)              | Internal          | xx          | 111        | 1, 2         |

| Fast RC Oscillator with Divide-by-16                       | Internal          | xx          | 110        | 1            |

| Low-Power RC Oscillator (LPRC)                             | Internal          | xx          | 101        | 1            |

| Primary Oscillator (HS) with PLL (HSPLL)                   | Primary           | 10          | 011        |              |

| Primary Oscillator (XT) with PLL (XTPLL)                   | Primary           | 01          | 011        |              |

| Primary Oscillator (EC) with PLL (ECPLL)                   | Primary           | 0.0         | 011        | 1            |

| Primary Oscillator (HS)                                    | Primary           | 10          | 010        |              |

| Primary Oscillator (XT)                                    | Primary           | 01          | 010        |              |

| Primary Oscillator (EC)                                    | Primary           | 00          | 010        | 1            |

| Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL) | Internal          | XX          | 001        | 1            |

| Fast RC Oscillator (FRC)                                   | Internal          | xx          | 000        | 1            |

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

### 8.2 Auxiliary Clock Generation

The auxiliary clock generation is used for peripherals that need to operate at a frequency unrelated to the system clock, such as PWM or ADC.

The primary oscillator and internal FRC oscillator sources can be used with an Auxiliary PLL (APLL) to obtain the auxiliary clock. The Auxiliary PLL has a fixed 16x multiplication factor.

The auxiliary clock has the following configuration restrictions:

- For proper PWM operation, auxiliary clock generation must be configured for 120 MHz (see Parameter OS56 in Section 25.0 "Electrical Characteristics"). If a slower frequency is desired, the PWM Input Clock Prescaler (Divider) Select bits (PCLKDIV<2:0>) should be used.

- To achieve 1.04 ns PWM resolution, the auxiliary clock must use the 16x Auxiliary PLL (APLL). All other clock sources will have a minimum PWM resolution of 8 ns.

- If the primary PLL is used as a source for the auxiliary clock, the primary PLL should be configured up to a maximum operation of 30 MIPS or less.

# 8.3 Oscillator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 8.3.1 KEY RESOURCES

- "Oscillator Module" (DS70005131) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

# **REGISTER 8-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

- bit 4 Unimplemented: Read as '0'

- bit 3 **CF:** Clock Fail Detect bit<sup>(3)</sup>

- 1 = FSCM has detected a clock failure

- 0 = FSCM has not detected a clock failure

- bit 2-1 Unimplemented: Read as '0'

- bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Requests oscillator switch to selection specified by the NOSC<2:0> bits

- 0 = Oscillator switch is complete

- **Note 1:** Writes to this register require an unlock sequence.

- 2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- **3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

NOTES:

| R/W-0         | R/W-0                                            | R/W-0                                                                                                            | R/W-0                              | R/W-0                | R/W-0            | R/W-0              | R/W-0  |

|---------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------|------------------|--------------------|--------|

| FLT4R7        | FLT4R6                                           | FLT4R5                                                                                                           | FLT4R4                             | FLT4R3               | FLT4R2           | FLT4R1             | FLT4R0 |

| bit 15        |                                                  |                                                                                                                  |                                    |                      |                  |                    | bit 8  |

|               |                                                  |                                                                                                                  |                                    |                      |                  |                    |        |

| R/W-0         | R/W-0                                            | R/W-0                                                                                                            | R/W-0                              | R/W-0                | R/W-0            | R/W-0              | R/W-0  |

| FLT3R7        | FLT3R6                                           | FLT3R5                                                                                                           | FLT3R4                             | FLT3R3               | FLT3R2           | FLT3R1             | FLT3R0 |

| bit 7         |                                                  |                                                                                                                  |                                    |                      |                  |                    | bit (  |

| Legend:       |                                                  |                                                                                                                  |                                    |                      |                  |                    |        |

| R = Readable  | e bit                                            | W = Writable                                                                                                     | bit                                | U = Unimpler         | nented bit, read | d as '0'           |        |

| -n = Value at | POR                                              | '1' = Bit is set                                                                                                 |                                    | '0' = Bit is cleared |                  | x = Bit is unknown |        |

| bit 7-0       | 10110100 =<br>•<br>•<br>00000000 =<br>FLT3R<7:0> | Input tied to RI<br>Input tied to RI<br>Input tied to RI<br>Input tied to Vs<br>: Assign PWM<br>Input tied to RI | ⊃180<br>⊃1<br>SS<br>Fault 3 (FLT3) | to the Corresp       | ponding RPn Pi   | in bits            |        |

|               | 10110100 =<br>•<br>•<br>•<br>00000001 =          | Input tied to RI<br>Input tied to RI<br>Input tied to RI                                                         | ⊃180<br>⊃1                         |                      |                  |                    |        |

### REGISTER 10-8: RPINR13: PERIPHERAL PIN SELECT INPUT REGISTER 13

# REGISTER 10-13: RPINR38: PERIPHERAL PIN SELECT INPUT REGISTER 38

| U-0                | U-0                            | U-0                     | U-0          | U-0                                | U-0           | U-0                | U-0   |  |

|--------------------|--------------------------------|-------------------------|--------------|------------------------------------|---------------|--------------------|-------|--|

| _                  | —                              | —                       | —            | —                                  | —             | —                  | —     |  |

| bit 15             |                                |                         |              |                                    |               |                    | bit 8 |  |

|                    |                                |                         |              |                                    |               |                    |       |  |

| R/W-0              | R/W-0                          | R/W-0                   | R/W-0        | R/W-0                              | R/W-0         | R/W-0              | R/W-0 |  |

|                    |                                |                         | SYNCI        | 2R<7:0>                            |               |                    |       |  |

| bit 7              |                                |                         |              |                                    |               |                    | bit 0 |  |

|                    |                                |                         |              |                                    |               |                    |       |  |

| Legend:            |                                |                         |              |                                    |               |                    |       |  |

| R = Readable bit W |                                | W = Writable            | bit          | U = Unimplemented bit, read as '0' |               |                    |       |  |

| -n = Value at      | POR                            | '1' = Bit is set        |              | '0' = Bit is cleared               |               | x = Bit is unknown |       |  |

|                    |                                |                         |              |                                    |               |                    |       |  |

| bit 15-8           | Unimplemen                     | ted: Read as '          | כ'           |                                    |               |                    |       |  |

| bit 7-0            | SYNCI2R<7:                     | <b>0&gt;:</b> Assign PW | M Synchroniz | ation Input 2 to                   | the Correspon | ding RPn Pin b     | oits  |  |

|                    | 10110101 = Input tied to RP181 |                         |              |                                    |               |                    |       |  |

|                    | 10110100 = Input tied to RP180 |                         |              |                                    |               |                    |       |  |

|                    | •                              |                         |              |                                    |               |                    |       |  |

|                    | •                              |                         |              |                                    |               |                    |       |  |

|                    | •                              |                         |              |                                    |               |                    |       |  |

|                    | 0000001=                       | Input tied to RF        | P1           |                                    |               |                    |       |  |

|                    | 00000000 =                     | Input tied to Vs        | S            |                                    |               |                    |       |  |

|                    |                                |                         |              |                                    |               |                    |       |  |

#### REGISTER 15-5: STCON: PWM SECONDARY MASTER TIME BASE CONTROL REGISTER

| U-0             | U-0                                                      | U-0              | HS/HC-0                                  | R/W-0            | R/W-0               | R/W-0          | R/W-0   |

|-----------------|----------------------------------------------------------|------------------|------------------------------------------|------------------|---------------------|----------------|---------|

|                 |                                                          | _                | SESTAT                                   | SEIEN            | EIPU <sup>(1)</sup> | SYNCPOL        | SYNCOEN |

| bit 15          | -                                                        |                  | -                                        |                  |                     |                | bit     |

|                 |                                                          |                  |                                          |                  |                     |                |         |

| R/W-0           | R/W-0                                                    | R/W-0            | R/W-0                                    | R/W-0            | R/W-0               | R/W-0          | R/W-0   |

| SYNCEN          | SYNCSRC2                                                 | SYNCSRC1         | SYNCSRC0                                 | SEVTPS3          | SEVTPS2             | SEVTPS1        | SEVTPS0 |

| bit 7           |                                                          |                  |                                          |                  |                     |                | bit     |

|                 |                                                          |                  |                                          |                  |                     |                |         |

| Legend:         |                                                          | HS = Hardwa      | re Settable bit                          | HC = Hardwa      | are Clearable bi    | t              |         |

| R = Readable    | bit                                                      | W = Writable     | bit                                      | U = Unimplei     | mented bit, read    | l as '0'       |         |

| -n = Value at F | POR                                                      | '1' = Bit is set | :                                        | '0' = Bit is cle | ared                | x = Bit is unk | nown    |

|                 |                                                          |                  |                                          |                  |                     |                |         |

| bit 15-13       | Unimplemen                                               | ted: Read as     | ʻ0'                                      |                  |                     |                |         |

| bit 12          | •                                                        |                  | rrupt Status bit                         |                  |                     |                |         |

|                 |                                                          |                  | nt interrupt is pe<br>nt interrupt is no |                  |                     |                |         |

| bit 11          |                                                          | ial Event Interr | •                                        | n penuing        |                     |                |         |

| bit II          | •                                                        |                  | t interrupt is en                        | abled            |                     |                |         |

|                 |                                                          |                  | it interrupt is dis                      |                  |                     |                |         |

| bit 10          | EIPU: Enable Immediate Period Updates bit <sup>(1)</sup> |                  |                                          |                  |                     |                |         |

|                 |                                                          | •                | d register is up                         |                  | •                   |                |         |

|                 |                                                          | -                |                                          |                  | PWM cycle bour      | ndaries        |         |

| bit 9           |                                                          |                  | put and Output                           | •                |                     |                |         |

|                 |                                                          |                  | ity is inverted (a<br>ity is active-hig  |                  |                     |                |         |

| bit 8           |                                                          | •                | ster Time Base                           |                  | on Enable bit       |                |         |

|                 |                                                          | output is enab   |                                          | Gyneinonizau     |                     |                |         |

|                 |                                                          | output is disal  |                                          |                  |                     |                |         |

| bit 7           | SYNCEN: Ex                                               | ternal Second    | ary Master Tim                           | e Base Synch     | ronization Enab     | le bit         |         |

|                 |                                                          | •                | n of secondary                           |                  |                     |                |         |

|                 |                                                          | -                | n of secondary                           |                  |                     |                |         |

| bit 6-4         |                                                          |                  | ry Time Base S                           | sync Source S    | election bits       |                |         |

|                 | 111 = Reserv<br>101 = Reserv                             |                  |                                          |                  |                     |                |         |

|                 | 100 = Reserv                                             |                  |                                          |                  |                     |                |         |

|                 | 011 = Reserv                                             |                  |                                          |                  |                     |                |         |

|                 | 010 = Reserv                                             |                  |                                          |                  |                     |                |         |

|                 | 001 = SYNCI<br>000 = SYNCI                               |                  |                                          |                  |                     |                |         |

| bit 3-0         |                                                          |                  | ndarv Special F                          | Event Triager (  | Output Postscal     | er Select bits |         |

|                 | 1111 = 1:16                                              |                  |                                          |                  |                     |                |         |

|                 | 0001 = 1:2 P                                             | ostscale         |                                          |                  |                     |                |         |

|                 | •                                                        |                  |                                          |                  |                     |                |         |

|                 |                                                          |                  |                                          |                  |                     |                |         |

|                 | •                                                        |                  |                                          |                  |                     |                |         |

Note 1: This bit only applies to the secondary master time base period.

# REGISTER 15-16: SPHASEx: PWMx SECONDARY PHASE-SHIFT REGISTER<sup>(1,2)</sup>

| R/W-0                                                    | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0    | R/W-0 | R/W-0 |

|----------------------------------------------------------|-------|------------------|-------|-----------------------------------------|----------|-------|-------|

|                                                          |       |                  | SPHAS | SEx<15:8>                               |          |       |       |

| bit 15                                                   |       |                  |       |                                         |          |       | bit 8 |

|                                                          |       |                  |       |                                         |          |       |       |

| R/W-0                                                    | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0    | R/W-0 | R/W-0 |

|                                                          |       |                  | SPHA  | SEx<7:0>                                |          |       |       |

| bit 7                                                    |       |                  |       |                                         |          |       | bit 0 |

|                                                          |       |                  |       |                                         |          |       |       |

| Legend:                                                  |       |                  |       |                                         |          |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, |       |                  |       | ented bit, read                         | d as '0' |       |       |

| -n = Value at P                                          | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |          | nown  |       |

bit 15-0 **SPHASEx<15:0>:** Secondary Phase Offset for PWMxL Output Pin bits (used in Independent PWM mode only)

- **Note 1:** If PWMCONx<9> = 0, the following applies based on the mode of operation:

- Complementary, Redundant and Push-Pull Output mode (IOCONx<11:10> = 00, 01 or 10); SPHASEx<15:0> = Not used

- True Independent Output mode (IOCONx<11:10> = 11), SPHASEx<15:0> = Phase-shift value for PWMxL only

- 2: If PWMCONx<9> = 1, the following applies based on the mode of operation:

- Complementary, Redundant and Push-Pull Output mode (IOCONx<11:10> = 00, 01 or 10); SPHASEx<15:0> = Not used

- True Independent Output mode (IOCONx<11:10> = 11); SPHASEx<15:0> = Independent time base period value for PWMxL only

- When the PHASEx/SPHASEx registers provide the local period, the valid range of values is 0x0010-0xFFF8

# REGISTER 19-13: ADLVLTRGL: ADC LEVEL-SENSITIVE TRIGGER CONTROL REGISTER LOW

| U-0                                            | R/W-0                                           | U-0              | U-0               | R/W-0             | R/W-0           | R/W-0            | R/W-0 |  |

|------------------------------------------------|-------------------------------------------------|------------------|-------------------|-------------------|-----------------|------------------|-------|--|

| _                                              | LVLEN14                                         | —                | —                 |                   | LVLE            | EN<11:8>         |       |  |

| bit 15                                         |                                                 |                  |                   |                   |                 |                  | bit 8 |  |

|                                                |                                                 |                  |                   |                   |                 |                  |       |  |

| R/W-0                                          | R/W-0                                           | R/W-0            | R/W-0             | R/W-0             | R/W-0           | R/W-0            | R/W-0 |  |

|                                                |                                                 |                  | LVL               | EN<7:0>           |                 |                  |       |  |

| bit 7                                          |                                                 |                  |                   |                   |                 |                  | bit 0 |  |

|                                                |                                                 |                  |                   |                   |                 |                  |       |  |

| Legend:                                        |                                                 |                  |                   |                   |                 |                  |       |  |

| R = Readab                                     | ole bit                                         | W = Writable     | bit               | U = Unimplem      | nented bit, rea | d as '0'         |       |  |

| -n = Value a                                   | at POR                                          | '1' = Bit is set |                   | '0' = Bit is clea | ared            | x = Bit is unkno | wn    |  |

|                                                |                                                 |                  |                   |                   |                 |                  |       |  |

| bit 15                                         | Unimpleme                                       | nted: Read as    | '0'               |                   |                 |                  |       |  |

| bit 14                                         | LVLEN14: L                                      | evel Trigger 14  | Enable bit        |                   |                 |                  |       |  |

|                                                | 1 = Input Channel 14 trigger is level-sensitive |                  |                   |                   |                 |                  |       |  |

| 0 = Input Channel 14 trigger is edge-sensitive |                                                 |                  |                   |                   |                 |                  |       |  |

| bit 13-12                                      | bit 13-12 Unimplemented: Read as '0'            |                  |                   |                   |                 |                  |       |  |

| bit 11-0                                       | LVLEN<11:0                                      | >: Level Trigg   | er x Enable bits  | ;                 |                 |                  |       |  |

|                                                | 1 = Input Ch                                    | annel x trigger  | is level-sensitiv | /e                |                 |                  |       |  |

|                                                | 0 = Input Ch                                    | annel x trigger  | is edge-sensiti   | ve                |                 |                  |       |  |

|                                                |                                                 |                  |                   |                   |                 |                  |       |  |

#### REGISTER 19-16: ADMODOL: ADC INPUT MODE CONTROL REGISTER 0 LOW

| -n = Value at POR (1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |                                    |       |       |       |

|------------------------------------|-------|-----------------------------------------|-------|------------------------------------|-------|-------|-------|

| R = Readable                       | e bit | W = Writable                            | bit   | U = Unimplemented bit, read as '0' |       |       |       |

| Legend:                            |       |                                         |       |                                    |       |       |       |

|                                    |       |                                         |       |                                    |       |       |       |

| bit 7                              |       |                                         |       | 1                                  |       | •     | bit   |

|                                    | SIGN3 |                                         | SIGN2 | DIFF1                              | SIGN1 | DIFF0 | SIGN0 |

| U-0                                | R/W-0 | U-0                                     | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|                                    |       |                                         |       |                                    |       |       |       |

| bit 15                             |       |                                         |       |                                    |       |       | bit   |

| —                                  | SIGN7 | _                                       | SIGN6 | —                                  | SIGN5 | —     | SIGN4 |

| U-0                                | R/W-0 | U-0                                     | R/W-0 | U-0                                | R/W-0 | U-0   | R/W-0 |

bit (odd)15-5 Unimplemented: Read as '0'

bit (3,1) **DIFF<x>:** Pseudo-Differential Mode for Corresponding Analog Inputs bits 1 = Channel is pseudo-differential 0 = Channel is single-ended

bit (even) **SIGNx:** Output Data Sign for Corresponding Analog Inputs bits

1 = Channel output data is signed

0 = Channel output data is unsigned

### REGISTER 19-17: ADMOD0H: ADC INPUT MODE CONTROL REGISTER 0 HIGH

| U-0     | U-0    | U-0 | R/W-0  | U-0 | R/W-0  | U-0 | R/W-0  |

|---------|--------|-----|--------|-----|--------|-----|--------|

| _       | —      | —   | SIGN14 | —   | SIGN13 | —   | SIGN12 |

| bit 15  |        |     |        |     | ·      | ·   | bit 8  |

|         |        |     |        |     |        |     |        |

| U-0     | R/W-0  | U-0 | R/W-0  | U-0 | R/W-0  | U-0 | R/W-0  |

| _       | SIGN11 | —   | SIGN10 | —   | SIGN9  | —   | SIGN8  |

| bit 7   |        |     | •      | •   |        | •   | bit 0  |

|         |        |     |        |     |        |     |        |

| Logondi |        |     |        |     |        |     |        |

| Legena.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 15-13 **Unimplemented:** Read as '0'

bit (odd) Unimplemented: Read as '0'

bit (even) SIGN<x>: Output Data Sign for Corresponding Analog Inputs bits

1 = Channel output data is signed

0 = Channel output data is unsigned

### REGISTER 19-23: ADCAL1H: ADC CALIBRATION REGISTER 1 HIGH

| R/W-0, HS | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0  | R/W-0   |

|-----------|-----|-----|-----|----------|----------|--------|---------|

| CSHRRDY   | —   | —   | —   | CSHRSKIP | CSHRDIFF | CSHREN | CSHRRUN |

| bit 15    |     |     |     |          |          |        | bit 8   |

|           |     |     |     |          |          |        |         |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   | —   | —   | —   | —   | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15    | CSHRRDY: Shared ADC Core Calibration Status Flag bit                                                                                     |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

|           | 1 = Shared ADC core calibration is finished                                                                                              |

|           | 0 = Shared ADC core calibration is in progress                                                                                           |

| bit 14-12 | Unimplemented: Read as '0'                                                                                                               |

| bit 11    | CSHRSKIP: Shared ADC Core Calibration Bypass bit                                                                                         |

|           | 1 = After power-up, the shared ADC core will not be calibrated                                                                           |

|           | 0 = After power-up, the shared ADC core will be calibrated                                                                               |

| bit 10    | CSHRDIFF: Shared ADC Core Pseudo-Differential Input Mode Calibration bit                                                                 |

|           | 1 = Shared ADC core will be calibrated in Pseudo-Differential Input mode                                                                 |

|           | 0 = Shared ADC core will be calibrated in Single-Ended Input mode                                                                        |

| bit 9     | CSHREN: Shared ADC Core Calibration Enable bit                                                                                           |

|           | 1 = Shared ADC core calibration bits (CSHRRDY, CSHRSKIP, CSHRDIFF and CSHRRUN) can be<br>accessed by software                            |

|           | 0 = Shared ADC core calibration bits are disabled                                                                                        |

| bit 8     | CSHRRUN: Shared ADC Core Calibration Start bit                                                                                           |

|           | 1 = If this bit is set by software, the shared ADC core calibration cycle is started; this bit is cleared auto-<br>matically by hardware |

|           | 0 = Software can start the next calibration cycle                                                                                        |

| bit 7-0   | Unimplemented: Read as '0'                                                                                                               |

# TABLE 22-1: CONFIGURATION REGISTER MAP

| Name    | Address           | Device<br>Memory Size<br>(Kbytes) | Bits 23-16 | Bit 15                  | Bit 14 | Bit 13 | Bit 12                  | Bit 11 | Bit 10   | Bit 9 | Bit 8    | Bit 7                   | Bit 6      | Bit 5      | Bit 4                | Bit 3 | Bit 2                   | Bit 1   | Bit 0                   |                     |  |          |

|---------|-------------------|-----------------------------------|------------|-------------------------|--------|--------|-------------------------|--------|----------|-------|----------|-------------------------|------------|------------|----------------------|-------|-------------------------|---------|-------------------------|---------------------|--|----------|

| FSEC    | 002B80            | 16                                |            | AIVTDIS                 | _      |        |                         | C      | SS <2:0> |       | CWRP     | GSS <1                  | .0>        | GWRP       | _                    | BSEN  | BSS <1:                 | 05      | BWRP                    |                     |  |          |

| FSEC    | 005780            | 32                                | _          | AIVIDIS                 |        |        | _                       | ن<br>ا | 55 ~2.0- | -     | CWRF     | 655 ~1                  | .0         | GWRF       | _                    | DOEN  | 600 1.                  | 0-      | DWKF                    |                     |  |          |

| FBSLIM  | 002B90            | 16                                |            |                         |        |        |                         |        |          |       |          |                         | DOLIM      | <12:0>     |                      |       |                         |         |                         |                     |  |          |

| FDOLIN  | 005790            | 32                                |            |                         |        |        |                         |        |          |       |          |                         | DOLIN      | 1<12.02    |                      |       |                         |         |                         |                     |  |          |

| FSIGN   | 002B94            | 16                                |            | Reserved <sup>(2)</sup> |        |        |                         |        |          |       |          |                         |            |            |                      |       |                         |         |                         |                     |  |          |

| FSIGN   | GN 005794 32 - Re | Reserved                          | _          | _                       | _      | —      | _                       | —      | _        | _     | —        | _                       | _          | _          | _                    | _     | _                       |         |                         |                     |  |          |

| FOSCSEL | 002B98            | 16                                |            |                         |        |        |                         |        |          |       |          |                         |            |            |                      |       |                         |         |                         |                     |  |          |

| FUSUSEL | 005798            | 32                                | _          | _                       | _      | _      | _                       | _      | IESO     | _     | _        | —                       | FNOSC<2:0> |            |                      |       |                         |         |                         |                     |  |          |

| FOSC    | 002B9C            | 16                                |            |                         |        |        |                         |        |          |       |          | FOKOM                   | 4.05       |            |                      |       |                         | DOO     |                         |                     |  |          |

| FUSC    | 00579C            | 32                                | _          | _                       | _      | _      | _                       | _      | _        | _     | _        | _                       | -          | PLLKEN     | FCKSM<1:0>           |       | IOL1WAY                 |         | _                       | OSCIOFNC POSCMD<1:0 |  | CMD<1:0> |

| FWDT    | 002BA0            | 16                                |            |                         |        |        |                         |        |          |       |          |                         | WDT        |            | WDTDDE               |       |                         | T -0.05 |                         |                     |  |          |

| FWDI    | 0057A0            | 32                                | —          | _                       | _      | _      | _                       | _      | —        | VVDIV | VIN<1:0> | WINDIS                  | VVDTE      | EN<1:0>    | WDTPRE WDTPOST <3:0> |       |                         | >       |                         |                     |  |          |

| FPOR    | 002BA4            | 16                                |            |                         |        |        |                         |        |          |       |          |                         |            |            |                      |       |                         |         | D                       |                     |  |          |

| FPUR    | 0057A4            | 32                                | —          | _                       | _      | _      | _                       | _      | _        | -     | _        | —                       |            | _          | _                    | _     | _                       | -       | Reserved <sup>(1)</sup> |                     |  |          |

| FICD    | 002BA8            | 16                                |            |                         |        |        |                         |        |          |       |          | Reserved <sup>(1)</sup> |            |            |                      |       |                         |         | S <1:0>                 |                     |  |          |

| FICD    | 0057A8            | 32                                |            | _                       | _      |        | _                       |        | _        | _     |          | Reserved                | —          | JTAGEN —   | _                    | —     |                         | S <1:0> |                         |                     |  |          |

| FDEVOPT | 002BAC            | 16                                |            |                         |        |        |                         |        |          |       |          |                         |            |            |                      |       | Reserved <sup>(1)</sup> |         | PWMLOCK                 |                     |  |          |

| FDEVOPT | 0057AC            | 32                                | _          | _                       | _      |        | _                       |        | _        | _     | —        | _                       | _          | _          | _                    | _     | reserved.,              | —       | FVVIVILUUK              |                     |  |          |

| FALTREG | 002BB0            | 16                                |            |                         |        |        | CTXT2 <2:0> CTXT1 <2:0> |        |          |       |          |                         |            |            |                      |       |                         |         |                         |                     |  |          |

| FALIKEG | 0057B0            | 32                                | —          | _                       | _      | _      | _                       | —      | _        | —     | _        | —                       |            | CTXT2 <2:0 | <ر                   | _     |                         | ×11<2   | .0>                     |                     |  |          |

Note 1: These bits are reserved and must be programmed as '1'.

2: This bit is reserved and must be programmed as '0'.

# 24.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

# 24.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 24.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 24.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a full-speed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

# 24.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

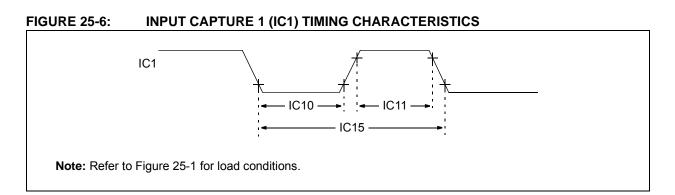

### TABLE 25-27: INPUT CAPTURE 1 MODULE TIMING REQUIREMENTS

| AC CHA        | RACTERI | STICS                          | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |       |                                  |                                  |  |  |  |

|---------------|---------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------------------|----------------------------------|--|--|--|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup> | Min.                                                                                                                                                                                                                                                                                    | Max. | Units | Conditions                       |                                  |  |  |  |

| IC10          | TccL    | IC1 Input Low Time             | Greater of:<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25                                                                                                                                                                                                                                         | —    | ns    | Must also meet<br>Parameter IC15 |                                  |  |  |  |

| IC11          | ТссН    | IC1 Input High Time            | Greater of:<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25                                                                                                                                                                                                                                         | —    | ns    | Must also meet<br>Parameter IC15 | N = Prescale Value<br>(1, 4, 16) |  |  |  |

| IC15          | TCCP    | IC1 Input Period               | Greater of:<br>25 + 50 or<br>(1 Tcy/N) + 50                                                                                                                                                                                                                                             | _    | ns    |                                  |                                  |  |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

| АС СНА       | RACTERI | STICS                     |                           | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |            |                                      |                                               |  |  |  |

|--------------|---------|---------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------------------------------|-----------------------------------------------|--|--|--|

|              |         |                           |                           | operating terri                                                                                                                                 | p o atai o | $\leq$ TA $\leq$ +125°C for Extended |                                               |  |  |  |

| Param<br>No. | Symbol  | Characte                  | Min.                      | Max.                                                                                                                                            | Units      | Conditions                           |                                               |  |  |  |

| IS10         | TLO:SCL | Clock Low Time            | 100 kHz mode              | 4.7                                                                                                                                             | —          | μS                                   |                                               |  |  |  |

|              |         |                           | 400 kHz mode              | 1.3                                                                                                                                             | _          | μS                                   |                                               |  |  |  |

|              |         |                           | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                             |            | μS                                   |                                               |  |  |  |

| IS11         | THI:SCL | Clock High Time           | 100 kHz mode              | 4.0                                                                                                                                             | —          | μS                                   | Device must operate at a minimum of 1.5 MHz   |  |  |  |

|              |         |                           | 400 kHz mode              | 0.6                                                                                                                                             | —          | μS                                   | Device must operate at a<br>minimum of 10 MHz |  |  |  |

|              |         |                           | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                             | _          | μS                                   |                                               |  |  |  |

| IS20         | TF:SCL  | SDA1 and SCL1             | 100 kHz mode              | —                                                                                                                                               | 300        | ns                                   | CB is specified to be from                    |  |  |  |

|              |         | Fall Time                 | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                     | 300        | ns                                   | 10 to 400 pF                                  |  |  |  |

|              |         |                           | 1 MHz mode <sup>(1)</sup> | —                                                                                                                                               | 100        | ns                                   |                                               |  |  |  |

| IS21         | TR:SCL  | SDA1 and SCL1             | 100 kHz mode              | —                                                                                                                                               | 1000       | ns                                   | CB is specified to be from                    |  |  |  |

|              |         | Rise Time                 | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                     | 300        | ns                                   | 10 to 400 pF                                  |  |  |  |

|              |         | 1 MHz mode <sup>(1)</sup> | —                         | 300                                                                                                                                             | ns         |                                      |                                               |  |  |  |

| IS25 TSU:DAT | TSU:DAT | Data Input                | 100 kHz mode              | 250                                                                                                                                             | _          | ns                                   |                                               |  |  |  |

|              |         | Setup Time                | 400 kHz mode              | 100                                                                                                                                             |            | ns                                   |                                               |  |  |  |

|              |         | 1 MHz mode <sup>(1)</sup> | 100                       | _                                                                                                                                               | ns         |                                      |                                               |  |  |  |

| IS26 THD:DA  | THD:DAT | Data Input                | 100 kHz mode              | 0                                                                                                                                               | _          | μS                                   |                                               |  |  |  |

|              |         | Hold Time                 | 400 kHz mode              | 0                                                                                                                                               | 0.9        | μS                                   |                                               |  |  |  |

|              |         |                           | 1 MHz mode <sup>(1)</sup> | 0                                                                                                                                               | 0.3        | μS                                   |                                               |  |  |  |

| IS30         | TSU:STA | Start Condition           | 100 kHz mode              | 4.7                                                                                                                                             | —          | μS                                   | Only relevant for Repeated                    |  |  |  |

|              |         | Setup Time                | 400 kHz mode              | 0.6                                                                                                                                             | —          | μS                                   | Start condition                               |  |  |  |

|              |         |                           | 1 MHz mode <sup>(1)</sup> | 0.25                                                                                                                                            | —          | μS                                   |                                               |  |  |  |

| IS31         | THD:STA | Start Condition           | 100 kHz mode              | 4.0                                                                                                                                             | —          | μS                                   | After this period, the first                  |  |  |  |

|              |         | Hold Time                 | 400 kHz mode              | 0.6                                                                                                                                             | —          | μS                                   | clock pulse is generated                      |  |  |  |

|              |         |                           | 1 MHz mode <sup>(1)</sup> | 0.25                                                                                                                                            | —          | μS                                   |                                               |  |  |  |

| IS33         | Tsu:sto | Stop Condition            | 100 kHz mode              | 4.7                                                                                                                                             | —          | μS                                   |                                               |  |  |  |

|              |         | Setup Time                | 400 kHz mode              | 0.6                                                                                                                                             | —          | μS                                   |                                               |  |  |  |

|              |         |                           | 1 MHz mode <sup>(1)</sup> | 0.6                                                                                                                                             | _          | μS                                   |                                               |  |  |  |

| IS34         | THD:STO | Stop Condition            | 100 kHz mode              | 4                                                                                                                                               | _          | μS                                   |                                               |  |  |  |

|              |         | Hold Time                 | 400 kHz mode              | 0.6                                                                                                                                             | —          | μS                                   |                                               |  |  |  |

|              |         |                           | 1 MHz mode <sup>(1)</sup> | 0.25                                                                                                                                            |            | μS                                   |                                               |  |  |  |

| IS40         | TAA:SCL | Output Valid from         | 100 kHz mode              | 0                                                                                                                                               | 3500       | ns                                   |                                               |  |  |  |

|              |         | Clock                     | 400 kHz mode              | 0                                                                                                                                               | 1000       | ns                                   |                                               |  |  |  |

|              |         |                           | 1 MHz mode <sup>(1)</sup> | 0                                                                                                                                               | 350        | ns                                   |                                               |  |  |  |

| IS45         | TBF:SDA | Bus Free Time             | 100 kHz mode              | 4.7                                                                                                                                             | _          | μS                                   | Time the bus must be free                     |  |  |  |

|              |         |                           | 400 kHz mode              | 1.3                                                                                                                                             |            | μS                                   | before a new transmission                     |  |  |  |

|              |         |                           | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                             |            | μS                                   | can start                                     |  |  |  |

| IS50         | Св      | Bus Capacitive Lo         | ading                     | —                                                                                                                                               | 400        | pF                                   |                                               |  |  |  |

| IS51         | TPGD    | Pulse Gobbler Del         | ay                        | 65                                                                                                                                              | 390        | ns                                   | (Note 2)                                      |  |  |  |

### TABLE 25-40: I2C1 BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

Note 1: Maximum Pin Capacitance = 10 pF for all I2C1 pins (for 1 MHz mode only).

- **2:** Typical value for this parameter is 130 ns.

- **3:** These parameters are characterized but not tested in manufacturing.

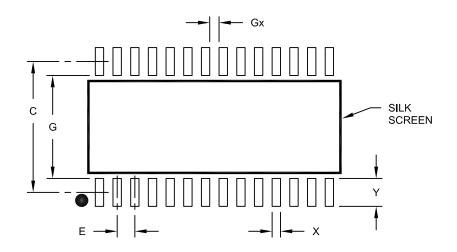

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                          | 1   | MILLIMETERS |          |      |  |

|--------------------------|-----|-------------|----------|------|--|

| Dimensio                 | MIN | NOM         | MAX      |      |  |

| Contact Pitch            | E   |             | 1.27 BSC |      |  |

| Contact Pad Spacing      | С   |             | 9.40     |      |  |

| Contact Pad Width (X28)  | Х   |             |          | 0.60 |  |

| Contact Pad Length (X28) | Y   |             |          | 2.00 |  |

| Distance Between Pads    | Gx  | 0.67        |          |      |  |

| Distance Between Pads    | G   | 7.40        |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway

Harbour City, Kowloon Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302