Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 2K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C                                                                     |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gs202t-i-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS202 family of devices. It is not intended to be a comprehensive resource. To complement the information in this data sheet, refer to the related section in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device-specific information for the dsPIC33EPXXGS202 Digital Signal Controller (DSC) devices.

The dsPIC33EPXXGS202 devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit MCU architecture.

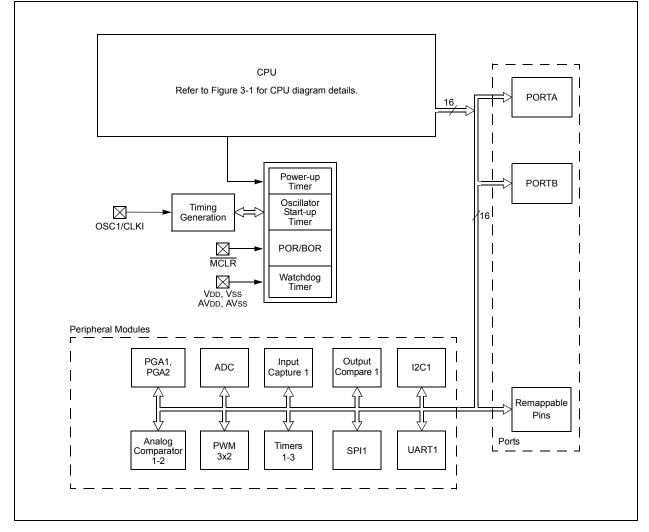

Figure 1-1 shows a general block diagram of the core and peripheral modules. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

## FIGURE 1-1: dsPIC33EPXXGS202 FAMILY BLOCK DIAGRAM

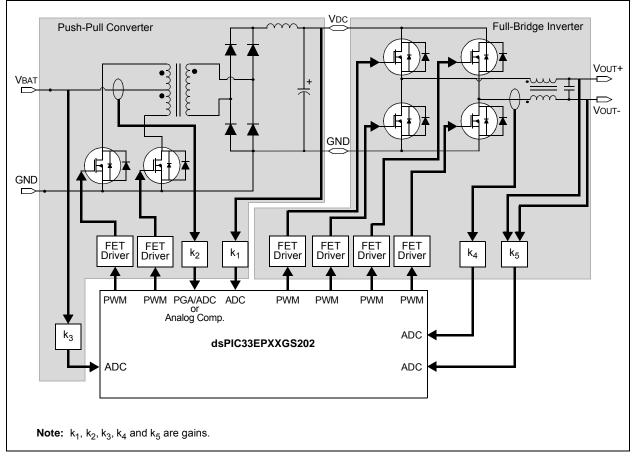

## FIGURE 2-6: OFF-LINE UPS

### TABLE 4-22: PORTA REGISTER MAP

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3 | Bit 2      | Bit 1     | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|------------|-------|------------|-----------|-------|---------------|

| TRISA        | 0E00  | _      | —      | —      |        |        |        | —     |       | _     |       |       |            | -     | TRISA<4:0> | •         |       | 001F          |

| PORTA        | 0E02  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     |            |       | RA<4:0>    |           |       | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     |            |       | LATA<4:0>  |           |       | 0000          |

| ODCA         | 0E06  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     |            |       | ODCA<4:0>  | •         |       | 0000          |

| CNENA        | 0E08  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     |            | (     | CNIEA<4:0> | >         |       | 0000          |

| CNPUA        | 0E0A  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     |            | C     | CNPUA<4:0  | >         |       | 0000          |

| CNPDA        | 0E0C  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     | CNPDA<4:0> |       |            |           | 0000  |               |

| ANSELA       | 0E0E  | —      | -      | _      | -      |        |        | —     |       | _     | _     |       |            | —     |            | ANSA<2:0> |       | 0007          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-23: PORTB REGISTER MAP

| File<br>Name | Addr. | Bit 15 | Bit 14                 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|------------------------|--------|--------|--------|--------|-------|----------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISB        | 0E10  |        | TRISB<15:0>            |        |        |        |        |       |          |       |       |       |       | FFFF  |       |       |       |               |

| PORTB        | 0E12  |        |                        |        |        |        |        |       | RB<15:0  | >     |       |       |       |       |       |       |       | xxxx          |

| LATB         | 0E14  |        | LATB<15:0>             |        |        |        |        |       |          |       |       |       | xxxx  |       |       |       |       |               |

| ODCB         | 0E16  |        |                        |        |        |        |        |       | ODCB<15  | :0>   |       |       |       |       |       |       |       | 0000          |

| CNENB        | 0E18  |        |                        |        |        |        |        |       | CNIEB<15 | :0>   |       |       |       |       |       |       |       | 0000          |

| CNPUB        | 0E1A  |        |                        |        |        |        |        |       | CNPUB<15 | 5:0>  |       |       |       |       |       |       |       | 0000          |

| CNPDB        | 0E1C  |        | CNPDB<15:0> 0          |        |        |        |        |       |          |       |       |       |       | 0000  |       |       |       |               |

| ANSELB       | 0E1E  | _      | ANSB<10:9> - ANSB<7:0> |        |        |        |        |       |          |       |       |       | 06FF  |       |       |       |       |               |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.9.1 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the Program Space without going through Data Space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a Program Space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two 16-bit wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from Program Space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the Program Space location (P<15:0>) to a data address (D<15:0>)

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. The 'phantom' byte (D<15:8>) is always '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a Program Space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user application and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

|     |                | \$P.4        | rogram ôpaca                                                                                                                                     |     |

|-----|----------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| \$2 |                |              |                                                                                                                                                  |     |

|     | s <u>1</u> 8 8 | 0x000000     | 23 16 8 (                                                                                                                                        | 0   |

|     |                |              | 00000000                                                                                                                                         |     |

|     |                |              | 0000000                                                                                                                                          |     |

|     |                | _000000000 ∏ | 0000000                                                                                                                                          |     |

|     |                | - 6×030000   | 0000000                                                                                                                                          |     |

|     |                |              |                                                                                                                                                  |     |

|     |                |              | 'Phantom' Byte                                                                                                                                   |     |

|     |                |              |                                                                                                                                                  |     |

|     |                |              |                                                                                                                                                  |     |

|     |                |              |                                                                                                                                                  |     |

|     |                |              | 2384.8268 . 8 (XMASON # 7)                                                                                                                       |     |

|     |                |              | THERE IN (6998(68-19-1.)                                                                                                                         |     |

|     |                |              | TRANSIS & (Waxax + 5)                                                                                                                            |     |

|     |                |              | THEREIN                                                                                                                                          |     |

|     |                |              |                                                                                                                                                  |     |

|     |                |              | <ul> <li>Whe arrives for the task spectrum is defined by the data<br/>within the page ordered by the TBLPAC regular.</li> </ul>                  | à à |

|     |                | 0-800000     | <ul> <li>Material of a page section of an even with a page time.</li> <li>Soly read operations are shown, whe operatives are also vel</li> </ul> | 83  |

|     |                | 5600000000   | and many manually near                                                                                                                           |     |

### FIGURE 4-11: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

| R/W-0           | R/W-0                                                                                                                                   | R/W-0                                                                                                              | R/W-0                                                                                                                               | R/W-0                                                       | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------|-----------------|-------|--|--|--|--|--|

| NSTDIS          | OVAERR                                                                                                                                  | OVBERR                                                                                                             | COVAERR                                                                                                                             | COVBERR                                                     | OVATE           | OVBTE           | COVTE |  |  |  |  |  |

| bit 15          |                                                                                                                                         |                                                                                                                    |                                                                                                                                     |                                                             |                 |                 | bit 8 |  |  |  |  |  |

|                 |                                                                                                                                         |                                                                                                                    |                                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |  |

| R/W-0           | R/W-0                                                                                                                                   | U-0                                                                                                                | R/W-0                                                                                                                               | R/W-0                                                       | R/W-0           | R/W-0           | U-0   |  |  |  |  |  |

| SFTACERR        | DIV0ERR                                                                                                                                 |                                                                                                                    | MATHERR                                                                                                                             | ADDRERR                                                     | STKERR          | OSCFAIL         | _     |  |  |  |  |  |

| bit 7           |                                                                                                                                         |                                                                                                                    |                                                                                                                                     |                                                             |                 |                 | bit   |  |  |  |  |  |

| Legend:         |                                                                                                                                         |                                                                                                                    |                                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |  |

| R = Readable    | bit                                                                                                                                     | W = Writable                                                                                                       | bit                                                                                                                                 | U = Unimpleme                                               | ented bit, read | as '0'          |       |  |  |  |  |  |

| -n = Value at F | POR                                                                                                                                     | '1' = Bit is set                                                                                                   |                                                                                                                                     | '0' = Bit is clear                                          | -               | x = Bit is unkr | nown  |  |  |  |  |  |

|                 |                                                                                                                                         |                                                                                                                    |                                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |  |

| bit 15          | NSTDIS: Inte                                                                                                                            | errupt Nesting                                                                                                     | Disable bit                                                                                                                         |                                                             |                 |                 |       |  |  |  |  |  |

|                 | 1 = Interrupt                                                                                                                           | nesting is disa                                                                                                    | abled                                                                                                                               |                                                             |                 |                 |       |  |  |  |  |  |

|                 | 0 = Interrupt                                                                                                                           | nesting is ena                                                                                                     | bled                                                                                                                                |                                                             |                 |                 |       |  |  |  |  |  |

| bit 14          |                                                                                                                                         |                                                                                                                    | Overflow Trap F                                                                                                                     | -                                                           |                 |                 |       |  |  |  |  |  |

|                 |                                                                                                                                         |                                                                                                                    | erflow of Accur                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |  |

|                 | -                                                                                                                                       |                                                                                                                    | y overflow of A                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |  |

| bit 13          |                                                                                                                                         |                                                                                                                    | Overflow Trap F                                                                                                                     | -                                                           |                 |                 |       |  |  |  |  |  |

|                 |                                                                                                                                         |                                                                                                                    | erflow of Accur<br>y overflow of Ac                                                                                                 |                                                             |                 |                 |       |  |  |  |  |  |

| bit 12          |                                                                                                                                         |                                                                                                                    | -                                                                                                                                   |                                                             | a hit           |                 |       |  |  |  |  |  |

|                 | <b>COVAERR:</b> Accumulator A Catastrophic Overflow Trap Flag bit<br>1 = Trap was caused by catastrophic overflow of Accumulator A      |                                                                                                                    |                                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |  |

|                 |                                                                                                                                         |                                                                                                                    |                                                                                                                                     | overflow of Accu                                            |                 |                 |       |  |  |  |  |  |

| bit 11          | COVBERR:                                                                                                                                | <b>DVBERR:</b> Accumulator B Catastrophic Overflow Trap Flag bit                                                   |                                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |  |

|                 | 1 = Trap was                                                                                                                            | s caused by ca                                                                                                     | tastrophic over                                                                                                                     | flow of Accumula                                            | ator B          |                 |       |  |  |  |  |  |

|                 | 0 = Trap was                                                                                                                            | s not caused b                                                                                                     | y catastrophic o                                                                                                                    | overflow of Accur                                           | mulator B       |                 |       |  |  |  |  |  |

| bit 10          | OVATE: Acc                                                                                                                              | OVATE: Accumulator A Overflow Trap Enable bit                                                                      |                                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |  |

|                 | 1 = Trap overflow of Accumulator A                                                                                                      |                                                                                                                    |                                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |  |

|                 | 0 = Trap is d                                                                                                                           |                                                                                                                    |                                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |  |

| bit 9           |                                                                                                                                         |                                                                                                                    | erflow Trap En                                                                                                                      | able bit                                                    |                 |                 |       |  |  |  |  |  |

|                 | 1 = Trap ove<br>0 = Trap is d                                                                                                           | erflow of Accun                                                                                                    | nulator B                                                                                                                           |                                                             |                 |                 |       |  |  |  |  |  |

| bit 8           | •                                                                                                                                       |                                                                                                                    | flow Trop Ench                                                                                                                      | la hit                                                      |                 |                 |       |  |  |  |  |  |

| DILO            |                                                                                                                                         | -                                                                                                                  | rflow Trap Enat                                                                                                                     |                                                             |                 |                 |       |  |  |  |  |  |

|                 | $\pm$ – nay on v                                                                                                                        | calasilopinic 0                                                                                                    |                                                                                                                                     | mulator A or R ie                                           | boldeno         |                 |       |  |  |  |  |  |

|                 |                                                                                                                                         |                                                                                                                    |                                                                                                                                     | nulator A or B is                                           | enabled         |                 |       |  |  |  |  |  |

| bit 7           | 0 = Trap is d                                                                                                                           | lisabled                                                                                                           |                                                                                                                                     |                                                             | enabled         |                 |       |  |  |  |  |  |

| bit 7           | 0 = Trap is d                                                                                                                           | lisabled<br>: Shift Accumu                                                                                         | lator Error Statu                                                                                                                   |                                                             |                 |                 |       |  |  |  |  |  |

| bit 7           | 0 = Trap is d<br>SFTACERR:<br>1 = Math err                                                                                              | lisabled<br>: Shift Accumu<br>or trap was ca                                                                       | lator Error Statu<br>used by an inva                                                                                                | ıs bit                                                      | shift           |                 |       |  |  |  |  |  |

| bit 7<br>bit 6  | 0 = Trap is d<br>SFTACERR:<br>1 = Math err<br>0 = Math err                                                                              | lisabled<br>Shift Accumu<br>or trap was ca<br>or trap was no                                                       | lator Error Statu<br>used by an inva                                                                                                | us bit<br>Ilid accumulator                                  | shift           |                 |       |  |  |  |  |  |

|                 | 0 = Trap is d<br>SFTACERR:<br>1 = Math erro<br>0 = Math erro<br>DIV0ERR: D<br>1 = Math erro                                             | lisabled<br>: Shift Accumu<br>or trap was ca<br>or trap was no<br>)ivide-by-Zero<br>or trap was ca                 | lator Error Statu<br>used by an inva<br>t caused by an<br>Error Status bit<br>used by a divide                                      | us bit<br>Ilid accumulator<br>invalid accumula<br>e-by-zero | shift           |                 |       |  |  |  |  |  |

|                 | 0 = Trap is d<br>SFTACERR:<br>1 = Math err<br>0 = Math err<br>DIV0ERR: D<br>1 = Math err<br>0 = Math err                                | lisabled<br>Shift Accumu<br>or trap was ca<br>or trap was no<br>Divide-by-Zero<br>or trap was ca<br>or trap was no | lator Error Statu<br>used by an inva<br>t caused by an<br>Error Status bit<br>used by a divide<br>t caused by a d                   | us bit<br>Ilid accumulator<br>invalid accumula<br>e-by-zero | shift           |                 |       |  |  |  |  |  |

|                 | 0 = Trap is d<br>SFTACERR:<br>1 = Math err<br>0 = Math err<br>DIV0ERR: D<br>1 = Math err<br>0 = Math err                                | lisabled<br>: Shift Accumu<br>or trap was ca<br>or trap was no<br>)ivide-by-Zero<br>or trap was ca                 | lator Error Statu<br>used by an inva<br>t caused by an<br>Error Status bit<br>used by a divide<br>t caused by a d                   | us bit<br>Ilid accumulator<br>invalid accumula<br>e-by-zero | shift           |                 |       |  |  |  |  |  |

| bit 6           | 0 = Trap is d<br>SFTACERR:<br>1 = Math erro<br>0 = Math erro<br>DIV0ERR: D<br>1 = Math erro<br>0 = Math erro<br>Unimplement<br>MATHERR: | lisabled<br>Shift Accumu<br>or trap was ca<br>or trap was no<br>Divide-by-Zero<br>or trap was ca<br>or trap was no | lator Error Statu<br>used by an inva<br>t caused by an<br>Error Status bit<br>used by a divide<br>t caused by a d<br>'0'<br>tus bit | us bit<br>Ilid accumulator<br>invalid accumula<br>e-by-zero | shift           |                 |       |  |  |  |  |  |

- 6. The Peripheral Pin Select (PPS) pin mapping rules are as follows:

- a) Only one "output" function can be active on a given pin at any time, regardless if it is a dedicated or remappable function (one pin, one output).

- b) It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- c) If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- d) If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- e) If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADC to convert the digital output logic level, or to toggle a digital output on a comparator or ADC input, provided there is no external analog input, such as for a built-in self-test.

- f) Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including to any pin with a single output from either a dedicated or remappable "output".

- g) The TRISx registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRISx setting. The TRISx register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRISx settings, which means that the TRISx bit must be set to input for pins with only remappable input function(s) assigned.

- h) All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin has been disabled. Only the Analog Pin Select (ANSELx) registers control the digital input buffer, *not* the TRISx register. The user must disable the analog function on a pin using the Analog Pin Select registers in order to use any "digital input(s)" on a corresponding pin, no exceptions.

## 10.6 I/O Ports Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

## 10.6.1 KEY RESOURCES

- "I/O Ports" (DS70000598) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### REGISTER 13-2: IC1CON2: INPUT CAPTURE CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0                 | R/W-0, HS               | U-0 | R/W-0       | R/W-1       | R/W-1       | R/W-0       | R/W-1       |

|-----------------------|-------------------------|-----|-------------|-------------|-------------|-------------|-------------|

| ICTRIG <sup>(1)</sup> | TRIGSTAT <sup>(2)</sup> |     | SYNCSEL4(3) | SYNCSEL3(3) | SYNCSEL2(3) | SYNCSEL1(3) | SYNCSEL0(3) |

| bit 7                 |                         |     |             |             |             |             | bit 0       |

| Legend:           | HS = Hardware Settable b | it                          |                    |

|-------------------|--------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-8 **Unimplemented:** Read as '0'

bit 7

- ICTRIG: Input Capture Trigger Operation Select bit<sup>(1)</sup>

- 1 = Input source used to trigger the input capture timer (Trigger mode)

- 0 = Input source used to synchronize the input capture timer to a timer of another module (Synchronization mode)

- bit 6 TRIGSTAT: Timer Trigger Status bit<sup>(2)</sup>

- 1 = IC1TMR has been triggered and is running

- 0 = IC1TMR has not been triggered and is being held clear

#### bit 5 Unimplemented: Read as '0'

- **Note 1:** The input source is selected by the SYNCSEL<4:0> bits of the IC1CON2 register.

- 2: This bit is set by the selected input source (selected by SYNCSEL<4:0> bits); it can be read, set and cleared in software.

- **3:** Do not use the IC1 module as its own sync or trigger source.

- 4: This option should only be selected as a trigger source and not as a synchronization source.

## REGISTER 15-1: PTCON: PWM TIME BASE CONTROL REGISTER (CONTINUED)

10001 = 12 Postscaler generates a Special Event Trigger on every second compare match event 0000 = 1:1 Postscaler generates a Special Event Trigger on every compare match event

**Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCIx feature, the user application must program the Period register with a value that is slightly larger than the expected period of the external synchronization input signal.

### REGISTER 15-2: PTCON2: PWM CLOCK DIVIDER SELECT REGISTER 2

| U-0              | U-0 | U-0              | U-0 | U-0                                     | U-0   | U-0                       | U-0   |  |  |

|------------------|-----|------------------|-----|-----------------------------------------|-------|---------------------------|-------|--|--|

| —                | —   | —                |     | _                                       | —     | _                         | —     |  |  |

| bit 15           |     |                  |     |                                         |       |                           | bit 8 |  |  |

|                  |     |                  |     |                                         |       |                           |       |  |  |

| U-0              | U-0 | U-0              | U-0 | U-0                                     | R/W-0 | R/W-0                     | R/W-0 |  |  |

| —                | _   | —                |     | —                                       | P     | CLKDIV<2:0> <sup>(1</sup> | )     |  |  |

| bit 7            |     |                  |     |                                         |       |                           | bit 0 |  |  |

|                  |     |                  |     |                                         |       |                           |       |  |  |

| Legend:          |     |                  |     |                                         |       |                           |       |  |  |

| R = Readable bit | :   | W = Writable I   | bit | U = Unimplemented bit, read as '0'      |       |                           |       |  |  |

| -n = Value at PO | R   | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |       |                           |       |  |  |

bit 15-3 Unimplemented: Read as '0'

bit 2-0 PCLKDIV<2:0>: PWM Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

111 = Reserved

110 = Divide-by-64, maximum PWM timing resolution

101 = Divide-by-32, maximum PWM timing resolution

- 100 = Divide-by-16, maximum PWM timing resolution

- 011 = Divide-by-8, maximum PWM timing resolution

- 010 = Divide-by-4, maximum PWM timing resolution

- 001 = Divide-by-2, maximum PWM timing resolution

- 000 = Divide-by-1, maximum PWM timing resolution (power-on default)

**Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

#### R/W-0 R/W-0 R/W-0 U-0 U-0 U-0 R/W-0 U-0 TRGDIV3 TRGDIV2 TRGDIV1 **TRGDIV0** bit 15 bit 8 R/W-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 DTM<sup>(1)</sup> TRGSTRT5 TRGSTRT4 TRGSTRT3 TRGSTRT2 TRGSTRT1 **TRGSTRT0** bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '0' = Bit is cleared '1' = Bit is set x = Bit is unknown bit 15-12 TRGDIV<3:0>: Trigger # Output Divider bits 1111 = Trigger output for every 16th trigger event 1110 = Trigger output for every 15th trigger event 1101 = Trigger output for every 14th trigger event 1100 = Trigger output for every 13th trigger event 1011 = Trigger output for every 12th trigger event 1010 = Trigger output for every 11th trigger event 1001 = Trigger output for every 10th trigger event 1000 = Trigger output for every 9th trigger event 0111 = Trigger output for every 8th trigger event 0110 = Trigger output for every 7th trigger event 0101 = Trigger output for every 6th trigger event 0100 = Trigger output for every 5th trigger event 0011 = Trigger output for every 4th trigger event 0010 = Trigger output for every 3rd trigger event 0001 = Trigger output for every 2nd trigger event 0000 = Trigger output for every trigger event Unimplemented: Read as '0' bit 11-8 bit 7 DTM: Dual Trigger Mode bit<sup>(1)</sup> 1 = Secondary trigger event is combined with the primary trigger event to create a PWM trigger 0 = Secondary trigger event is not combined with the primary trigger event to create a PWM trigger; two separate PWM triggers are generated bit 6 Unimplemented: Read as '0' bit 5-0 TRGSTRT<5:0>: Trigger Postscaler Start Enable Select bits 111111 = Wait 63 PWM cycles before generating the first trigger event after the module is enabled 000010 = Wait 2 PWM cycles before generating the first trigger event after the module is enabled 000001 = Wait 1 PWM cycle before generating the first trigger event after the module is enabled 000000 = Wait 0 PWM cycles before generating the first trigger event after the module is enabled

## REGISTER 15-19: TRGCONx: PWMx TRIGGER CONTROL REGISTER

### REGISTER 17-4: I2C1MSK: I2C1 SLAVE MODE ADDRESS MASK REGISTER

|                 | -     |                  | -     |                  |                 |                 |       |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

| U-0             | U-0   | U-0              | U-0   | U-0              | U-0             | R/W-0           | R/W-0 |

|                 | _     | —                |       | —                | —               | AMSK            | <9:8> |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | AMSł  | <<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimple      | mented bit, rea | ad as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | eared           | x = Bit is unkr | iown  |

bit 15-10 Unimplemented: Read as '0'

bit 9-0

AMSK<9:0>: Address Mask Select bits

For 10-Bit Address:

1 = Enables masking for bit Ax of incoming message address; bit match is not required in this position

0 = Disables masking for bit Ax; bit match is required in this position

For 7-Bit Address (I2C1MSK<6:0> only):

1 = Enables masking for bit Ax + 1 of incoming message address; bit match is not required in this position

0 = Disables masking for bit Ax + 1; bit match is required in this position

### REGISTER 19-3: ADCON2L: ADC CONTROL REGISTER 2 LOW

| R/W-0      | R/W-0                   | U-0               | R/W-0             | U-0              | R/W-0                     | R/W-0                                  | R/W-0                    |

|------------|-------------------------|-------------------|-------------------|------------------|---------------------------|----------------------------------------|--------------------------|

| REFCIE     | REFERCIE <sup>(2)</sup> | _                 | EIEN              | _                | SHREISEL2 <sup>(1)</sup>  | SHREISEL1 <sup>(1)</sup>               | SHREISEL0 <sup>(1)</sup> |

| bit 15     |                         |                   | 21211             |                  | 01111210222               | OFINEIOLET                             | bit 8                    |

|            |                         |                   |                   |                  |                           |                                        | bit o                    |

| U-0        | R/W-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0                     | R/W-0                                  | R/W-0                    |

|            | SHRADCS6                | SHRADCS5          | SHRADCS4          | SHRADCS3         | SHRADCS2                  | SHRADCS1                               | SHRADCS0                 |

| bit 7      | 0                       | 0.11.0.2000       | 0                 | 0                | 0111012002                | 0                                      | bit 0                    |

| U.I.I      |                         |                   |                   |                  |                           |                                        |                          |

| Legend:    |                         |                   |                   |                  |                           |                                        |                          |

| R = Reada  | able bit                | W = Writable b    | bit               | U = Unimpler     | nented bit, read          | as '0'                                 |                          |

| -n = Value | at POR                  | '1' = Bit is set  |                   | '0' = Bit is cle |                           | x = Bit is unkno                       | wn                       |

|            |                         |                   |                   |                  |                           |                                        |                          |

| bit 15     | REFCIE: Ban             | d Gap and Ref     | erence Voltage    | Readv Comm       | on Interrupt En           | able bit                               |                          |

|            |                         |                   | -                 | -                | ap will become            |                                        |                          |

|            |                         | interrupt is disa |                   |                  |                           | -                                      |                          |

| bit 14     | REFERCIE: E             | Band Gap or Re    | eference Voltag   | e Error Comm     | on Interrupt En           | able bit <sup>(2)</sup>                |                          |

|            |                         |                   |                   |                  |                           | voltage error is o                     | detected                 |

|            |                         | -                 |                   | nd gap and re    | ference voltage           | error event                            |                          |

| bit 13     | -                       | ted: Read as '(   |                   |                  |                           |                                        |                          |

| bit 12     | •                       | iterrupts Enable  |                   | r the input che  | nnolo interrunte          |                                        | (flog is sot)            |

|            |                         |                   |                   |                  |                           | (when EISTATx<br>en ANxRDY flag        |                          |

| bit 11     |                         | ted: Read as '0   | -                 |                  |                           |                                        |                          |

| bit 10-8   | -                       | :0>: Shared Co    |                   | upt Time Seleo   | ction bits <sup>(1)</sup> |                                        |                          |

|            |                         |                   | •                 | •                |                           | prior to when the                      | data is readv            |

|            | 110 = Early in          | iterrupt is set a | nd interrupt is g | generated 7 TA   | DCORE clocks p            | rior to when the                       | data is ready            |

|            |                         |                   |                   |                  |                           | rior to when the                       |                          |

|            |                         |                   |                   |                  |                           | prior to when the<br>prior to when the |                          |

|            |                         |                   |                   |                  |                           | prior to when the                      |                          |

|            |                         |                   |                   |                  |                           | rior to when the                       |                          |

|            | -                       | -                 |                   | generated 1 TA   | DCORE clock pr            | ior to when the c                      | lata is ready            |

| bit 7      | -                       | ted: Read as '(   |                   |                  |                           |                                        |                          |

| bit 6-0    |                         | :0>: Shared AI    | -                 |                  |                           |                                        |                          |

|            | Core Clock) p           |                   | IDER OF ICORES    | RC (Core Sour    | ce Clock) period          | s for one shared                       | IADCORE (ADC             |

|            |                         | 54 Core Source    | Clock periods     |                  |                           |                                        |                          |

|            | •                       |                   | ·                 |                  |                           |                                        |                          |

|            | •                       |                   |                   |                  |                           |                                        |                          |

|            | -0000011 = 6            | Core Source C     | lock periods      |                  |                           |                                        |                          |

|            |                         | Core Source C     |                   |                  |                           |                                        |                          |

|            |                         | Core Source C     |                   |                  |                           |                                        |                          |

|            | 0000000 = 2             | Core Source C     | lock periods      |                  |                           |                                        |                          |

| Note 1:    | For the 6-bit sha       | ared ADC core     | resolution (SHF   | RRES<1:0> = (    | 00), the SHREIS           | SEL<2:0> setting                       | S,                       |

|            |                         |                   |                   |                  |                           | d ADC core reso                        |                          |

- (SHRRES<1:0> = 01), the SHREISEL<2:0> settings, '110' and '111', are not valid and should not be used.

- 2: To avoid false interrupts, the REFERCIE bit must be set only after the module is enabled (ADON = 1).

## 22.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the dsPIC33EPXXGS202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33EPXXGS202 family devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard<sup>™</sup> Security

- JTAG Boundary Scan Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

- Brown-out Reset (BOR)

## 22.1 Configuration Bits

In the dsPIC33EPXXGS202 family devices, the Configuration Words are implemented as volatile memory. This means that configuration data must be programmed each time the device is powered up. Configuration data is stored at the end of the on-chip program memory space, known as the Flash Configuration Words. Their specific locations are shown in Table 22-1 with detailed descriptions in Table 22-2. The configuration data is automatically loaded from the Flash Configuration Words to the proper Configuration Shadow registers during device Resets.

| Note: | Configuration data is reloaded on all types |

|-------|---------------------------------------------|

|       | of device Resets.                           |

When creating applications for these devices, users should always specifically allocate the location of the Flash Configuration Words for configuration data in their code for the compiler. This is to make certain that program code is not stored in this address when the code is compiled. Program code executing out of configuration space will cause a device Reset.

**Note:** Performing a page erase operation on the last page of program memory clears the Flash Configuration Words.

Most instructions are a single word. Certain double-word instructions are designed to provide all the required information in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it executes as a NOP.

The double-word instructions execute in two instruction cycles.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the Program Counter is changed as a result of the instruction, or a PSV or Table Read is performed. In these cases, the execution takes multiple instruction cycles, with the additional instruction cycle(s) executed as a NOP. Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles.

| Note: | For more deta | ils on the inst | ruction set, |

|-------|---------------|-----------------|--------------|

|       | refer to the  | "16-bit MCU     | and DSC      |

|       | Programmer's  |                 |              |

|       | (DS70157).    |                 |              |

| Field           | Description                                                                          |

|-----------------|--------------------------------------------------------------------------------------|

| #text           | Means literal defined by "text"                                                      |

| (text)          | Means "content of text"                                                              |

| [text]          | Means "the location addressed by text"                                               |

| {}              | Optional field or operation                                                          |

| $a\in\{b,c,d\}$ | a is selected from the set of values b, c, d                                         |

| <n:m></n:m>     | Register bit field                                                                   |

| .b              | Byte mode selection                                                                  |

| .d              | Double-Word mode selection                                                           |

| .S              | Shadow register select                                                               |

| .W              | Word mode selection (default)                                                        |

| Acc             | One of two accumulators {A, B}                                                       |

| AWB             | Accumulator write-back destination address register $\in$ {W13, [W13]+ = 2}          |

| bit4            | 4-bit bit selection field (used in word addressed instructions) $\in \{015\}$        |

| C, DC, N, OV, Z | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                 |

| Expr            | Absolute address, label or expression (resolved by the linker)                       |

| f               | File register address ∈ {0x00000x1FFF}                                               |

| lit1            | 1-bit unsigned literal $\in \{0,1\}$                                                 |

| lit4            | 4-bit unsigned literal $\in \{015\}$                                                 |

| lit5            | 5-bit unsigned literal $\in \{031\}$                                                 |

| lit8            | 8-bit unsigned literal $\in \{0255\}$                                                |

| lit10           | 10-bit unsigned literal $\in$ {0255} for Byte mode, {0:1023} for Word mode           |

| lit14           | 14-bit unsigned literal $\in \{016384\}$                                             |

| lit16           | 16-bit unsigned literal $\in \{065535\}$                                             |

| lit23           | 23-bit unsigned literal $\in$ {08388608}; LSb must be '0'                            |

| None            | Field does not require an entry, can be blank                                        |

| OA, OB, SA, SB  | DSP Status bits: ACCA Overflow, ACCB Overflow, ACCA Saturate, ACCB Saturate          |

| PC              | Program Counter                                                                      |

| Slit10          | 10-bit signed literal $\in$ {-512511}                                                |

| Slit16          | 16-bit signed literal ∈ {-3276832767}                                                |

| Slit6           | 6-bit signed literal $\in$ {-1616}                                                   |

| Wb              | Base W register ∈ {W0W15}                                                            |

| Wd              | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                    |

| Wdo             | Destination W register ∈<br>{ Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] } |

| Wm,Wn           | Dividend, Divisor Working register pair (Direct Addressing)                          |

### TABLE 23-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax Description |                                    | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|--------|-----------------------------|------------------------------------|---------------|----------------|--------------------------|

| 74                 | SL                   | SL     | f                           | f = Left Shift f                   | 1             | 1              | C,N,OV,Z                 |

|                    |                      | SL     | f,WREG                      | WREG = Left Shift f                | 1             | 1              | C,N,OV,Z                 |

|                    |                      | SL     | Ws,Wd                       | Wd = Left Shift Ws                 | 1             | 1              | C,N,OV,Z                 |

|                    |                      | SL     | Wb,Wns,Wnd                  | Wnd = Left Shift Wb by Wns         | 1             | 1              | N,Z                      |

|                    |                      | SL     | Wb,#lit5,Wnd                | Wnd = Left Shift Wb by lit5        | 1             | 1              | N,Z                      |

| 75                 | SUB                  | SUB    | Acc                         | Subtract Accumulators              | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | SUB    | f                           | f = f – WREG                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUB    | f,WREG                      | WREG = f – WREG                    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUB    | #lit10,Wn                   | Wn = Wn - lit10                    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUB    | Wb,Ws,Wd                    | Wd = Wb – Ws                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUB    | Wb,#lit5,Wd                 | Wd = Wb – lit5                     | 1             | 1              | C,DC,N,OV,Z              |

| 76                 | SUBB                 | SUBB   | f                           | $f = f - WREG - (\overline{C})$    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUBB   | f,WREG                      | WREG = $f - WREG - (\overline{C})$ | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUBB   | #lit10,Wn                   | Wn = Wn - lit10 - $(\overline{C})$ | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUBB   | Wb,Ws,Wd                    | $Wd = Wb - Ws - (\overline{C})$    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUBB   | Wb,#lit5,Wd                 | $Wd = Wb - lit5 - (\overline{C})$  | 1             | 1              | C,DC,N,OV,Z              |

| 77                 | SUBR                 | SUBR   | f                           | f = WREG – f                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUBR   | f,WREG                      | WREG = WREG – f                    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUBR   | Wb,Ws,Wd                    | Wd = Ws – Wb                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUBR   | Wb,#lit5,Wd                 | Wd = lit5 – Wb                     | 1             | 1              | C,DC,N,OV,Z              |

| 78                 | SUBBR                | SUBBR  | f                           | $f = WREG - f - (\overline{C})$    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUBBR  | f,WREG                      | WREG = WREG – f – $(\overline{C})$ | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUBBR  | Wb,Ws,Wd                    | $Wd = Ws - Wb - (\overline{C})$    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUBBR  | Wb,#lit5,Wd                 | $Wd = lit5 - Wb - (\overline{C})$  | 1             | 1              | C,DC,N,OV,Z              |

| 79                 | SWAP                 | SWAP.b | Wn                          | Wn = nibble swap Wn                | 1             | 1              | None                     |

|                    |                      | SWAP   | Wn                          | Wn = byte swap Wn                  | 1             | 1              | None                     |

| 80                 | TBLRDH               | TBLRDH | Ws,Wd                       | Read Prog<23:16> to Wd<7:0>        | 1             | 5              | None                     |

| 81                 | TBLRDL               | TBLRDL | Ws,Wd                       | Read Prog<15:0> to Wd              | 1             | 5              | None                     |

| 82                 | TBLWTH               | TBLWTH | Ws,Wd                       | Write Ws<7:0> to Prog<23:16>       | 1             | 2              | None                     |

| 83                 | TBLWTL               | TBLWTL | Ws,Wd                       | Write Ws to Prog<15:0>             | 1             | 2              | None                     |

| 84                 | ULNK                 | ULNK   |                             | Unlink Frame Pointer               | 1             | 1              | SFA                      |

| 85                 | XOR                  | XOR    | f                           | f = f .XOR. WREG                   | 1             | 1              | N,Z                      |

|                    |                      | XOR    | f,WREG                      | WREG = f .XOR. WREG                | 1             | 1              | N,Z                      |

|                    |                      | XOR    | #lit10,Wn                   | Wd = lit10 .XOR. Wd                | 1             | 1              | N,Z                      |

|                    |                      | XOR    | Wb,Ws,Wd                    | Wd = Wb .XOR. Ws                   | 1             | 1              | N,Z                      |

|                    |                      | XOR    | Wb,#lit5,Wd                 | Wd = Wb .XOR. lit5                 | 1             | 1              | N,Z                      |

| 86                 | ZE                   | ZE     | Ws,Wnd                      | Wnd = Zero-extend Ws               | 1             | 1              | C,Z,N                    |

## TABLE 23-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

NOTES:

## TABLE 25-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARACTERISTICS |                           |      | (unless oth |        | ns: 3.0V to 3.6V<br>≤ TA ≤ +85°C for Ind<br>≤ TA ≤ +125°C for E |           |  |

|--------------------|---------------------------|------|-------------|--------|-----------------------------------------------------------------|-----------|--|

| Parameter<br>No.   | Тур.                      | Max. | Units       |        | Conditions                                                      |           |  |

| Operating Cur      | rent (IDD) <sup>(1)</sup> |      |             |        |                                                                 |           |  |

| DC20d              | 5                         | 10   | mA          | -40°C  |                                                                 |           |  |

| DC20a              | 5                         | 10   | mA          | +25°C  | 3.3V                                                            | 10 MIPS   |  |

| DC20b              | 5                         | 10   | mA          | +85°C  | 3.3V                                                            | 10 101195 |  |

| DC20c              | 5                         | 10   | mA          | +125°C |                                                                 |           |  |

| DC22d              | 10                        | 15   | mA          | -40°C  |                                                                 |           |  |

| DC22a              | 10                        | 15   | mA          | +25°C  | 2.21/                                                           |           |  |

| DC22b              | 10                        | 15   | mA          | +85°C  | 3.3V                                                            | 20 MIPS   |  |

| DC22c              | 10                        | 15   | mA          | +125°C |                                                                 |           |  |

| DC24d              | 15                        | 20   | mA          | -40°C  |                                                                 |           |  |

| DC24a              | 15                        | 20   | mA          | +25°C  | 3.3V                                                            |           |  |

| DC24b              | 15                        | 20   | mA          | +85°C  | 3.3V                                                            | 40 MIPS   |  |

| DC24c              | 15                        | 20   | mA          | +125°C |                                                                 |           |  |

| DC25d              | 20                        | 28   | mA          | -40°C  |                                                                 |           |  |

| DC25a              | 20                        | 28   | mA          | +25°C  | 3.3V                                                            | 60 MIPS   |  |

| DC25b              | 20                        | 28   | mA          | +85°C  | 3.3V                                                            | 00 101175 |  |

| DC25c              | 20                        | 28   | mA          | +125°C | ]                                                               |           |  |

| DC26d              | 30                        | 35   | mA          | -40°C  |                                                                 |           |  |

| DC26a              | 30                        | 35   | mA          | +25°C  | 3.3V                                                            | 70 MIPS   |  |

| DC26b              | 30                        | 35   | mA          | +85°C  | ]                                                               |           |  |

**Note 1:** IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

Oscillator is configured in EC mode with PLL, OSC1 is driven with external square wave from rail-to-rail (EC Clock Overshoot/Undershoot < 250 mV required)</li>

- · CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as outputs and driving low

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating or being clocked (defined PMDx bits are all ones)

- CPU executing:

while(1) {

· JTAG is disabled

#### TABLE 25-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS