Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l100r8t6 |  |

|----------------------------|-----------------------------------------------------------------------|--|

| Supplier Device Package    | 64-LQFP (10x10)                                                       |  |

| Package / Case             | 64-LQFP                                                               |  |

| Mounting Type              | Surface Mount                                                         |  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |  |

| Oscillator Type            | Internal                                                              |  |

| Data Converters            | A/D 20x12b; D/A 2x12b                                                 |  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |  |

| RAM Size                   | 8K x 8                                                                |  |

| EEPROM Size                | 2K x 8                                                                |  |

| Program Memory Type        | FLASH                                                                 |  |

| Program Memory Size        | 64KB (64K x 8)                                                        |  |

| Number of I/O              | 51                                                                    |  |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                       |  |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                |  |

| Speed                      | 32MHz                                                                 |  |

| Core Size                  | 32-Bit Single-Core                                                    |  |

| Core Processor             | ARM® Cortex®-M3                                                       |  |

| Product Status             | Not For New Designs                                                   |  |

| Details                    |                                                                       |  |

# **Contents**

| 1 | Intro | duction            | 1                                                                | 8    |

|---|-------|--------------------|------------------------------------------------------------------|------|

| 2 | Desc  | ription            |                                                                  | 9    |

|   | 2.1   | Device             | overview                                                         | . 10 |

|   | 2.2   | Ultra-lo           | ow-power device continuum                                        | 11   |

|   |       | 2.2.1              | Performance                                                      | 11   |

|   |       | 2.2.2              | Shared peripherals                                               | 11   |

|   |       | 2.2.3              | Common system strategy                                           | 11   |

|   |       | 2.2.4              | Features                                                         | 11   |

| 3 | Fund  | tional o           | overview                                                         | . 12 |

|   | 3.1   | Low-po             | ower modes                                                       | . 13 |

|   | 3.2   | $ARM^{\mathbb{R}}$ | Cortex <sup>®</sup> -M3 core with MPU                            | . 17 |

|   | 3.3   | Reset              | and supply management                                            | . 18 |

|   |       | 3.3.1              | Power supply schemes                                             | 18   |

|   |       | 3.3.2              | Power supply supervisor                                          | 18   |

|   |       | 3.3.3              | Voltage regulator                                                | 19   |

|   |       | 3.3.4              | Boot modes                                                       | 19   |

|   | 3.4   | Clock i            | management                                                       | . 20 |

|   | 3.5   | Low-po             | ower real-time clock and backup registers                        | . 22 |

|   | 3.6   | GPIOs              | (general-purpose inputs/outputs)                                 | . 22 |

|   | 3.7   | Memoi              | ries                                                             | . 23 |

|   | 3.8   | DMA (              | direct memory access)                                            | . 23 |

|   | 3.9   |                    | iquid crystal display)                                           |      |

|   | 3.10  | ADC (a             | analog-to-digital converter)                                     | . 24 |

|   |       | 3.10.1             | Internal voltage reference (V <sub>REFINT</sub> )                |      |

|   | 3.11  | DAC (d             | digital-to-analog converter)                                     |      |

|   | 3.12  | Ultra-lo           | ow-power comparators and reference voltage                       | . 25 |

|   | 3.13  |                    | g interface                                                      |      |

|   | 3.14  |                    | and watchdogs                                                    |      |

|   | 0.11  | 3.14.1             | General-purpose timers (TIM2, TIM3, TIM4, TIM9, TIM10 and TIM11) |      |

|   |       | 3.14.2             | Basic timers (TIM6 and TIM7)                                     |      |

|   |       | 3.14.3             | SysTick timer                                                    |      |

|   |       | _                  | •                                                                | _    |

|   |       | 3.14.4    | Independent watchdog (IWDG)                                     | 26   |

|---|-------|-----------|-----------------------------------------------------------------|------|

|   |       | 3.14.5    | Window watchdog (WWDG)                                          | 27   |

|   | 3.15  | Commi     | unication interfaces                                            | . 27 |

|   |       | 3.15.1    | I <sup>2</sup> C bus                                            | 27   |

|   |       | 3.15.2    | Universal synchronous/asynchronous receiver transmitter (USART) | 27   |

|   |       | 3.15.3    | Serial peripheral interface (SPI)                               | 27   |

|   |       | 3.15.4    | Universal serial bus (USB)                                      | 27   |

|   | 3.16  | CRC (c    | cyclic redundancy check) calculation unit                       | . 28 |

|   | 3.17  | Develo    | pment support                                                   | . 28 |

| 4 | Pin d | lescript  | ions                                                            | . 29 |

| 5 | Mem   | ory ma    | pping                                                           | . 39 |

| 6 | Elect | trical ch | naracteristics                                                  | . 40 |

|   | 6.1   | Parame    | eter conditions                                                 | . 40 |

|   |       | 6.1.1     | Minimum and maximum values                                      | 40   |

|   |       | 6.1.2     | Typical values                                                  | 40   |

|   |       | 6.1.3     | Typical curves                                                  | 40   |

|   |       | 6.1.4     | Loading capacitor                                               | 40   |

|   |       | 6.1.5     | Pin input voltage                                               | 40   |

|   |       | 6.1.6     | Power supply scheme                                             | 41   |

|   |       | 6.1.7     | Optional LCD power supply scheme                                |      |

|   |       | 6.1.8     | Current consumption measurement                                 | 42   |

|   | 6.2   | Absolu    | te maximum ratings                                              | . 43 |

|   | 6.3   | Operat    | ing conditions                                                  | . 44 |

|   |       | 6.3.1     | General operating conditions                                    | 44   |

|   |       | 6.3.2     | Embedded reset and power control block characteristics          | 45   |

|   |       | 6.3.3     | Embedded internal reference voltage                             | 47   |

|   |       | 6.3.4     | Supply current characteristics                                  | 48   |

|   |       | 6.3.5     | Wakeup time from Low-power mode                                 | 57   |

|   |       | 6.3.6     | External clock source characteristics                           | 59   |

|   |       | 6.3.7     | Internal clock source characteristics                           | 64   |

|   |       | 6.3.8     | PLL characteristics                                             | 66   |

|   |       | 6.3.9     | Memory characteristics                                          | 67   |

|   |       | 6.3.10    | EMC characteristics                                             | 68   |

|   |       | 6.3.11    | Electrical sensitivity characteristics                          | 69   |

|   |       |           |                                                                 |      |

# List of tables

| Table 1.  | Ultra-low-power STM32L100C6 and STM32L100R8/RB device features                |    |

|-----------|-------------------------------------------------------------------------------|----|

|           | and peripheral counts                                                         |    |

| Table 2.  | Functionalities depending on the operating power supply range                 | 14 |

| Table 3.  | CPU frequency range depending on dynamic voltage scaling                      | 15 |

| Table 4.  | Working mode-dependent functionalities (from Run/active down to standby)      | 16 |

| Table 5.  | Timer feature comparison                                                      |    |

| Table 6.  | Legend/abbreviations used in the pinout table                                 |    |

| Table 7.  | STM32L100C6 and STM32L100R8/RB pin definitions                                |    |

| Table 8.  | Alternate function input/output                                               |    |

| Table 9.  | Voltage characteristics                                                       |    |

| Table 10. | Current characteristics                                                       |    |

| Table 11. | Thermal characteristics                                                       |    |

| Table 12. | General operating conditions                                                  |    |

| Table 13. | Embedded reset and power control block characteristics                        |    |

| Table 14. | Embedded internal reference voltage calibration values                        |    |

| Table 15. | Embedded internal reference voltage                                           |    |

| Table 16. | Current consumption in Run mode, code with data processing running from Flash |    |

| Table 17. | Current consumption in Run mode, code with data processing running from RAM   |    |

| Table 18. | Current consumption in Sleep mode                                             |    |

| Table 19. | Current consumption in Low power run mode                                     |    |

| Table 20. | Current consumption in Low power sleep mode                                   |    |

| Table 21. | Typical and maximum current consumptions in Stop mode                         |    |

| Table 22. | Typical and maximum current consumptions in Standby mode                      |    |

| Table 23. | Peripheral current consumption                                                |    |

| Table 24. | Low-power mode wakeup timings                                                 |    |

| Table 25. | High-speed external user clock characteristics.                               |    |

| Table 26. | Low-speed external user clock characteristics                                 |    |

| Table 27. | HSE oscillator characteristics                                                |    |

| Table 28. | LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz)                |    |

| Table 29. | HSI oscillator characteristics                                                |    |

| Table 30. | LSI oscillator characteristics                                                |    |

| Table 31. | MSI oscillator characteristics                                                |    |

| Table 32. | PLL characteristics                                                           |    |

| Table 33. | RAM and hardware registers                                                    |    |

| Table 34. | Flash memory and data EEPROM characteristics                                  |    |

| Table 35. | Flash memory, data EEPROM endurance and data retention                        |    |

| Table 36. | EMS characteristics                                                           |    |

| Table 37. | EMI characteristics                                                           |    |

| Table 38. | ESD absolute maximum ratings                                                  |    |

| Table 39. | Electrical sensitivities                                                      |    |

| Table 40. | I/O current injection susceptibility                                          |    |

| Table 41. | I/O static characteristics                                                    |    |

| Table 42. | Output voltage characteristics                                                |    |

| Table 43. | I/O AC characteristics                                                        |    |

| Table 44. | NRST pin characteristics                                                      |    |

| Table 45. | TIMx characteristics                                                          |    |

| Table 46. | I <sup>2</sup> C characteristics                                              |    |

| Table 47. | SCL frequency ( $f_{PCLK1}$ = 32 MHz, $V_{DD}$ = VDD I2C = 3.3 V)             |    |

|           |                                                                               |    |

|                                        |                            |                           | Low-    | Low-           | Stop |                                        |                                            | Standby                                |  |

|----------------------------------------|----------------------------|---------------------------|---------|----------------|------|----------------------------------------|--------------------------------------------|----------------------------------------|--|

| lps                                    | Run/Active                 | Sleep power<br>Run        |         | power<br>Sleep |      | Wakeup capability                      |                                            | Wakeup capability                      |  |

| DAC                                    | Y                          | Y                         | Y       | Υ              | Υ    | -                                      | -                                          | -                                      |  |

| Comparators                            | Y                          | Υ                         | Υ       | Υ              | Υ    | Y                                      | -                                          | -                                      |  |

| 16-bit Timers                          | Y                          | Υ                         | Y       | Υ              | -    | -                                      | -                                          | -                                      |  |

| IWDG                                   | Y                          | Υ                         | Y       | Υ              | Υ    | Y                                      | Υ                                          | Y                                      |  |

| WWDG                                   | Y                          | Υ                         | Υ       | Υ              | -    | -                                      | -                                          | -                                      |  |

| Systick Timer                          | Y                          | Υ                         | Y       | Y              | -    | -                                      | -                                          | -                                      |  |

| GPIOs                                  | Y                          | Y                         | Υ       | Υ              | Υ    | Y                                      | -                                          | 2 pins                                 |  |

| Wakeup time to Run mode                | 0 μs                       | 0.4 μs                    | 3 µs    | 46 µs          |      | < 8 µs                                 | 58 µs                                      |                                        |  |

|                                        |                            |                           |         |                |      | 65 μΑ (No<br>) V <sub>DD</sub> =1.8 V  | 0.3 μA (No RTC<br>V V <sub>DD</sub> =1.8 V |                                        |  |

| Consumption                            | Down to                    | Downto                    | Down to | Down to        |      | 4 μΑ (with<br>) V <sub>DD</sub> =1.8 V |                                            | (with RTC)<br>DD=1.8 V                 |  |

| V <sub>DD</sub> =1.8V to 3.6V<br>(Typ) | 214 μA/MHz<br>(from Flash) | 50 μA/MHz<br>(from Flash) | 9 μΑ    | 4.4 µA         |      | 65 μΑ (No<br>) V <sub>DD</sub> =3.0 V  |                                            | IA (No RTC)<br>DD=3.0 V                |  |

|                                        |                            |                           |         |                |      | 6 μΑ (with<br>) V <sub>DD</sub> =3.0 V |                                            | 3 μA (with<br>) V <sub>DD</sub> =3.0 V |  |

Table 4. Working mode-dependent functionalities (from Run/active down to standby) (continued)

# 3.2 ARM® Cortex®-M3 core with MPU

The ARM® Cortex®-M3 processor is the industry leading processor for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM® Cortex®-M3 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The memory protection unit (MPU) improves system reliability by defining the memory attributes (such as read/write access permissions) for different memory regions. It provides up to eight different regions and an optional predefined background region.

Owing to its embedded ARM core, the STM32L100C6 and STM32L100R8/RB devices are compatible with all ARM tools and software.

The startup on communication line wakes the CPU which was made possible by an EXTI, this induces a delay before entering run mode.

#### **Nested vectored interrupt controller (NVIC)**

The ultra-low-power STM32L100C6 and STM32L100R8/RB devices embed a nested vectored interrupt controller able to handle up to 45 maskable interrupt channels (not including the 16 interrupt lines of Cortex-M3) and 16 priority levels.

- Closely coupled NVIC gives low-latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of late arriving, higher-priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

## 3.3 Reset and supply management

#### 3.3.1 Power supply schemes

- V<sub>DD</sub> = 1.8 to 3.6 V: external power supply for I/Os and the internal regulator.

Provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.8 to 3.6 V: external analog power supplies for ADC, reset blocks, RCs and PLI

$V_{DDA}$  and  $V_{SSA}$  must be connected to  $V_{DD}$  and  $V_{SS}$ , respectively.

#### 3.3.2 Power supply supervisor

18/103

The device has an integrated ZEROPOWER power-on reset (POR)/power-down reset (PDR) that can be coupled with a brownout reset (BOR) circuitry.

BOR is activated at power-on and the device operates between 1.8 V and 3.6 V.

After the  $V_{DD}$  threshold is reached, the option byte loading process starts, either to confirm or modify default thresholds, or to disable the BOR permanently.

BOR ensures proper operation starting from 1.8 V whatever the power ramp-up phase before it reaches 1.8 V.

DocID024295 Rev 5

Five BOR thresholds are available through option bytes, starting from 1.8 V to 3 V. To reduce the power consumption in Stop mode, it is possible to automatically switch off the internal reference voltage ( $V_{REFINT}$ ) in Stop mode. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for any external reset circuit.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. This PVD offers 7 different levels between 1.85 V and 3.05 V, chosen by software, with a step around 200 mV. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

#### 3.3.3 Voltage regulator

The regulator has three operation modes: main (MR), low-power (LPR) and power down.

- MR is used in Run mode (nominal regulation)

- LPR is used in the Low-power run, Low-power sleep and Stop modes

- Power down is used in Standby mode. The regulator output is high impedance, the kernel circuitry is powered down, inducing zero consumption but the contents of the registers and RAM are lost are lost except for the standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE crystal 32K osc, RCC\_CSR).

#### 3.3.4 Boot modes

At startup, boot pins are used to select one of three boot options:

- Boot from Flash memory

- Boot from System Memory

- Boot from embedded RAM

The boot loader is located in System Memory. It is used to reprogram the Flash memory by using USART1 or USART2. See the application note "STM32 microcontroller system memory boot mode" (AN2606) for details.

The HSI oscillator is to be calibrated to +/-1% before using of the bootloader.

#### 3.14.1 General-purpose timers (TIM2, TIM3, TIM4, TIM9, TIM10 and TIM11)

There are six synchronizable general-purpose timers embedded in the STM32L100C6 and STM32L100R8/RB devices (see *Table 5* for differences).

#### TIM2, TIM3, TIM4

These timers are based on a 16-bit auto-reload up/down-counter and a 16-bit prescaler. They feature 4 independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 12 input captures/output compares/PWMs on the largest packages.

The TIM2, TIM3, TIM4 general-purpose timers can work together or with the TIM10, TIM11 and TIM9 general-purpose timers via the Timer Link feature for synchronization or event chaining. Their counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs.

TIM2, TIM3, TIM4 all have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

#### TIM10, TIM11 and TIM9

TIM10 and TIM11 are based on a 16-bit auto-reload upcounter. TIM9 is based on a 16-bit auto-reload up/down counter. They include a 16-bit prescaler. TIM10 and TIM11 feature one independent channel, whereas TIM9 has two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4 full-featured general-purpose timers.

They can also be used as simple time bases and be clocked by the LSE clock source (32.768 kHz) to provide time bases independent from the main CPU clock.

#### 3.14.2 Basic timers (TIM6 and TIM7)

These timers are mainly used for DAC trigger generation. They can also be used as generic 16-bit time bases.

#### 3.14.3 SysTick timer

This timer is dedicated to the OS, but could also be used as a standard downcounter. It is based on a 24-bit down-counter with autoreload capability and a programmable clock source. It features a maskable system interrupt generation when the counter reaches 0.

#### 3.14.4 Independent watchdog (IWDG)

The independent watchdog is based on a 12-bit down-counter and 8-bit prescaler. It is clocked from an independent 37 kHz internal RC and, as it operates independently of the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes. The counter can be frozen in debug mode.

26/103 DocID024295 Rev 5

## 6.1.6 Power supply scheme

Standby-power circuitry (OSC32K,RTC, Wake-up logic RTC backup registers) Ю Kernel GP I/Os logic (CPU, Logic Digital & Memories) Regulator N x 100 nF + 1 x 10 µF V<sub>SS1/2/.../N</sub>  $V_{\text{DDA}}$ Analog: V<sub>REF+</sub> RCs, PLL ADC/ 100 nF COMP,  $V_{\mathsf{REF}}$ + 1 µF DAC MS32484V1

Figure 8. Power supply scheme

| Symbol            | Ratings                                                      | Value        | Unit |

|-------------------|--------------------------------------------------------------|--------------|------|

| T <sub>STG</sub>  | Storage temperature range                                    | -65 to +150  | °C   |

| $T_J$             | Maximum junction temperature                                 | 105          | °C   |

| T <sub>LEAD</sub> | Maximum lead temperature during soldering (LQFP64, UFQFPN48) | see note (1) | °C   |

**Table 11. Thermal characteristics**

## 6.3 Operating conditions

#### 6.3.1 General operating conditions

Table 12. General operating conditions

| Symbol                          | Parameter                                      | Conditions                                 |      | Max                  | Unit  |

|---------------------------------|------------------------------------------------|--------------------------------------------|------|----------------------|-------|

| f <sub>HCLK</sub>               | Internal AHB clock frequency                   | -                                          | 0    | 32                   |       |

| f <sub>PCLK1</sub>              | Internal APB1 clock frequency                  | -                                          | 0    | 32                   | MHz   |

| f <sub>PCLK2</sub>              | Internal APB2 clock frequency                  | -                                          | 0    | 32                   |       |

| V                               | Standard energting voltage                     | BOR detector enabled,<br>(at power-on)     | 1.8  | 3.6                  | V     |

| $V_{DD}$                        | Standard operating voltage                     | BOR detector disabled, after power on      | 1.65 | 3.6                  | V     |

| V <sub>DDA</sub> <sup>(1)</sup> | Analog operating voltage                       | Must be the same voltage as $V_{DD}^{(2)}$ | 1.8  | 3.6                  | V     |

|                                 |                                                | FT pins: 2.0 V ≤V <sub>DD</sub>            | -0.3 | 5.5 <sup>(3)</sup>   |       |

| W                               | I/O input voltage                              | FT pins: V <sub>DD</sub> < 2.0 V           | -0.3 | 5.25 <sup>(3)</sup>  | V     |

| $V_{IN}$                        | I/O input voltage                              | воото                                      | 0    | 5.5                  | V     |

|                                 |                                                | Any other pin                              | -0.3 | V <sub>DD</sub> +0.3 |       |

| D                               | Power dissipation at TA = 85 °C <sup>(4)</sup> | LQFP64 package                             | -    | 444                  | mW    |

| $P_{D}$                         | Fower dissipation at IA - 65 CV                | UFQFPN48 package                           | -    | 606                  | IIIVV |

| TA                              | Ambient temperature range                      | Maximum power dissipation                  | -40  | 85                   |       |

| TJ                              | Junction temperature range                     | -40 °C ≤ T <sub>A</sub> ≤ 85°C             | -40  | 105                  | °C    |

<sup>1.</sup> When the ADC is used, refer to *Table 53: ADC characteristics*.

44/103 DocID024295 Rev 5

Compliant with JEDEC Std J-STD-020D (for small body, Sn-Pb or Pb assembly), the ST ECOPACK<sup>®</sup>

7191395 specification, and the European directive on Restrictions on Hazardous Substances (ROHS

directive 2011/65/EU, July 2011).

<sup>2.</sup> It is recommended to power  $V_{DD}$  and  $V_{DDA}$  from the same source. A maximum difference of 300 mV between  $V_{DD}$  and  $V_{DDA}$  can be tolerated during power-up and operation.

<sup>3.</sup> To sustain a voltage higher than  $V_{DD}$ +0.3 V, the internal pull-up/pull-down resistors must be disabled.

If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>J</sub> max (see Section 7.3: Thermal characteristics on page 97).

### 6.3.3 Embedded internal reference voltage

The parameters given in the following table are based on characterization results, unless otherwise specified.

Table 14. Embedded internal reference voltage calibration values

| Calibration value name | Description                                                                    | Memory address          |

|------------------------|--------------------------------------------------------------------------------|-------------------------|

| VREFINT_CAL            | Raw data acquired at temperature of 30 °C ±5 °C, V <sub>DDA</sub> = 3 V ±10 mV | 0x1FF8 0078-0x1FF8 0079 |

Table 15. Embedded internal reference voltage

| Symbol                                 | Parameter                                                           | Conditions                                                     | Min   | Тур   | Max   | Unit                  |

|----------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------|-------|-------|-------|-----------------------|

| V <sub>REFINT out</sub> <sup>(1)</sup> | Internal reference voltage                                          | - 40 °C < T <sub>J</sub> < +85 °C                              | 1.202 | 1.224 | 1.242 | V                     |

| I <sub>REFINT</sub>                    | Internal reference current consumption                              | -                                                              | -     | 1.4   | 2.3   | μΑ                    |

| T <sub>VREFINT</sub>                   | Internal reference startup time                                     | -                                                              | -     | 2     | 3     | ms                    |

| V <sub>VREF_MEAS</sub>                 | V <sub>DDA</sub> voltage during V <sub>REFINT</sub> factory measure | -                                                              | 2.99  | 3     | 3.01  | V                     |

| A <sub>VREF_MEAS</sub>                 | Accuracy of factory-measured V <sub>REF</sub> value <sup>(2)</sup>  | Including uncertainties due to ADC and V <sub>DDA</sub> values | -     | -     | ±5    | mV                    |

| T <sub>Coeff</sub> <sup>(3)</sup>      | Temperature coefficient                                             | -40 °C < T <sub>J</sub> < +105 °C                              | -     | 25    | 100   | ppm/°C                |

| A <sub>Coeff</sub> <sup>(3)</sup>      | Long-term stability                                                 | 1000 hours, T= 25 °C                                           | -     | -     | 1000  | ppm                   |

| V <sub>DDCoeff</sub> <sup>(3)(4)</sup> | Voltage coefficient                                                 | 3.0 V < V <sub>DDA</sub> < 3.6 V                               | -     | -     | 2000  | ppm/V                 |

| T <sub>S_vrefint</sub> <sup>(3)</sup>  | ADC sampling time when reading the internal reference voltage       | -                                                              | 4     | -     | -     | μs                    |

| T <sub>ADC_BUF</sub> <sup>(3)</sup>    | Startup time of reference voltage buffer for ADC                    | -                                                              | -     | -     | 10    | μs                    |

| I <sub>BUF_ADC</sub> (3)               | Consumption of reference voltage buffer for ADC                     | -                                                              | -     | 13.5  | 25    | μΑ                    |

| I <sub>VREF_OUT</sub> (3)              | VREF_OUT output current <sup>(5)</sup>                              | -                                                              | -     | -     | 1     | μA                    |

| C <sub>VREF_OUT</sub> (3)              | VREF_OUT output load                                                | -                                                              | -     | -     | 50    | pF                    |

| I <sub>LPBUF</sub> <sup>(3)</sup>      | Consumption of reference voltage buffer for VREF_OUT and COMP       | -                                                              | -     | 730   | 1200  | nA                    |

| V <sub>REFINT_DIV1</sub> (3)           | 1/4 reference voltage                                               | -                                                              | 24    | 25    | 26    |                       |

| V <sub>REFINT_DIV2</sub> (3)           | 1/2 reference voltage                                               | -                                                              | 49    | 50    | 51    | % V <sub>REFINT</sub> |

| V <sub>REFINT_DIV3</sub> (3)           | 3/4 reference voltage                                               | -                                                              | 74    | 75    | 76    |                       |

<sup>1.</sup> Guaranteed by test in production.

<sup>5.</sup> To guarantee less than 1% VREF\_OUT deviation.

$<sup>2. \</sup>quad \text{The internal $V_{\text{REF}}$ value is individually measured in production and stored in dedicated EEPROM bytes. } \\$

<sup>3.</sup> Guaranteed by characterization results.

<sup>4.</sup> Shortest sampling time can be determined in the application by multiple interactions.

Table 16. Current consumption in Run mode, code with data processing running from Flash

| Symbol               | Parameter                                                           | Conditions                                                                              |                                                    | £                                                  | Tun      | Ма    | x <sup>(1)</sup> | Unit |    |

|----------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------|-------|------------------|------|----|

|                      | Parameter                                                           | Conc                                                                                    | iitions                                            | f <sub>HCLK</sub>                                  | Тур      | 55 °C | 85 °C            | Unit |    |

|                      |                                                                     |                                                                                         |                                                    | 1 MHz                                              | 270      | 400   | 400              |      |    |

|                      |                                                                     |                                                                                         | Range 3, V <sub>CORE</sub> =1.2<br>V VOS[1:0] = 11 | 2 MHz                                              | 470      | 600   | 600              | μA   |    |

|                      |                                                                     | <br> f <sub>HSE</sub> = f <sub>HCLK</sub>                                               |                                                    | 4 MHz                                              | 890      | 1025  | 1025             |      |    |

|                      |                                                                     | up to 16 MHz,                                                                           |                                                    | 4 MHz                                              | 1        | 1.3   | 1.3              |      |    |

|                      | Supply<br>current in<br>Run mode,<br>code<br>executed<br>from Flash | included  f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above  16 MHz (PLL ON) <sup>(2)</sup> | Range 2, V <sub>CORE</sub> =1.5<br>V VOS[1:0] = 10 | 8 MHz                                              | 2        | 2.5   | 2.5              |      |    |

|                      |                                                                     |                                                                                         |                                                    | 16 MHz                                             | 3.9      | 5     | 5                |      |    |

|                      |                                                                     |                                                                                         | Range 1, V <sub>CORE</sub> =1.8<br>V VOS[1:0] = 01 | 8 MHz                                              | 2.16 3 3 | 3     |                  |      |    |

| I <sub>DD (Run</sub> |                                                                     |                                                                                         |                                                    | 16 MHz                                             | 4.8      | 5.5   | 5.5              |      |    |

| from Flash)          |                                                                     |                                                                                         |                                                    | 32 MHz                                             | 9.6      | 11    | 11               |      |    |

|                      |                                                                     | from Flash                                                                              | om Flash HSI clock source (16                      | Range 2, V <sub>CORE</sub> =1.5<br>V VOS[1:0] = 10 | 16 MHz   | 4     | 5                | 5    | mA |

|                      |                                                                     | MHz)                                                                                    | Range 1, V <sub>CORE</sub> =1.8<br>V VOS[1:0] = 01 | 32 MHz                                             | 9.4      | 11    | 11               |      |    |

|                      |                                                                     | MSI clock, 65 kHz                                                                       | Range 3, V <sub>CORE</sub> =1.2<br>V VOS[1:0] = 11 | 65 kHz                                             | 0.05     | 0.085 | 0.09             |      |    |

|                      |                                                                     | MSI clock, 524 kHz                                                                      |                                                    | 524 kHz                                            | 0.15     | 0.185 | 0.19             |      |    |

|                      |                                                                     | MSI clock, 4.2 MHz                                                                      | 4.2 MHz                                            | 0.9                                                | 1        | 1     |                  |      |    |

<sup>1.</sup> Guaranteed by characterization results, unless otherwise specified.

<sup>2.</sup> Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

Table 19. Current consumption in Low power run mode

| Symbol                                            | Parameter                                     |                                                | Conditions                                        |                                                              |      |     | Unit |

|---------------------------------------------------|-----------------------------------------------|------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------|------|-----|------|

|                                                   |                                               | All                                            | MSI clock, 65 kHz                                 | T <sub>A</sub> = -40 °C to 25 °C                             | 9    | 12  |      |

|                                                   |                                               | peripherals<br>OFF, code                       | f <sub>HCLK</sub> = 32 kHz                        | T <sub>A</sub> = 85 °C                                       | 17.5 | 24  |      |

| I <sub>DD (LP</sub><br>Run)                       |                                               | executed                                       | MSI clock, 65 kHz                                 | $T_A = -40 ^{\circ}\text{C} \text{ to } 25 ^{\circ}\text{C}$ | 14   | 17  |      |

|                                                   |                                               | from RAM,<br>Flash                             | f <sub>HCLK</sub> = 65 kHz                        | T <sub>A</sub> = 85 °C                                       | 22   | 29  |      |

|                                                   |                                               | switched                                       | MOLALA 404 III                                    | T <sub>A</sub> = -40 °C to 25 °C                             | 37   | 42  |      |

|                                                   | Supply<br>current in<br>Low power<br>run mode | OFF, V <sub>DD</sub><br>from 1.8 V<br>to 3.6 V | MSI clock, 131 kHz<br>f <sub>HCLK</sub> = 131 kHz | T <sub>A</sub> = 55 °C                                       | 37   | 42  |      |

|                                                   |                                               |                                                |                                                   | T <sub>A</sub> = 85 °C                                       | 37   | 42  |      |

|                                                   |                                               | All peripherals OFF, code executed from Flash. | MSI clock, 65 kHz                                 | T <sub>A</sub> = -40 °C to 25 °C                             | 24   | 32  |      |

|                                                   |                                               |                                                | f <sub>HCLK</sub> = 32 kHz                        | T <sub>A</sub> = 85 °C                                       | 33   | 42  | μA   |

|                                                   |                                               |                                                | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 65 kHz   | T <sub>A</sub> = -40 °C to 25 °C                             | 31   | 40  |      |

|                                                   |                                               |                                                |                                                   | T <sub>A</sub> = 85 °C                                       | 40   | 48  |      |

|                                                   |                                               | V <sub>DD</sub> from                           |                                                   | T <sub>A</sub> = -40 °C to 25 °C                             | 48   | 58  |      |

|                                                   |                                               | 1.8 V to<br>3.6 V                              | MSI clock, 131 kHz<br>f <sub>HCLK</sub> = 131 kHz | T <sub>A</sub> = 55 °C                                       | 54   | 63  |      |

|                                                   |                                               |                                                | HOLK TOT KITZ                                     | T <sub>A</sub> = 85 °C                                       | 56   | 65  |      |

| I <sub>DD</sub> Max<br>(LP<br>Run) <sup>(2)</sup> | Max allowed current in Low power run mode     | V <sub>DD</sub> from<br>1.8 V to<br>3.6 V      | -                                                 | -                                                            | -    | 200 |      |

<sup>1.</sup> Guaranteed by characterization results, unless otherwise specified.

**577**

<sup>2.</sup> This limitation is related to the consumption of the CPU core and the peripherals that are powered by the regulator. Consumption of the I/Os is not included in this limitation.

Max (1)(2) Conditions Unit **Symbol Parameter** RMS (root MSI = 4.2 MHz2 mean square) MSI = 1.05 MHz 1.45 supply current  $V_{DD} = 3.0 \text{ V}$  $I_{DD (WU)}$ during wakeup mΑ  $T_A = -40^{\circ}C$  to  $25^{\circ}C$ from Stop) time when  $MSI = 65 \text{ kHz}^{(6)}$ 1.45 exiting from Stop mode

Table 21. Typical and maximum current consumptions in Stop mode (continued)

- The typical values are given for V<sub>DD</sub> = 3.0 V and max values are given for V<sub>DD</sub> = 3.6 V, unless otherwise specified.

- 2. Guaranteed by characterization results, unless otherwise specified.

- 3. LCD enabled with external VLCD, static duty, division ratio = 256, all pixels active, no LCD connected.

- LCD enabled with external VLCD, 1/8 duty, 1/3 bias, division ratio = 64, all pixels active, no LCD connected.

- Based on characterization done with a 32.768 kHz crystal (MC306-G-06Q-32.768, manufacturer JFVNY) with two 6.8pF loading capacitors.

- 6. When MSI = 64 kHz, the RMS current is measured over the first 15 µs following the wakeup event. For the remaining time of the wakeup period, the current is similar to the Run mode current.

Table 22. Typical and maximum current consumptions in Standby mode

| Symbol                            | Parameter                                                            | Conditions                                                  |                                                              | Typ <sup>(1)</sup> | Max<br>(1)(2) | Unit |

|-----------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------|--------------------|---------------|------|

|                                   |                                                                      |                                                             | T <sub>A</sub> = -40 °C to 25 °C<br>V <sub>DD</sub> = 1.8 V  | 0.9                | -             |      |

|                                   |                                                                      | RTC clocked by LSI (no independent watchdog)                | $T_A$ = -40 °C to 25 °C                                      | 1.1                | 1.8           |      |

|                                   |                                                                      | independent watchdog)                                       | T <sub>A</sub> = 55 °C                                       | 1.42               | 2.5           |      |

| I <sub>DD</sub>                   | Supply current in Standby                                            |                                                             | T <sub>A</sub> = 85 °C                                       | 1.87               | 3             |      |

| (Standby<br>with RTC)             | mode with RTC enabled                                                | RTC clocked by LSE (no independent watchdog) <sup>(3)</sup> | T <sub>A</sub> = -40 °C to 25 °C<br>V <sub>DD</sub> = 1.8 V  | 1                  | -             |      |

|                                   |                                                                      |                                                             | $T_A$ = -40 °C to 25 °C                                      | 1.33               | 2.9           | μΑ   |

|                                   |                                                                      |                                                             | T <sub>A</sub> = 55 °C                                       | 1.59               | 3.4           |      |

|                                   |                                                                      |                                                             | T <sub>A</sub> = 85 °C                                       | 2.01               | 4.3           |      |

|                                   |                                                                      | Independent watchdog and LSI enabled                        | T <sub>A</sub> = -40 °C to 25 °C                             | 1.1                | 1.6           |      |

| I <sub>DD</sub>                   | Supply current in Standby mode with RTC disabled                     |                                                             | $T_A = -40 ^{\circ}\text{C} \text{ to } 25 ^{\circ}\text{C}$ | 0.3                | 0.55          |      |

| (Standby)                         | mode with KTC disabled                                               | Independent watchdog and LSI OFF                            | T <sub>A</sub> = 55 °C                                       | 0.5                | 0.8           |      |

|                                   |                                                                      |                                                             | T <sub>A</sub> = 85 °C                                       | 1                  | 1.7           |      |

| I <sub>DD (WU</sub> from Standby) | RMS supply current during wakeup time when exiting from Standby mode | -                                                           | V <sub>DD</sub> = 3.0 V<br>T <sub>A</sub> = -40 °C to 25 °C  | 1                  | -             | mA   |

- 1. The typical values are given for  $V_{DD}$  = 3.0 V and max values are given for  $V_{DD}$  = 3.6 V, unless otherwise specified.

- 2. Guaranteed by characterization results, unless otherwise specified.

- Based on characterization done with a 32.768 kHz crystal (MC306-G-06Q-32.768, manufacturer JFVNY) with two 6.8pF loading capacitors.

#### On-chip peripheral current consumption

The current consumption of the on-chip peripherals is given in the following table. The MCU is placed under the following conditions:

- ullet all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

Table 23. Peripheral current consumption<sup>(1)</sup>

|            |                    | Typica                                                | consumption,                                          | V <sub>DD</sub> = 3.0 V, T <sub>A</sub>               | = 25 °C                 |                                |

|------------|--------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------|--------------------------------|

| Peripheral |                    | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | Range 3,<br>V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | Low power sleep and run | Unit                           |

|            | TIM2               | 13                                                    | 10.5                                                  | 8                                                     | 10.5                    |                                |

|            | TIM3               | 14                                                    | 12                                                    | 9                                                     | 12                      |                                |

|            | TIM4               | 12.5                                                  | 10.5                                                  | 8                                                     | 11                      |                                |

|            | TIM6               | 5.5                                                   | 4.5                                                   | 3.5                                                   | 4.5                     |                                |

|            | TIM7               | 5.5                                                   | 5                                                     | 3.5                                                   | 4.5                     |                                |

|            | LCD                | 5.5                                                   | 5                                                     | 3.5                                                   | 5                       |                                |

|            | WWDG               | 4                                                     | 3.5                                                   | 2.5                                                   | 3.5                     |                                |

| APB1       | SPI2               | 5.5                                                   | 5                                                     | 4                                                     | 5                       | μΑ/MHz                         |

| APBI       | USART2             | 9                                                     | 8                                                     | 5.5                                                   | 8.5                     | (f <sub>HCLK</sub> )           |

| 1          | USART3             | 10.5                                                  | 9                                                     | 6                                                     | 8                       |                                |

|            | I2C1               | 8.5                                                   | 7                                                     | 5.5                                                   | 7.5                     |                                |

|            | I2C2               | 8.5                                                   | 7                                                     | 5.5                                                   | 6.5                     |                                |

|            | USB                | 12.5                                                  | 10                                                    | 6.5                                                   | 10                      |                                |

|            | PWR                | 4.5                                                   | 4                                                     | 3                                                     | 3.5                     |                                |

|            | DAC                | 9                                                     | 7.5                                                   | 6                                                     | 7                       |                                |

|            | COMP               | 4.5                                                   | 4                                                     | 3.5                                                   | 4.5                     |                                |

|            | SYSCFG & RI        | 3                                                     | 2.5                                                   | 2                                                     | 2.5                     |                                |

| APB2       | TIM9               | 9                                                     | 7.5                                                   | 6                                                     | 7                       |                                |

|            | TIM10              | 6.5                                                   | 5.5                                                   | 4.5                                                   | 5.5                     |                                |

|            | TIM11              | 7                                                     | 6                                                     | 4.5                                                   | 5.5                     | µA/MHz<br>(f <sub>HCLK</sub> ) |

|            | ADC <sup>(2)</sup> | 11.5                                                  | 9.5                                                   | 8                                                     | 9                       | ('HCLK/                        |

|            | SPI1               | 5                                                     | 4.5                                                   | 3                                                     | 4                       |                                |

|            | USART1             | 9                                                     | 7.5                                                   | 6                                                     | 7.5                     |                                |

Note:

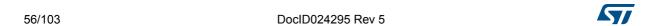

For CL1 and CL2, it is recommended to use high-quality ceramic capacitors in the 5 pF to 15 pF range selected to match the requirements of the crystal or resonator (see Figure 14). CL1 and CL2, are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of CL1 and CL2.

Load capacitance CL has the following formula:  $CL = CL1 \times CL2 / (CL1 + CL2) + Cstray$  where Cstray is the pin capacitance and board or trace PCB-related capacitance. Typically, it is between 2 pF and 7 pF.

Caution:

To avoid exceeding the maximum value of CL1 and CL2 (15 pF) it is strongly recommended to use a resonator with a load capacitance CL  $\leq$  7 pF. Never use a resonator with a load capacitance of 12.5 pF.

Example: if you choose a resonator with a load capacitance of CL = 6 pF and Cstray = 2 pF, then CL1 = CL2 = 8 pF.

Figure 14. Typical application with a 32.768 kHz crystal

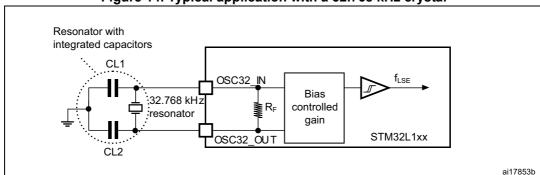

Figure 15. I/O AC characteristics definition

#### 6.3.14 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor, RPU (see *Table 44*).

Unless otherwise specified, the parameters given in *Table 44* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 12*.

| Symbol                                | Parameter                                       | Conditions                                                  | Min                        | Тур                               | Max                 | Unit |

|---------------------------------------|-------------------------------------------------|-------------------------------------------------------------|----------------------------|-----------------------------------|---------------------|------|

| V <sub>IL(NRST)</sub> <sup>(1)</sup>  | NRST input low level voltage                    | -                                                           | -                          | -                                 | 0.3 V <sub>DD</sub> |      |

| V <sub>IH(NRST)</sub> <sup>(1)</sup>  | NRST input high level voltage                   | -                                                           | 0.39 V <sub>DD</sub> +0.59 | -                                 |                     |      |

| V . (1)                               | NRST output low level voltage                   | I <sub>OL</sub> = 2 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V   | -                          | -                                 | - 0.4               |      |

| V <sub>OL(NRST)</sub> <sup>(1)</sup>  | NKS i output low level voltage                  | I <sub>OL</sub> = 1.5 mA<br>1.8 V < V <sub>DD</sub> < 2.7 V | -                          | 1                                 | 0.4                 |      |

| V <sub>hys(NRST)</sub> <sup>(1)</sup> | NRST Schmitt trigger voltage hysteresis         | -                                                           | -                          | 10%V <sub>DD</sub> <sup>(2)</sup> |                     | mV   |

| R <sub>PU</sub>                       | Weak pull-up equivalent resistor <sup>(3)</sup> | $V_{IN} = V_{SS}$                                           | 30                         | 45                                | 60                  | kΩ   |

| V <sub>F(NRST)</sub> <sup>(1)</sup>   | NRST input filtered pulse                       | -                                                           | -                          | -                                 | 50                  | ns   |

| V <sub>NF(NRST)</sub> <sup>(1)</sup>  | NRST input not filtered pulse                   | -                                                           | 350                        | -                                 | -                   | ns   |

Table 44. NRST pin characteristics

74/103

DocID024295 Rev 5

<sup>1.</sup> Guaranteed by design.

<sup>2. 200</sup> mV minimum value

<sup>3.</sup> The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is around 10%.

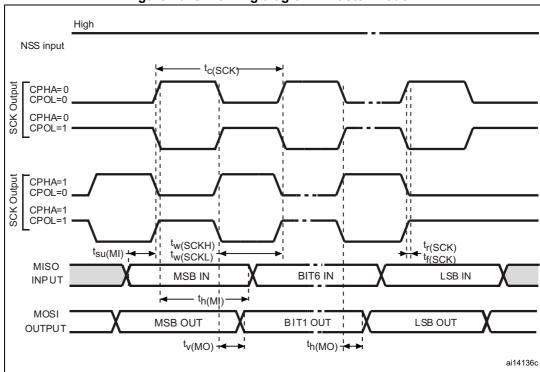

Figure 20. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

#### **USB** characteristics

The USB interface is USB-IF certified (full speed).

Table 49. USB startup time

| Symbol                              | Parameter                    | Max | Unit |

|-------------------------------------|------------------------------|-----|------|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB transceiver startup time | 1   | μs   |

1. Guaranteed by design.

#### 6.3.20 LCD controller

The STM32L100C6 and STM32L100R8/RB devices embed a built-in step-up converter to provide a constant LCD reference voltage independently from the  $V_{DD}$  voltage. An external capacitor  $C_{\text{ext}}$  must be connected to the  $V_{LCD}$  pin to decouple this converter.

Table 59. LCD controller characteristics

| Symbol                           | Parameter                                                         | Min  | Тур                  | Max       | Unit     |  |

|----------------------------------|-------------------------------------------------------------------|------|----------------------|-----------|----------|--|

| $V_{LCD}$                        | LCD external voltage                                              | -    | -                    | 3.6       |          |  |

| V <sub>LCD0</sub>                | LCD internal reference voltage 0                                  | -    | 2.6                  | -         |          |  |

| V <sub>LCD1</sub>                | LCD internal reference voltage 1                                  | -    | 2.73                 | -         |          |  |

| V <sub>LCD2</sub>                | LCD internal reference voltage 2                                  | -    | 2.86                 | -         |          |  |

| V <sub>LCD3</sub>                | LCD internal reference voltage 3                                  | -    | 2.98                 | -         | V        |  |

| V <sub>LCD4</sub>                | LCD internal reference voltage 4                                  |      | 3.12                 | -         |          |  |

| V <sub>LCD5</sub>                | LCD internal reference voltage 5                                  | -    | 3.26                 | -         |          |  |

| V <sub>LCD6</sub>                | LCD internal reference voltage 6                                  | -    | 3.4                  | -         |          |  |

| V <sub>LCD7</sub>                | LCD internal reference voltage 7                                  | -    | 3.55                 | -         |          |  |

| C <sub>ext</sub>                 | V <sub>LCD</sub> external capacitance                             | 0.1  | -                    | 2         | μF       |  |

| ı (1)                            | Supply current at V <sub>DD</sub> = 2.2 V                         | -    | 3.3                  | -         | μA       |  |

| I <sub>LCD</sub> <sup>(1)</sup>  | Supply current at V <sub>DD</sub> = 3.0 V                         | -    | 3.1                  | -         | μΑ       |  |

| R <sub>Htot</sub> <sup>(2)</sup> | Low drive resistive network overall value                         | 5.28 | 6.6                  | 7.92      | МΩ       |  |

| R <sub>L</sub> <sup>(2)</sup>    | High drive resistive network total value                          | 192  | 240                  | 288       | kΩ       |  |

| V <sub>44</sub>                  | Segment/Common highest level voltage                              | -    | -                    | $V_{LCD}$ | V        |  |

| V <sub>34</sub>                  | Segment/Common 3/4 level voltage                                  | -    | 3/4 V <sub>LCD</sub> | -         |          |  |

| V <sub>23</sub>                  | Segment/Common 2/3 level voltage                                  | -    | 2/3 V <sub>LCD</sub> | -         |          |  |

| V <sub>12</sub>                  | Segment/Common 1/2 level voltage                                  |      | 1/2 V <sub>LCD</sub> | -         | .,       |  |

| V <sub>13</sub>                  | Segment/Common 1/3 level voltage                                  | -    | 1/3 V <sub>LCD</sub> | -         | V        |  |

| V <sub>14</sub>                  | Segment/Common 1/4 level voltage                                  | -    | 1/4 V <sub>LCD</sub> | -         | <u> </u> |  |

| V <sub>0</sub>                   | Segment/Common lowest level voltage                               | 0    | -                    | -         | İ        |  |

| ΔVxx <sup>(2)</sup>              | Segment/Common level voltage error T <sub>A</sub> = -40 to 85 ° C | -    | -                    | ±50       | mV       |  |

LCD enabled with 3 V internal step-up active, 1/8 duty, 1/4 bias, division ratio= 64, all pixels active, no LCD connected

**577**

<sup>2.</sup> Guaranteed by characterization results.

## 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK<sup>®</sup> is an ST trademark.

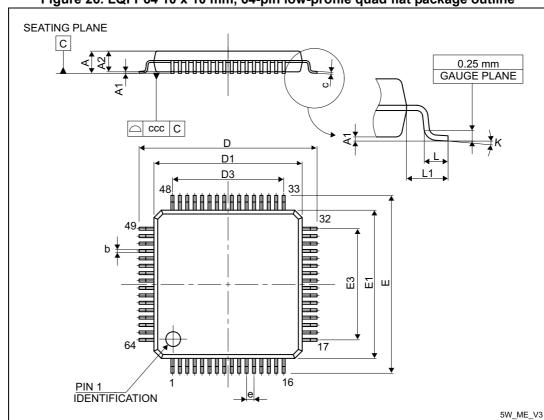

# 7.1 LQFP64 10 x 10 mm, 64-pin low-profile quad flat package information

Figure 26. LQFP64 10 x 10 mm, 64-pin low-profile quad flat package outline

1. Drawing is not to scale.

Table 60. LQFP64 10 x 10 mm, 64-pin low-profile quad flat package mechanical

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

|        | Min   | Тур         | Max   | Тур    | Min                   | Max    |

| Α      | -     | -           | 1.600 | -      | -                     | 0.0630 |

| A1     | 0.050 | -           | 0.150 | 0.0020 | -                     | 0.0059 |

| A2     | 1.350 | 1.400       | 1.450 | 0.0531 | 0.0551                | 0.0571 |

#### 7.3.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.

98/103 DocID024295 Rev 5