#### Welcome to E-XFL.COM

**Renesas Electronics America Inc - D12320VF25V Datasheet**

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                          |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                     |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 25MHz                                                                        |

| Connectivity               | SCI, SmartCard                                                               |

| Peripherals                | DMA, POR, PWM, WDT                                                           |

| Number of I/O              | 86                                                                           |

| Program Memory Size        | · ·                                                                          |

| Program Memory Type        | ROMIess                                                                      |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 4K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                  |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                          |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 128-BFQFP                                                                    |

| Supplier Device Package    | 128-QFP (14x20)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/d12320vf25v |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.5.1 General Register Data Formats

| Data Type      | Register Number | Data Format                                                                                                      |

|----------------|-----------------|------------------------------------------------------------------------------------------------------------------|

| 1-bit data     | RnH             | 7 0<br>7 6 5 4 3 2 1 0 Don't care                                                                                |

| 1-bit data     | RnL             | 7         0           Don't care         7         6         5         4         3         2         1         0 |

| 4-bit BCD data | RnH             | 7     4     3     0       Upper     Lower     Don't care                                                         |

| 4-bit BCD data | RnL             | 7430Don't careUpperLower                                                                                         |

| Byte data      | RnH             | 7 0<br>Don't care<br>MSB LSB                                                                                     |

| Byte data      | RnL             | 70Don't careMSBMSBLSB                                                                                            |

Figure 2.7 General Register Data Formats

## 7.4 **Register Descriptions (3)**

## 7.4.1 DMA Write Enable Register (DMAWER)

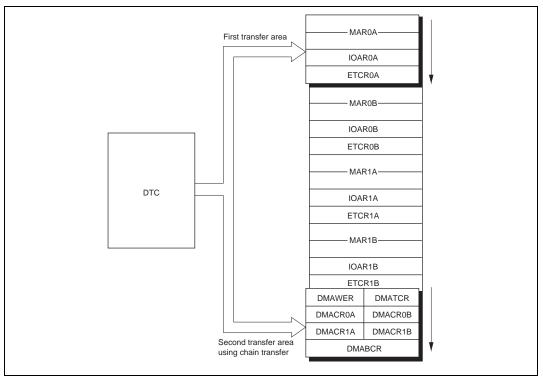

The DMAC can activate the DTC with a transfer end interrupt, rewrite the channel on which the transfer ended using a DTC chain transfer, and reactivate the DTC. DMAWER applies restrictions so that specific bits of DMACR for the specific channel, and also DMATCR and DMABCR, can be changed to prevent inadvertent rewriting of registers other than those for the channel concerned. The restrictions applied by DMAWER are valid for the DTC.

Figure 7.2 shows the transfer areas for activating the DTC with a channel 0A transfer end interrupt, and reactivating channel 0A. The address register and count register area is re-set by the first DTC transfer, then the control register area is re-set by the second DTC chain transfer.

When re-setting the control register area, perform masking by setting bits in DMAWER to prevent modification of the contents of the other channels.

Figure 7.2 Areas for Register Re-Setting by DTC (Example: Channel 0A)

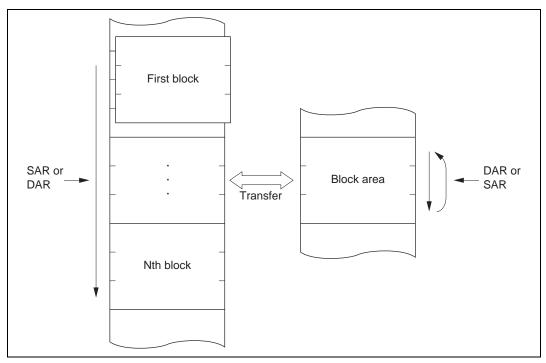

### 7.5.7 Block Transfer Mode

In block transfer mode, transfer is performed with channels A and B used in combination. Block transfer mode can be specified by setting the FAE bit in DMABCR and the BLKE bit in DMACRA to 1.

In block transfer mode, a transfer of the specified block size is carried out in response to a single transfer request, and this is executed the specified number of times. The transfer source is specified by MARA, and the transfer destination by MARB. Either the transfer source or the transfer destination can be selected as a block area (an area composed of a number of bytes or words).

Table 7.11 summarizes register functions in block transfer mode.

| Table 7.11         Register Functions in Block Trans |

|------------------------------------------------------|

|------------------------------------------------------|

| Register      | Function                        | Initial Setting                       | Operation                                                                          |

|---------------|---------------------------------|---------------------------------------|------------------------------------------------------------------------------------|

| 23 00         | Source address register         | Start address of transfer source      | Incremented/decremented every transfer, or fixed                                   |

| 23 00         | Destination<br>address register | Start address of transfer destination | Incremented/decremented every transfer, or fixed                                   |

| 7 (<br>ETCRAH | Holds block<br>size             | Block size                            | Fixed                                                                              |

| 7 V<br>ETCRAL | Block size<br>counter           | Block size                            | Decremented every<br>transfer; ETCRH value<br>copied when count reaches<br>H'00    |

| 15 C          | Block transfer counter          | Number of block<br>transfers          | Decremented every block<br>transfer; transfer ends<br>when count reaches<br>H'0000 |

Legend:

MARA: Memory address register A

MARB: Memory address register B

ETCRA: Execute transfer count register A

ETCRB: Execute transfer count register B

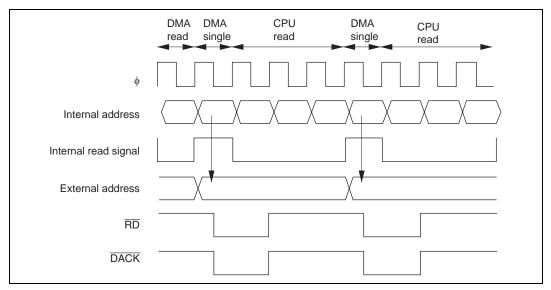

Figure 7.34 shows an example of single address transfer using the write data buffer function. In this example, the CPU program area is in on-chip memory.

Figure 7.34 Example of Single Address Transfer Using Write Data Buffer Function

When the write data buffer function is activated, the DMAC recognizes that the bus cycle concerned has ended, and starts the next operation. Therefore,  $\overline{DREQ}$  pin sampling is started one state after the start of the DMA write cycle or single address transfer.

### 7.5.13 DMAC Multi-Channel Operation

The DMAC channel priority order is: channel 0 > channel 1, and channel A > channel B. Table 7.13 summarizes the priority order for DMAC channels.

### Table 7.13 DMAC Channel Priority Order

| Short Address Mode | Full Address Mode | Priority |  |

|--------------------|-------------------|----------|--|

| Channel 0A         | Channel 0         | High     |  |

| Channel 0B         |                   | Ť        |  |

| Channel 1A         | Channel 1         |          |  |

| Channel 1B         |                   | Low      |  |

Figure 8.8 Memory Map in Block Transfer Mode

### 11.2.8 Port 2 Data Direction Register (P2DDR)

| Bit        | Bit : 7 |        | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|------------|---------|--------|--------|--------|--------|--------|--------|--------|--------|

|            |         | P27DDR | P26DDR | P25DDR | P24DDR | P23DDR | P22DDR | P21DDR | P20DDR |

| Initial va | alue :  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W        | :       | W      | W      | W      | W      | W      | W      | W      | W      |

P2DDR is an 8-bit write-only register, the individual bits of which specify input or output for the pins of port 2.

Port 2 is multiplexed with pins PO7 to PO0. Bits corresponding to pins used for PPG output must be set to 1. For further information about P2DDR, see section 9, I/O Port.

### 11.2.9 Module Stop Control Register (MSTPCR)

|                 |     | MSTPCRH |     |     |     |     |     |     |     |     |     | MSTI | PCRL | -   |     |     |

|-----------------|-----|---------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|-----|-----|-----|

| Bit :           | 15  | 14      | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4    | 3    | 2   | 1   | 0   |

|                 |     |         |     |     |     |     |     |     |     |     |     |      |      |     |     |     |

| Initial value : | 0   | 0       | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1    | 1    | 1   | 1   | 1   |

| R/W :           | R/W | R/W     | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W  | R/W  | R/W | R/W | R/W |

MSTPCR is a 16-bit readable/writable register that performs module stop mode control.

When the MSTP11 bit in MSTPCR is set to 1, PPG operation stops at the end of the bus cycle and a transition is made to module stop mode. Registers cannot be read or written to in module stop mode. For details, see section 21.5, Module Stop Mode.

MSTPCR is initialized to H'3FFF by a reset and in hardware standby mode. It is not initialized in software standby mode.

Bit 11—Module Stop (MSTP11): Specifies the PPG module stop mode.

| Bit 11<br>MSTP11 | Description                  |                 |

|------------------|------------------------------|-----------------|

| 0                | PPG module stop mode cleared |                 |

| 1                | PPG module stop mode set     | (Initial value) |

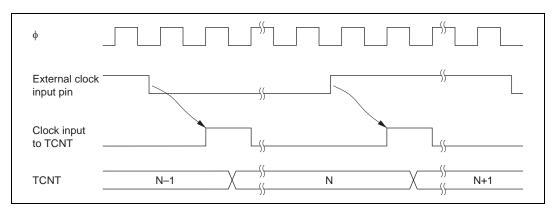

Figure 12.3 Count Timing for External Clock Input

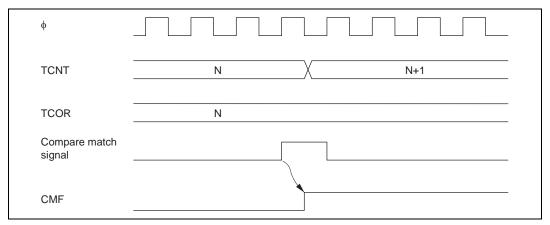

### 12.3.2 Compare Match Timing

**Setting of Compare Match Flags A and B (CMFA, CMFB):** The CMFA and CMFB flags in TCSR are set to 1 by a compare match signal generated when the TCOR and TCNT values match. The compare match signal is generated at the last state in which the match is true, just before the timer counter is updated.

Therefore, when TCOR and TCNT match, the compare match signal is not generated until the next incrementation clock input. Figure 12.4 shows this timing.

Figure 12.4 Timing of CMF Setting

**Bit 3—Smart Card Data Transfer Direction (SDIR):** Selects the serial/parallel conversion format.

This bit is valid when 8-bit data is used as the transmit/receive format.

| Bit 3<br>SDIR | Description                             |                 |

|---------------|-----------------------------------------|-----------------|

| 0             | TDR contents are transmitted LSB-first  | (Initial value) |

|               | Receive data is stored in RDR LSB-first |                 |

| 1             | TDR contents are transmitted MSB-first  |                 |

|               | Receive data is stored in RDR MSB-first |                 |

**Bit 2—Smart Card Data Invert (SINV):** Specifies inversion of the data logic level. The SINV bit does not affect the logic level of the parity bit(s): parity bit inversion requires inversion of the  $O/\overline{E}$  bit in SMR.

| Bit 2<br>SINV | Description                                        |                 |

|---------------|----------------------------------------------------|-----------------|

| 0             | TDR contents are transmitted without modification  | (Initial value) |

|               | Receive data is stored in RDR without modification |                 |

| 1             | TDR contents are inverted before being transmitted |                 |

|               | Receive data is stored in RDR in inverted form     |                 |

Bit 1—Reserved: This bit cannot be modified and is always read as 1.

**Bit 0—Smart Card Interface Mode Select (SMIF):** When the smart card interface operates as a normal SCI, 0 should be written to this bit.

| Bit 0<br>SMIF | Description                                                     |                 |

|---------------|-----------------------------------------------------------------|-----------------|

| 0             | Operates as normal SCI (smart card interface function disabled) | (Initial value) |

| 1             | Smart card interface function enabled                           |                 |

# 14.4 SCI Interrupts

The SCI has four interrupt sources: the transmit-end interrupt (TEI) request, receive-error interrupt (ERI) request, receive-data-full interrupt (RXI) request, and transmit-data-empty interrupt (TXI) request. Table 14.12 shows the interrupt sources and their relative priorities. Individual interrupt sources can be enabled or disabled with the TIE, RIE, and TEIE bits in the SCR. Each kind of interrupt request is sent to the interrupt controller independently.

When the TDRE flag in SSR is set to 1, a TXI interrupt request is generated. When the TEND flag in SSR is set to 1, a TEI interrupt request is generated. A TXI interrupt can activate the DMAC<sup>\*</sup> or DTC to perform data transfer. The TDRE flag is cleared to 0 automatically when data transfer is performed by the DMAC<sup>\*</sup> or DTC. The DMAC<sup>\*</sup> and DTC cannot be activated by a TEI interrupt request.

When the RDRF flag in SSR is set to 1, an RXI interrupt request is generated. When the ORER, PER, or FER flag in SSR is set to 1, an ERI interrupt request is generated. An RXI interrupt can activate the DMAC<sup>\*</sup> or DTC to perform data transfer. The RDRF flag is cleared to 0 automatically when data transfer is performed by the DMAC<sup>\*</sup> or DTC. The DMAC<sup>\*</sup> and DTC cannot be activated by an ERI interrupt request.

Also note that the  $DMAC^*$  cannot be activated by an SCI channel 2 interrupt.

Note: \* The DMAC is not supported in the H8S/2321.

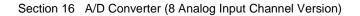

Figure 16.3 Example of A/D Converter Operation (Single Mode, Channel 1 Selected)

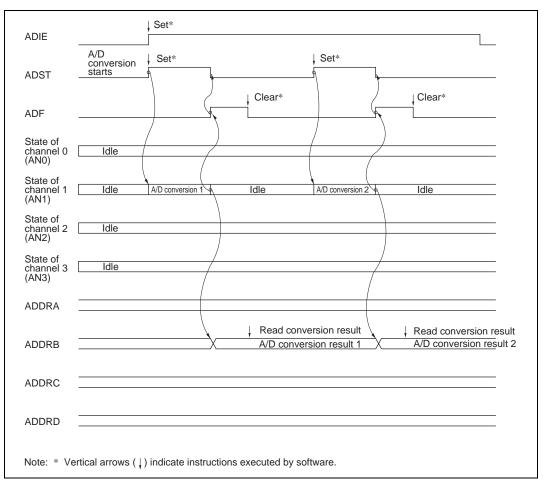

**Automatic SCI Bit Rate Adjustment:** When boot mode is initiated, the H8S/2329B F-ZTAT chip measures the low period of the asynchronous SCI communication data (H'00) transmitted continuously from the host. The SCI transmit/receive format should be set as follows: 8-bit data, 1 stop bit, no parity. The chip calculates the bit rate of the transmission from the host from the measured low period, and transmits one H'00 byte to the host to indicate the end of bit rate adjustment. The host should confirm that this adjustment end indication (H'00) has been received normally, and transmit one H'55 byte to the chip. If reception cannot be performed normally, initiate boot mode again (reset), and repeat the above operations. Depending on the host's transmission bit rate and the chip's system clock frequency, there will be a discrepancy between the bit rates of the host and the chip. To ensure correct SCI operation, the host's transfer bit rate should be set to 9,600 or 19,200 bps.

Table 19.10 shows typical host transfer bit rates and system clock frequencies for which automatic adjustment of the MCU's bit rate is possible. The boot program should be executed within this system clock range.

Figure 19.11 Automatic SCI Bit Rate Adjustment

| Table 19.10         System Clock Frequencies for which Automatic Adjustment of H8S/2329B |  |

|------------------------------------------------------------------------------------------|--|

| F-ZTAT Bit Rate is Possible                                                              |  |

| Host Bit Rate | System Clock Frequency for which Automatic Adjustment of H8S/2329B F-ZTAT Bit Rate is Possible |

|---------------|------------------------------------------------------------------------------------------------|

| 19,200 bps    | 16 MHz to 25 MHz                                                                               |

| 9,600 bps     | 8 MHz to 25 MHz                                                                                |

**On-Chip RAM Area Divisions in Boot Mode:** In boot mode, the 2-kbyte area from H'FF7C00 to H'FF83FF is reserved for use by the boot program, as shown in figure 19.12. The area to which the programming control program is transferred is H'FF8400 to H'FFFBFF. The boot program area can be used when the programming control program transferred into RAM enters the execution state. A stack area should be set up as required.

## Renesas

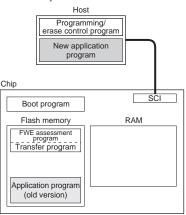

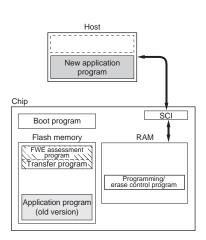

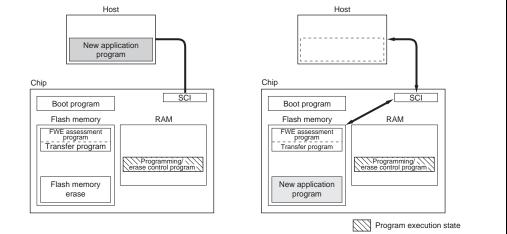

### User program mode

1. Initial state

(1) The FWE assessment program that confirms that the FWE pin has been driven high, and (2) the program that will transfer the programming/ erase control program to on-chip RAM should be written into the flash memory by the user beforehand. (3) The programming/erase control program should be prepared in the host or in the flash memory.

3. Flash memory initialization The programming/erase program in RAM is

executed, and the flash memory is initialized (to H'FF). Erasing can be performed in block units, but not in byte units.

2. Programming/erase control program transfer When the FWE pin is driven high, user software confirms this fact, executes the transfer program in the flash memory, and transfers the programming/erase control program to RAM.

4. Writing new application program Next, the new application program in the host is written into the erased flash memory blocks. Do not write to unerased blocks.

Figure 19.32 User Program Mode (Example)

### 19.13.8 Pin Configuration

The flash memory is controlled by means of the pins shown in tables 19.26.

| Pin Name           | Abbreviation | I/O    | Function                                   |

|--------------------|--------------|--------|--------------------------------------------|

| Reset              | RES          | Input  | Reset                                      |

| Flash write enable | FWE          | Input  | Flash program/erase protection by hardware |

| Mode 2             | MD2          | Input  | Sets MCU operating mode                    |

| Mode 1             | MD1          | Input  | Sets MCU operating mode                    |

| Mode 0             | MD0          | Input  | Sets MCU operating mode                    |

| Port 64            | P64          | Input  | Sets MCU operating mode in PROM mode       |

| Port 65            | P65          | Input  | Sets MCU operating mode in PROM mode       |

| Port 66            | P66          | Input  | Sets MCU operating mode in PROM mode       |

| Transmit data      | TxD1         | Output | Serial transmit data output                |

| Receive data       | RxD1         | Input  | Serial receive data input                  |

### Table 19.26 Flash Memory Pins

**Bit 2—Program-Verify (PV):** Selects program-verify mode transition or clearing. Do not set the SWE, ESU, PSU, EV, E, or P bit at the same time.

| Bit 2<br>PV | Description                       |                 |

|-------------|-----------------------------------|-----------------|

| 0           | Program-verify mode cleared       | (Initial value) |

| 1           | Transition to program-verify mode |                 |

|             | [Setting condition]               |                 |

|             | When FWE = 1 and SWE = 1          |                 |

**Bit 1—Erase (E):** Selects erase mode transition or clearing. Do not set the SWE, ESU, PSU, EV, PV, or P bit at the same time.

| Bit 1<br>E | Description                                |                 |

|------------|--------------------------------------------|-----------------|

| 0          | Erase mode cleared                         | (Initial value) |

| 1          | Transition to erase mode                   |                 |

|            | [Setting condition]                        |                 |

|            | When $FWE = 1$ , $SWE = 1$ , and $ESU = 1$ |                 |

**Bit 0—Program (P):** Selects program mode transition or clearing. Do not set the SWE, PSU, ESU, EV, PV, or E bit at the same time.

| Bit 0<br>P | Description                                |                 |

|------------|--------------------------------------------|-----------------|

| 0          | Program mode cleared                       | (Initial value) |

| 1          | Transition to program mode                 |                 |

|            | [Setting condition]                        |                 |

|            | When $FWE = 1$ , $SWE = 1$ , and $PSU = 1$ |                 |

| Block (Size)     | Address              |

|------------------|----------------------|

| EB0 (4 kbytes)   | H'000000 to H'000FFF |

| EB1 (4 kbytes)   | H'001000 to H'001FFF |

| EB2 (4 kbytes)   | H'002000 to H'002FFF |

| EB3 (4 kbytes)   | H'003000 to H'003FFF |

| EB4 (4 kbytes)   | H'004000 to H'004FFF |

| EB5 (4 kbytes)   | H'005000 to H'005FFF |

| EB6 (4 kbytes)   | H'006000 to H'006FFF |

| EB7 (4 kbytes)   | H'007000 to H'007FFF |

| EB8 (32 kbytes)  | H'008000 to H'00FFFF |

| EB9 (64 kbytes)  | H'010000 to H'01FFFF |

| EB10 (64 kbytes) | H'020000 to H'02FFFF |

| EB11 (64 kbytes) | H'030000 to H'03FFFF |

### Table 19.28 Flash Memory Erase Blocks

### 19.14.5 System Control Register 2 (SYSCR2)

| Bit         | :    | 7 | 6 | 5 | 4 | 3     | 2 | 1 | 0 |

|-------------|------|---|---|---|---|-------|---|---|---|

|             |      |   | _ | — |   | FLSHE | _ | — | — |

| Initial val | ue : | 0 | 0 | 0 | 0 | 0     | 0 | 0 | 0 |

| R/W         | :    | — | — | — | — | R/W   | — | — | — |

SYSCR2 is an 8-bit readable/writable register that performs on-chip flash memory control.

SYSCR2 is initialized to H'00 by a reset and in hardware standby mode.

SYSCR2 can only be used in the F-ZTAT versions. In the mask ROM versions this register will return an undefined value if read, and cannot be modified.

Bits 7 to 4—Reserved: These bits cannot be modified and are always read as 0.

### 22.1.2 DC Characteristics

### Table 22.2 DC Characteristics (H8S/2328, H8S/2327, H8S/2323)

Conditions:  $V_{CC} = 2.7 \text{ V}$  to 3.6 V,  $AV_{CC} = 2.7 \text{ V}$  to 3.6 V,  $V_{ref} = 2.7 \text{ V}$  to  $AV_{CC}$ ,  $V_{SS} = AV_{SS} = 0 \text{ V}^{*1}$ ,  $T_a = -20^{\circ}\text{C}$  to  $+75^{\circ}\text{C}$  (regular specifications),  $T_a = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  (widerange specifications)

| Item                  |                                                                                         | Symbol                      | Min                         | Тур | Max                        | Unit | Test<br>Conditions                                                                                            |

|-----------------------|-----------------------------------------------------------------------------------------|-----------------------------|-----------------------------|-----|----------------------------|------|---------------------------------------------------------------------------------------------------------------|

| Schmitt               | Ports 1, 2,                                                                             | V <sub>T</sub> <sup>-</sup> | $V_{\text{CC}} \times 0.2$  | _   | _                          | V    |                                                                                                               |

| trigger input voltage | P6 <sub>4</sub> to P6 <sub>7</sub>                                                      | V <sub>T</sub> <sup>+</sup> | _                           | —   | $V_{\text{CC}} \times 0.7$ | V    |                                                                                                               |

| vollage               | PA <sub>4</sub> to PA <sub>7</sub>                                                      | $V_T^+ - V_T^-$             | $V_{\text{CC}} \times 0.07$ | —   | _                          | V    |                                                                                                               |

|                       | Port 5 (when using $\overline{IRQ}$ )                                                   |                             |                             |     |                            |      |                                                                                                               |

| Input high<br>voltage | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                   | V <sub>IH</sub>             | $V_{CC} \times 0.9$         | —   | V <sub>CC</sub> + 0.3      | V    |                                                                                                               |

|                       | EXTAL                                                                                   | _                           | $V_{CC} \times 0.7$         | —   | $V_{CC} + 0.3$             | V    |                                                                                                               |

|                       | Ports 3, 5,<br>B to G, $P6_0$ to $P6_3$ ,<br>$PA_0$ to $PA_3$                           | _                           | 2.2                         | _   | V <sub>CC</sub> + 0.3      | V    | _                                                                                                             |

|                       | Port 4                                                                                  | _                           | 2.2                         | —   | $AV_{CC} + 0.3$            | V    |                                                                                                               |

| Input low<br>voltage  | $\overline{\text{RES}}, \overline{\text{STBY}}, \\ \text{MD}_2 \text{ to } \text{MD}_0$ | V <sub>IL</sub>             | -0.3                        |     | $V_{CC} \times 0.1$        | V    |                                                                                                               |

|                       | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                   | _                           | -0.3                        | _   | $V_{CC} 	imes 0.2$         | V    |                                                                                                               |

| Output high           | All output pins                                                                         | V <sub>OH</sub>             | $V_{CC}-0.5$                | —   | _                          | V    | I <sub>OH</sub> = -200 μA                                                                                     |

| voltage               |                                                                                         |                             | V <sub>cc</sub> – 1.0       | —   | _                          | V    | $I_{OH} = -1 \text{ mA}$                                                                                      |

| Output low voltage    | All output pins                                                                         | V <sub>OL</sub>             | —                           | —   | 0.4                        | V    | I <sub>OL</sub> = 1.6 mA                                                                                      |

| Input                 | RES                                                                                     | I <sub>in</sub>             | _                           | _   | 10.0                       | μA   | V <sub>in</sub> = 0.5 V to                                                                                    |

| leakage<br>current    | STBY, NMI,<br>MD <sub>2</sub> to MD <sub>0</sub>                                        | _                           | _                           | —   | 1.0                        | μΑ   | <sup></sup> V <sub>CC</sub> - 0.5 V                                                                           |

|                       | Port 4                                                                                  | _                           | _                           | _   | 1.0                        | μA   | $\label{eq:Vin} \begin{array}{l} V_{\text{in}} = 0.5 \ V \ \text{to} \\ AV_{\text{CC}} - 0.5 \ V \end{array}$ |

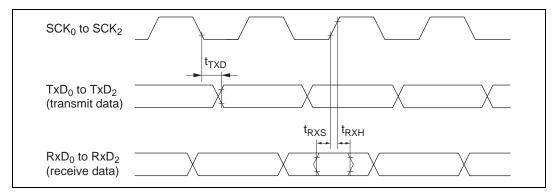

Figure 22.29 SCI Input/Output Timing (Synchronous Mode)

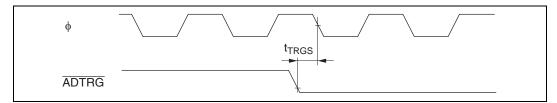

Figure 22.30 A/D Converter External Trigger Input Timing

| Address              | Register<br>Name | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Module<br>Name              | Data<br>Bus<br>Width |

|----------------------|------------------|---------|---------|---------|---------|---------|---------|---------|---------|-----------------------------|----------------------|

| H'FF06               | DMABCRH          | FAE1    | FAE0    | SAE1    | SAE0    | DTA1B   | DTA1A   | DTA0B   | DTA0A   | Short<br>address<br>mode    |                      |

|                      |                  | FAE1    | FAE0    | _       | _       | DTA1    | _       | DTA0    | _       | Full<br>address<br>mode     | _                    |

| H'FF07               | DMABCRL          | DTE1B   | DTE1A   | DTE0B   | DTE0A   | DTIE1B  | DTIE1A  | DTIE0B  | DTIE0A  | Short<br>address<br>mode    | _                    |

|                      |                  | DTME1   | DTE1    | DTME0   | DTE0    | DTIE1B  | DTIE1A  | DTIE0B  | DTIE0A  | Full<br>address<br>mode     | _                    |

| H'FF2C               | ISCRH            | IRQ7SCB | IRQ7SCA | IRQ6SCB | IRQ6SCA | IRQ5SCB | IRQ5SCA | IRQ4SCB | IRQ4SCA | Interrupt                   | 8 bits               |

| H'FF2D               | ISCRL            | IRQ3SCB | IRQ3SCA | IRQ2SCB | IRQ2SCA | IRQ1SCB | IRQ1SCA | IRQ0SCB | IRQ0SCA | controller                  |                      |

| H'FF2E               | IER              | IRQ7E   | IRQ6E   | IRQ5E   | IRQ4E   | IRQ3E   | IRQ2E   | IRQ1E   | IRQ0E   | -                           |                      |

| H'FF2F               | ISR              | IRQ7F   | IRQ6F   | IRQ5F   | IRQ4F   | IRQ3F   | IRQ2F   | IRQ1F   | IRQ0F   | -                           |                      |

| H'FF30<br>to         | DTCER            | DTCE7   | DTCE6   | DTCE5   | DTCE4   | DTCE3   | DTCE2   | DTCE1   | DTCE0   | DTC                         | 8 bits               |

| H'FF35               |                  |         |         |         |         |         |         |         |         | -                           |                      |

| H'FF37               | DTVECR           | SWDTE   | DTVEC6  | DTVEC5  | DTVEC4  | DTVEC3  | DTVEC2  | DTVEC1  | DTVEC0  |                             |                      |

| H'FF38               | SBYCR            | SSBY    | STS2    | STS1    | STS0    | OPE     | _       | _       | IRQ37S  | Power-<br>down<br>mode      | 8 bits               |

| H'FF39               | SYSCR            | _       | _       | INTM1   | INTM0   | NMIEG   | LWROD   | IRQPAS  | RAME    | MCU                         | 8 bits               |

| H'FF3A               | SCKCR            | PSTOP   | _       | DIV     | _       | _       | SCK2    | SCK1    | SCK0    | Clock<br>pulse<br>generator | 8 bits               |

| H'FF3B               | MDCR             | _       | _       | _       | _       | _       | MDS2    | MDS1    | MDS0    | MCU                         | 8 bits               |

| H'FF3C               | MSTPCRH          | MSTP15  | MSTP14  | MSTP13  | MSTP12  | MSTP11  | MSTP10  | MSTP9   | MSTP8   | Power-                      | 8 bits               |

| H'FF3D               | MSTPCRL          |         | MSTP6   | MSTP5   | MSTP4   | MSTP3   | MSTP2   | MSTP1   | MSTP0   | down<br>mode                |                      |

| H'FF42               | SYSCR2*4         | _       | _       | _       | _       | FLSHE   | _       | _       | —       | MCU                         | 8 bits               |

| H'FF44               | Reserved         | _       | —       | _       | _       | _       | —       | _       | —       | Reserved                    | —                    |

| HFF45                | PFCR1            | _       | —       | —       | —       | A23E    | A22E    | A21E    | A20E    | Port                        | 8 bits               |

| H'FF46               | PCR              | G3CMS1  | G3CMS0  | G2CMS1  | G2CMS0  | G1CMS1  | G1CMS0  | G0CMS1  | G0CMS0  | PPG                         | 8 bits               |

| H'FF47               | PMR              | G3INV   | G2INV   | G1INV   | G0INV   | G3NOV   | G2NOV   | G1NOV   | G0NOV   | _                           |                      |

| H'FF48               | NDERH            | NDER15  | NDER14  | NDER13  | NDER12  | NDER11  | NDER10  | NDER9   | NDER8   | _                           |                      |

| H'FF49               | NDERL            | NDER7   | NDER6   | NDER5   | NDER4   | NDER3   | NDER2   | NDER1   | NDER0   | _                           |                      |

| H'FF4A               | PODRH            | POD15   | POD14   | POD13   | POD12   | POD11   | POD10   | POD9    | POD8    | _                           |                      |

| H'FF4B               | PODRL            | POD7    | POD6    | POD5    | POD4    | POD3    | POD2    | POD1    | POD0    | _                           |                      |

| H'FF4C <sup>*6</sup> | NDRH             | NDR15   | NDR14   | NDR13   | NDR12   | NDR11   | NDR10   | NDR9    | NDR8    | -                           |                      |

| H'FF4D*6             | NDRL             | NDR7    | NDR6    | NDR5    | NDR4    | NDR3    | NDR2    | NDR1    | NDR0    | -                           |                      |

| H'FF4E <sup>*6</sup> | NDRH             | _       | _       | _       | —       | NDR11   | NDR10   | NDR9    | NDR8    | _                           |                      |

| H'FF4F <sup>*6</sup> | NDRL             | _       |         |         |         | NDR3    | NDR2    | NDR1    | NDR0    |                             |                      |

Rev.6.00 Sep. 27, 2007 Page 1060 of 1268 REJ09B0220-0600

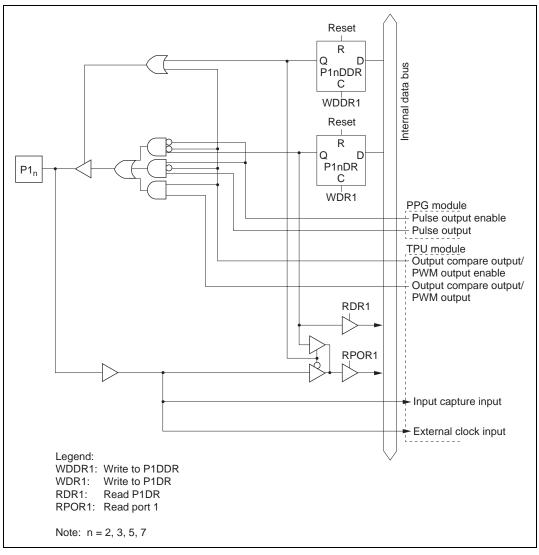

Figure C.1 (b) Port 1 Block Diagram (Pins P1<sub>2</sub>, P1<sub>3</sub>, P1<sub>5</sub>, and P1<sub>7</sub>)

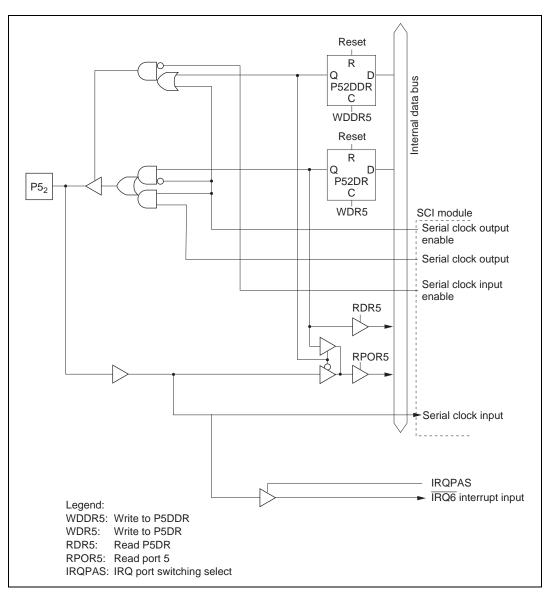

Figure C.5 (c) Port 5 Block Diagram (Pin P5<sub>2</sub>)