Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                      |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 20MHz                                                                         |

| Connectivity               | SCI, SmartCard                                                                |

| Peripherals                | POR, PWM, WDT                                                                 |

| Number of I/O              | 86                                                                            |

| Program Memory Size        | -                                                                             |

| Program Memory Type        | ROMIess                                                                       |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                   |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                           |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 120-TQFP                                                                      |

| Supplier Device Package    | 120-TQFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/d12321vte20v |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Item                                       | Page | Revision (See Manual for Details)                                                                                                           |  |  |  |  |  |  |

|--------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 22.2.6 Flash Memory                        | 978  | Notes added                                                                                                                                 |  |  |  |  |  |  |

| Characteristics                            |      | 7. The minimum number of rewrites after which all                                                                                           |  |  |  |  |  |  |

| Table 22.22 Flash<br>Memory Characteristic | s    | characteristics are guaranteed. (The guaranteed range is one to min. rewrites.)                                                             |  |  |  |  |  |  |

|                                            |      | <ol> <li>Reference value at 25°C. (This is a general indication of the<br/>number of rewrites possible under normal conditions.)</li> </ol> |  |  |  |  |  |  |

|                                            |      | <ol> <li>The data retention characteristics within the specified range,<br/>including min. rewrites.</li> </ol>                             |  |  |  |  |  |  |

| Appendix F Package<br>Dimensions           | 1267 | Figure replaced                                                                                                                             |  |  |  |  |  |  |

| Figure F.1 TFP-120<br>Package Dimensions   |      |                                                                                                                                             |  |  |  |  |  |  |

| Figure F.2 FP-128B<br>Package Dimensions   | 1268 | Figure replaced                                                                                                                             |  |  |  |  |  |  |

All trademarks and registered trademarks are the property of their respective owners.

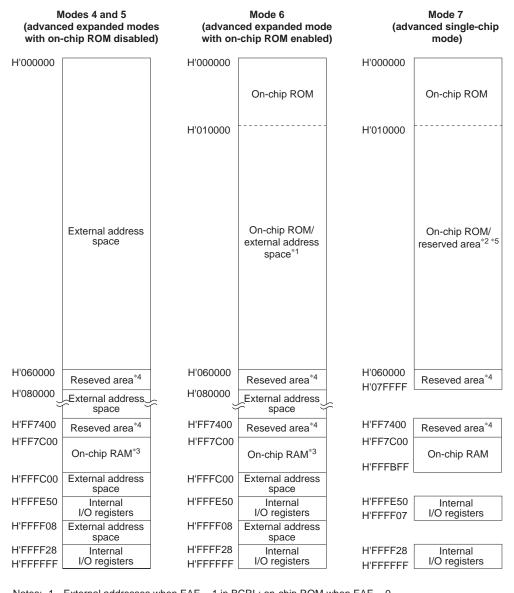

Notes: 1. External addresses when EAE = 1 in BCRL; on-chip ROM when EAE = 0.

2. Reserved area when EAE = 1 in BCRL; on-chip ROM when EAE = 0.

3. External addresses can be accessed by clearing the RAME bit in SYSCR to 0.

4. Access to the reserved areas H'060000 to H'07FFFF and H'FF7400 to H'FF7BFF is prohibited.

5. Do not access a reserved area.

### Figure 3.1 (b) H8S/2329B Memory Map in Each Operating Mode

Bits 3 and 2—Area 1 Wait Control 1 and 0 (W11, W10): These bits select the number of program wait states when area 1 in external space is accessed while the AST1 bit in ASTCR is set to 1.

| Bit 3<br>W11 | Bit 2<br>W10 | Description                                                                           |

|--------------|--------------|---------------------------------------------------------------------------------------|

| 0            | 0            | Program wait not inserted when external space area 1 is accessed                      |

|              | 1            | 1 program wait state inserted when external space area 1 is accessed                  |

| 1            | 0            | 2 program wait states inserted when external space area 1 is accessed                 |

|              | 1            | 3 program wait states inserted when external space area 1 is accessed (Initial value) |

Bits 1 and 0—Area 0 Wait Control 1 and 0 (W01, W00): These bits select the number of program wait states when area 0 in external space is accessed while the AST0 bit in ASTCR is set to 1.

| Bit 1<br>W01 | Bit 0<br>W00 | Description                                                                           |

|--------------|--------------|---------------------------------------------------------------------------------------|

| 0            | 0            | Program wait not inserted when external space area 0 is accessed                      |

|              | 1            | 1 program wait state inserted when external space area 0 is accessed                  |

| 1            | 0            | 2 program wait states inserted when external space area 0 is accessed                 |

|              | 1            | 3 program wait states inserted when external space area 0 is accessed (Initial value) |

#### **Bus Control Register H (BCRH)** 6.2.4

| Bit             | :                             | 7          | 6         | 5       | 4      | 3      | 2      | 1      | 0      |

|-----------------|-------------------------------|------------|-----------|---------|--------|--------|--------|--------|--------|

|                 |                               | ICIS1      | ICIS0     | BRSTRM  | BRSTS1 | BRSTS0 | RMTS2* | RMTS1* | RMTS0* |

| Initial value : |                               | 1          | 1         | 0       | 1      | 0      | 0      | 0      | 0      |

| R/W             | R/W : R/W R/W R/W R/W R/W R/W |            |           |         |        |        |        |        |        |

| Note: * Thi     | is bit is                     | s reserved | in the H8 | S/2321. |        |        |        |        |        |

Ν

BCRH is an 8-bit readable/writable register that selects enabling or disabling of idle cycle insertion, and the memory interface for areas 2 to 5 and area 0.

BCRH is initialized to H'D0 by a reset and in hardware standby mode. It is not initialized in software standby mode.

| Interrupt Source             | Origin of<br>Interrupt<br>Source | Vector<br>Number | Vector<br>Address | DTCE <sup>*1</sup> | Priority |

|------------------------------|----------------------------------|------------------|-------------------|--------------------|----------|

| RXI0 (receive-data-full 0)   | SCI                              | 81               | H'04A2            | DTCEE3             | High     |

| TXI0 (transmit-data-empty 0) | channel 0                        | 82               | H'04A4            | DTCEE2             | _ ↑      |

| RXI1 (receive-data-full 1)   | SCI                              | 85               | H'04AA            | DTCEE1             | _        |

| TXI1 (transmit-data-empty 1) | channel 1                        | 86               | H'04AC            | DTCEE0             | _        |

| RXI2 (receive-data-full 2)   | SCI                              | 89               | H'04B2            | DTCEF7             | _        |

| TXI2 (transmit-data-empty 2) | channel 2                        | 90               | H'04B4            | DTCEF6             | Low      |

Notes: 1. DTCE bits with no corresponding interrupt are reserved, and should be written with 0.

2. The DMAC is not supported in the H8S/2321.

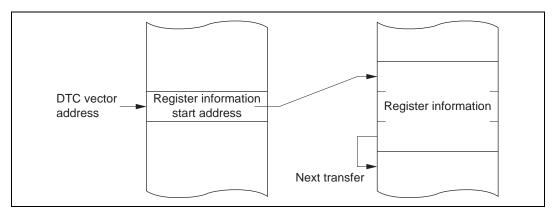

Figure 8.4 Correspondence between DTC Vector Address and Register Information

### 9.3.2 Register Configuration

Table 9.4 shows the port 2 register configuration.

### Table 9.4Port 2 Registers

| Name                           | Abbreviation | R/W | Initial Value | Address* |

|--------------------------------|--------------|-----|---------------|----------|

| Port 2 data direction register | P2DDR        | W   | H'00          | H'FEB1   |

| Port 2 data register           | P2DR         | R/W | H'00          | H'FF61   |

| Port 2 register                | PORT2        | R   | Undefined     | H'FF51   |

Note: \* Lower 16 bits of the address.

### Port 2 Data Direction Register (P2DDR)

| Bit        | Bit : 7 6<br>P27DDR P26DDR P2 |        | 5      | 4      | 3      | 2      | 1      | 0      |        |

|------------|-------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|

|            |                               | P27DDR | P26DDR | P25DDR | P24DDR | P23DDR | P22DDR | P21DDR | P20DDR |

| Initial va | lue :                         | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W        | :                             | W      | W      | W      | W      | W      | W      | W      | W      |

P2DDR is an 8-bit write-only register, the individual bits of which specify input or output for the pins of port 2. P2DDR cannot be read; if it is, an undefined value will be read.

Setting a P2DDR bit to 1 makes the corresponding port 2 pin an output pin, while clearing the bit to 0 makes the pin an input pin.

P2DDR is initialized to H'00 by a reset, and in hardware standby mode. It retains its prior state in software standby mode.

### 9.9.4 MOS Input Pull-Up Function

Port B has a built-in MOS input pull-up function that can be controlled by software. This MOS input pull-up function can be used in modes 6 and 7, and can be specified as on or off on an individual bit basis.

When a PBDDR bit is cleared to 0 in mode 6 or 7, setting the corresponding PBPCR bit to 1 turns on the MOS input pull-up for that pin.

The MOS input pull-up function is in the off state after a reset, and in hardware standby mode. The prior state is retained in software standby mode.

Table 9.17 summarizes the MOS input pull-up states.

### Table 9.17MOS Input Pull-Up States (Port B)

| Modes | Reset | Hardware<br>Standby Mode | Software<br>Standby Mode | In Other<br>Operations |

|-------|-------|--------------------------|--------------------------|------------------------|

| 4, 5  | Off   | Off                      | Off                      | Off                    |

| 6, 7  |       |                          | On/off                   | On/off                 |

Legend:

Off: MOS input pull-up is always off.

On/off: On when PBDDR = 0 and PBPCR = 1; otherwise off.

Bits 2 to 0—Reserved: These bits are always read as 0.

### System Control Register (SYSCR)

| Bit         | :    | 7   | 6 | 5     | 4     | 3     | 2     | 1      | 0    |

|-------------|------|-----|---|-------|-------|-------|-------|--------|------|

|             |      | _   | — | INTM1 | INTM0 | NMIEG | LWROE | IRQPAS | RAME |

| Initial val | ue : | 0   | 0 | 0     | 0     | 0     | 0     | 0      | 1    |

| R/W         | :    | R/W | — | R/W   | R/W   | R/W   | R/W   | R/W    | R/W  |

SYSCR is an 8-bit readable/writable register that selects the interrupt control mode, controls the  $\overline{LWR}$  pin, switches the  $\overline{IRQ}_4$  to  $\overline{IRQ}_7$  input pins, and selects the detected edge for NMI. SYSCR is initialized to H'01 by a reset, and in hardware standby mode. It is not initialized in software standby mode.

**Bits 5 and 4—Interrupt Control Mode 1 and 0 (INTM1, INTM0):** These bits select either of two interrupt control modes for the interrupt controller. For details, see section 5, Interrupt Controller.

**Bit 3—NMI Edge Select (NMIEG):** Selects the input edge for the NMI pin. For details, see section 5, Interrupt Controller.

**Bit 2—LWR Output Disable (LWROD):** Enables or disables  $\overline{LWR}$  output. This bit is valid in modes 4 to 6.

| Bit 2<br>LWROD | Description                                                                      |                 |

|----------------|----------------------------------------------------------------------------------|-----------------|

| 0              | $PF_3$ is designated as $\overline{LWR}$ output pin                              | (Initial value) |

| 1              | $PF_3$ is designated as I/O port, and does not function as $\overline{LWR}$ outp | ut pin          |

**Bit 1—IRQ Port Switching Select (IRQPAS):** Selects switching of input pins for  $\overline{IRQ}_4$  to  $\overline{IRQ}_7$ . For details, see section 9.6, Port 5.

**Bit 0—RAM Enable (RAME):** Enables or disables on-chip RAM. For details, see section 18, RAM.

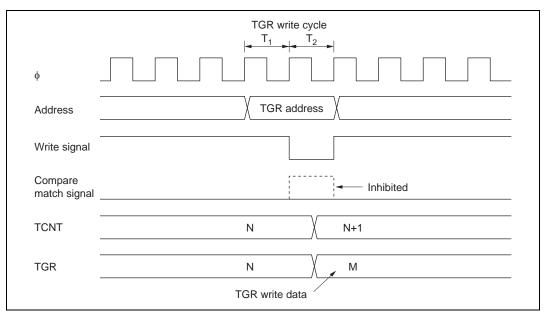

**Contention between TGR Write and Compare Match:** If a compare match occurs in the  $T_2$  state of a TGR write cycle, the TGR write takes precedence and the compare match signal is inhibited. A compare match does not occur even if the same value as before is written.

Figure 10.51 shows the timing in this case.

Figure 10.51 Contention between TGR Write and Compare Match

|                      |   | φ = 18 MHz |              |   | φ = 19.6608 MHz |              |   | φ = 20 ľ |              | φ = 25 MHz |     |              |

|----------------------|---|------------|--------------|---|-----------------|--------------|---|----------|--------------|------------|-----|--------------|

| Bit Rate<br>(bits/s) | n | N          | Error<br>(%) | n | N               | Error<br>(%) | n | N        | Error<br>(%) | n          | N   | Error<br>(%) |

| 110                  | 3 | 79         | -0.12        | 3 | 86              | 0.31         | 3 | 88       | -0.25        | 3          | 110 | -0.02        |

| 150                  | 2 | 233        | 0.16         | 2 | 255             | 0.00         | 3 | 64       | 0.16         | 3          | 80  | 0.47         |

| 300                  | 2 | 116        | 0.16         | 2 | 127             | 0.00         | 2 | 129      | 0.16         | 2          | 162 | -0.15        |

| 600                  | 1 | 233        | 0.16         | 1 | 255             | 0.00         | 2 | 64       | 0.16         | 2          | 80  | 0.47         |

| 1200                 | 1 | 116        | 0.16         | 1 | 127             | 0.00         | 1 | 129      | 0.16         | 1          | 162 | -0.15        |

| 2400                 | 0 | 233        | 0.16         | 0 | 255             | 0.00         | 1 | 64       | 0.16         | 1          | 80  | 0.47         |

| 4800                 | 0 | 116        | 0.16         | 0 | 127             | 0.00         | 0 | 129      | 0.16         | 0          | 162 | -0.15        |

| 9600                 | 0 | 58         | -0.69        | 0 | 63              | 0.00         | 0 | 64       | 0.16         | 0          | 80  | 0.47         |

| 19200                | 0 | 28         | 1.02         | 0 | 31              | 0.00         | 0 | 32       | -1.36        | 0          | 40  | -0.76        |

| 31250                | 0 | 17         | 0.00         | 0 | 19              | -1.70        | 0 | 19       | 0.00         | 0          | 24  | 1.00         |

| 38400                | 0 | 14         | -2.34        | 0 | 15              | 0.00         | 0 | 15       | 1.73         | 0          | 19  | 1.73         |

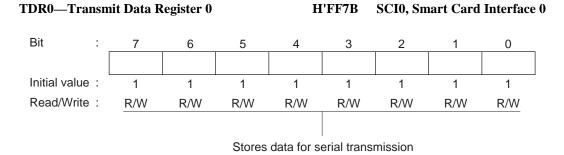

### Section 14 Serial Communication Interface (SCI)

In serial transmission, the SCI operates as described below.

- [1] The SCI monitors the TDRE flag in SSR, and if is 0, recognizes that data has been written to TDR, and transfers the data from TDR to TSR.

- [2] After transferring data from TDR to TSR, the SCI sets the TDRE flag to 1 and starts transmission.

If the TIE bit is set to 1 at this time, a transmit-data-empty interrupt (TXI) is generated.

The serial transmit data is sent from the TxD pin in the following order.

[a] Start bit:

One 0-bit is output.

[b] Transmit data:

8-bit or 7-bit data is output in LSB-first order.

[c] Multiprocessor bit

One multiprocessor bit (MPBT value) is output.

[d] Stop bit(s):

One or two 1-bits (stop bits) are output.

[e] Mark state:

1 is output continuously until the start bit that starts the next transmission is sent.

[3] The SCI checks the TDRE flag at the timing for sending the stop bit.

If the TDRE flag is cleared to 0, data is transferred from TDR to TSR, the stop bit is sent, and then serial transmission of the next frame is started.

If the TDRE flag is set to 1, the TEND flag in SSR is set to 1, the stop bit is sent, and then the mark state is entered in which 1 is output continuously. If the TEIE bit in SCR is set to 1 at this time, a transmit-end interrupt (TEI) request is generated.

The operation sequence is as follows.

- [1] When the data line is not in use it is in the high-impedance state, and is fixed high with a pullup resistor.

- [2] The transmitting station starts transfer of one frame of data. The data frame starts with a start bit (Ds, low-level), followed by 8 data bits (D0 to D7) and a parity bit (Dp).

- [3] With the smart card interface, the data line then returns to the high-impedance state. The data line is pulled high with a pull-up resistor.

- [4] The receiving station carries out a parity check.

If there is no parity error and the data is received normally, the receiving station waits for reception of the next data.

If a parity error occurs, however, the receiving station outputs an error signal (DE, low-level) to request retransmission of the data. After outputting the error signal for the prescribed length of time, the receiving station places the signal line in the high-impedance state again. The signal line is pulled high again by a pull-up resistor.

[5] If the transmitting station does not receive an error signal, it proceeds to transmit the next data frame.

If it does receive an error signal, however, it returns to step [2] and retransmits the data in which the error occurred.

Block Transfer Mode: The operation sequence in block transfer mode is as follows.

- [1] When the data line is not in use it is in the high-impedance state, and is fixed high with a pullup resistor.

- [2] The transmitting station starts transfer of one frame of data. The data frame starts with a start bit (Ds, low-level), followed by 8 data bits (D0 to D7) and a parity bit (Dp).

- [3] With the smart card interface, the data line then returns to the high-impedance state. The data line is pulled high with a pull-up resistor.

- [4] The receiving station carries out a parity check, but does not output an error signal even if an error has occurred. Since subsequent receive operations cannot be carried out if an error occurs, the error flag must be cleared to 0 before the parity bit for the next frame is received.

- [5] The transmitting station proceeds to transmit the next data frame.

# Renesas

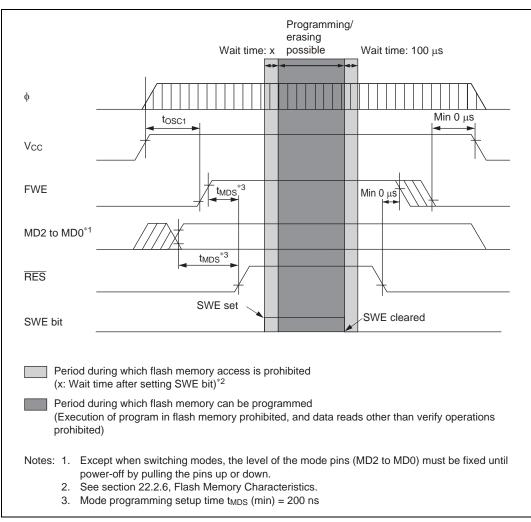

# 19.7 Programming/Erasing Flash Memory

In the on-board programming modes, flash memory programming and erasing is performed by software, using the CPU. There are four flash memory operating modes: program mode, erase mode, program-verify mode, and erase-verify mode. Transitions to these modes can be made by setting the PSU, ESU, P, E, PV, and EV bits in FLMCR1.

The flash memory cannot be read while being programmed or erased. Therefore, the program that controls flash memory programming/erasing (the programming control program) should be located and executed in on-chip RAM or external memory. When the program is located in external memory, an instruction for programming the flash memory and the following instruction should be located in on-chip RAM. The DMAC or DTC should not be activated before or after the instruction for programming the flash memory is executed.

2. Perform programming in the erased state. Do not perform additional programming on previously programmed addresses.

### 19.7.1 Program Mode

Follow the procedure shown in the program/program-verify flowchart in figure 19.14 to write data or programs to flash memory. Performing program operations according to this flowchart will enable data or programs to be written to flash memory without subjecting the device to voltage stress or sacrificing program data reliability. Programming should be carried out 128 bytes at a time.

For the wait times (x, y, z1, z2, z3  $\alpha$ ,  $\beta$ ,  $\gamma$ ,  $\varepsilon$ ,  $\eta$ , and  $\theta$ ) after bits are set or cleared in flash memory control register 1 (FLMCR1) and the maximum number of programming operations (N), see section 22.2.6, Flash Memory Characteristics.

Following the elapse of (x)  $\mu$ s or more after the SWE bit is set to 1 in flash memory control register 1 (FLMCR1), 128-byte program data is stored in the program data area and reprogram data area, and the 128-byte data in the reprogram data area is written consecutively to the write addresses. The lower 8 bits of the first address written to must be H'00 or H'80. 128 consecutive byte data transfers are performed. The program address and program data are latched in the flash memory. A 128-byte data transfer must be performed even if writing fewer than 128 bytes; in this case, H'FF data must be written to the extra addresses.

Next, the watchdog timer is set to prevent overprogramming in the event of program runaway, etc. Set a value greater than  $(y + z^2 + \alpha + \beta) \mu s$  as the WDT overflow period. After this, preparation for program mode (program setup) is carried out by setting the PSU bit in FLMCR1, and after the

Notes: 1. Operation is not guaranteed if setting/resetting of the SWE, ESU, PSU, EV, PV, E, and P bits in FLMCR1 is executed by a program in flash memory.

|                   | Number<br>of Cycles | 1st Cycle |         |      | 2nd Cycle |         |      |

|-------------------|---------------------|-----------|---------|------|-----------|---------|------|

| Command Name      |                     | Mode      | Address | Data | Mode      | Address | Data |

| Memory read mode  | 1 + n               | Write     | Х       | H'00 | Read      | RA      | Dout |

| Auto-program mode | 129                 | Write     | Х       | H'40 | Write     | PA      | Din  |

| Auto-erase mode   | 2                   | Write     | Х       | H'20 | Write     | Х       | H'20 |

| Status read mode  | 2                   | Write     | Х       | H'71 | Write     | Х       | H'71 |

#### Table 19.36 PROM Mode Commands

Legend:

RA: Read address

PA: Program address

Notes: 1. In auto-program mode, 129 cycles are required for command writing by a simultaneous 128-byte write.

2. In memory read mode, the number of cycles depends on the number of address write cycles (n).

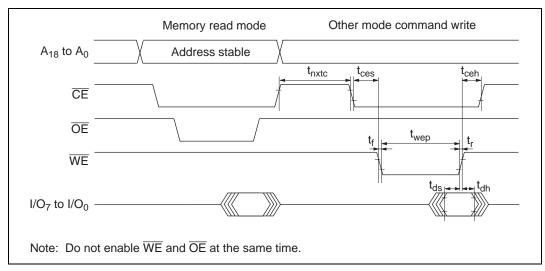

### 19.20.4 Memory Read Mode

- After the end of an auto-program, auto-erase, or status read operation, the command wait state is entered. To read memory contents, a transition must be made to memory read mode by means of a command write before the read is executed.

- Command writes can be performed in memory read mode, just as in the command wait state.

- Once memory read mode has been entered, consecutive reads can be performed.

- After power-on, memory read mode is entered.

#### Table 19.38 AC Characteristics when Entering Another Mode from Memory Read Mode

Conditions:  $V_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}$ ,  $V_{SS} = 0 \text{ V}$ ,  $T_a = 25^{\circ}C \pm 5^{\circ}C$

| Item                | Symbol            | Min | Max | Unit |  |

|---------------------|-------------------|-----|-----|------|--|

| Command write cycle | t <sub>nxtc</sub> | 20  | —   | μs   |  |

| CE hold time        | t <sub>ceh</sub>  | 0   | —   | ns   |  |

| CE setup time       | t <sub>ces</sub>  | 0   | —   | ns   |  |

| Data hold time      | t <sub>dh</sub>   | 50  | —   | ns   |  |

| Data setup time     | t <sub>ds</sub>   | 50  | —   | ns   |  |

| Write pulse width   | t <sub>wep</sub>  | 70  | _   | ns   |  |

| WE rise time        | t <sub>r</sub>    | _   | 30  | ns   |  |

| WE fall time        | t <sub>f</sub>    | _   | 30  | ns   |  |

Figure 19.49 Timing Waveforms when Entering Another Mode from Memory Read Mode

# Figure 19.56 Power-On/Off Timing (Boot Mode)

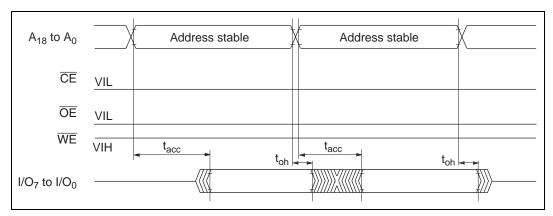

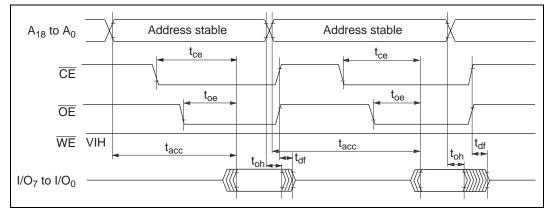

#### Table 19.60 AC Characteristics in Memory Read Mode

Conditions:  $V_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}$ ,  $V_{SS} = 0 \text{ V}$ ,  $T_a = 25^{\circ}C \pm 5^{\circ}C$

| Item                      | Symbol           | Min | Max | Unit |  |

|---------------------------|------------------|-----|-----|------|--|

| Access time               | t <sub>acc</sub> | _   | 20  | μs   |  |

| CE output delay time      | t <sub>ce</sub>  | —   | 150 | ns   |  |

| OE output delay time      | t <sub>oe</sub>  | —   | 150 | ns   |  |

| Output disable delay time | t <sub>df</sub>  | _   | 100 | ns   |  |

| Data output hold time     | t <sub>oh</sub>  | 5   | _   | ns   |  |

Figure 19.80 Timing Waveforms for CE/OE Enable State Read

Figure 19.81 Timing Waveforms for CE/OE Clocked Read

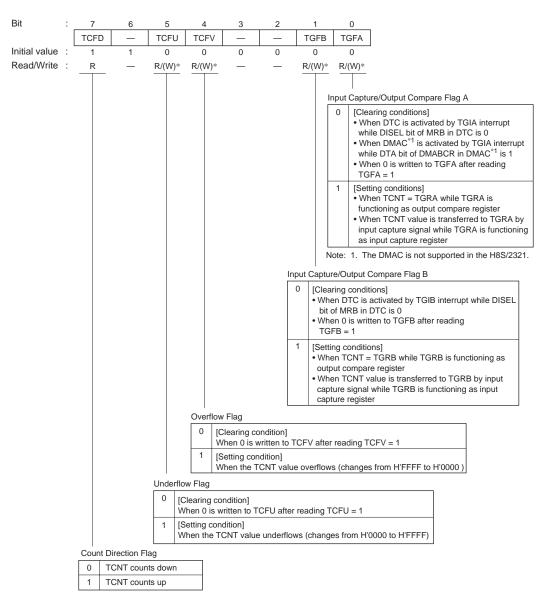

TPU<sub>2</sub>

H'FFF5

TSR2—Timer Status Register 2

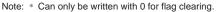

Figure C.3 (c) Port 3 Block Diagram (Pins P3<sub>4</sub> and P3<sub>5</sub>)

Rev.6.00 Sep. 27, 2007 Page 1228 of 1268 REJ09B0220-0600

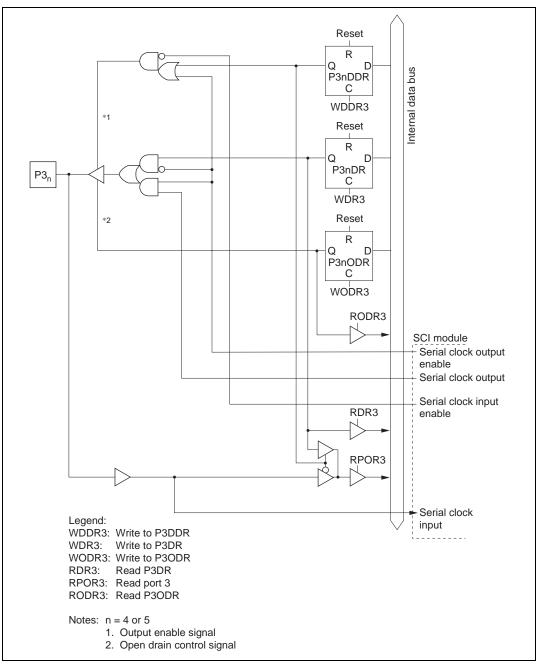

Figure C.12 (g) Port F Block Diagram (Pin PF<sub>6</sub>)