Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                      |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 25MHz                                                                         |

| Connectivity               | SCI, SmartCard                                                                |

| Peripherals                | POR, PWM, WDT                                                                 |

| Number of I/O              | 86                                                                            |

| Program Memory Size        | -                                                                             |

| Program Memory Type        | ROMIess                                                                       |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                   |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                           |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 120-TQFP                                                                      |

| Supplier Device Package    | 120-TQFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/d12321vte25v |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

H8S/2329 Group, H8S/2328 Group Manuals:

| Document Title                                   | Document No. |

|--------------------------------------------------|--------------|

| H8S/2329 Group, H8S/2328 Group Hardware Manual   | This manual  |

| H8S/2600 Series, H8S/2000 Series Software Manual | REJ09B0139   |

User's Manuals for Development Tools:

| Document Title                                                                                                     | Document No. |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------|--------------|--|--|--|--|--|--|

| H8S, H8S/300 Series C/C++ Compiler, Assembler, Optimized Linkage<br>Editor Compiler Package Ver.6.01 User's Manual | REJ10B0161   |  |  |  |  |  |  |

| H8S, H8S/300 Series Simulator/Debugger (for Windows) User's Manual                                                 | ADE-702-037  |  |  |  |  |  |  |

| High-performance Embedded Workshop (for Windows 95/98 and Windows ADE-702-201 NT 4.0) User's Manual                |              |  |  |  |  |  |  |

| Application Notes:                                                                                                 |              |  |  |  |  |  |  |

| Document Title                              | Document No. |

|---------------------------------------------|--------------|

| H8S Series Technical Q & A Application Note | REJ05B0397   |

## Section 1 Overview

## 1.1 Overview

The H8S/2329 Group and H8S/2328 Group are series of microcomputers (MCUs: microcomputer units), built around the H8S/2000 CPU, employing Renesas' proprietary architecture, and equipped with supporting functions on-chip.

The H8S/2000 CPU has an internal 32-bit architecture, is provided with sixteen 16-bit general registers and a concise, optimized instruction set designed for high-speed operation, and can address a 16-Mbyte linear address space. The instruction set is upward-compatible with H8/300 and H8/300H CPU instructions at the object-code level, facilitating migration from the H8/300, H8/300L, or H8/300H Series.

On-chip supporting functions required for system configuration include DMA controller (DMAC)<sup>\*1</sup> and data transfer controller (DTC) bus masters, ROM and RAM, a 16-bit timer-pulse unit (TPU), programmable pulse generator (PPG), 8-bit timer, watchdog timer (WDT), serial communication interface (SCI), A/D converter, D/A converter, and I/O ports.

A high-functionality bus controller is also provided, enabling fast and easy connection of DRAM and other kinds of memory.

Single-power-supply flash memory (F-ZTAT<sup>TM\*2</sup>) and mask ROM versions are available, providing a quick and flexible response to conditions from ramp-up through full-scale volume production, even for applications with frequently changing specifications. ROM is connected to the CPU via a 16-bit data bus, enabling both byte and word data to be accessed in one state. Instruction fetching is thus speeded up, and processing speed increased.

The features of the H8S/2329 Group is shown in table 1.1.

Notes: 1. The DMAC is not supported in the H8S/2321.

2. F-ZTAT is a trademark of Renesas Technology Corp.

## Renesas

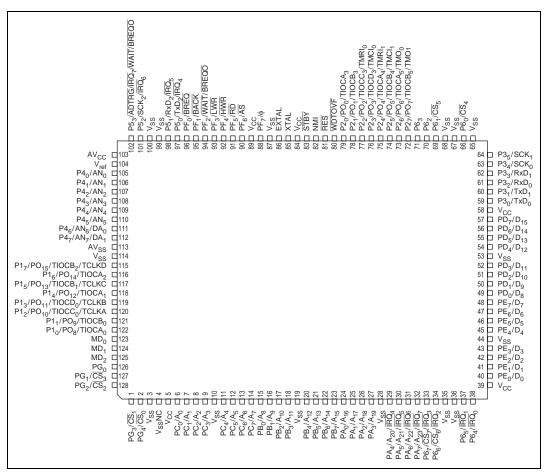

Figure 1.6 H8S/2321 Pin Arrangement (FP-128B: Top View)

**Bit 1—Write Data Buffer Enable (WDBE):** Selects whether or not the write buffer function is used for an external write cycle or DMAC single address cycle. In the H8S/2321 this bit is reserved and should only be written with 0.

| Bit 1<br>WDBE | Description                         |                 |

|---------------|-------------------------------------|-----------------|

| 0             | Write data buffer function not used | (Initial value) |

| 1             | Write data buffer function used     |                 |

**Bit 0—WAIT Pin Enable (WAITE):** Selects enabling or disabling of wait input by the WAIT pin.

# Bit 0 Description 0 Wait input by WAIT pin disabled. WAIT pin can be used as I/O port (Initial value) 1 Wait input by WAIT pin enabled

#### 6.2.6 Memory Control Register (MCR)

| Bit             | : | 7   | 6   | 5    | 4   | 3    | 2    | 1    | 0    |

|-----------------|---|-----|-----|------|-----|------|------|------|------|

|                 |   | TPC | BE  | RCDM | —   | MXC1 | MXC0 | RLW1 | RLW0 |

| Initial value : |   | 0   | 0   | 0    | 0   | 0    | 0    | 0    | 0    |

| R/W             | : | R/W | R/W | R/W  | R/W | R/W  | R/W  | R/W  | R/W  |

MCR is an 8-bit readable/writable register that selects the DRAM strobe control method, number of precharge cycles, access mode, address multiplexing shift size, and the number of wait states inserted during refreshing, when areas 2 to 5 are designated as DRAM interface areas.

MCR is initialized to H'00 by a reset and in hardware standby mode. It is not initialized in software standby mode.

Note: In the H8S/2321 this register is reserved and must not be accessed.

#### 7.3.4 DMA Control Register (DMACR)

DMACR is a 16-bit readable/writable register that controls the operation of each DMAC channel. In full address mode, DMACRA and DMACRB have different functions.

DMACR is initialized to H'0000 by a reset, and in hardware standby mode.

#### DMACRA

| Bit        | :     | 15   | 14   | 13    | 12     | 11   | 10  | 9   | 8   |

|------------|-------|------|------|-------|--------|------|-----|-----|-----|

|            |       | DTSZ | SAID | SAIDE | BLKDIR | BLKE | —   | _   | —   |

| Initial va | lue : | 0    | 0    | 0     | 0      | 0    | 0   | 0   | 0   |

| R/W        | :     | R/W  | R/W  | R/W   | R/W    | R/W  | R/W | R/W | R/W |

#### DMACRB

| Bit             | : | 7   | 6    | 5     | 4   | 3    | 2    | 1    | 0    |

|-----------------|---|-----|------|-------|-----|------|------|------|------|

|                 |   | _   | DAID | DAIDE | _   | DTF3 | DTF2 | DTF1 | DTF0 |

| Initial value : |   | 0   | 0    | 0     | 0   | 0    | 0    | 0    | 0    |

| R/W             | : | R/W | R/W  | R/W   | R/W | R/W  | R/W  | R/W  | R/W  |

#### Bit 15—Data Transfer Size (DTSZ): Selects the size of data to be transferred at one time.

| Bit 15 |                    |                 |

|--------|--------------------|-----------------|

| DTSZ   | Description        |                 |

| 0      | Byte-size transfer | (Initial value) |

| 1      | Word-size transfer |                 |

#### Port C MOS Pull-Up Control Register (PCPCR)

| Bit        | :     | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|

|            |       | PC7PCR | PC6PCR | PC5PCR | PC4PCR | PC3PCR | PC2PCR | PC1PCR | PC0PCR |

| Initial va | lue : | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W        | :     | R/W    |

PCPCR is an 8-bit readable/writable register that controls the MOS input pull-up function incorporated into port C on an individual bit basis.

When a PCDDR bit is cleared to 0 (input port setting) in mode 6 or 7, setting the corresponding PCPCR bit to 1 turns on the MOS input pull-up for the corresponding pin.

PCPCR is initialized to H'00 by a reset, and in hardware standby mode. It retains its prior state in software standby mode.

#### 9.10.3 Pin Functions

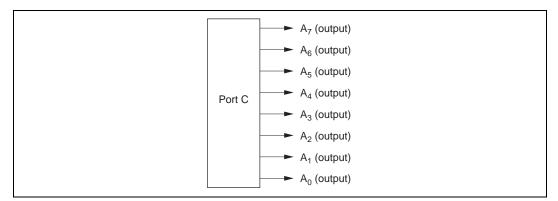

Modes 4 and 5: In modes 4 and 5, port C pins are automatically designated as address outputs.

Port C pin functions in modes 4 and 5 are shown in figure 9.13.

Figure 9.13 Port C Pin Functions (Modes 4 and 5)

| Channel | Bit 7<br>IOD3                                                       | Bit 6<br>IOD2     | Bit 5<br>IOD1                                    | Bit 4<br>IOD0 | Descripti                                                  | on                        |                                |                                |

|---------|---------------------------------------------------------------------|-------------------|--------------------------------------------------|---------------|------------------------------------------------------------|---------------------------|--------------------------------|--------------------------------|

| 3       | 0                                                                   | 0                 | 0                                                | 0             | TGR3D                                                      | Output disabled           | (Initial value)                |                                |

|         |                                                                     |                   |                                                  | 1             | is output                                                  | Initial output is 0       | 0 output at compare match      |                                |

|         |                                                                     |                   | 1                                                | 0             | <ul> <li>compare</li> <li>register*<sup>2</sup></li> </ul> | output                    | 1 output at compare match      |                                |

|         |                                                                     |                   |                                                  | 1             |                                                            |                           | Toggle output at compare match |                                |

|         |                                                                     |                   | 0                                                | 0             | -                                                          | -                         | Output disabled                |                                |

|         |                                                                     |                   | Initial output is                                | _             | Initial output is 1                                        | 0 output at compare match |                                |                                |

|         |                                                                     |                   | 1 0 output                                       | output        | 1 output at compare match                                  |                           |                                |                                |

|         |                                                                     |                   |                                                  | 1             |                                                            |                           |                                | Toggle output at compare match |

|         | 1                                                                   | 0                 | 0                                                | 0             | TGR3D                                                      | Capture input             | Input capture at rising edge   |                                |

|         |                                                                     |                   |                                                  | 1             | is input<br>_ capture                                      | source is                 | Input capture at falling edge  |                                |

|         |                                                                     |                   | 1                                                | *             | register*2                                                 |                           | Input capture at both edges    |                                |

|         | 1     *     *     Capture input<br>source is chann<br>4/count clock | source is channel | Input capture at TCNT4 count-<br>up/count-down*1 |               |                                                            |                           |                                |                                |

\*: Don't care

- Notes: 1. When bits TPSC2 to TPSC0 in TCR4 are set to B'000 and  $\phi/1$  is used as the TCNT4 count clock, this setting is invalid and input capture is not generated.

- 2. When the BFB bit in TMDR3 is set to 1 and TGR3D is used as a buffer register, this setting is invalid and input capture/output compare is not generated.

| Channel | Bit 3<br>IOA3                      | Bit 2<br>IOA2 | Bit 1<br>IOA1                  | Bit 0<br>IOA0 | Descripti                                | on                                                                  |                                                                                  |

|---------|------------------------------------|---------------|--------------------------------|---------------|------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 1       | 0                                  | 0             | 0                              | 0             | TGR1A                                    | Output disabled                                                     | (Initial value)                                                                  |

|         |                                    |               |                                | 1             | is output                                | Initial output is 0                                                 | 0 output at compare match                                                        |

|         |                                    |               | 1                              | 0             | <ul> <li>compare<br/>register</li> </ul> | output                                                              | 1 output at compare match                                                        |

|         | 1                                  |               | Toggle output at compare match |               |                                          |                                                                     |                                                                                  |

|         |                                    | 1             | 0                              | 0             | _                                        | Output disabled                                                     |                                                                                  |

|         |                                    |               |                                | 1             |                                          | Initial output is 1                                                 | 0 output at compare match                                                        |

|         |                                    |               | 1                              | 0             | _                                        | output                                                              | 1 output at compare match                                                        |

|         |                                    |               |                                | 1             | _                                        |                                                                     | Toggle output at compare match                                                   |

|         | 1                                  | 0             | 0                              | 0             | TGR1A                                    | Capture input                                                       | Input capture at rising edge                                                     |

|         |                                    |               |                                | 1             | is input                                 | source is                                                           | Input capture at falling edge                                                    |

|         | capture TIOCA1 pin<br>1 * register | ПОСАТрії      | Input capture at both edges    |               |                                          |                                                                     |                                                                                  |

|         |                                    | 1             | *                              | *             | _                                        | Capture input<br>source is TGR0A<br>compare match/<br>input capture | Input capture at generation of<br>channel 0/TGR0A compare<br>match/input capture |

|         |                                    |               |                                |               |                                          |                                                                     | *· Don't care                                                                    |

\*: Don't care

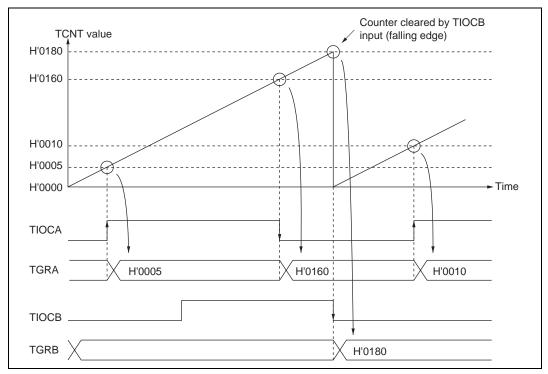

• Example of input capture operation

Figure 10.13 shows an example of input capture operation.

In this example both rising and falling edges have been selected as the TIOCA pin input capture input edge, falling edge has been selected as the TIOCB pin input capture input edge, and counter clearing by TGRB input capture has been designated for TCNT.

Figure 10.13 Example of Input Capture Operation

Figure 10.26 shows an example of PWM mode 2 operation.

In this example, synchronous operation is designated for channels 0 and 1, TGR1B compare match is set as the TCNT clearing source, and 0 is set for the initial output value and 1 for the output value of the other TGR registers (TGR0A to TGR0D, TGR1A), to output a 5-phase PWM waveform.

In this case, the value set in TGR1B is used as the period, and the values set in the other TGR registers as the duty.

Figure 10.26 Example of PWM Mode Operation (2)

| Bit 6<br>WT/IT | Description                                                                                                              |                 |

|----------------|--------------------------------------------------------------------------------------------------------------------------|-----------------|

| 0              | Interval timer: Sends the CPU an interval timer interrupt request (WOVI) when TCNT overflows                             | (Initial value) |

| 1              | Watchdog timer: Generates the WDTOVF signal*1 when TCNT overflows*                                                       | k2              |

| Notes: 1.      | The $\overline{\text{WDTOVF}}$ pin function cannot be used in the F-ZTAT versions.                                       |                 |

| 2.             | For details of the case where TCNT overflows in watchdog timer mode, see 13.2.3, Reset Control/Status Register (RSTCSR). | e section       |

Bit 5—Timer Enable (TME): Selects whether TCNT runs or is halted.

| Bit 5<br>TME | Description                            |                 |

|--------------|----------------------------------------|-----------------|

| 0            | TCNT is initialized to H'00 and halted | (Initial value) |

| 1            | TCNT counts                            |                 |

Bits 4 and 3—Reserved: These bits cannot be modified and are always read as 1.

Bits 2 to 0—Clock Select 2 to 0 (CKS2 to CKS0): These bits select one of eight internal clock sources, obtained by dividing the system clock ( $\phi$ ), for input to TCNT.

|               |               |               | Description         |                                                  |

|---------------|---------------|---------------|---------------------|--------------------------------------------------|

| Bit 2<br>CKS2 | Bit 1<br>CKS1 | Bit 0<br>CKS0 | Clock               | Overflow Period (when $\phi = 20 \text{ MHz})^*$ |

| 0             | 0             | 0             | φ/2 (Initial value) | 25.6 µs                                          |

|               |               | 1             | ф/64                | 819.2 µs                                         |

|               | 1             | 0             | ф/128               | 1.6 ms                                           |

|               |               | 1             | φ/512               | 6.6 ms                                           |

| 1             | 0             | 0             | ф/2048              | 26.2 ms                                          |

|               |               | 1             | ф/8192              | 104.9 ms                                         |

|               | 1             | 0             | ф/32768             | 419.4 ms                                         |

|               |               | 1             | ф/131072            | 1.68 s                                           |

Note: \* The overflow period is the time from when TCNT starts counting up from H'00 until overflow occurs.

Bit 6—Receive Data Register Full (RDRF): Indicates that the received data is stored in RDR.

| Bit 6 |                                                                                                                                                               |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDRF  | Description                                                                                                                                                   |

| 0     | [Clearing conditions] (Initial value)                                                                                                                         |

|       | <ul> <li>When 0 is written to RDRF after reading RDRF = 1</li> </ul>                                                                                          |

|       | <ul> <li>When the DMAC<sup>*</sup> or DTC is activated by an RXI interrupt and reads data from<br/>RDR</li> </ul>                                             |

| 1     | [Setting condition]                                                                                                                                           |

|       | When serial reception ends normally and receive data is transferred from RSR to RDR                                                                           |

| Notes | RDR and the RDRF flag are not affected and retain their previous values when an error is detected during reception or when the RE bit in SCR is cleared to 0. |

|       | If reception of the payt data is completed while the PDPE flag is still set to 1, an overrup                                                                  |

If reception of the next data is completed while the RDRF flag is still set to 1, an overrun error will occur and the receive data will be lost.

\* The DMAC is not supported in the H8S/2321.

Bit 5-Overrun Error (ORER): Indicates that an overrun error occurred during reception, causing abnormal termination.

| Bit 5  |    |                                                                                                                                                                                                                      |                               |

|--------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| ORER   |    | Description                                                                                                                                                                                                          |                               |

| 0      |    | [Clearing condition]                                                                                                                                                                                                 | (Initial value) <sup>*1</sup> |

|        |    | When 0 is written to ORER after reading ORER = 1                                                                                                                                                                     |                               |

| 1      |    | [Setting condition]                                                                                                                                                                                                  |                               |

|        |    | When the next serial reception is completed while RDRF = $1^{*2}$                                                                                                                                                    |                               |

| Notes: | 1. | The ORER flag is not affected and retains its previous state when the cleared to 0.                                                                                                                                  | RE bit in SCR is              |

|        | 2. | The receive data prior to the overrun error is retained in RDR, and the subsequently is lost. Also, subsequent serial reception cannot be com ORER flag is set to 1. In synchronous mode, serial transmission cannot | tinued while the              |

either.

REJ09B0220-0600

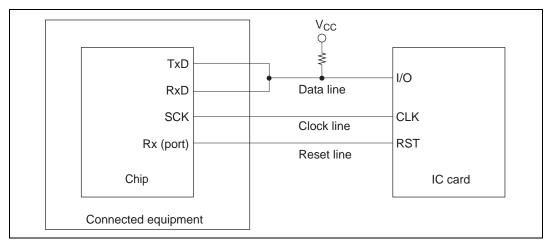

Figure 15.2 Schematic Diagram of Smart Card Interface Pin Connections

Note: If an IC card is not connected, and the TE and RE bits are both set to 1, closed transmission/reception is possible, enabling self-diagnosis to be carried out.

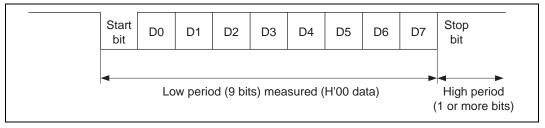

**Automatic SCI Bit Rate Adjustment:** When boot mode is initiated, the H8S/2329B F-ZTAT chip measures the low period of the asynchronous SCI communication data (H'00) transmitted continuously from the host. The SCI transmit/receive format should be set as follows: 8-bit data, 1 stop bit, no parity. The chip calculates the bit rate of the transmission from the host from the measured low period, and transmits one H'00 byte to the host to indicate the end of bit rate adjustment. The host should confirm that this adjustment end indication (H'00) has been received normally, and transmit one H'55 byte to the chip. If reception cannot be performed normally, initiate boot mode again (reset), and repeat the above operations. Depending on the host's transmission bit rate and the chip's system clock frequency, there will be a discrepancy between the bit rates of the host and the chip. To ensure correct SCI operation, the host's transfer bit rate should be set to 9,600 or 19,200 bps.

Table 19.10 shows typical host transfer bit rates and system clock frequencies for which automatic adjustment of the MCU's bit rate is possible. The boot program should be executed within this system clock range.

Figure 19.11 Automatic SCI Bit Rate Adjustment

| Table 19.10         System Clock Frequencies for which Automatic Adjustment of H8S/2329B |  |

|------------------------------------------------------------------------------------------|--|

| F-ZTAT Bit Rate is Possible                                                              |  |

| Host Bit Rate | System Clock Frequency for which Automatic Adjustment of H8S/2329B F-ZTAT Bit Rate is Possible |

|---------------|------------------------------------------------------------------------------------------------|

| 19,200 bps    | 16 MHz to 25 MHz                                                                               |

| 9,600 bps     | 8 MHz to 25 MHz                                                                                |

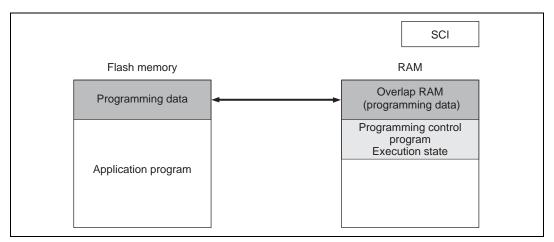

**On-Chip RAM Area Divisions in Boot Mode:** In boot mode, the 2-kbyte area from H'FF7C00 to H'FF83FF is reserved for use by the boot program, as shown in figure 19.12. The area to which the programming control program is transferred is H'FF8400 to H'FFFBFF. The boot program area can be used when the programming control program transferred into RAM enters the execution state. A stack area should be set up as required.

## Renesas

## **19.8 Flash Memory Protection**

There are three kinds of flash memory program/erase protection: hardware protection, software protection, and error protection.

## 19.8.1 Hardware Protection

Hardware protection refers to a state in which programming/erasing of flash memory is forcibly disabled or aborted. Settings in flash memory control registers 1 and 2 (FLMCR1, FLMCR2) and erase block registers 1 and 2 (EBR1, EBR2) are reset (see table 19.11).

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Fu      | nctions |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|

| ltem                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Program | Erase   |

| Reset/standby<br>protection | <ul> <li>In a reset (including a WDT overflow reset) and in standby mode, FLMCR1, FLMCR2, EBR1, and EBR2 are initialized, and the program/erase-protected state is entered.</li> <li>In a reset via the RES pin, the reset state is not entered unless the RES pin is held low until oscillation stabilizes after powering on. In the case of a reset during operation, hold the RES pin low for the RES pulse width specified in section 22.2.3, AC Characteristics.</li> </ul> | Yes     | Yes     |

## **Table 19.11 Hardware Protection**

## **19.8.2** Software Protection

Software protection can be implemented by setting the SWE bit in flash memory control register 1 (FLMCR1), erase block registers 1 and 2 (EBR1, EBR2), and the RAMS bit in the RAM emulation register (RAMER). When software protection is in effect, setting the P or E bit in FLMCR1 does not cause a transition to program mode or erase mode (see table 19.12).

| Bit         | :     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| EBR1        |       | EB7 | EB6 | EB5 | EB4 | EB3 | EB2 | EB1 | EB0 |

| Initial val | lue : | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W         | :     | R/W |

#### 19.14.3 Erase Block Register 1 (EBR1)

EBR1 is an 8-bit register that specifies the flash memory erase area block by block. EBR1 is initialized to H'00 by a reset, in hardware standby mode and software standby mode, when a low level is input to the FWE pin, and when a high level is input to the FWE pin and the SWE bit in FLMCR1 is not set. When a bit in EBR1 is set, the corresponding block can be erased. Other blocks are erase-protected. Set only one bit in EBR1 and EBR2 together (setting more than one bit will automatically clear all EBR1 and EBR2 bits to 0). When on-chip flash memory is disabled, a read will return H'00 and writes are invalid.

The flash memory block configuration is shown in table 19.28.

#### 19.14.4 Erase Block Registers 2 (EBR2)

| Bit          | :    | 7 | 6 | 5 | 4 | 3    | 2    | 1   | 0   |

|--------------|------|---|---|---|---|------|------|-----|-----|

| EBR2         |      |   | — | — | _ | EB11 | EB10 | EB9 | EB8 |

| Initial valu | re : | 0 | 0 | 0 | 0 | 0    | 0    | 0   | 0   |

| R/W          | :    | — | — | — |   | R/W  | R/W  | R/W | R/W |

EBR2 is an 8-bit register that specifies the flash memory erase area block by block. EBR2 is initialized to H'00 by a reset, in hardware standby mode and software standby mode, when a low level is input to the FWE pin, and when a high level is input to the FWE pin and the SWE bit in FLMCR1 is not set. When a bit in EBR2 is set, the corresponding block can be erased. Other blocks are erase-protected. Set only one bit in EBR2 and EBR1 together (setting more than one bit will automatically clear all EBR1 and EBR2 bits to 0). Bits 7 to 4 are reserved: they are always read as 0 and cannot be modified. When on-chip flash memory is disabled, a read will return H'00, and writes are invalid.

The flash memory block configuration is shown in table 19.28.

## Renesas

Writing Overlap RAM Data in User Program Mode: When overlap RAM data is confirmed, the RAMS bit is cleared, RAM overlap is released, and writes should actually be performed to the flash memory.

When the programming control program is transferred to RAM, ensure that the transfer destination and the overlap RAM do not overlap, as this will cause data in the overlap RAM to be rewritten.

Figure 19.64 Writing Overlap RAM Data in User Program Mode

#### **19.22.6** Differences between Boot Mode and User Program Mode

#### Table 19.46 Differnces between Boot Mode and User Program Mode

|                              | Boot Mode              | User Program Mode                                       |

|------------------------------|------------------------|---------------------------------------------------------|

| Entire memory erase          | Yes                    | Yes                                                     |

| Block erase                  | No                     | Yes                                                     |

| Programming control program* | Program/program-verify | Erase/erase-verify/program/<br>program-verify/emulation |

Note: \* To be provided by the user, in accordance with the recommended algorithm.

## 19.24.2 User Program Mode

When set to user program mode, the chip can program and erase its flash memory by executing a user program/erase control program. Therefore, on-board programming of the on-chip flash memory can be carried out by providing ahead of time an on-board FWE control means to supply programming data, and storing a program/erase control program in part of the program area if necessary.

To select user program mode, select a mode that enables the on-chip flash memory (mode 6 or 7) and apply a high level to the FWE pin. In this mode, on-chip supporting modules other than flash memory operate as they normally would in modes 6 and 7.

While the SWE1 bit is set to 1 to perform programming or erasing for the addresses H'000000 to H'03FFFF, this address area cannot be read. While the SWE2 bit is set to 1 to perform programming or erasing for the addresses H'040000 to H'07FFFF, this address area cannot be read. The control program that performs programming and erasing should be run in on-chip RAM or flash memory except for the above address areas. When the program is located in external memory, an instruction for programming the flash memory and the following instruction should be located in on-chip RAM.

Figure 19.70 shows the procedure for executing the program/erase control program when transferred to on-chip RAM.

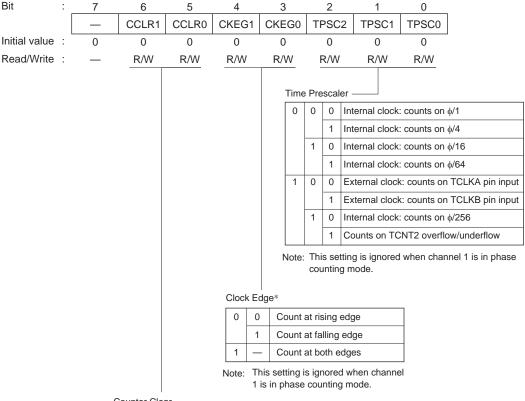

#### **TCR1—Timer Control Register 1**

H'FFE0

**TPU1**

#### Counter Clear

| 0 | 0 | TCNT clearing disabled                                                                                      |

|---|---|-------------------------------------------------------------------------------------------------------------|

|   | 1 | TCNT cleared by TGRA compare match/input capture                                                            |

| 1 | 0 | TCNT cleared by TGRB compare match/input capture                                                            |

|   | 1 | TCNT cleared by counter clearing for another channel performing synchronous clearing/synchronous operation* |

Note: \* Synchronous operation setting is performed by setting the SYNC bit in TSYR to 1.

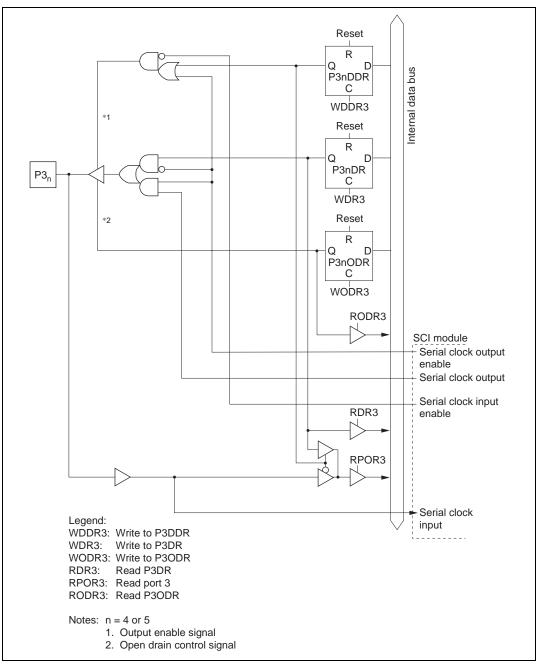

Figure C.3 (c) Port 3 Block Diagram (Pins P3<sub>4</sub> and P3<sub>5</sub>)

Rev.6.00 Sep. 27, 2007 Page 1228 of 1268 REJ09B0220-0600