Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product StatusActiveCore ProcessorH8S/2000Core Size16-BitSpeed20MHzConnectivitySCI, SmartCardPreipheralsDMA, POR, PWM, WDTNumber of I/O86Program Memory Size-Program Memory TypeRoMlessEPROM Size-At Size32K × 8Voltage - Supply (Vcc/Vdd)A/D × 10b; D/A × 28b |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Core Size16-BitSpeed20MHzConnectivitySCI, SmartCardPeripheralsDMA, POR, PWM, WDTNumber of I/O86Program Memory Size-Program Memory TypeROMIessEEPROM Size-RAM Size32K × 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6V                                                  |

| Speed20MHzConnectivitySCI, SmartCardPeripheralsDMA, POR, PWM, WDTNumber of I/O86Program Memory Size-Program Memory TypeROMIessEEPROM Size-RAM Size32K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6V                                                                 |

| ConnectivitySCI, SmartCardPeripheralsDMA, POR, PWM, WDTNumber of I/O86Program Memory Size-Program Memory TypeROMIessEEPROM Size-RAM Size32K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6V                                                                           |

| PeripheralsDMA, POR, PWM, WDTNumber of I/O86Program Memory Size-Program Memory TypeROMIessEEPROM Size-RAM Size32K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6V                                                                                                     |

| Number of I/O86Program Memory Size-Program Memory TypeROMIessEEPROM Size-RAM Size32K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6V                                                                                                                                  |

| Program Memory Size-Program Memory TypeROMlessEEPROM Size-RAM Size32K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6V                                                                                                                                                 |

| Program Memory TypeROMlessEEPROM Size-RAM Size32K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6V                                                                                                                                                                     |

| EEPROM Size     -       RAM Size     32K x 8       Voltage - Supply (Vcc/Vdd)     2.7V ~ 3.6V                                                                                                                                                                  |

| RAM Size         32K x 8           Voltage - Supply (Vcc/Vdd)         2.7V ~ 3.6V                                                                                                                                                                              |

| Voltage - Supply (Vcc/Vdd) 2.7V ~ 3.6V                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                |

| Data Converters A/D 8x10b; D/A 2x8b                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                |

| Oscillator Type Internal                                                                                                                                                                                                                                       |

| Operating Temperature -20°C ~ 75°C (TA)                                                                                                                                                                                                                        |

| Mounting Type Surface Mount                                                                                                                                                                                                                                    |

| Package / Case 120-TQFP                                                                                                                                                                                                                                        |

| Supplier Device Package 120-TQFP (14x14)                                                                                                                                                                                                                       |

| Purchase URL https://www.e-xfl.com/product-detail/renesas-electronics-america/d12324svte20v                                                                                                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

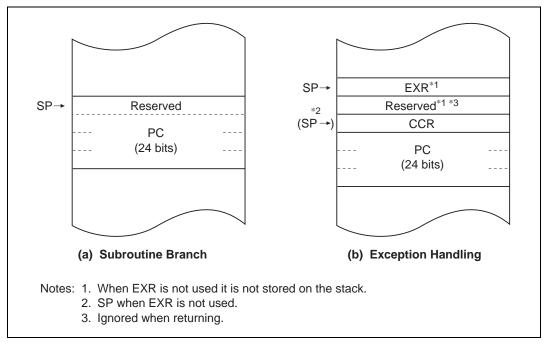

**Stack Structure:** In advanced mode, when the program counter (PC) is pushed onto the stack in a subroutine call, and the PC, condition-code register (CCR), and extended control register (EXR) are pushed onto the stack in exception handling, they are stored as shown in figure 2.2. When EXR is invalid, it is not pushed onto the stack. For details, see section 4, Exception Handling.

Figure 2.2 Stack Structure in Advanced Mode

#### 6.5.5 Pins Used for DRAM Interface

Table 6.7 shows the pins used for DRAM interfacing and their functions.

### Table 6.7DRAM Interface Pins

| Pin               | With DRAM<br>Setting | Name                        | I/O    | Function                                                           |

|-------------------|----------------------|-----------------------------|--------|--------------------------------------------------------------------|

| HWR               | WE                   | Write enable                | Output | When 2-CAS system is set,<br>write enable for DRAM space<br>access |

| LCAS              | LCAS                 | Lower column address strobe | Output | Lower column address strobe for 16-bit DRAM space access           |

| CS2               | RAS2                 | Row address strobe 2        | Output | Row address strobe when area 2 is designated as DRAM space         |

| CS3               | RAS3                 | Row address strobe 3        | Output | Row address strobe when area 3 is designated as DRAM space         |

| CS4               | RAS4                 | Row address strobe 4        | Output | Row address strobe when area 4 is designated as DRAM space         |

| CS5               | RAS5                 | Row address strobe 5        | Output | Row address strobe when area 5 is designated as DRAM space         |

| CAS               | UCAS                 | Upper column address strobe | Output | Upper column address strobe for DRAM space access                  |

| WAIT              | WAIT                 | Wait                        | Input  | Wait request signal                                                |

| $A_{12}$ to $A_0$ | $A_{12}$ to $A_0$    | Address pins                | Output | Row address/column address multiplexed output                      |

| $D_{15}$ to $D_0$ | $D_{15}$ to $D_0$    | Data pins                   | I/O    | Data input/output pins                                             |

### 7.3.5 DMA Band Control Register (DMABCR)

### DMABCRH:

| Bit             | :   | 15    | 14   | 13    | 12   | 11     | 10     | 9      | 8      |

|-----------------|-----|-------|------|-------|------|--------|--------|--------|--------|

|                 |     | FAE1  | FAE0 | _     |      | DTA1   |        | DTA0   | —      |

| Initial value   | e : | 0     | 0    | 0     | 0    | 0      | 0      | 0      | 0      |

| R/W             | :   | R/W   | R/W  | R/W   | R/W  | R/W    | R/W    | R/W    | R/W    |

|                 |     |       |      |       |      |        |        |        |        |

| DMABCRL:        |     |       |      |       |      |        |        |        |        |

| 5.4             |     | _     |      | _     |      |        |        |        |        |

| Bit             | :   | 7     | 6    | 5     | 4    | 3      | 2      | 1      | 0      |

|                 | :   | DTME1 | DTE1 | DTME0 | DTE0 | DTIE1B | DTIE1A | DTIE0B | DTIE0A |

| Initial value : |     | 0     | 0    | 0     | 0    | 0      | 0      | 0      | 0      |

| R/W             | :   | R/W   | R/W  | R/W   | R/W  | R/W    | R/W    | R/W    | R/W    |

DMABCR is a 16-bit readable/writable register that controls the operation of each DMAC channel.

DMABCR is initialized to H'0000 by a reset, and in hardware standby mode.

Bit 15—Full Address Enable 1 (FAE1): Specifies whether channel 1 is to be used in short address mode or full address mode.

In full address mode, channels 1A and 1B are used together as a single channel.

| Bit 15<br>FAE1 | Description        |                 |

|----------------|--------------------|-----------------|

| 0              | Short address mode | (Initial value) |

| 1              | Full address mode  |                 |

unless the prescribed register is accessed in a DMA transfer. If the same interrupt is used as an activation source for more than one channel, the interrupt request flag is cleared when the highest-priority channel is activated first. Transfer requests for other channels are held pending in the DMAC, and activation is carried out in order of priority.

When DTE = 0, such as after completion of a transfer, a request from the selected activation source is not sent to the DMAC, regardless of the DTA bit. In this case, the relevant interrupt request is sent to the CPU or DTC.

In case of overlap with a CPU interrupt source or DTC activation source (DTA = 0), the interrupt request flag is not cleared by the DMAC.

Activation by External Request: If an external request ( $\overline{DREQ}$  pin) is specified as an activation source, the relevant port should be set to input mode in advance.

Level sensing or edge sensing can be used for external requests.

External request operation in normal mode (short address mode or full address mode) is described below.

When edge sensing is selected, a 1-byte or 1-word transfer is executed each time a high-to-low transition is detected on the  $\overline{\text{DREQ}}$  pin. The next transfer may not be performed if the next edge is input before transfer is completed.

When level sensing is selected, the DMAC stands by for a transfer request while the  $\overline{\text{DREQ}}$  pin is held high. While the  $\overline{\text{DREQ}}$  pin is held low, transfers continue in succession, with the bus being released each time a byte or word is transferred. If the  $\overline{\text{DREQ}}$  pin goes high in the middle of a transfer, the transfer is interrupted and the DMAC stands by for a transfer request.

Activation by Auto-Request: Auto-request activation is performed by register setting only, and transfer continues to the end.

With auto-request activation, cycle steal mode or burst mode can be selected.

In cycle steal mode, the DMAC releases the bus to another bus master each time a byte or word is transferred. DMA and CPU cycles usually alternate.

In burst mode, the DMAC keeps possession of the bus until the end of the transfer, and transfer is performed continuously.

**Single Address Mode:** The DMAC can operate in dual address mode in which read cycles and write cycles are separate cycles, or single address mode in which read and write cycles are executed in parallel.

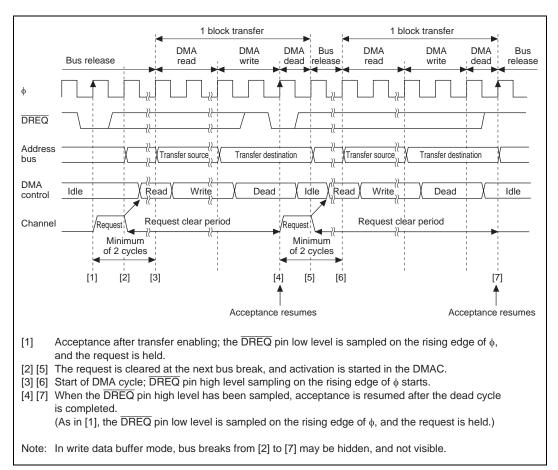

Figure 7.24 shows an example of  $\overline{\text{DREQ}}$  pin falling edge activated block transfer mode transfer.

# Figure 7.24 Example of DREQ Pin Falling Edge Activated Block Transfer Mode Transfer

$\overline{\text{DREQ}}$  pin sampling is performed every cycle, with the rising edge of the next  $\phi$  cycle after the end of the DMABCR write cycle for setting the transfer enabled state as the starting point.

When the  $\overline{\text{DREQ}}$  pin low level is sampled while acceptance by means of the  $\overline{\text{DREQ}}$  pin is possible, the request is held in the DMAC. Then, when activation is initiated in the DMAC, the request is cleared, and  $\overline{\text{DREQ}}$  pin high level sampling for edge detection is started. If  $\overline{\text{DREQ}}$  pin high level sampling has been completed by the time the DMA dead cycle ends, acceptance resumes after the end of the dead cycle,  $\overline{\text{DREQ}}$  pin low level sampling is performed again, and this operation is repeated until the transfer ends.

**Bit 3—Input Capture/Output Compare Flag D (TGFD):** Status flag that indicates the occurrence of TGRD input capture or compare match in channels 0 and 3.

In channels 1, 2, 4, and 5, bit 3 is reserved. It is always read as 0 and cannot be modified.

| Bit 3<br>TGFD | Description                                                                                                                                |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 0             | [Clearing conditions] (Initial value)                                                                                                      |

|               | <ul> <li>When DTC is activated by TGID interrupt while DISEL bit of MRB in DTC is 0</li> </ul>                                             |

|               | <ul> <li>When 0 is written to TGFD after reading TGFD = 1</li> </ul>                                                                       |

| 1             | [Setting conditions]                                                                                                                       |

|               | <ul> <li>When TCNT = TGRD while TGRD is functioning as output compare register</li> </ul>                                                  |

|               | <ul> <li>When TCNT value is transferred to TGRD by input capture signal while TGRD is<br/>functioning as input capture register</li> </ul> |

**Bit 2—Input Capture/Output Compare Flag C (TGFC):** Status flag that indicates the occurrence of TGRC input capture or compare match in channels 0 and 3.

In channels 1, 2, 4, and 5, bit 2 is reserved. It is always read as 0 and cannot be modified.

| Bit 2 |                                                                                           |

|-------|-------------------------------------------------------------------------------------------|

| TGFC  | Description                                                                               |

| 0     | [Clearing conditions] (Initial value)                                                     |

|       | When DTC is activated by TGIC interrupt while DISEL bit of MRB in DTC is 0                |

|       | <ul> <li>When 0 is written to TGFC after reading TGFC = 1</li> </ul>                      |

| 1     | [Setting conditions]                                                                      |

|       | <ul> <li>When TCNT = TGRC while TGRC is functioning as output compare register</li> </ul> |

|       | When TCNT value is transferred to TGRC by input capture signal while TGRC is              |

|       | functioning as input capture register                                                     |

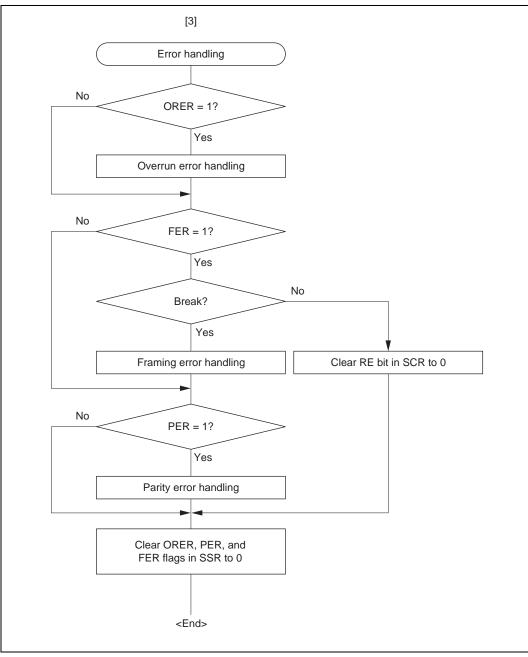

Figure 14.7 Sample Serial Reception Flowchart (cont)

**Data Transfer Operation by DMAC<sup>\*</sup> or DTC:** In smart card mode, as with the normal SCI, transfer can be carried out using the DMAC<sup>\*</sup> or DTC. In a transmit operation, the TDRE flag is also set to 1 at the same time as the TEND flag in SSR, and a TXI interrupt is generated. If the TXI request is designated beforehand as a DMAC<sup>\*</sup> or DTC activation source, the DMAC<sup>\*</sup> or DTC will be activated by the TXI request, and transfer of the transmit data will be carried out. The TDRE and TEND flags are automatically cleared to 0 when data transfer is performed by the DMAC<sup>\*</sup> or DTC. In the event of an error, the SCI retransmits the same data automatically. The TEND flag remains cleared to 0 during this time, and the DMAC<sup>\*</sup> is not activated. Thus, the number of bytes specified by the SCI and DMAC<sup>\*</sup> are transmitted automatically even in retransmission following an error. However, the ERS flag is not cleared automatically when an error occurs, and so the RIE bit should be set to 1 beforehand so that an ERI request will be generated in the event of an error, and the ERS flag will be cleared.

When performing transfer using the DMAC<sup>\*</sup> or DTC, it is essential to set and enable the DMAC<sup>\*</sup> or DTC before carrying out SCI setting. For details of the DMAC<sup>\*</sup> and DTC setting procedures, see section 7, DMA Controller<sup>\*</sup>, and section 8, Data Transfer Controller.

In a receive operation, an RXI interrupt request is generated when the RDRF flag in SSR is set to 1. If the RXI request is designated beforehand as a DMAC<sup>\*</sup> or DTC activation source, the DMAC<sup>\*</sup> or DTC will be activated by the RXI request, and transfer of the receive data will be carried out. The RDRF flag is cleared to 0 automatically when data transfer is performed by the DMAC<sup>\*</sup> or DTC. If an error occurs, an error flag is set but the RDRF flag is not. Consequently, the DMAC<sup>\*</sup> or DTC is not activated, but instead, an ERI interrupt request is sent to the CPU. Therefore, the error flag should be cleared.

Notes: For details of operation in block transfer mode, see section 14.4, SCI Interrupts. \* The DMAC is not supported in the H8S/2321.

**Bit 5—A/D Start (ADST):** Selects starting or stopping of A/D conversion. Holds a value of 1 during A/D conversion.

The ADST bit can be set to 1 by software, a timer conversion start trigger, or the A/D external trigger input pin ( $\overline{ADTRG}$ ).

| Bit 5<br>ADST | D  | escription     |                                                                                                                                          |                            |

|---------------|----|----------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 0             | A/ | D conversion s | topped                                                                                                                                   | (Initial value)            |

| 1             | •  | Single mode:   | A/D conversion is started. Cleared to 0 autor<br>conversion on the specified channel ends                                                | matically when             |

|               | •  | Scan mode:     | A/D conversion is started. Conversion continues selected channels until ADST is cleared to 0 a transition to standby mode or module stop | ) by software, a reset, or |

**Bit 4—Scan Mode (SCAN):** Selects single mode or scan mode as the A/D conversion operating mode. See section 16.4, Operation, for details of single mode and scan mode operation. Only set the SCAN bit while conversion is stopped (ADST = 0).

| Bit 4<br>SCAN | Description |                 |

|---------------|-------------|-----------------|

| 0             | Single mode | (Initial value) |

| 1             | Scan mode   |                 |

| ADCR3<br>CKS1 | Bit 3<br>CKS | Description                         |                 |

|---------------|--------------|-------------------------------------|-----------------|

| 0             | 0            | Conversion time = 530 states (max.) |                 |

|               | 1            | Conversion time = 68 states (max.)  |                 |

| 1             | 0            | Conversion time = 266 states (max.) | (Initial value) |

|               | 1            | Conversion time = 134 states (max.) |                 |

**Bit 3—Clock Select (CKS):** Used together with the CKS1 bit in ADCR to set the A/D conversion time. Only change the conversion time while conversion is stopped (ADST = 0).

Bits 2 to 0—Channel Select 2 to 0 (CH2 to CH0): These bits are used together with the SCAN bit to select the analog input channels.

Only set the input channel(s) while conversion is stopped (ADST = 0).

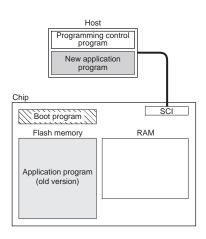

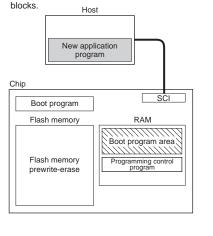

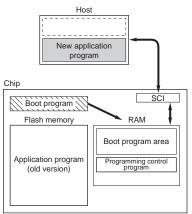

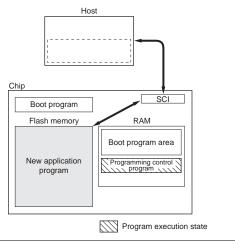

### 19.13.4 On-Board Programming Modes

#### Boot mode

#### 1. Initial state

The old program version or data remains written in the flash memory. The user should prepare the programming control program and new application program beforehand in the host.

Flash memory initialization The erase program in the boot program area (in RAM) is executed, and the flash memory is initialized (to H'FF). In boot mode, entire flash memory erasure is performed, without regard to

Programming control program transfer When boot mode is entered, the boot program in the chip (originally incorporated in the chip) is started and the programming control program in the host is transferred to RAM via SCI communication. The boot program required for flash memory erasing is automatically transferred to the RAM boot program area.

Writing new application program The programming control program transferred from the host to RAM is executed, and the new application program in the host is written into the flash memory.

#### Figure 19.31 Boot Mode

| Wait time: x                                                                                                                                                                                                                       | Programming/<br>erasing<br>possible | Wait time: 100 µs               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------------------|

| φtosc1                                                                                                                                                                                                                             |                                     | Min 0 μs                        |

| V <sub>CC</sub>                                                                                                                                                                                                                    |                                     |                                 |

| FWE                                                                                                                                                                                                                                |                                     |                                 |

| MD2 to MD0*1                                                                                                                                                                                                                       |                                     |                                 |

| RES                                                                                                                                                                                                                                |                                     |                                 |

| SWE set                                                                                                                                                                                                                            |                                     | SWE cleared                     |

| <ul> <li>Period during which flash memory access is pr (x: Wait time after setting SWE bit)*2</li> <li>Period during which flash memory can be prog (Execution of program in flash memory prohibit prohibited)</li> </ul>          | rammed                              | other than verify operations    |

| <ol> <li>Notes: 1. Except when switching modes, the level of power-off by pulling the pins up or down.</li> <li>2. See section 22.2.6, Flash Memory Chara</li> <li>3. Mode programming setup time t<sub>MDS</sub> (min)</li> </ol> | cteristics.                         | ID2 to MD0) must be fixed until |

Figure 19.87 Power-On/Off Timing (User Program Mode)

#### 22.2.4 A/D Conversion Characteristics

#### Table 22.20 A/D Conversion Characteristics

Condition B:  $V_{CC} = 3.0 \text{ V}$  to 3.6 V,  $AV_{CC} = 3.0 \text{ V}$  to 3.6 V,  $V_{ref} = 3.0 \text{ V}$  to  $AV_{CC}$ ,  $V_{SS} = AV_{SS} = 0 \text{ V}$ ,  $\phi = 2 \text{ MHz}$  to 25 MHz,  $T_a = -20^{\circ}\text{C}$  to 75°C (regular specifications),  $T_a = -40^{\circ}\text{C}$  to 85°C (wide-range specifications)

| Item                                | Min  | Тур | Max  | Unit |

|-------------------------------------|------|-----|------|------|

| Resolution                          | 10   | 10  | 10   | Bits |

| Conversion time                     | 10.6 | —   | _    | μS   |

| Analog input capacitance            | _    | _   | 20   | pF   |

| Permissible signal source impedance | _    | _   | 5    | kΩ   |

| Nonlinearity error                  | _    | _   | ±5.5 | LSB  |

| Offset error                        | _    | _   | ±5.5 | LSB  |

| Full-scale error                    | _    | _   | ±5.5 | LSB  |

| Quantization error                  | _    | _   | ±0.5 | LSB  |

| Absolute accuracy                   | _    | _   | ±6.0 | LSB  |

### TIOR4—Timer I/O Control Register 4

#### H'FE92

TPU4

| Initial value : 0 0 0 0 0 0 0 0              | Bit        | :      | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|----------------------------------------------|------------|--------|------|------|------|------|------|------|------|------|

|                                              |            |        | IOB3 | IOB2 | IOB1 | IOB0 | IOA3 | IOA2 | IOA1 | IOA0 |

| Read/Write · R/W R/W R/W R/W R/W R/W R/W R/W | Initial va | lue :  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

|                                              | Read/W     | rite : | R/W  |

#### TGR4A I/O Control

|  | 0 | 0 | 0 | 0 | TGR4A                | Output disabled                                                     |                                                                        |

|--|---|---|---|---|----------------------|---------------------------------------------------------------------|------------------------------------------------------------------------|

|  |   |   |   | 1 | is output<br>compare | Initial output is 0                                                 | 0 output at compare match                                              |

|  |   |   | 1 | 0 | register             | output                                                              | 1 output at compare match                                              |

|  |   |   |   | 1 |                      |                                                                     | Toggle output at compare match                                         |

|  |   | 1 | 0 | 0 |                      | Output disabled                                                     |                                                                        |

|  |   |   |   | 1 | 1                    | Initial output is 1                                                 | 0 output at compare match                                              |

|  |   |   | 1 | 0 |                      | output                                                              | 1 output at compare match                                              |

|  |   |   |   | 1 |                      |                                                                     | Toggle output at compare match                                         |

|  | 1 | 0 | 0 | 0 | TGR4A                | Capture input                                                       | Input capture at rising edge                                           |

|  |   |   |   | 1 | is input capture     | source is<br>TIOCA₄ pin                                             | Input capture at falling edge                                          |

|  |   |   | 1 | * | register             |                                                                     | Input capture at both edges                                            |

|  |   | 1 | * | * |                      | Capture input<br>source is TGR3A<br>compare match/<br>input capture | Input capture at generation of<br>TGR3A compare match/input<br>capture |

\* : Don't care

#### TGR4B I/O Control

| 0 | 0 0 0 0 | TGR4B | Output disabled |                   |                                                                     |                                                                        |  |  |

|---|---------|-------|-----------------|-------------------|---------------------------------------------------------------------|------------------------------------------------------------------------|--|--|

|   |         |       | 1               | is output compare | Initial output is 0 output                                          | 0 output at compare match                                              |  |  |

|   |         | 1     | 0               | register          | ouipui                                                              | 1 output at compare match                                              |  |  |

|   |         |       | 1               | ]                 |                                                                     | Toggle output at compare match                                         |  |  |

|   | 1       | 0     | 0               |                   | Output disabled                                                     |                                                                        |  |  |

|   |         |       | 1               |                   | Initial output is 1                                                 | 0 output at compare match                                              |  |  |

|   |         | 1     | 0               |                   | output                                                              | 1 output at compare match                                              |  |  |

|   |         |       | 1               |                   |                                                                     | Toggle output at compare match                                         |  |  |

| 1 | 0       | 0     | 0               | TGR4B             | Capture input                                                       | Input capture at rising edge                                           |  |  |

|   |         |       | 1               | is input capture  | source is<br>TIOCB <sub>4</sub> pin                                 | Input capture at falling edge                                          |  |  |

|   |         | 1     | *               | register          |                                                                     | Input capture at both edges                                            |  |  |

|   | 1       | *     | *               |                   | Capture input<br>source is TGR3C<br>compare match/<br>input capture | Input capture at generation of<br>TGR3C compare match/input<br>capture |  |  |

### PCPCR—Port C MOS Pull-Up Control Register H'FF72

| Bit           | :  | 7 6    |        | 5      | 4      | 3      | 2      | 1      | 0      |

|---------------|----|--------|--------|--------|--------|--------|--------|--------|--------|

|               |    | PC7PCR | PC6PCR | PC5PCR | PC4PCR | PC3PCR | PC2PCR | PC1PCR | PC0PCR |

| Initial value | ): | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| Read/Write    | ): | R/W    |

|               |    |        |        |        |        |        |        |        |        |

Controls the MOS input pull-up function incorporated into port C on a bit-by-bit basis

#### PDPCR—Port D MOS Pull-Up Control Register H'FF73

| Bit           | : | 7 6    |        | 5      | 4      | 3      | 2      | 1      | 0      |

|---------------|---|--------|--------|--------|--------|--------|--------|--------|--------|

|               |   | PD7PCR | PD6PCR | PD5PCR | PD4PCR | PD3PCR | PD2PCR | PD1PCR | PD0PCR |

| Initial value | : | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| Read/Write    | : | R/W    |

|               |   |        |        |        |        |        |        |        |        |

|               |   |        |        |        |        |        |        |        |        |

Controls the MOS input pull-up function incorporated into port D on a bit-by-bit basis

#### PEPCR—Port E MOS Pull-Up Control Register H'FF74

#### Bit 7 6 5 4 3 2 1 0 PE7PCR PE6PCR PE5PCR PE4PCR PE3PCR PE2PCR PE1PCR PE0PCR Initial value : 0 0 0 0 0 0 0 0 Read/Write : R/W R/W R/W R/W R/W R/W R/W R/W

Controls the MOS input pull-up function incorporated into port E on a bit-by-bit basis

# RENESAS

Port C

Port D

Port E

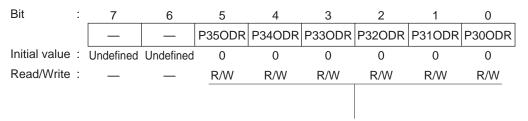

#### P3ODR—Port 3 Open Drain Control Register H'FF76

Controls the PMOS on/off status for each port 3 pin (P35 to P30)

| PAODR—Port A Open Drain Control Register H'FF77 |   |        |        |        |        |        |        |        |        |  |

|-------------------------------------------------|---|--------|--------|--------|--------|--------|--------|--------|--------|--|

| Bit                                             | : | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |

|                                                 |   | PA7ODR | PA60DR | PA5ODR | PA40DR | PA3ODR | PA2ODR | PA10DR | PA00DR |  |

| Initial value                                   | : | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |  |

| Read/Write                                      | : | R/W    |  |

Controls the PMOS on/off status for each port A pin (PA7 to PA0)

| BRR2—B                            | Bit Rate | e Registe | r 2 | H'FF89 | SCI2, Sn | nart Card | Interface 2 |     |     |

|-----------------------------------|----------|-----------|-----|--------|----------|-----------|-------------|-----|-----|

| Bit                               | :        | 7         | 6   | 5      | 4        | 3         | 2           | 1   | 0   |

|                                   |          |           |     |        |          |           |             |     |     |

| Initial va                        | lue :    | 1         | 1   | 1      | 1        | 1         | 1           | 1   | 1   |

| Read/W                            | rite :   | R/W       | R/W | R/W    | R/W      | R/W       | R/W         | R/W | R/W |

|                                   |          |           |     |        |          |           |             |     |     |

| Sets the serial transfer bit rate |          |           |     |        |          |           |             |     |     |

|                                   |          |           |     |        |          |           |             |     |     |

Note: For details, see section 14.2.8, Bit Rate Register (BRR).

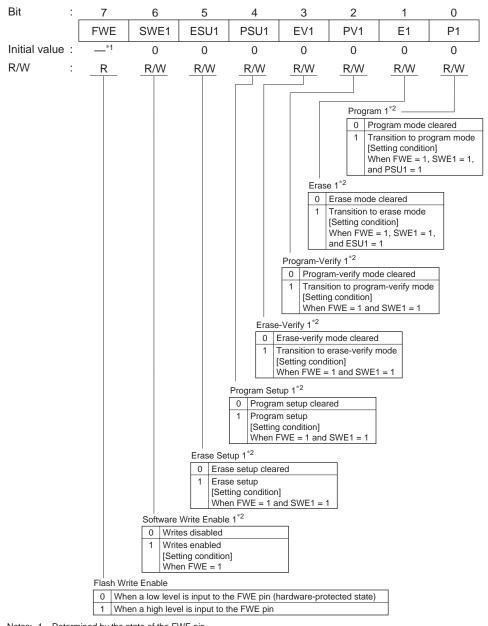

### FLMCR1—Flash Memory Control Register 1 (H8S/2326 F-ZTAT)

H'FFC8

**Flash Memory**

Notes: 1. Determined by the state of the FWE pin.

2. Applicable addresses are H'000000 to H'03FFFF.

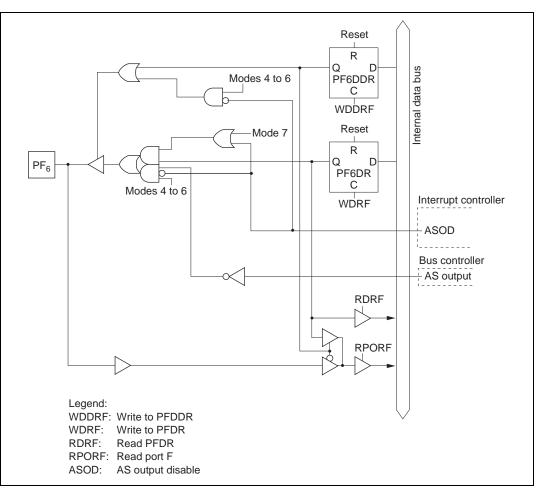

Figure C.12 (g) Port F Block Diagram (Pin PF<sub>6</sub>)

| Port Name<br>Pin Name              | MCU<br>Operating<br>Mode | Reset | Hardware<br>Standby<br>Mode | Software<br>Standby Mode                                                                  | Bus-Released<br>State | Program<br>Execution State<br>Sleep Mode                               |

|------------------------------------|--------------------------|-------|-----------------------------|-------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------|

| PG <sub>0</sub> /CAS <sup>*3</sup> | 4 to 6                   | Т     | Т                           | $[DRAME^{*4} = 0]$ kept $[DRAME^{*4} \cdot OPE = 1]$ T $[DRAME^{*4} \cdot OPE = 1]$ CAS*3 | Т                     | $[DRAME^{*4} = 0]$ Input port $[DRAME^{*4} = 1]$ $\overline{CAS}^{*3}$ |

|                                    | 7                        | Т     | Т                           | kept                                                                                      | kept                  | I/O port                                                               |

- Legend:

- H: High level

- L: Low level

- T: High impedance

- kept: Input port becomes high-impedance, output port retains state

- DDR: Data direction register

- OPE: Output port enable

- WAITE: Wait input enable

- WAITPS: WAIT pin select

- BRLE: Bus release enable

- BREQOE: BREQO pin enable

- **BREQOPS: BREQO pin select**

- DRAME: DRAM space setting

- LCASE: DRAM space setting, 16-bit access setting

- AnE: Address n enable (n = 23 to 21)

- A20E: Address 20 enable

- ASOD: AS output disable

- CS167E: CS167 enable

- CS25E: CS25 enable

- LWROD: LWR output disable

- Notes: 1.  $\overline{\text{LCAS}}$  is not supported in the H8S/2321.

- 2. As the DRAM interface is not supported in the H8S/2321, LCASE is always 0.

- 3.  $\overline{CAS}$  is not supported in the H8S/2321.

- 4. As the DRAM interface is not supported in the H8S/2321, DRAME is always 0.

- 5. The  $\overline{\text{WDTOVF}}$  pin function is not usable on the F-ZTAT version.

- 6. A low level is output if a WDT overflow occurs while WT/IT is set to 1.

# Renesas