Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active              |

|----------------------------|---------------------|

| Core Processor             | H8S/2000            |

| Core Size                  | 16-Bit              |

| Speed                      | 25MHz               |

| Connectivity               | SCI, SmartCard      |

| Peripherals                | DMA, POR, PWM, WDT  |

| Number of I/O              | 86                  |

| Program Memory Size        | -                   |

| Program Memory Type        | ROMIess             |

| EEPROM Size                | -                   |

| RAM Size                   | 32K x 8             |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V         |

| Data Converters            | A/D 8x10b; D/A 2x8b |

| Oscillator Type            | Internal            |

| Operating Temperature      | -20°C ~ 75°C (TA)   |

| Mounting Type              | Surface Mount       |

| Package / Case             | 120-TQFP            |

| Supplier Device Package    | 120-TQFP (14x14)    |

|                            |                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|      | 9.5.1   | Overview                   |     |

|------|---------|----------------------------|-----|

|      | 9.5.2   | Register Configuration     |     |

|      | 9.5.3   | Pin Functions              |     |

| 9.6  | Port 5. |                            |     |

|      | 9.6.1   | Overview                   |     |

|      | 9.6.2   | Register Configuration     |     |

|      | 9.6.3   | Pin Functions              |     |

| 9.7  | Port 6. |                            |     |

|      | 9.7.1   | Overview                   |     |

|      | 9.7.2   | Register Configuration     |     |

|      | 9.7.3   | Pin Functions              |     |

| 9.8  | Port A  |                            |     |

|      | 9.8.1   | Overview                   |     |

|      | 9.8.2   | Register Configuration     |     |

|      | 9.8.3   | Pin Functions              |     |

|      | 9.8.4   | MOS Input Pull-Up Function |     |

| 9.9  | Port B  |                            |     |

|      | 9.9.1   | Overview                   |     |

|      | 9.9.2   | Register Configuration     |     |

|      | 9.9.3   | Pin Functions              |     |

|      | 9.9.4   | MOS Input Pull-Up Function |     |

| 9.10 | Port C  |                            |     |

|      | 9.10.1  | Overview                   |     |

|      | 9.10.2  | Register Configuration     | 411 |

|      | 9.10.3  | Pin Functions              |     |

|      | 9.10.4  | MOS Input Pull-Up Function |     |

| 9.11 | Port D  |                            | 416 |

|      | 9.11.1  | Overview                   |     |

|      | 9.11.2  | Register Configuration     | 417 |

|      | 9.11.3  | Pin Functions              |     |

|      | 9.11.4  | MOS Input Pull-Up Function |     |

| 9.12 | Port E  |                            |     |

|      | 9.12.1  | Overview                   |     |

|      | 9.12.2  | Register Configuration     |     |

|      | 9.12.3  | Pin Functions              |     |

|      | 9.12.4  | MOS Input Pull-Up Function |     |

| 9.13 | Port F. |                            |     |

|      |         | Overview                   |     |

|      | 9.13.2  | Register Configuration     |     |

|      | 9.13.3  | Pin Functions              |     |

# Section 2 CPU

## 2.1 Overview

The H8S/2000 CPU is a high-speed central processing unit with an internal 32-bit architecture that is upward-compatible with the H8/300 and H8/300H CPUs. The H8S/2000 CPU has sixteen 16-bit general registers, can address a 16-Mbyte (architecturally 4-Gbyte) linear address space, and is ideal for realtime control.

### 2.1.1 Features

The H8S/2000 CPU has the following features.

- Upward-compatible with H8/300 and H8/300H CPUs

- Can execute H8/300 and H8/300H object programs

- General-register architecture

- Sixteen 16-bit general registers (also usable as sixteen 8-bit registers or eight 32-bit registers)

- Sixty-five basic instructions

- 8/16/32-bit arithmetic and logic instructions

- Multiply and divide instructions

- Powerful bit-manipulation instructions

- Eight addressing modes

- Register direct [Rn]

- Register indirect [@ERn]

- Register indirect with displacement [@(d:16,ERn) or @(d:32,ERn)]

- Register indirect with post-increment or pre-decrement [@ERn+ or @-ERn]

- Absolute address [@aa:8, @aa:16, @aa:24, or @aa:32]

- Immediate [#xx:8, #xx:16, or #xx:32]

- Program-counter relative [@(d:8,PC) or @(d:16,PC)]

- Memory indirect [@@aa:8]

- 16-Mbyte address space

- Program: 16 Mbytes

- Data: 16 Mbytes (4 Gbytes architecturally)

- High-speed operation

- All frequently-used instructions execute in one or two states

- Maximum clock rate: 25 MHz

- 8/16/32-bit register-register add/subtract: 40 ns

- -- 8 × 8-bit register-register multiply: 480 ns

- $-16 \div 8$ -bit register-register divide: 480 ns

- $-16 \times 16$ -bit register-register multiply: 800 ns

- $-32 \div 16$ -bit register-register divide: 800 ns

- CPU operating mode

- Advanced mode

- Power-down state

- Transition to power-down state by SLEEP instruction

- CPU clock speed selection

### 2.1.2 Differences between H8S/2600 CPU and H8S/2000 CPU

The differences between the H8S/2600 CPU and the H8S/2000 CPU are as shown below.

• Register configuration

The MAC register is supported only by the H8S/2600 CPU.

Basic instructions

The four instructions MAC, CLRMAC, LDMAC, and STMAC are supported only by the H8S/2600 CPU.

• Number of execution states

The number of exection states of the MULXU and MULXS instructions.

|             |                 | In       | ternal Operation |  |

|-------------|-----------------|----------|------------------|--|

| Instruction | Mnemonic        | H8S/2600 | H8S/2000         |  |

| MULXU       | MULXU.B Rs, Rd  | 3        | 12               |  |

|             | MULXU.W Rs, ERd | 4        | 20               |  |

| MULXS       | MULXS.B Rs, Rd  | 4        | 13               |  |

|             | MULXS.W Rs, ERd | 5        | 21               |  |

There are also differences in the address space, CCR and EXR functions, power-down state, etc., depending on the product.

### (2) Reset Exception Handling

After the  $\overline{\text{RES}}$  pin has gone low and the reset state has been entered, when  $\overline{\text{RES}}$  goes high again, reset exception handling starts. When reset exception handling starts the CPU fetches a start address (vector) from the exception vector table and starts program execution from that address. All interrupts, including NMI, are disabled during reset exception handling and after it ends.

### (3) Traces

Traces are enabled only in interrupt control mode 2. Trace mode is entered when the T bit of EXR is set to 1. When trace mode is established, trace exception handling starts at the end of each instruction.

At the end of a trace exception-handling sequence, the T bit of EXR is cleared to 0 and trace mode is cleared. Interrupt masks are not affected.

The T bit saved on the stack retains its value of 1, and when the RTE instruction is executed to return from the trace exception-handling routine, trace mode is entered again. Trace exception-handling is not executed at the end of the RTE instruction.

Trace mode is not entered in interrupt control mode 0, regardless of the state of the T bit.

### (4) Interrupt Exception Handling and Trap Instruction Exception Handling

When interrupt or trap-instruction exception handling begins, the CPU references the stack pointer (ER7) and pushes the program counter and other control registers onto the stack. Next, the CPU alters the settings of the interrupt mask bits in the control registers. Then the CPU fetches a start address (vector) from the exception vector table and program execution starts from that start address.

Figure 2.13 shows the stack after exception handling ends.

| Bit 3<br>FLSHE | Description                                                                                 |

|----------------|---------------------------------------------------------------------------------------------|

| 0              | Flash control registers are not selected for addresses H'FFFFC8 to H'FFFFCB (Initial value) |

| 1              | Flash control registers are not selected for addresses H'FFFFC8 to H'FFFFCB                 |

Bits 2 and 1—Reserved: These bits are always read as 0. Only 0 should be written to these bits.

**Bit 0—Reserved:** In the H8S/2328B F-ZTAT and H8S/2326 F-ZTAT, this bit is always read as 0 and should only be written with 0. In the H8S/2329B F-ZTAT, this bit is reserved and should only be written with 0.

### **3.3 Operating Mode Descriptions**

### 3.3.1 Mode 1

The H8S/2329 does not support mode 1. Do not select the mode 1 setting.

### 3.3.2 Mode 2 (H8S/2329B F-ZTAT Only)

This is a flash memory boot mode. See section 19, ROM, for details. This is the same as advanced on-chip ROM enabled expansion mode, except when erasing and reprogramming flash memory.

### 3.3.3 Mode 3 (H8S/2329B F-ZTAT Only)

This is a flash memory boot mode. See section 19, ROM, for details. This is the same as advanced single-chip ROM mode, except when erasing and reprogramming flash memory.

### 3.3.4 Mode 4 (Expanded Mode with On-Chip ROM Disabled)

The CPU can access a 16-Mbyte address space in advanced mode. The on-chip ROM is disabled.

Ports A, B, and C function as an address bus, port D functions as a data bus, and part of port F carries bus control signals.

The initial bus mode after a reset is 16 bits, with 16-bit access to all areas. However, note that if 8-bit access is designated by the bus controller for all areas, the bus mode switches to 8 bits.

#### 3.3.10 Mode 11 (H8S/2328B F-ZTAT and H8S/2326 F-ZTAT Only)

This is a flash memory boot mode. For details, see section 19, ROM.

Except for the fact that flash memory programming and erasing can be performed, operation in this mode is the same as in advanced single-chip mode.

### 3.3.11 Modes 12 and 13

Modes 12 and 13 are not supported and must not be set.

### 3.3.12 Mode 14 (H8S/2328B F-ZTAT and H8S/2326 F-ZTAT Only)

This is a flash memory user program mode. For details, see section 19, ROM.

Except for the fact that flash memory programming and erasing can be performed, operation in this mode is the same as in advanced expanded mode with on-chip ROM enabled.

### 3.3.13 Mode 15 (H8S/2328B F-ZTAT and H8S/2326 F-ZTAT Only)

This is a flash memory user program mode. For details, see section 19, ROM.

Except for the fact that flash memory programming and erasing can be performed, operation in this mode is the same as in advanced single-chip mode.

## **3.4 Pin Functions in Each Operating Mode**

The pin functions of ports A to F vary depending on the operating mode. Table 3.4 shows their functions in each operating mode.

| Interrupt Source        | Origin of<br>Interrupt<br>Source | Vector<br>Number | Vector<br>Address <sup>*1</sup> | IPR               | Priority | DTC<br>Activa-<br>tion | DMAC <sup>*2</sup><br>Activa-<br>tion |

|-------------------------|----------------------------------|------------------|---------------------------------|-------------------|----------|------------------------|---------------------------------------|

| Power-on reset          |                                  | 0                | H'0000                          | _                 | High     | _                      | _                                     |

| Reserved                |                                  | 1                | H'0004                          | -                 | Ť        |                        |                                       |

| Reserved for system     |                                  | 2                | H'0008                          | -                 |          |                        |                                       |

| use                     |                                  | 3                | H'000C                          | _                 |          |                        |                                       |

|                         |                                  | 4                | H'0010                          | -                 |          |                        |                                       |

| Trace                   |                                  | 5                | H'0014                          | -                 |          |                        |                                       |

| Reserved for system use |                                  | 6                | H'0018                          | _                 |          |                        |                                       |

| NMI                     | External<br>pin                  | 7                | H'001C                          | =                 |          |                        |                                       |

| Trap instruction        |                                  | 8                | H'0020                          | -                 |          |                        |                                       |

| (4 sources)             |                                  | 9                | H'0024                          | -                 |          |                        |                                       |

|                         |                                  | 10               | H'0028                          | -                 |          |                        |                                       |

|                         |                                  | 11               | H'002C                          | -                 |          |                        |                                       |

| Reserved for system     |                                  | 12               | H'0030                          | -                 |          |                        |                                       |

| use                     |                                  | 13               | H'0034                          | -                 |          |                        |                                       |

|                         |                                  | 14               | H'0038                          | -                 |          |                        |                                       |

|                         |                                  | 15               | H'003C                          | _                 |          |                        |                                       |

| IRQ <sub>0</sub>        | External<br>pin                  | 16               | H'0040                          | IPRA6 to<br>IPRA4 | -        | 0                      | _                                     |

| IRQ <sub>1</sub>        | _                                | 17               | H'0044                          | IPRA2 to<br>IPRA0 | -        | 0                      | _                                     |

| IRQ <sub>2</sub>        |                                  | 18               | H'0048                          | IPRB6 to          | -        | 0                      | _                                     |

| IRQ <sub>3</sub>        | -                                | 19               | H'004C                          | IPRB4             |          | 0                      | _                                     |

| IRQ <sub>4</sub>        | _                                | 20               | H'0050                          | IPRB2 to          | -        | 0                      | _                                     |

| IRQ <sub>5</sub>        | _                                | 21               | H'0054                          | IPRB0             |          | 0                      | _                                     |

| IRQ <sub>6</sub>        | _                                | 22               | H'0058                          | IPRC6 to          | -        | 0                      | _                                     |

| IRQ <sub>7</sub>        |                                  | 23               | H'005C                          | IPRC4             | Low      | 0                      | _                                     |

### Table 5.4 Interrupt Sources, Vector Addresses, and Interrupt Priorities

### Port B Data Register (PBDR)

| Bit         | :     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|             |       | PB7DR | PB6DR | PB5DR | PB4DR | PB3DR | PB2DR | PB1DR | PB0DR |

| Initial val | lue : | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W         | :     | R/W   |

PBDR is an 8-bit readable/writable register that stores output data for the port B pins ( $PB_7$  to  $PB_0$ ). PBDR is initialized to H'00 by a reset, and in hardware standby mode. It retains its prior state in software standby mode.

### **Port B Register (PORTB)**

| Bit        | :     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------|-------|-----|-----|-----|-----|-----|-----|-----|-----|

|            |       | PB7 | PB6 | PB5 | PB4 | PB3 | PB2 | PB1 | PB0 |

| Initial va | lue : | *   | *   | *   | *   | *   | *   | *   | *   |

| R/W        | :     | R   | R   | R   | R   | R   | R   | R   | R   |

Note: \* Determined by state of pins PB7 to PB0.

PORTB is an 8-bit read-only register that shows the pin states. It cannot be written to. Writing of output data for the port B pins ( $PB_7$  to  $PB_0$ ) must always be performed on PBDR.

If a port B read is performed while PBDDR bits are set to 1, the PBDR values are read. If a port B read is performed while PBDDR bits are cleared to 0, the pin states are read.

After a reset and in hardware standby mode, PORTB contents are determined by the pin states, as PBDDR and PBDR are initialized. PORTB retains its prior state in software standby mode.

### 11.2.3 Next Data Registers H and L (NDRH, NDRL)

NDRH and NDRL are 8-bit readable/writable registers that store the next data for pulse output. During pulse output, the contents of NDRH and NDRL are transferred to the corresponding bits in PODRH and PODRL when the TPU compare match event specified by PCR occurs. The NDRH and NDRL addresses differ depending on whether pulse output groups have the same output trigger or different output triggers. For details see section 11.2.4, Notes on NDR Access.

NDRH and NDRL are each initialized to H'00 by a reset and in hardware standby mode. They are not initialized in software standby mode.

### 11.2.4 Notes on NDR Access

The NDRH and NDRL addresses differ depending on whether pulse output groups have the same output trigger or different output triggers.

**Same Trigger for Pulse Output Groups:** If pulse output groups 2 and 3 are triggered by the same compare match event, the NDRH address is H'FF4C. The upper 4 bits belong to group 3 and the lower 4 bits to group 2. Address H'FF4E consists entirely of reserved bits that cannot be modified and are always read as 1.

### Address H'FF4C

| Bit :           | 7          | 6     | 5     | 4     | 3     | 2     | 1    | 0    |

|-----------------|------------|-------|-------|-------|-------|-------|------|------|

|                 | NDR15      | NDR14 | NDR13 | NDR12 | NDR11 | NDR10 | NDR9 | NDR8 |

| Initial value : | 0          | 0     | 0     | 0     | 0     | 0     | 0    | 0    |

| R/W :           | R/W        | R/W   | R/W   | R/W   | R/W   | R/W   | R/W  | R/W  |

|                 |            |       |       |       |       |       |      |      |

| Address H'FF4   | <b>4</b> E |       |       |       |       |       |      |      |

| Bit :           | 7          | 6     | 5     | 4     | 3     | 2     | 1    | 0    |

|                 | _          | —     | —     | —     | _     | —     | _    |      |

| Initial value : | 1          | 1     | 1     | 1     | 1     | 1     | 1    | 1    |

| R/W :           | —          |       |       |       |       | _     | _    | _    |

If pulse output groups 0 and 1 are triggered by the same compare match event, the NDRL address is H'FF4D. The upper 4 bits belong to group 1 and the lower 4 bits to group 0. Address H'FF4F consists entirely of reserved bits that cannot be modified and are always read as 1.

### 12.3.5 Operation with Cascaded Connection

If bits CKS2 to CKS0 in either TCR0 or TCR1 are set to B'100, the 8-bit timers of the two channels are cascaded. With this configuration, a single 16-bit timer could be used (16-bit counter mode) or compare matches of the 8-bit channel 0 could be counted by the timer of channel 1 (compare match counter mode). In this case, the timer operates as below.

**16-Bit Counter Mode:** When bits CKS2 to CKS0 in TCR0 are set to B'100, the timer functions as a single 16-bit timer with channel 0 occupying the upper 8 bits and channel 1 occupying the lower 8 bits.

- Setting of compare match flags

- The CMF flag in TCSR0 is set to 1 when a 16-bit compare match event occurs.

- The CMF flag in TCSR1 is set to 1 when a lower 8-bit compare match event occurs.

- Counter clear specification

- If the CCLR1 and CCLR0 bits in TCR0 have been set for counter clear at compare match, the 16-bit counter (TCNT0 and TCNT1 together) is cleared when a 16-bit compare match event occurs. The 16-bit counter (TCNT0 and TCNT1 together) is cleared even if counter clear by the TMRI0 pin has also been set.

- The settings of the CCLR1 and CCLR0 bits in TCR1 are ignored. The lower 8 bits cannot be cleared independently.

- Pin output

- Control of output from the TMO0 pin by bits OS3 to OS0 in TCSR0 is in accordance with the 16-bit compare match conditions.

- Control of output from the TMO1 pin by bits OS3 to OS0 in TCSR1 is in accordance with the lower 8-bit compare match conditions.

**Compare Match Counter Mode:** When bits CKS2 to CKS0 in TCR1 are B'100, TCNT1 counts compare match A's for channel 0.

Channels 0 and 1 are controlled independently. Conditions such as setting of the CMF flag, generation of interrupts, output from the TMO pin, and counter clear are in accordance with the settings for each channel.

**Usage Note:** If the 16-bit counter mode and compare match counter mode are set simultaneously, the input clock pulses for TCNT0 and TCNT1 are not generated and thus the counters will stop operating. Software should therefore avoid using both these modes.

In serial reception, the SCI operates as described below.

[1] The SCI performs internal initialization in synchronization with serial clock input or output.

[2] The received data is stored in RSR in LSB-to-MSB order.

After reception, the SCI checks whether the RDRF flag is 0 and the receive data can be transferred from RSR to RDR.

If this check is passed, the RDRF flag is set to 1, and the receive data is stored in RDR. If a receive error is detected in the error check, the operation is as shown in table 14.11.

Neither transmit nor receive operations can be performed subsequently when a receive error has been found in the error check.

[3] If the RIE bit in SCR is set to 1 when the RDRF flag changes to 1, a receive-data-full interrupt (RXI) request is generated.

Also, if the RIE bit in SCR is set to 1 when the ORER flag changes to 1, a receive-error interrupt (ERI) request is generated.

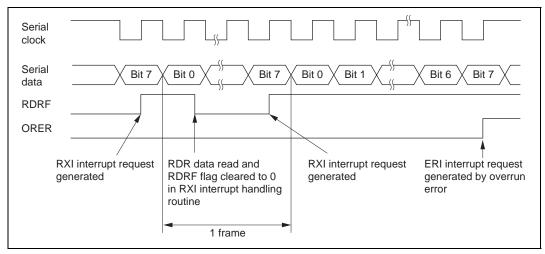

Figure 14.19 shows an example of SCI operation in reception.

Figure 14.19 Example of SCI Receive Operation

**Simultaneous serial data transmission and reception (synchronous mode):** Figure 14.20 shows a sample flowchart for simultaneous serial transmit and receive operations.

The following procedure should be used for simultaneous serial data transmit and receive operations.

**Break Detection and Processing (Asynchronous Mode Only):** When framing error (FER) detection is performed, a break can be detected by reading the RxD pin value directly. In a break, the input from the RxD pin becomes all 0s, and so the FER flag is set, and the parity error flag (PER) may also be set.

Note that, since the SCI continues the receive operation after receiving a break, even if the FER flag is cleared to 0, it will be set to 1 again.

**Sending a Break (Asynchronous Mode Only):** The TxD pin has a dual function as an I/O port whose direction (input or output) is determined by DR and DDR. This can be used to send a break.

Between serial transmission initialization and setting of the TE bit to 1, the mark state is replaced by the value of DR (the pin does not function as the TxD pin until the TE bit is set to 1). Therefore, DDR and DR for the port corresponding to the TxD pin should first be set to 1.

To send a break during serial transmission, first clear DR to 0, then clear the TE bit to 0.

When the TE bit is cleared to 0, the transmitter is initialized regardless of the current transmission state, the TxD pin becomes an I/O port, and 0 is output from the TxD pin.

**Receive Error Flags and Transmit Operations (Synchronous Mode Only):** Transmission cannot be started when a receive error flag (ORER, PER, or FER) is set to 1, even if the TDRE flag is cleared to 0. Be sure to clear the receive error flags to 0 before starting transmission.

Note also that receive error flags cannot be cleared to 0 even if the RE bit is cleared to 0.

**Receive Data Sampling Timing and Receive Margin in Asynchronous Mode:** In asynchronous mode, the SCI operates on a base clock with a frequency of 16 times the transfer rate.

In reception, the SCI samples the falling edge of the start bit using the base clock, and performs internal synchronization. Receive data is latched internally at the rising edge of the 8th pulse of the base clock. This is illustrated in figure 14.21.

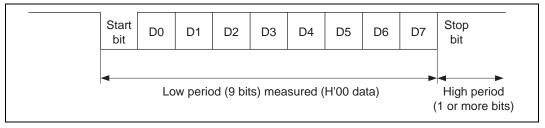

**Automatic SCI Bit Rate Adjustment:** When boot mode is initiated, the H8S/2329B F-ZTAT chip measures the low period of the asynchronous SCI communication data (H'00) transmitted continuously from the host. The SCI transmit/receive format should be set as follows: 8-bit data, 1 stop bit, no parity. The chip calculates the bit rate of the transmission from the host from the measured low period, and transmits one H'00 byte to the host to indicate the end of bit rate adjustment. The host should confirm that this adjustment end indication (H'00) has been received normally, and transmit one H'55 byte to the chip. If reception cannot be performed normally, initiate boot mode again (reset), and repeat the above operations. Depending on the host's transmission bit rate and the chip's system clock frequency, there will be a discrepancy between the bit rates of the host and the chip. To ensure correct SCI operation, the host's transfer bit rate should be set to 9,600 or 19,200 bps.

Table 19.10 shows typical host transfer bit rates and system clock frequencies for which automatic adjustment of the MCU's bit rate is possible. The boot program should be executed within this system clock range.

Figure 19.11 Automatic SCI Bit Rate Adjustment

| Table 19.10         System Clock Frequencies for which Automatic Adjustment of H8S/2329B |  |

|------------------------------------------------------------------------------------------|--|

| F-ZTAT Bit Rate is Possible                                                              |  |

| Host Bit Rate | System Clock Frequency for which Automatic Adjustment<br>of H8S/2329B F-ZTAT Bit Rate is Possible |

|---------------|---------------------------------------------------------------------------------------------------|

| 19,200 bps    | 16 MHz to 25 MHz                                                                                  |

| 9,600 bps     | 8 MHz to 25 MHz                                                                                   |

**On-Chip RAM Area Divisions in Boot Mode:** In boot mode, the 2-kbyte area from H'FF7C00 to H'FF83FF is reserved for use by the boot program, as shown in figure 19.12. The area to which the programming control program is transferred is H'FF8400 to H'FFFBFF. The boot program area can be used when the programming control program transferred into RAM enters the execution state. A stack area should be set up as required.

#### 19.11.10 Notes on Memory Programming

- When programming addresses which have previously been programmed, carry out autoerasing before auto-programming.

- When performing programming using PROM mode on a chip that has been programmed/erased in an on-board programming mode, auto-erasing is recommended before carrying out auto-programming.

- Notes: 1. The flash memory is initially in the erased state when the device is shipped by Renesas Technology. For other chips for which the erasure history is unknown, it is recommended that auto-erasing be executed to check and supplement the initialization (erase) level.

- 2. Auto-programming should be performed once only on the same address block. Additional programming cannot be carried out on address blocks that have already been programmed.

### 19.12 Flash Memory Programming and Erasing Precautions

Precautions concerning the use of on-board programming mode, the RAM emulation function, and PROM mode are summarized below.

**Use the specified voltages and timing for programming and erasing:** Applied voltages in excess of the rating can permanently damage the device. Use a PROM programmer that supports the Renesas microcomputer device type with 512-kbyte on-chip flash memory (FZTAT512V3A).

Do not select the HN27C4096 setting for the PROM programmer, and only use the specified socket adapter. Failure to observe these points may result in damage to the device.

**Powering on and off:** When applying or disconnecting  $V_{CC}$  power, fix the  $\overline{RES}$  pin low and place the flash memory in the hardware protection state.

The power-on and power-off timing requirements should also be satisfied in the event of a power failure and subsequent recovery.

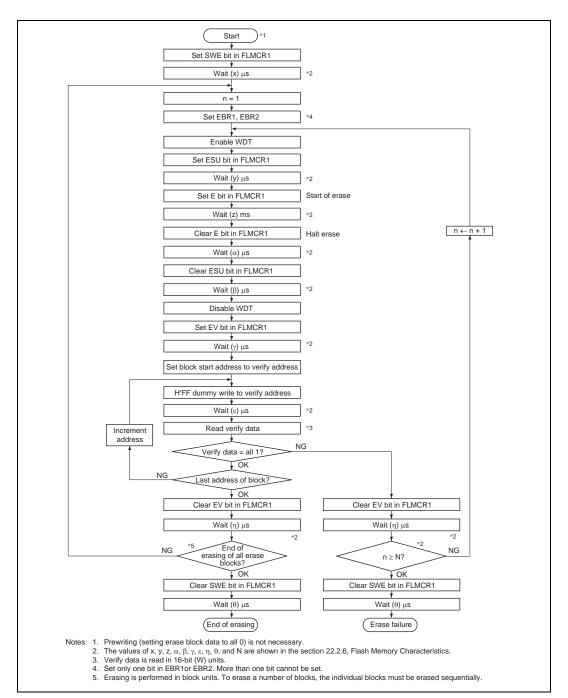

**Use the recommended algorithm when programming and erasing flash memory:** The recommended algorithm enables programming and erasing to be carried out without subjecting the device to voltage stress or sacrificing program data reliability. When setting the P or E bit in FLMCR1, the watchdog timer should be set beforehand as a precaution against program runaway, etc.

#### Figure 19.42 Erase/Erase-Verify Flowchart

# Section 22 Electrical Characteristics

## 22.1 Electrical Characteristics of Mask ROM Version (H8S/2328, H8S/2327, H8S/2323) and ROMless Version (H8S/2324S, H8S/2322R, H8S/2321, H8S/2320)

#### 22.1.1 Absolute Maximum Ratings

Table 22.1 lists the absolute maximum ratings.

| <b>Table 22.1</b> | Absolute Maximum Ratings |

|-------------------|--------------------------|

|-------------------|--------------------------|

| Item                           | Symbol           | Value                                 | Unit |

|--------------------------------|------------------|---------------------------------------|------|

| Power supply voltage           | V <sub>CC</sub>  | –0.3 to +4.6                          | V    |

| Input voltage (except port 4)  | Vin              | –0.3 to V <sub>CC</sub> +0.3          | V    |

| Input voltage (port 4)         | Vin              | -0.3 to AV <sub>CC</sub> +0.3         | V    |

| Reference power supply voltage | V <sub>ref</sub> | –0.3 to AV <sub>CC</sub> +0.3         | V    |

| Analog power supply voltage    | AV <sub>CC</sub> | -0.3 to +4.6                          | V    |

| Analog input voltage           | V <sub>AN</sub>  | –0.3 to AV <sub>CC</sub> +0.3         | V    |

| Operating temperature          | T <sub>opr</sub> | Regular specifications: -20 to +75    | °C   |

|                                |                  | Wide-range specifications: -40 to +85 | °C   |

| Storage temperature            | T <sub>stg</sub> | –55 to +125                           | °C   |

Caution: Permanent damage to the chip may result if absolute maximum ratings are exceeded.

| _           |                    |             |               | _                 | _                 | _               | _              | _                |                   | _                  | _                  | _             |                 | _                | _                 | -                 | _             | _               | _                | _                 | _                 | _             | _                 | _                 | _                 | _                 |                | _                | _                 | _                  | _                  |              |                | _               | _                | _                | _             |

|-------------|--------------------|-------------|---------------|-------------------|-------------------|-----------------|----------------|------------------|-------------------|--------------------|--------------------|---------------|-----------------|------------------|-------------------|-------------------|---------------|-----------------|------------------|-------------------|-------------------|---------------|-------------------|-------------------|-------------------|-------------------|----------------|------------------|-------------------|--------------------|--------------------|--------------|----------------|-----------------|------------------|------------------|---------------|

| 6           |                    |             |               |                   |                   |                 |                |                  |                   |                    |                    |               |                 |                  |                   |                   |               |                 |                  |                   |                   |               |                   |                   |                   |                   |                |                  |                   |                    |                    |              |                |                 |                  |                  |               |

| 80          |                    |             |               |                   |                   |                 |                |                  |                   |                    |                    |               |                 |                  |                   |                   |               |                 |                  |                   |                   |               |                   |                   |                   |                   |                |                  |                   |                    |                    |              |                |                 |                  |                  |               |

| 7           |                    |             |               |                   |                   |                 |                |                  |                   |                    |                    |               |                 |                  |                   |                   |               |                 |                  |                   |                   |               |                   |                   |                   |                   |                |                  |                   |                    |                    |              |                |                 |                  |                  |               |

| 9           | W:B EA             |             |               |                   |                   | W:B EA          |                |                  |                   |                    |                    |               |                 |                  |                   |                   |               |                 |                  |                   |                   |               |                   |                   |                   | W:B EA            |                |                  |                   |                    |                    |              |                |                 |                  |                  |               |

| 5           | R:W:M NEXT         |             |               |                   | W:B EA            | R:W:M NEXT      |                |                  |                   |                    | R:W:M NEXT         |               |                 |                  |                   | R:W:M NEXT        |               |                 |                  |                   | R:W:M NEXT        |               |                   |                   | W:B EA            | R:W:M NEXT        |                |                  |                   |                    | R:W:M NEXT         |              |                |                 |                  | R:W:M NEXT       |               |

| 4           | R:B:M EA           |             | W:B EA        | W:B EA            | R:W:M NEXT W:B EA | R:B:M EA        |                |                  |                   | R:W:M NEXT         | R:B EA             |               |                 |                  | R:W:M NEXT        | R:B EA            |               |                 |                  | R:W:M NEXT        | R:B EA            |               | W:B EA            | W:B EA            | R:W:M NEXT W:B EA | R:B:M EA          |                |                  |                   | R:W:M NEXT         | R:B EA             |              |                |                 | R:W:M NEXT       | R:B EA           |               |

| 3           | R:W 4th            |             | R:W:M NEXT    | R:W:M NEXT W:B EA | R:B:M EA          | R:W 4th         |                | R:W:M NEXT       | R:W:M NEXT        | R:B EA             | R:W 4th            |               | R:W:M NEXT      | R:W:M NEXT       | R:B EA            | R:W 4th           |               | R:W:M NEXT      | R:W:M NEXT       | R:B EA            | R:W 4th           |               | R:W:M NEXT W:B EA | R:W:M NEXT W:B EA | R:B:M EA          | R:W 4th           |                | R:W:M NEXT       | R:W:M NEXT        | R:B EA             | R:W 4th            |              | R:W:M NEXT     | R:W:M NEXT      | R:B EA           | R:W 4th          |               |

| 2           | R:W 3rd            |             | R:B:M EA      | R:B:M EA          | R:W 3rd           | R:W 3rd         |                | R:B EA           | R:B EA            | R:W 3rd            | R:W 3rd            |               | R:B EA          | R:B EA           | R:W 3rd           | R:W 3rd           |               | R:B EA          | R:B EA           | R:W 3rd           | R:W 3rd           |               | R:B:M EA          | R:B:M EA          | R:W 3rd           | R:W 3rd           |                | R:B EA           | R:B EA            | R:W 3rd            | R:W 3rd            |              | R:B EA         | R:B EA          | R:W 3rd          | R:W 3rd          |               |

| -           | R:W 2nd            | R:W NEXT    | R:W 2nd       | R:W 2nd           | R:W 2nd           | R:W 2nd         | R:W NEXT       | R:W 2nd          | R:W 2nd           | R:W 2nd            | R:W 2nd            | R:W NEXT      | R:W 2nd         | R:W 2nd          | R:W 2nd           | R:W 2nd           | R:W NEXT      | R:W 2nd         | R:W 2nd          | R:W 2nd           | R:W 2nd           | R:W NEXT      | R:W 2nd           | R:W 2nd           | R:W 2nd           | R:W 2nd           | R:W NEXT       | R:W 2nd          | R:W 2nd           | R:W 2nd            | R:W 2nd            | R:W NEXT     | R:W 2nd        | R:W 2nd         | R:W 2nd          | R:W 2nd          | R:W NEXT      |

| Instruction | BCLR #xx:3, @aa:32 | BCLR Rn, Rd | BCLR Rn, @ERd | BCLR Rn, @aa:8    | BCLR Rn, @aa:16   | BCLR Rn, @aa:32 | BIAND #xx:3,Rd | BIAND #xx:3,@ERd | BIAND #xx:3,@aa:8 | BIAND #xx:3,@aa:16 | BIAND #xx:3,@aa:32 | BILD #xx:3,Rd | BILD #xx:3,@ERd | BILD #xx:3,@aa:8 | BILD #xx:3,@aa:16 | BILD #xx:3,@aa:32 | BIOR #xx:3,Rd | BIOR #xx:3,@ERd | BIOR #xx:3,@aa:8 | BIOR #xx:3,@aa:16 | BIOR #xx:3,@aa:32 | BIST #xx:3,Rd | BIST #xx:3,@ERd   | BIST #xx:3,@aa:8  | BIST #xx:3,@aa:16 | BIST #xx:3,@aa:32 | BIXOR #xx:3,Rd | BIXOR #xx:3,@ERd | BIXOR #xx:3,@aa:8 | BIXOR #xx:3,@aa:16 | BIXOR #xx:3,@aa:32 | BLD #xx:3,Rd | BLD #xx:3,@ERd | BLD #xx:3,@aa:8 | BLD #xx:3,@aa:16 | BLD #xx:3,@aa:32 | BNOT #xx:3,Rd |

Appendix A Instruction Set

Rev.6.00 Sep. 27, 2007 Page 1040 of 1268 REJ09B0220-0600

#### TIOR3L—Timer I/O Control Register 3L

#### **H'FE83**

**TPU3**

| Bit :           | 7    | 6    | 5    | 4     |                                                    | 3    |       | 2                 | 1                                        | 0                         | _                                              |  |  |  |

|-----------------|------|------|------|-------|----------------------------------------------------|------|-------|-------------------|------------------------------------------|---------------------------|------------------------------------------------|--|--|--|

|                 | IOD3 | IOD2 | IOD1 | IOD   | 0                                                  | 100  | 23    | IOC2              | IOC1                                     | IOC0                      |                                                |  |  |  |

| Initial value : | 0    | 0    | 0    | 0     |                                                    | C    |       | 0                 | 0 0                                      |                           |                                                |  |  |  |

| Read/Write :    | R/W  | R/W  | R/W  | R/W   | <u>/</u>                                           | _R/  | N     | R/W               | R/W                                      | R/W                       |                                                |  |  |  |

|                 |      |      |      |       |                                                    |      |       |                   |                                          |                           |                                                |  |  |  |

|                 |      |      |      | TGR   | 3C I.                                              | /0 C | ontro | ol                | I                                        |                           |                                                |  |  |  |

|                 |      |      |      | 0     | 0 0 0 TGR3C Output disabled                        |      |       |                   |                                          |                           |                                                |  |  |  |

|                 |      |      |      |       |                                                    |      | 1     | is output compare | Initial outpu<br>0 output                | ut is                     | output at compare match                        |  |  |  |

|                 |      |      |      |       |                                                    | 1    | 0     | register*1        | 0 output                                 |                           | 1 output at compare match                      |  |  |  |

|                 |      |      |      |       |                                                    |      | 1     | 1                 |                                          |                           | Toggle output at compare match                 |  |  |  |

|                 |      |      |      |       | 1                                                  | 0    | 0     | 1                 | Output disa                              | abled                     |                                                |  |  |  |

|                 |      |      |      |       | 1 Initial output is 1 0 output at compare materies |      |       |                   |                                          |                           | 0 output at compare match                      |  |  |  |

|                 |      |      |      |       | 1 0 Output 1 output at comp                        |      |       |                   |                                          | 1 output at compare match |                                                |  |  |  |

|                 |      |      |      |       |                                                    |      | 1     |                   |                                          |                           | Toggle output at compare match                 |  |  |  |

|                 |      |      |      | 1     | 0                                                  | 0    | 0     | TGR3C<br>is input | Capture in<br>source is                  | put                       | Input capture at rising edge                   |  |  |  |

|                 |      |      |      |       |                                                    |      | 1     | capture           | TIOCC <sub>3</sub> pi                    | n                         | Input capture at falling edge                  |  |  |  |

|                 |      |      |      |       |                                                    | 1    | *     | register*1        |                                          |                           | Input capture at both edges                    |  |  |  |

|                 |      |      |      |       | 1                                                  | *    | *     |                   | Capture in<br>source is c<br>4/count clo | hannel                    | Input capture at TCNT4 count-up/<br>count-down |  |  |  |

|                 |      |      |      | Note: | 1 1                                                | Nhor | the   |                   |                                          | oot to 1                  | * : Don't care                                 |  |  |  |

Note: 1. When the BFA bit in TMDR3 is set to 1 and TGR3C is used as a buffer register, this setting is invalid and input capture/output compare does not occur.

#### TGR3D I/O Control

| 0 | 0 | 0 | 0 | TGR3D               | Output disabled                                     |                                                  |  |  |  |  |  |  |  |

|---|---|---|---|---------------------|-----------------------------------------------------|--------------------------------------------------|--|--|--|--|--|--|--|

|   |   |   | 1 | is output compare   | Initial output is 0<br>output                       | 0 output at compare match                        |  |  |  |  |  |  |  |

|   |   | 1 | 0 | register<br>*2      | ouipui                                              | 1 output at compare match                        |  |  |  |  |  |  |  |

|   |   |   | 1 |                     |                                                     | Toggle output at compare match                   |  |  |  |  |  |  |  |

|   | 1 | 0 | 0 |                     | Output disabled                                     |                                                  |  |  |  |  |  |  |  |

|   |   |   | 1 |                     | Initial output is 1<br>output                       | 0 output at compare match                        |  |  |  |  |  |  |  |

|   |   | 1 | 0 |                     | ouipui                                              | 1 output at compare match                        |  |  |  |  |  |  |  |

|   |   |   | 1 |                     |                                                     | Toggle output at compare match                   |  |  |  |  |  |  |  |

| 1 | 0 | 0 | 0 | TGR3D               | Capture input<br>source is                          | Input capture at rising edge                     |  |  |  |  |  |  |  |

|   |   |   | 1 | is input<br>capture | TIOCD <sub>3</sub> pin                              | Input capture at falling edge                    |  |  |  |  |  |  |  |

|   |   | 1 | * | register<br>*2      |                                                     | Input capture at both edges                      |  |  |  |  |  |  |  |

|   | 1 | * | * |                     | Capture input<br>source is channel<br>4/count clock | Input capture at TCNT4 count-up/<br>count-down*1 |  |  |  |  |  |  |  |

\* : Don't care

- Notes: 1. When bits TPSC2 to TPSC0 in TCR4 are set to B'000 and \$\phi/1\$ is used as the TCNT4 count clock, this setting is invalid and input capture does not occur.

- 2. When the BFB bit in TMDR3 is set to 1 and TGR3D is used as a buffer register, this setting is invalid and input capture/output compare does not occur.

- Note: When TGRC or TGRD is designated for buffer operation, this setting is invalid and the register operates as a buffer register.

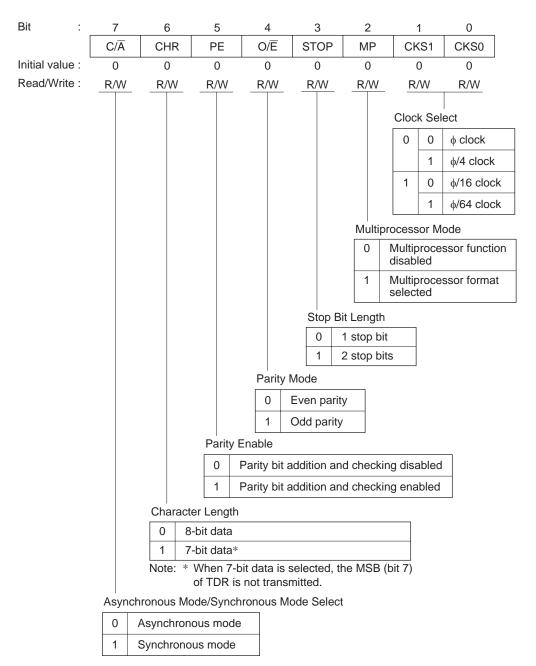

### SMR0—Serial Mode Register 0

H'FF78

SCI0

Note: If 0 is written to the CST bit during operation with the TIOC pin designated for output, the counter stops but the TIOC pin output compare output level is retained. If TIOR is written to when the CST bit is cleared to 0, the pin output level will be changed to the set initial output value.

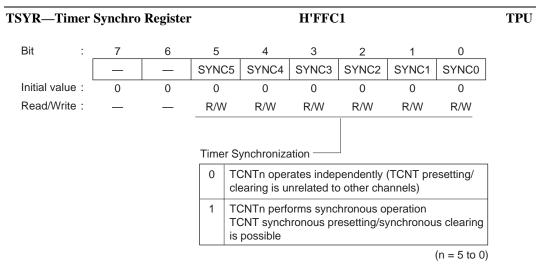

- Notes: 1. To set synchronous operation, the SYNC bits for at least two channels must be set to 1.

- 2. To set synchronous clearing, in addition to the SYNC bit , the TCNT clearing source must also be set by means of bits CCLR2 to CCLR0 in TCR.