#### Welcome to E-XFL.COM

Renesas Electronics America Inc - DF2326VF25V Datasheet

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                     |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 25MHz                                                                        |

| Connectivity               | SCI, SmartCard                                                               |

| Peripherals                | DMA, POR, PWM, WDT                                                           |

| Number of I/O              | 86                                                                           |

| Program Memory Size        | 512KB (512K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | <u>.</u>                                                                     |

| RAM Size                   | 8K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                  |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                          |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 128-BFQFP                                                                    |

| Supplier Device Package    | 128-QFP (14x20)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2326vf25v |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Item<br>Operating modes  | -                                                                                                                                                                                                                                                                         | <ul> <li>Specification</li> <li>Four MCU operating modes (ROMless, mask ROM versions, H8S/2329B</li> </ul> |                                     |          |          |             |  |  |  |  |  |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------|----------|----------|-------------|--|--|--|--|--|

|                          | F-2                                                                                                                                                                                                                                                                       | ZTAT)                                                                                                      | 0                                   |          |          |             |  |  |  |  |  |

|                          |                                                                                                                                                                                                                                                                           | CPU                                                                                                        |                                     |          | Extern   | al Data Bus |  |  |  |  |  |

|                          |                                                                                                                                                                                                                                                                           | Operating                                                                                                  |                                     | On-Chip  | Initial  | Maximum     |  |  |  |  |  |

|                          | Mode                                                                                                                                                                                                                                                                      | Mode                                                                                                       | Description                         | ROM      | Value    | Value       |  |  |  |  |  |

|                          | 1                                                                                                                                                                                                                                                                         | _                                                                                                          | _                                   | _        | _        | _           |  |  |  |  |  |

|                          | 2 <sup>*1</sup>                                                                                                                                                                                                                                                           | _                                                                                                          |                                     |          |          |             |  |  |  |  |  |

|                          | 3 <sup>*1</sup>                                                                                                                                                                                                                                                           |                                                                                                            |                                     |          |          |             |  |  |  |  |  |

|                          | 4 <sup>*2</sup>                                                                                                                                                                                                                                                           | Advanced                                                                                                   | On-chip ROM disabled expansion mode | Disabled | 16 bits  | 16 bits     |  |  |  |  |  |

|                          | 5 <sup>*2</sup>                                                                                                                                                                                                                                                           | _                                                                                                          | On-chip ROM disabled expansion mode | Disabled | 8 bits   | 16 bits     |  |  |  |  |  |

|                          | 6                                                                                                                                                                                                                                                                         | _                                                                                                          | On-chip ROM enabled expansion mode  | Enabled  | 8 bits   | 16 bits     |  |  |  |  |  |

|                          | 7                                                                                                                                                                                                                                                                         |                                                                                                            | Single-chip mode                    | Enabled  | _        | _           |  |  |  |  |  |

|                          | <ul> <li>Notes: 1. Boot mode in the H8S/2329B F-ZTAT. See table 19.9, for information on H8S/2329B F-ZTAT user boot modes. See table 19.9, for information on H8S/2329B F-ZTAT user program modes</li> <li>2. The ROMless versions can use only modes 4 and 5.</li> </ul> |                                                                                                            |                                     |          |          |             |  |  |  |  |  |

| Clock pulse<br>generator | • Bu                                                                                                                                                                                                                                                                      |                                                                                                            | rrection circuit                    |          | - and J. |             |  |  |  |  |  |

| Туре                     | Instruction | Size <sup>*1</sup> | Function                                                                                                                                                                                                       |

|--------------------------|-------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arithmetic<br>operations | DIVXS       | B/W                | Rd ÷ Rs → Rd<br>Performs signed division on data in two general<br>registers: either 16 bits ÷ 8 bits → 8-bit quotient and 8-bit<br>remainder or 32 bits ÷ 16 bits → 16-bit quotient and 16-<br>bit remainder. |

|                          | CMP         | B/W/L              | Rd – Rs, Rd – #IMM<br>Compares data in a general register with data in another<br>general register or with immediate data, and sets CCR<br>bits according to the result.                                       |

|                          | NEG         | B/W/L              | $0 - Rd \rightarrow Rd$<br>Takes the two's complement (arithmetic complement) of data in a general register.                                                                                                   |

|                          | EXTU        | W/L                | Rd (zero extension) $\rightarrow$ Rd<br>Extends the lower 8 bits of a 16-bit register to word size,<br>or the lower 16 bits of a 32-bit register to longword size,<br>by padding with zeros on the left.       |

|                          | EXTS        | W/L                | Rd (sign extension) $\rightarrow$ Rd<br>Extends the lower 8 bits of a 16-bit register to word size,<br>or the lower 16 bits of a 32-bit register to longword size,<br>by extending the sign bit.               |

|                          | TAS         | В                  | @ERd – 0, 1 → ( <bit 7=""> of @Erd)<sup>*2</sup><br/>Tests memory contents, and sets the most significant bit<br/>(bit 7) to 1.</bit>                                                                          |

## Bit 2—Data Transfer Interrupt Enable 1A (DTIE1A): Enables or disables the channel 1

transfer end interrupt.

| Bit 2<br>DTIE1A | Description                     |                 |

|-----------------|---------------------------------|-----------------|

| 0               | Transfer end interrupt disabled | (Initial value) |

| 1               | Transfer end interrupt enabled  |                 |

**Bit 0—Data Transfer Interrupt Enable 0A (DTIE0A):** Enables or disables the channel 0 transfer end interrupt.

| Bit 0<br>DTIE0A | Description                     |                 |

|-----------------|---------------------------------|-----------------|

| 0               | Transfer end interrupt disabled | (Initial value) |

| 1               | Transfer end interrupt enabled  |                 |

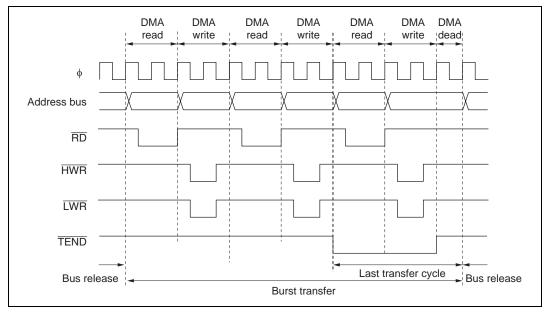

**Full Address Mode (Burst Mode):** Figure 7.21 shows a transfer example in which TEND output is enabled and word-size full address mode transfer (burst mode) is performed from external 16-bit, 2-state access space to external 16-bit, 2-state access space.

Figure 7.21 Example of Full Address Mode (Burst Mode) Transfer

In burst mode, one-byte or one-word transfers are executed consecutively until transfer ends.

In the transfer end cycle (the cycle in which the transfer counter reaches 0), a one-state DMA dead cycle is inserted after the DMA write cycle.

If a request from another higher-priority channel is generated after burst transfer starts, that channel has to wait until the burst transfer ends.

If an NMI is generated while a channel designated for burst transfer is in the transfer enabled state, the DTME bit is cleared and the channel is placed in the transfer disabled state. If burst transfer has already been activated inside the DMAC, the bus is released on completion of a one-byte or one-word transfer within the burst transfer, and burst transfer is suspended. If the last transfer cycle of the burst transfer has already been activated inside the DMAC, execution continues to the end of the transfer even if the DTME bit is cleared.

## Renesas

### Section 8 Data Transfer Controller

| Interrupt Source                             | Origin of<br>Interrupt<br>Source | Vector<br>Number | Vector<br>Address | DTCE <sup>*1</sup> | Priority |

|----------------------------------------------|----------------------------------|------------------|-------------------|--------------------|----------|

| TGI3A (GR3A compare match/<br>input capture) | TPU<br>channel 3                 | 48               | H'0460            | DTCEC5             | High     |

| TGI3B (GR3B compare match/<br>input capture) |                                  | 49               | H'0462            | DTCEC4             | —        |

| TGI3C (GR3C compare match/<br>input capture) |                                  | 50               | H'0464            | DTCEC3             |          |

| TGI3D (GR3D compare match/<br>input capture) |                                  | 51               | H'0466            | DTCEC2             |          |

| TGI4A (GR4A compare match/<br>input capture) | TPU<br>channel 4                 | 56               | H'0470            | DTCEC1             | _        |

| TGI4B (GR4B compare match/<br>input capture) |                                  | 57               | H'0472            | DTCEC0             |          |

| DMTEND0A (DMAC transfer complete 0)          | DMAC                             | 72               | H'0490            | DTCEE7             | _        |

| DMTEND0B (DMAC transfer complete 1           |                                  | 73               | H'0492            | DTCEE6             | _        |

| DMTEND1A (DMAC transfer complete 2)          |                                  | 74               | H'0494            | DTCEE5             |          |

| DMTEND1B (DMAC transfer complete 3)          |                                  | 75               | H'0496            | DTCEE4             | _        |

| TGI5A (GR5A compare match/<br>input capture) | TPU<br>channel 5                 | 60               | H'0478            | DTCED5             | _        |

| TGI5B (GR5B compare match/<br>input capture) |                                  | 61               | H'047A            | DTCED4             | _        |

| CMIA0                                        | 8-bit timer                      | 64               | H'0480            | DTCED3             |          |

| CMIB0                                        | channel 0                        | 65               | H'0482            | DTCED2             | _        |

| CMIA1                                        | 8-bit timer                      | 68               | H'0488            | DTCED1             | _        |

| CMIB1                                        | channel 1                        | 69               | H'048A            | DTCED0             | _        |

| DMTEND0A (DMAC transfer complete 0)          | DMAC*2                           | 72               | H'0490            | DTCEE7             | _        |

| DMTEND0B (DMAC transfer complete 1)          |                                  | 73               | H'0492            | DTCEE6             | _        |

| DMTEND1A (DMAC transfer complete 2)          |                                  | 74               | H'0494            | DTCEE5             | _        |

| DMTEND1B (DMAC transfer complete 3)          |                                  | 75               | H'0496            | DTCEE4             | <br>Low  |

### Port A Data Register (PADR)

| Bit         | :     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|             |       | PA7DR | PA6DR | PA5DR | PA4DR | PA3DR | PA2DR | PA1DR | PA0DR |

| Initial val | lue : | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W         | :     | R/W   |

PADR is an 8-bit readable/writable register that stores output data for the port A pins ( $PA_7$  to  $PA_0$ ).

PADR is initialized to H'00 by a reset, and in hardware standby mode. It retains its prior state in software standby mode.

### **Port A Register (PORTA)**

| Bit        | :     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------|-------|-----|-----|-----|-----|-----|-----|-----|-----|

|            | ſ     | PA7 | PA6 | PA5 | PA4 | PA3 | PA2 | PA1 | PA0 |

| Initial va | lue : | *   | *   | *   | *   | *   | *   | *   | *   |

| R/W        | :     | R   | R   | R   | R   | R   | R   | R   | R   |

Note: \* Determined by state of pins PA7 to PA0.

PORTA is an 8-bit read-only register that shows the pin states. It cannot be written to. Writing of output data for the port A pins ( $PA_7$  to  $PA_0$ ) must always be performed on PADR.

If a port A read is performed while PADDR bits are set to 1, the PADR values are read. If a port A read is performed while PADDR bits are cleared to 0, the pin states are read.

After a reset and in hardware standby mode, PORTA contents are determined by the pin states, as PADDR and PADR are initialized. PORTA retains its prior state in software standby mode.

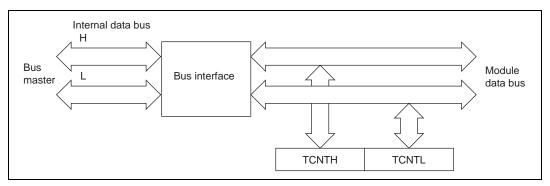

### **10.3** Interface to Bus Master

### 10.3.1 16-Bit Registers

TCNT and TGR are 16-bit registers. As the data bus to the bus master is 16 bits wide, these registers can be read and written to in 16-bit units.

These registers cannot be read or written to in 8-bit units; 16-bit access must always be used.

An example of 16-bit register access operation is shown in figure 10.2.

Figure 10.2 16-Bit Register Access Operation [Bus Master ↔ TCNT (16 Bits)]

#### 10.3.2 8-Bit Registers

Registers other than TCNT and TGR are 8-bit. As the data bus to the CPU is 16 bits wide, these registers can be read and written to in 16-bit units. They can also be read and written to in 8-bit units.

Examples of 8-bit register access operation are shown in figures 10.3 to 10.5.

## Renesas

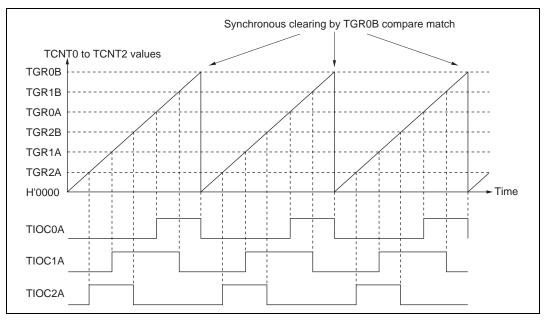

Example of Synchronous Operation: Figure 10.15 shows an example of synchronous operation.

In this example, synchronous operation and PWM mode 1 have been designated for channels 0 to 2, TGR0B compare match has been set as the channel 0 counter clearing source, and synchronous clearing has been set for the channel 1 and 2 counter clearing source.

Three-phase PWM waveforms are output from pins TIOC0A, TIOC1A, and TIOC2A. At this time, synchronous presetting, and synchronous clearing by TGR0B compare match, is performed for channel 0 to 2 TCNT counters, and the data set in TGR0B is used as the PWM cycle.

For details of PWM modes, see section 10.4.6, PWM Modes.

Figure 10.15 Example of Synchronous Operation

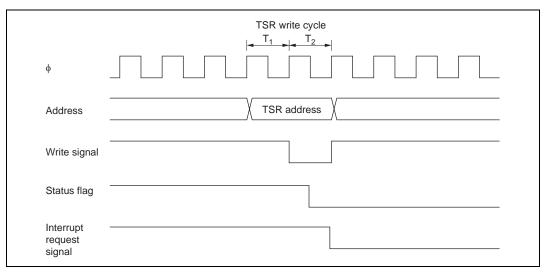

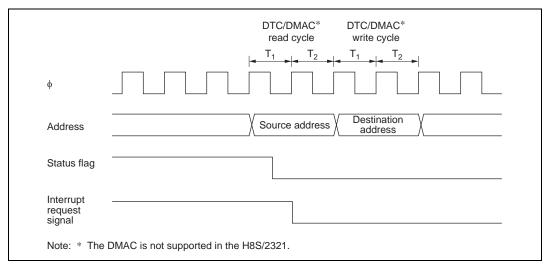

**Status Flag Clearing Timing:** After a status flag is read as 1 by the CPU, it is cleared by writing 0 to it. When the DTC or  $DMAC^*$  is activated, the flag is cleared automatically. Figure 10.46 shows the timing for status flag clearing by the CPU, and figure 10.47 shows the timing for status flag clearing by the DTC or  $DMAC^*$ .

Note: \* The DMAC is not supported in the H8S/2321.

Figure 10.46 Timing for Status Flag Clearing by CPU

Figure 10.47 Timing for Status Flag Clearing by DTC/DMAC Activation

## **13.2** Register Descriptions

### **13.2.1** Timer Counter (TCNT)

| Bit        | :     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|------------|-------|-----|-----|-----|-----|-----|-----|-----|-----|--|

|            |       |     |     |     |     |     |     |     |     |  |

| Initial va | lue : | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W        | :     | R/W |  |

TCNT is an 8-bit readable/writable<sup>\*1</sup> up-counter.

When the TME bit is set to 1 in TCSR, TCNT starts counting pulses generated from the internal clock source selected by bits CKS2 to CKS0 in TCSR. When the count overflows (changes from H'FF to H'00), either the watchdog timer overflow signal ( $\overline{WDTOVF}$ )<sup>\*2</sup> or an interval timer interrupt (WOVI) is generated, depending on the mode selected by the WT/ $\overline{IT}$  bit in TCSR.

TCNT is initialized to H'00 by a reset, in hardware standby mode, or when the TME bit is cleared to 0. It is not initialized in software standby mode.

- Notes: 1. TCNT is write-protected by a password to prevent accidental overwriting. For details see section 13.2.4, Notes on Register Access.

- 2. The  $\overline{WDTOVF}$  pin function cannot be used in the F-ZTAT versions.

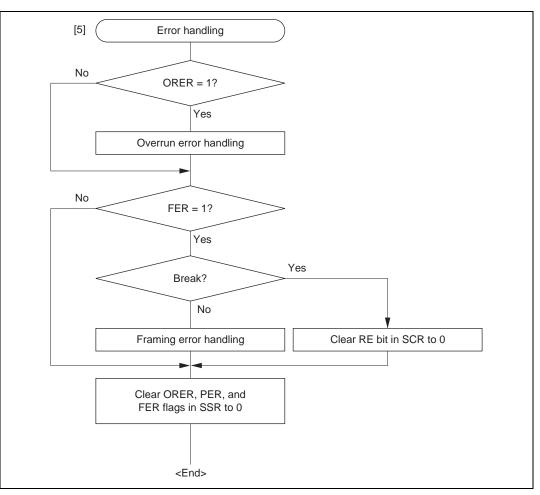

Figure 14.12 Sample Multiprocessor Serial Reception Flowchart (cont)

### **19.11.3 PROM Mode Operation**

Table 19.14 shows how the different operating modes are set when using PROM mode, and table 19.15 lists the commands used in PROM mode. Details of each mode are given below.

Memory Read Mode: Memory read mode supports byte reads.

**Auto-Program Mode:** Auto-program mode supports programming of 128 bytes at a time. Status polling is used to confirm the end of auto-programming.

**Auto-Erase Mode:** Auto-erase mode supports automatic erasing of the entire flash memory. Status polling is used to confirm the end of auto-erasing.

**Status Read Mode:** Status polling is used for auto-programming and auto-erasing, and normal termination can be confirmed by reading the  $I/O_6$  signal. In status read mode, error information is output if an error occurs.

### Table 19.14 Settings for Each Operating Mode in PROM Mode

|                            | Pin Names |    |    |                                      |                                   |  |  |  |

|----------------------------|-----------|----|----|--------------------------------------|-----------------------------------|--|--|--|

| Mode                       | CE        | ŌĒ | WE | I/O <sub>7</sub> to I/O <sub>0</sub> | A <sub>18</sub> to A <sub>0</sub> |  |  |  |

| Read                       | L         | L  | Н  | Data output                          | Ain                               |  |  |  |

| Output disable             | L         | Н  | Н  | Hi-Z                                 | Х                                 |  |  |  |

| Command write              | L         | Н  | L  | Data input                           | Ain <sup>*2</sup>                 |  |  |  |

| Chip disable <sup>*1</sup> | Н         | Х  | Х  | Hi-Z                                 | Х                                 |  |  |  |

Legend:

H: High level

L: Low level

Hi-Z: High impedance

X: Don't care

Notes: 1. Chip disable is not a standby state; internally, it is an operation state.

2. Ain indicates that there is also address input in auto-program mode.

### 19.13.8 Pin Configuration

The flash memory is controlled by means of the pins shown in tables 19.26.

| Pin Name           | Abbreviation | I/O    | Function                                   |

|--------------------|--------------|--------|--------------------------------------------|

| Reset              | RES          | Input  | Reset                                      |

| Flash write enable | FWE          | Input  | Flash program/erase protection by hardware |

| Mode 2             | MD2          | Input  | Sets MCU operating mode                    |

| Mode 1             | MD1          | Input  | Sets MCU operating mode                    |

| Mode 0             | MD0          | Input  | Sets MCU operating mode                    |

| Port 64            | P64          | Input  | Sets MCU operating mode in PROM mode       |

| Port 65            | P65          | Input  | Sets MCU operating mode in PROM mode       |

| Port 66            | P66          | Input  | Sets MCU operating mode in PROM mode       |

| Transmit data      | TxD1         | Output | Serial transmit data output                |

| Receive data       | RxD1         | Input  | Serial receive data input                  |

### Table 19.26 Flash Memory Pins

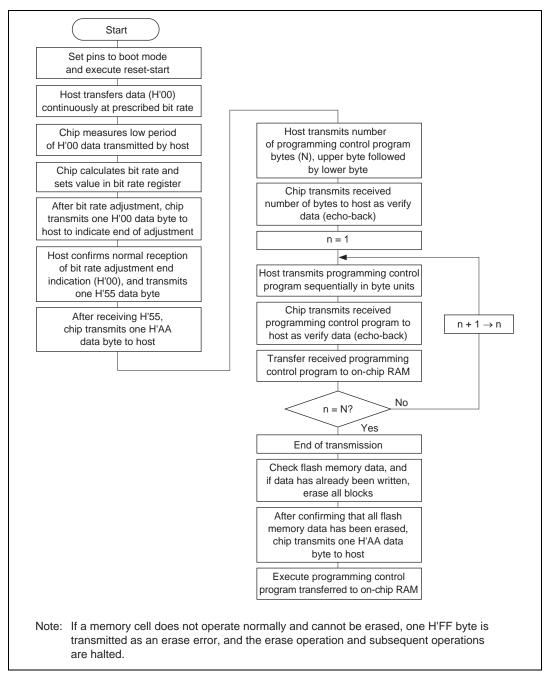

#### Figure 19.37 Boot Mode Execution Procedure

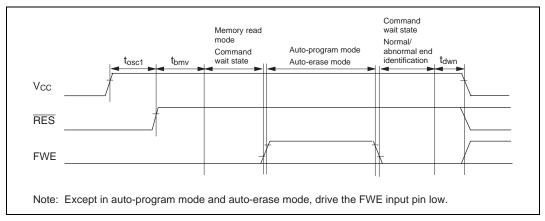

### 19.20.9 PROM Mode Transition Time

Commands cannot be accepted during the oscillation stabilization period or the PROM mode setup period. After the PROM mode setup time, a transition is made to memory read mode.

### Table 19.45 Command Wait State Transition Time Specifications

| Item                                             | Symbol            | Min | Max | Unit |  |

|--------------------------------------------------|-------------------|-----|-----|------|--|

| Standby release (oscillation stabilization time) | t <sub>osc1</sub> | 30  | _   | ms   |  |

| PROM mode setup time                             | t <sub>bmv</sub>  | 10  | —   | ms   |  |

| V <sub>CC</sub> hold time                        | t <sub>dwn</sub>  | 0   |     | ms   |  |

Figure 19.55 Oscillation Stabilization Time, PROM Mode Setup Time, and Power Supply Fall Sequence

#### 22.2.4 A/D Conversion Characteristics

#### Table 22.20 A/D Conversion Characteristics

Condition B:  $V_{CC} = 3.0 \text{ V}$  to 3.6 V,  $AV_{CC} = 3.0 \text{ V}$  to 3.6 V,  $V_{ref} = 3.0 \text{ V}$  to  $AV_{CC}$ ,  $V_{SS} = AV_{SS} = 0 \text{ V}$ ,  $\phi = 2 \text{ MHz}$  to 25 MHz,  $T_a = -20^{\circ}\text{C}$  to 75°C (regular specifications),  $T_a = -40^{\circ}\text{C}$  to 85°C (wide-range specifications)

|                                     |      | Conditio | on B |      |

|-------------------------------------|------|----------|------|------|

| Item                                | Min  | Тур      | Max  | Unit |

| Resolution                          | 10   | 10       | 10   | Bits |

| Conversion time                     | 10.6 | —        | _    | μS   |

| Analog input capacitance            | _    | _        | 20   | pF   |

| Permissible signal source impedance | _    | _        | 5    | kΩ   |

| Nonlinearity error                  | _    | _        | ±5.5 | LSB  |

| Offset error                        | _    | _        | ±5.5 | LSB  |

| Full-scale error                    | _    | _        | ±5.5 | LSB  |

| Quantization error                  | _    | _        | ±0.5 | LSB  |

| Absolute accuracy                   | _    | _        | ±6.0 | LSB  |

| Inctruc- |                     |      |          |      |          |     |          |          | Instruction Format | n Format |          |          |          |           |

|----------|---------------------|------|----------|------|----------|-----|----------|----------|--------------------|----------|----------|----------|----------|-----------|

| tion     | Mnemonic            | Size | 1st byte | oyte | 2nd byte | yte | 3rd byte | 4th byte | 5th byte           | 6th byte | 7th byte | 8th byte | 9th byte | 10th byte |

| Bcc      | BHI d:8             |      | 4        | ~    | disp     | đ   |          |          |                    |          |          |          |          |           |

|          | BHI d:16            | Ι    | 5        | 80   | 2        | 0   | disp     | d        |                    |          |          |          |          |           |

|          | BLS d:8             | Ι    | 4        | e    | disp     | d   |          |          |                    |          |          |          |          |           |

|          | BLS d:16            | Ι    | 5        | 8    | ю        | 0   | disp     | d        |                    |          |          |          |          |           |

|          | BCC d:8 (BHS d:8)   |      | 4        | 4    | disp     | d   |          |          |                    |          |          |          |          |           |

|          | BCC d:16 (BHS d:16) | Ι    | 5        | 8    | 4        | 0   | disp     | d        |                    |          |          |          |          |           |

|          | BCS d:8 (BLO d:8)   |      | 4        | 5    | disp     | d   |          |          |                    |          |          |          |          |           |

|          | BCS d:16 (BLO d:16) |      | 5        | 8    | 5        | 0   | disp     | d        |                    |          |          |          |          |           |

|          | BNE d:8             | Ι    | 4        | 9    | disp     | d   |          |          |                    |          |          |          |          |           |

|          | BNE d:16            | Ι    | 5        | 80   | 9        | 0   | disp     | d        |                    |          |          |          |          |           |

|          | BEQ d:8             | Ι    | 4        | 7    | disp     | d   |          |          |                    |          |          |          |          |           |

|          | BEQ d:16            | Ι    | 5        | 80   | 7        | 0   | disp     | d        |                    |          |          |          |          |           |

|          | BVC d:8             | I    | 4        | œ    | disp     | d   |          |          |                    |          |          |          |          |           |

|          | BVC d:16            | Ι    | 5        | 8    | 8        | 0   | disp     | d        |                    |          |          |          |          |           |

|          | BVS d:8             | I    | 4        | 6    | disp     | d   |          |          |                    |          |          |          |          |           |

|          | BVS d:16            | Ι    | 2        | 8    | 6        | 0   | disp     | d        |                    |          |          |          |          |           |

|          | BPL d:8             | Ι    | 4        | A    | disp     | d   |          |          |                    |          |          |          |          |           |

|          | BPL d:16            |      | 5        | 8    | A        | 0   | disp     | d        |                    |          |          |          |          |           |

|          | BMI d:8             | Ι    | 4        | в    | disp     | d   |          |          |                    |          |          |          |          |           |

|          | BMI d:16            |      | 5        | 8    | В        | 0   | disp     | þ        |                    |          |          |          |          |           |

|          | BGE d:8             | Ι    | 4        | υ    | disp     | d   |          |          |                    |          |          |          |          |           |

|          | BGE d:16            |      | 5        | 8    | υ        | 0   | disp     | þ        |                    |          |          |          |          |           |

|          | BLT d:8             | Ι    | 4        | D    | disp     | d   |          |          |                    |          |          |          |          |           |

|          | BLT d:16            | Ι    | 5        | 8    | ۵        | 0   | disp     | d        |                    |          |          |          |          |           |

|          | BGT d:8             |      | 4        | ш    | disp     | d   |          |          |                    |          |          |          |          |           |

|          | BGT d:16            | Ι    | 2        | 8    | ш        | 0   | disp     | d        |                    |          |          |          |          |           |

|          | BLE d:8             | Ι    | 4        | ш    | disp     | ď   |          |          |                    |          |          |          |          |           |

|          | BLE d:16            |      | 5        | 80   | ш        | 0   | disp     | đ        |                    |          |          |          |          |           |

| Full address m  | ode (cont)                            | )    |      |     |       |              |                        |                               |                            |           |                                             |

|-----------------|---------------------------------------|------|------|-----|-------|--------------|------------------------|-------------------------------|----------------------------|-----------|---------------------------------------------|

| Bit :           | 7                                     | 6    | 5    |     | 4     |              | 3                      | 2                             | 1                          | 0         | -                                           |

| DMACRB :        | —                                     | DAID | DAID | E   | _     |              | DTF3                   | DTF2                          | DTF1                       | DTF0      |                                             |

| Initial value : | 0                                     | 0    | 0    |     | 0     |              | 0                      | 0                             | 0                          | 0         |                                             |

| Read/Write :    | R/W                                   | R/W  | R/W  |     | R/W   |              | R/W                    | R/W                           | R/W                        | R/W       |                                             |

| O               | eserved<br>nly 0 shou<br>ritten to th |      | Data | Onl | ten t | hou<br>o thi | ld be<br>s bit         |                               |                            |           |                                             |

|                 |                                       |      |      | DTF |       |              | в                      | lock Transf                   | er Mode                    |           | Normal Mode                                 |

|                 |                                       |      | 3    | 2   | 1     | 0            |                        | NUUR HAIISI                   |                            |           |                                             |

|                 |                                       |      |      | 0   |       | 0            |                        |                               |                            |           |                                             |

|                 |                                       |      |      |     |       | 1            | Activated<br>end inter | d by A/D con<br>rrupt         | verter conv                | rersion   | -                                           |

|                 |                                       |      |      |     | 1     | 0            | Activated              | d by DREQ p                   | oin falling e              | dge input | Activated by DREQ<br>pin falling edge input |

|                 |                                       |      |      |     |       | 1            | Activated              | d by DREQ p                   | oin low-leve               | l input   | Activated by DREQ pin low-level input       |

|                 |                                       |      |      | 1   | 0     | 0            |                        | d by SCI cha<br>pty interrupt |                            | smission  | _                                           |

|                 |                                       |      |      |     |       | 1            | Activated data-full    | d by SCI cha<br>interrupt     | annel 0 rece               | ption     | _                                           |

|                 |                                       |      |      |     | 1     | 0            |                        | d by SCI cha<br>pty interrupt |                            | smission  | Auto-request (cycle steal)                  |

|                 |                                       |      |      |     |       | 1            |                        | d by SCI cha<br>interrupt     | annel 1 rece               | ption     | Auto-request (burst)                        |

|                 |                                       |      | 1    | 0   | 0     | 0            | Activated match/in     | d by TPU cha<br>put capture   | annel 0 con<br>A interrupt | npare     | _                                           |

|                 |                                       |      |      |     |       | 1            |                        | d by TPU cha<br>put capture   |                            | npare     | _                                           |

|                 |                                       |      |      |     | 1     | 0            | Activated match/in     | d by TPU cha<br>put capture   | annel 2 con<br>A interrupt | npare     | _                                           |

|                 |                                       |      |      |     |       | 1            |                        | d by TPU cha<br>put capture   |                            | npare     | _                                           |

|                 |                                       |      |      | 1   | 0     | 0            | Activated match/in     | d by TPU cha<br>put capture   | annel 4 con<br>A interrupt | npare     | _                                           |

|                 |                                       |      |      |     |       | 1            | Activated match/in     | d by TPU cha<br>put capture   | annel 5 con<br>A interrupt | npare     | _                                           |

|                 |                                       |      |      |     | 1     | 0            | -                      |                               |                            |           | _                                           |

|                 |                                       |      |      |     |       | 1            | _                      |                               |                            |           | _                                           |

Destination Address Increment/Decrement

| 0 | 0 | MARB is fixed                             |

|---|---|-------------------------------------------|

|   | 1 | MARB is incremented after a data transfer |

| 1 | 0 | MARB is fixed                             |

|   | 1 | MARB is decremented after a data transfer |

### DACR01—D/A Control Register 01

| H'FFA6 |

|--------|

|--------|

**D/A Converter**

| Bit :           | 7     | 6       | 5         | 4                                    | 3        | 2      | 1 | 0 |

|-----------------|-------|---------|-----------|--------------------------------------|----------|--------|---|---|

|                 | DAOE1 | DAOE0   | DAE       | —                                    | —        | _      | — | _ |

| Initial value : | 0     | 0       | 0         | 1                                    | 1        | 1      | 1 | 1 |

| Read/Write :    | R/W   | R/W     | R/W       | _                                    | _        | _      | _ | _ |

|                 |       | D/A Out | put Enab  | le 0                                 |          |        |   |   |

|                 |       | 0 A     | nalog out | tput DA <sub>0</sub> is              | disabled |        |   |   |

|                 |       |         |           | D/A conve<br>tput DA <sub>0</sub> is |          | nabled |   |   |

|                 |       |         |           |                                      |          |        |   |   |

#### D/A Output Enable 1

| 0 | Analog output DA <sub>1</sub> is disabled |

|---|-------------------------------------------|

| 1 | Channel 1 D/A conversion is enabled       |

|   | Analog output DA <sub>1</sub> is enabled  |

#### D/A Conversion Control

| DAOE1 | DAOE0 | DAE | Description                             |

|-------|-------|-----|-----------------------------------------|

| 0     | 0     | *   | Channel 0 and 1 D/A conversion disabled |

|       | 1     | 0   | Channel 0 D/A conversion enabled        |

|       |       |     | Channel 1 D/A conversion disabled       |

|       |       | 1   | Channel 0 and 1 D/A conversion enabled  |

| 1     | 0     | 0   | Channel 0 D/A conversion disabled       |

|       |       |     | Channel 1 D/A conversion enabled        |

|       |       | 1   | Channel 0 and 1 D/A conversion enabled  |

|       | 1     | *   | Channel 0 and 1 D/A conversion enabled  |

\* : Don't care

| Port Name<br>Pin Name                                                | MCU<br>Operating<br>Mode | Reset | Hardware<br>Standby<br>Mode | Software<br>Standby Mode                        | Bus-Released<br>State    | Program<br>Execution State<br>Sleep Mode         |

|----------------------------------------------------------------------|--------------------------|-------|-----------------------------|-------------------------------------------------|--------------------------|--------------------------------------------------|

| PA <sub>4</sub> /A <sub>20</sub>                                     | 4, 5                     | L     | Т                           | [A20E • DDR = 1]<br>kept                        | [A20E ⋅ DDR = 1]<br>kept | $\overline{ A20E} \cdot DDR = 1]$<br>Output port |

|                                                                      |                          |       |                             | [A20E • OPE = 1]<br>T                           | [A20E+A20E •<br>DDR = 1] | [A20E+A20E •<br>DDR = 1]                         |

|                                                                      |                          |       |                             | [A20E • OPE = 1]<br>kept                        | Т                        | Address output                                   |

|                                                                      | 6                        | Т     | Т                           | $[A20E = 0],$ $[A20E \cdot \overline{DDR} = 1]$ | [A20E = 0]<br>kept       | [A20E = 0]<br>I/O port                           |

|                                                                      |                          |       |                             | kept<br>[A20E • DDR •                           | [A20E • DDR = 1]<br>kept | $[A20E \cdot \overline{DDR} = 1]$ Output port    |

|                                                                      |                          |       |                             | OPE = 1]<br>T                                   | [A20E • DDR = 1]<br>T    | [A20E · DDR = 1]<br>Address output               |

|                                                                      |                          |       |                             | [A20E • DDR •<br>OPE = 1]<br>kept               |                          |                                                  |

|                                                                      | 7                        | Т     | Т                           | kept                                            | kept                     | I/O port                                         |

| PA <sub>3</sub> /A <sub>19</sub><br>PA <sub>2</sub> /A <sub>18</sub> | 4, 5                     | L     | Т                           | [OPE = 0]<br>T                                  | Т                        | Address output                                   |

| PA <sub>1</sub> /A <sub>17</sub><br>PA <sub>0</sub> /A <sub>16</sub> |                          |       |                             | [OPE = 1]<br>kept                               |                          |                                                  |

|                                                                      | 6                        | Т     | Т                           | $[DDR \cdot OPE = 0]$ T                         | Т                        | [DDR = 0]<br>Input port                          |

|                                                                      |                          |       |                             | [DDR • OPE = 1]<br>kept                         |                          | [DDR = 1]<br>Address output                      |

|                                                                      | 7                        | Т     | Т                           | kept                                            | kept                     | I/O port                                         |

| Port B                                                               | 4, 5                     | L     | Т                           | [OPE = 0]<br>T                                  | Т                        | Address output                                   |

|                                                                      |                          |       |                             | [OPE = 1]<br>kept                               |                          |                                                  |

|                                                                      | 6                        | Т     | Т                           | $[DDR \cdot OPE = 0]$ T                         | Т                        | [DDR = 0]<br>Input port                          |

|                                                                      |                          |       |                             | [DDR • OPE = 1]<br>kept                         |                          | [DDR = 1]<br>Address output                      |

|                                                                      | 7                        | Т     | Т                           | kept                                            | kept                     | I/O port                                         |