Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product StatusActiveCore ProcessorH85/2000Core Size6-BitSpeed25MHzConnectivitySCI, SmarCardPripheralsDMA POR, PWM, WDTNumber of I/O86Program Memory Size12KB (S12K x 8)Program Memory TypeI-ASHERPROM Size-Nufsze Supply (Vcc/Vdd)37V ~ 3.6VOrder Jonger SignerJ02 N - 3.6VSocial Strategy-Program Signer-Program Signer-Signer Signer- |                            |                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------------|

| Core Size16-BitSpeed25MHzConnectivitySCI, SmartCardPeripheralsDMA, POR, PWM, WDTNumber of I/O86Program Memory Size12KB (512K x 8)Program Memory TypeFLASHEEPROM Size-XMASize8K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersAID 8x10b; D/A 2x8bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting Type120-TQFP (14x14)                                                                                                                                                                                                                                                                                                                                                                                                                                       | Product Status             | Active                                                                        |

| Speed25MHzConnectivitySCI, SmartCardPeripheralsDMA, POR, PWM, WDTNumber of I/O86Program Memory Size512KB (512K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size8K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 8x10b; D/A 2x8bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case120-TQFP (14x14)                                                                                                                                                                                                                                                                                                                                                                                                                         | Core Processor             | H8S/2000                                                                      |

| ConnectivitySCI, SmartCardPeripheralsDMA, POR, PWM, WDTNumber of I/O86Program Memory Size512KB (512K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size8K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 8x10b; D/A 2x8bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case120-TQFP (14x14)                                                                                                                                                                                                                                                                                                                                                                                                                                   | Core Size                  | 16-Bit                                                                        |

| PeripheralsDMA, POR, PWM, WDTNumber of I/O86Program Memory Size512KB (512K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size8K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 8x10b; D/A 2x8bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case120-TQFP (14x14)                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Speed                      | 25MHz                                                                         |

| Number of I/O86Program Memory Size512KB (512K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size8K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 8x10b; D/A 2x8bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case120-TQFP (14x14)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Connectivity               | SCI, SmartCard                                                                |

| Program Memory Size512KB (512K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size8K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 8x10b; D/A 2x8bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting Type120-TQFPSuppler Device Package120-TQFP (14x14)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Peripherals                | DMA, POR, PWM, WDT                                                            |

| Program Memory TypeFLASHEEPROM Size-RAM Size8K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 8x10b; D/A 2x8bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case120-TQFP (14x14)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Number of I/O              | 86                                                                            |

| EEPROM Size-RAM Size8K × 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 8x10b; D/A 2x8bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case120-TQFPSupplier Device Package120-TQFP (14x14)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Program Memory Size        | 512KB (512K x 8)                                                              |

| RAM Size8K × 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 8x10b; D/A 2x8bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case120-TQFPSupplier Device Package120-TQFP (14x14)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Program Memory Type        | FLASH                                                                         |

| Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 8x10b; D/A 2x8bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case120-TQFPSupplier Device Package120-TQFP (14x14)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | EEPROM Size                | -                                                                             |

| Data ConvertersA/D 8x10b; D/A 2x8bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case120-TQFPSupplier Device Package120-TQFP (14x14)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RAM Size                   | 8K x 8                                                                        |

| Oscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case120-TQFPSupplier Device Package120-TQFP (14x14)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                   |

| Operating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case120-TQFPSupplier Device Package120-TQFP (14x14)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Data Converters            | A/D 8x10b; D/A 2x8b                                                           |

| Mounting TypeSurface MountPackage / Case120-TQFPSupplier Device Package120-TQFP (14x14)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Oscillator Type            | Internal                                                                      |

| Package / Case     120-TQFP       Supplier Device Package     120-TQFP (14x14)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Operating Temperature      | -20°C ~ 75°C (TA)                                                             |

| Supplier Device Package 120-TQFP (14x14)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Mounting Type              | Surface Mount                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Package / Case             | 120-TQFP                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Supplier Device Package    | 120-TQFP (14x14)                                                              |

| Purchase URL https://www.e-xfl.com/product-detail/renesas-electronics-america/df2326vte25v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2326vte25v |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 19.14.5 System Control Register 2 (SYSCR2)                     |  |

|----------------------------------------------------------------|--|

| 19.14.6 RAM Emulation Register (RAMER)                         |  |

| 19.15 On-Board Programming Modes                               |  |

| 19.15.1 Boot Mode                                              |  |

| 19.15.2 User Program Mode                                      |  |

| 19.16 Programming/Erasing Flash Memory                         |  |

| 19.16.1 Program Mode                                           |  |

| 19.16.2 Program-Verify Mode                                    |  |

| 19.16.3 Erase Mode                                             |  |

| 19.16.4 Erase-Verify Mode                                      |  |

| 19.17 Flash Memory Protection                                  |  |

| 19.17.1 Hardware Protection                                    |  |

| 19.17.2 Software Protection                                    |  |

| 19.17.3 Error Protection                                       |  |

| 19.18 Flash Memory Emulation in RAM                            |  |

| 19.18.1 Emulation in RAM                                       |  |

| 19.18.2 RAM Overlap                                            |  |

| 19.19 Interrupt Handling when Programming/Erasing Flash Memory |  |

| 19.20 Flash Memory PROM Mode                                   |  |

| 19.20.1 PROM Mode Setting                                      |  |

| 19.20.2 Socket Adapters and Memory Map                         |  |

| 19.20.3 PROM Mode Operation                                    |  |

| 19.20.4 Memory Read Mode                                       |  |

| 19.20.5 Auto-Program Mode                                      |  |

| 19.20.6 Auto-Erase Mode                                        |  |

| 19.20.7 Status Read Mode                                       |  |

| 19.20.8 Status Polling                                         |  |

| 19.20.9 PROM Mode Transition Time                              |  |

| 19.20.10 Notes on Memory Programming                           |  |

| 19.21 Flash Memory Programming and Erasing Precautions         |  |

| 19.22 Overview of Flash Memory (H8S/2326 F-ZTAT)               |  |

| 19.22.1 Features                                               |  |

| 19.22.2 Overview                                               |  |

| 19.22.3 Flash Memory Operating Modes                           |  |

| 19.22.4 On-Board Programming Modes                             |  |

| 19.22.5 Flash Memory Emulation in RAM                          |  |

| 19.22.6 Differences between Boot Mode and User Program Mode    |  |

| 19.22.7 Block Configuration                                    |  |

| 19.22.8 Pin Configuration                                      |  |

| 19.22.9 Register Configuration                                 |  |

#### 1.3.3 Pin Functions

#### Table 1.3Pin Functions

|       |                 | Pi                                      | n No.                                                                            |        |                                                                                                                                                                                                                            |

|-------|-----------------|-----------------------------------------|----------------------------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Туре  | Symbol          | TFP-120                                 | FP-128B                                                                          | I/O    | Name and Function                                                                                                                                                                                                          |

| Power | V <sub>cc</sub> | 1, 33,<br>52, 76,<br>81                 | 5, 39,<br>58, 84,<br>89                                                          | Input  | <b>Power supply:</b> For connection to the power supply. All V <sub>CC</sub> pins should be connected to the system power supply.                                                                                          |

|       | V <sub>SS</sub> | 6, 15,<br>24, 38,<br>47, 59,<br>79, 104 | 3, 10,<br>19, 28,<br>35, 36,<br>44, 53,<br>65, 67,<br>68, 87,<br>99, 100,<br>114 | Input  | <b>Ground:</b> For connection to ground $(0 \text{ V})$ . All V <sub>SS</sub> pins should be connected to the system power supply $(0 \text{ V})$ .                                                                        |

| Clock | XTAL            | 77                                      | 85                                                                               | Input  | Connects to a crystal resonator.<br>See section 20, Clock Pulse<br>Generator for typical connection<br>diagrams for a crystal resonator and<br>external clock input.                                                       |

|       | EXTAL           | 78                                      | 86                                                                               | Input  | Connects to a crystal resonator.<br>The EXTAL pin can also input an<br>external clock.<br>See section 20, Clock Pulse<br>Generator for typical connection<br>diagrams for a crystal resonator and<br>external clock input. |

|       | φ               | 80                                      | 88                                                                               | Output | <b>System clock:</b> Supplies the system clock to an external device.                                                                                                                                                      |

### 2.6 Instruction Set

#### 2.6.1 Overview

The H8S/2000 CPU has 65 types of instructions. The instructions are classified by function in table 2.1.

| Table 2.1 | Instruction | Classification |

|-----------|-------------|----------------|

|-----------|-------------|----------------|

| Function            | Instructions                                                                      | Size | Types |

|---------------------|-----------------------------------------------------------------------------------|------|-------|

| Data transfer       | MOV                                                                               | BWL  | 5     |

|                     | POP <sup>*1</sup> , PUSH <sup>*1</sup>                                            | WL   |       |

|                     | LDM, STM                                                                          | L    | _     |

|                     | MOVFPE, MOVTPE <sup>*3</sup>                                                      | В    | _     |

| Arithmetic          | ADD, SUB, CMP, NEG                                                                | BWL  | 19    |

| operations          | ADDX, SUBX, DAA, DAS                                                              | В    |       |

|                     | INC, DEC                                                                          | BWL  | _     |

|                     | ADDS, SUBS                                                                        | L    | _     |

|                     | MULXU, DIVXU, MULXS, DIVXS                                                        | BW   | _     |

|                     | EXTU, EXTS                                                                        | WL   | _     |

|                     | TAS <sup>*4</sup>                                                                 | В    | -     |

| Logic operations    | AND, OR, XOR, NOT                                                                 | BWL  | 4     |

| Shift               | SHAL, SHAR, SHLL, SHLR, ROTL, ROTR, ROTXL, ROTXR                                  | BWL  | 8     |

| Bit manipulation    | BSET, BCLR, BNOT, BTST, BLD, BILD, BST, BIST, BAND, BIAND, BOR, BIOR, BXOR, BIXOR | В    | 14    |

| Branch              | Bcc <sup>*2</sup> , JMP, BSR, JSR, RTS                                            | _    | 5     |

| System control      | TRAPA, RTE, SLEEP, LDC, STC, ANDC, ORC, XORC, NOP                                 | —    | 9     |

| Block data transfer | EEPMOV                                                                            | —    | 1     |

Total: 65

Legend:

B: Byte

W: Word

L: Longword

- Notes: 1. POP.W Rn and PUSH.W Rn are identical to MOV.W @SP+, Rn and MOV.W Rn, @-SP. POP.L ERn and PUSH.L ERn are identical to MOV.L @SP+, ERn and MOV.L ERn, @-SP.

- 2. Bcc is the general name for conditional branch instructions.

- 3. Cannot be used in the H8S/2329 Group and H8S/2328 Group.

- 4. Only register ER0, ER1, ER4, or ER5 should be used when using the TAS instruction.

|                       |          |               | Vector Address <sup>*1</sup> |  |

|-----------------------|----------|---------------|------------------------------|--|

| Exception Source      |          | Vector Number | Advanced Mode                |  |

| Reset                 |          | 0             | H'0000 to H'0003             |  |

| Reserved              |          | 1             | H'0004 to H'0007             |  |

| Reserved for syster   | n use    | 2             | H'0008 to H'000B             |  |

|                       |          | 3             | H'000C to H'000F             |  |

|                       |          | 4             | H'0010 to H'0013             |  |

| Trace                 |          | 5             | H'0014 to H'0017             |  |

| Reserved for syster   | n use    | 6             | H'0018 to H'001B             |  |

| External interrupt    | NMI      | 7             | H'001C to H'001F             |  |

| Trap instruction (4 s | sources) | 8             | H'0020 to H'0023             |  |

|                       |          | 9             | H'0024 to H'0027             |  |

|                       |          | 10            | H'0028 to H'002B             |  |

|                       |          | 11            | H'002C to H'002F             |  |

| Reserved for syster   | n use    | 12            | H'0030 to H'0033             |  |

|                       |          | 13            | H'0034 to H'0037             |  |

|                       |          | 14            | H'0038 to H'003B             |  |

|                       |          | 15            | H'003C to H'003F             |  |

| External interrupt    | IRQ0     | 16            | H'0040 to H'0043             |  |

|                       | IRQ1     | 17            | H'0044 to H'0047             |  |

|                       | IRQ2     | 18            | H'0048 to H'004B             |  |

|                       | IRQ3     | 19            | H'004C to H'004F             |  |

|                       | IRQ4     | 20            | H'0050 to H'0053             |  |

|                       | IRQ5     | 21            | H'0054 to H'0057             |  |

|                       | IRQ6     | 22            | H'0058 to H'005B             |  |

|                       | IRQ7     | 23            | H'005C to H'005F             |  |

| Internal interrupt*2  |          | 24<br>        | H'0060 to H'0063             |  |

|                       |          | 91            | H'016C to H'016F             |  |

#### **Exception Vector Table** Table 4.2

Notes: 1. Lower 16 bits of the address.

2. For details of internal interrupt vectors, see section 5.3.3, Interrupt Exception Vector Table.

| 5.2.4 | IRQ Sense Control Registers H and L (ISCRH, ISCRL) |

|-------|----------------------------------------------------|

|-------|----------------------------------------------------|

ISCRH

| Bit        | :     | 15      | 14      | 13      | 12      | 11      | 10      | 9       | 8       |

|------------|-------|---------|---------|---------|---------|---------|---------|---------|---------|

|            |       | IRQ7SCB | IRQ7SCA | IRQ6SCB | IRQ6SCA | IRQ5SCB | IRQ5SCA | IRQ4SCB | IRQ4SCA |

| Initial va | lue : | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| R/W        | :     | R/W     |

|            |       |         |         |         |         |         |         |         |         |

| ISCRL      |       |         |         |         |         |         |         |         |         |

| Bit        | :     | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|            |       | IRQ3SCB | IRQ3SCA | IRQ2SCB | IRQ2SCA | IRQ1SCB | IRQ1SCA | IRQ0SCB | IRQ0SCA |

| Initial va | lue : | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| R/W        | :     | R/W     |

ISCR (composed of ISCRH and ISCRL) is a 16-bit readable/writable register that selects rising edge, falling edge, or both edge detection, or level sensing, for the input at pins  $\overline{IRQ7}$  to  $\overline{IRQ0}$ .

ISCR is initialized to H'0000 by a reset and in hardware standby mode.

# Bits 15 to 0—IRQ7 Sense Control A and B (IRQ7SCA, IRQ7SCB) to IRQ0 Sense Control A and B (IRQ0SCA, IRQ0SCB)

| Bits 15 to 0<br>IRQ7SCB to<br>IRQ0SCB IRQ0SCA to |   | <br>Description                                                                                                            |  |

|--------------------------------------------------|---|----------------------------------------------------------------------------------------------------------------------------|--|

|                                                  |   |                                                                                                                            |  |

|                                                  | 1 | Interrupt request generated at falling edge of $\overline{IRQ7}$ to $\overline{IRQ0}$ input                                |  |

| 1                                                | 0 | Interrupt request generated at rising edge of IRQ7 to IRQ0 input                                                           |  |

|                                                  | 1 | Interrupt request generated at both falling and rising edges of $\overline{\text{IRQ7}}$ to $\overline{\text{IRQ0}}$ input |  |

Bit 6—Data Transfer Enable 1A (DTE1A): Enables or disables data transfer on channel 1A.

| Bit 6 |                        |                 |

|-------|------------------------|-----------------|

| DTE1A | Description            |                 |

| 0     | Data transfer disabled | (Initial value) |

| 1     | Data transfer enabled  |                 |

Bit 5—Data Transfer Enable 0B (DTE0B): Enables or disables data transfer on channel 0B.

| Bit 5<br>DTE0B | Description            |                 |

|----------------|------------------------|-----------------|

| 0              | Data transfer disabled | (Initial value) |

| 1              | Data transfer enabled  |                 |

Bit 4—Data Transfer Enable 0A (DTE0A): Enables or disables data transfer on channel 0A.

| Bit 4<br>DTE0A | Description            |                 |

|----------------|------------------------|-----------------|

| 0              | Data transfer disabled | (Initial value) |

| 1              | Data transfer enabled  |                 |

**Bits 3 to 0—Data Transfer End Interrupt Enable (DTIE):** These bits enable or disable an interrupt to the CPU or DTC when transfer ends. If the DTIE bit is set to 1 when DTE = 0, the DMAC regards this as indicating the end of a transfer, and issues a transfer end interrupt request to the CPU or DTC.

A transfer end interrupt can be canceled either by clearing the DTIE bit to 0 in the interrupt handling routine, or by performing processing to continue transfer by setting the transfer counter and address register again, and then setting the DTE bit to 1.

**Bit 3—Data Transfer Interrupt Enable 1B (DTIE1B):** Enables or disables the channel 1B transfer end interrupt.

| Bit 3<br>DTIE1B | Description                     |                 |

|-----------------|---------------------------------|-----------------|

| 0               | Transfer end interrupt disabled | (Initial value) |

| 1               | Transfer end interrupt enabled  |                 |

#### System Control Register (SYSCR)

| Bit             | it : 7  |   | 6 | 5     | 4     | 3     | 2     | 1      | 0    |

|-----------------|---------|---|---|-------|-------|-------|-------|--------|------|

|                 |         |   | — | INTM1 | INTM0 | NMIEG | LWROD | IRQPAS | RAME |

| Initial value : |         | 0 | 0 | 0     | 0     | 0     | 0     | 0      | 1    |

| R/W             | : R/W — |   | — | R/W   | R/W   | R/W   | R/W   | R/W    | R/W  |

SYSCR is an 8-bit readable/writable register that selects the interrupt control mode, controls the  $\overline{LWR}$  pin, switches the  $\overline{IRQ_4}$  to  $\overline{IRQ_7}$  input pins, and selects the detected edge for NMI. SYSCR is initialized to H'01 by a reset, and in hardware standby mode. It is not initialized in software standby mode.

**Bits 5 and 4—Interrupt Control Mode 1 and 0 (INTM1, INTM0):** These bits select either of two interrupt control modes for the interrupt controller. For details, see section 5, Interrupt Controller.

**Bit 3—NMI Edge Select (NMIEG):** Selects the input edge for the NMI pin. For details, see section 5, Interrupt Controller.

**Bit 2—LWR Output Disable (LWROD):** Enables or disables  $\overline{LWR}$  output. For details, see section 9.13, Port F.

**Bit 1—IRQ Port Switching Select (IRQPAS):** Selects switching of input pins for  $\overline{IRQ}_4$  to  $\overline{IRQ}_7$ . IRQ<sub>4</sub> to  $\overline{IRQ}_7$  input is always performed from one of the ports.

| Bit 1<br>IRQPAS | Description                                                              |                 |

|-----------------|--------------------------------------------------------------------------|-----------------|

| 0               | $PA_4$ to $PA_7$ used for $\overline{IRQ_4}$ to $\overline{IRQ_7}$ input | (Initial value) |

| 1               | $P5_0$ to $P5_3$ used for $\overline{IRQ}_4$ to $\overline{IRQ}_7$ input |                 |

**Bit 0—RAM Enable (RAME):** Enables or disables on-chip RAM. For details, see section 18, RAM.

#### 9.11.2 Register Configuration

Table 9.20 shows the port D register configuration.

#### Table 9.20 Port D Registers

| Name                                | Abbreviation | R/W | Initial Value | Address* |

|-------------------------------------|--------------|-----|---------------|----------|

| Port D data direction register      | PDDDR        | W   | H'00          | H'FEBC   |

| Port D data register                | PDDR         | R/W | H'00          | H'FF6C   |

| Port D register                     | PORTD        | R   | Undefined     | H'FF5C   |

| Port D MOS pull-up control register | PDPCR        | R/W | H'00          | H'FF73   |

|                                     |              |     |               |          |

Note: \* Lower 16 bits of the address.

#### Port D Data Direction Register (PDDDR)

| Bit             | it : 7 |   | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-----------------|--------|---|--------|--------|--------|--------|--------|--------|--------|

|                 | PD7    |   | PD6DDR | PD5DDR | PD4DDR | PD3DDR | PD2DDR | PD1DDR | PD0DDR |

| Initial value : |        | 0 | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W             | :      | W | W      | W      | W      | W      | W      | W      | W      |

PDDDR is an 8-bit write-only register, the individual bits of which specify input or output for the pins of port D. PDDDR cannot be read; if it is, an undefined value will be read.

PDDDR is initialized to H'00 by a reset, and in hardware standby mode. It retains its prior state in software standby mode.

• Modes 4 to 6

The input/output direction specification by PDDDR is ignored, and port D is automatically designated for data I/O.

• Mode 7

Setting a PDDDR bit to 1 makes the corresponding port D pin an output port, while clearing the bit to 0 makes the pin an input port.

**Bit 3—Input Capture/Output Compare Flag D (TGFD):** Status flag that indicates the occurrence of TGRD input capture or compare match in channels 0 and 3.

In channels 1, 2, 4, and 5, bit 3 is reserved. It is always read as 0 and cannot be modified.

| Bit 3<br>TGFD | Description                                                                                                                                |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 0             | [Clearing conditions] (Initial value)                                                                                                      |

|               | <ul> <li>When DTC is activated by TGID interrupt while DISEL bit of MRB in DTC is 0</li> </ul>                                             |

|               | <ul> <li>When 0 is written to TGFD after reading TGFD = 1</li> </ul>                                                                       |

| 1             | [Setting conditions]                                                                                                                       |

|               | <ul> <li>When TCNT = TGRD while TGRD is functioning as output compare register</li> </ul>                                                  |

|               | <ul> <li>When TCNT value is transferred to TGRD by input capture signal while TGRD is<br/>functioning as input capture register</li> </ul> |

**Bit 2—Input Capture/Output Compare Flag C (TGFC):** Status flag that indicates the occurrence of TGRC input capture or compare match in channels 0 and 3.

In channels 1, 2, 4, and 5, bit 2 is reserved. It is always read as 0 and cannot be modified.

| Bit 2 |                                                                                           |

|-------|-------------------------------------------------------------------------------------------|

| TGFC  | Description                                                                               |

| 0     | [Clearing conditions] (Initial value)                                                     |

|       | When DTC is activated by TGIC interrupt while DISEL bit of MRB in DTC is 0                |

|       | <ul> <li>When 0 is written to TGFC after reading TGFC = 1</li> </ul>                      |

| 1     | [Setting conditions]                                                                      |

|       | <ul> <li>When TCNT = TGRC while TGRC is functioning as output compare register</li> </ul> |

|       | When TCNT value is transferred to TGRC by input capture signal while TGRC is              |

|       | functioning as input capture register                                                     |

**Examples of Cascaded Operation:** Figure 10.22 illustrates the operation when counting upon TCNT2 overflow/underflow has been set for TCNT1, TGR1A, and TGR2A have been designated as input capture registers, and TIOC pin rising edge has been selected.

When a rising edge is input to the TIOCA1 and TIOCA2 pins simultaneously, the upper 16 bits of the 32-bit data are transferred to TGR1A, and the lower 16 bits to TGR2A.

| TCNT1<br>clock    |        |   |        |        |        |

|-------------------|--------|---|--------|--------|--------|

| TCNT1             | H'03A1 | χ |        | H'03A2 |        |

| TCNT2<br>clock    |        |   |        |        |        |

| TCNT2             | H'FFFF | χ | H'0000 | χ      | H'0001 |

| TIOCA1,<br>TIOCA2 |        |   |        |        |        |

| TGR1A             |        |   | X      | H'03A2 |        |

| TGR2A             |        |   | χ      | H'0000 |        |

Figure 10.22 Example of Cascaded Operation (1)

Figure 10.23 illustrates the operation when counting upon TCNT2 overflow/underflow has been set for TCNT1, and phase counting mode has been designated for channel 2.

TCNT1 is incremented by TCNT2 overflow and decremented by TCNT2 underflow.

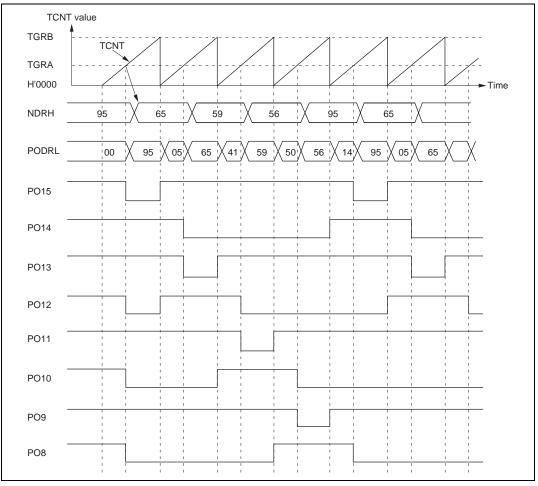

#### 11.3.5 Inverted Pulse Output

If the G3INV, G2INV, G1INV, and G0INV bits in PMR are cleared to 0, values that are the inverse of the PODR contents can be output.

Figure 11.8 shows the outputs when G3INV and G2INV are cleared to 0, in addition to the settings of figure 11.7.

Figure 11.8 Inverted Pulse Output (Example)

#### 13.2.3 Reset Control/Status Register (RSTCSR)

| Bit             | : | 7      | 6    | 5   | 4 | 3 | 2 | 1 | 0 |

|-----------------|---|--------|------|-----|---|---|---|---|---|

|                 |   | WOVF   | RSTE | _   | — | _ | _ | — | — |

| Initial value : |   | 0      | 0    | 0   | 1 | 1 | 1 | 1 | 1 |

| R/W             | : | R/(W)* | R/W  | R/W | _ | _ | _ | _ | _ |

Note: \* Only 0 can be written, to clear the flag.

RSTCSR is an 8-bit readable/writable<sup>\*</sup> register that controls the generation of the internal reset signal when TCNT overflows, and selects the type of internal reset signal.

RSTCSR is initialized to H'1F by a reset signal from the  $\overline{\text{RES}}$  pin, but not by the WDT internal reset signal caused by overflows.

Note: \* RSTCSR is write-protected by a password to prevent accidental overwriting. For details see section 13.2.4, Notes on Register Access.

**Bit 7—Watchdog Timer Overflow Flag (WOVF):** Indicates that TCNT has overflowed (changed from H'FF to H'00) during watchdog timer operation. This bit is not set in interval timer mode.

| Bit 7<br>WOVF | Description                                                                   |                 |

|---------------|-------------------------------------------------------------------------------|-----------------|

| 0             | [Clearing condition]                                                          | (Initial value) |

|               | Cleared by reading RSTCSR when $WOVF = 1$ , then writing 0 to $WOVF$          |                 |

| 1             | [Setting condition]                                                           |                 |

|               | Set when TCNT overflows (changes from H'FF to H'00) during watchdog operation | ı timer         |

**Bit 6—Reset Enable (RSTE):** Specifies whether or not a reset signal is generated in the chip if TCNT overflows during watchdog timer operation.

| Bit 6<br>RSTE | Description                                                     |                         |

|---------------|-----------------------------------------------------------------|-------------------------|

| 0             | Reset signal is not generated if TCNT overflows $^{st}$         | (Initial value)         |

| 1             | Reset signal is generated if TCNT overflows                     |                         |

| Noto: * T     | he medules within the ship are not report, but TCNT and TCCD wi | ithin the WDT are readt |

Note: \* The modules within the chip are not reset, but TCNT and TCSR within the WDT are reset.

#### **16.2** Register Descriptions

#### 16.2.1 A/D Data Registers A to D (ADDRA to ADDRD)

| Bit           | : | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|---------------|---|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---|---|---|---|---|---|

|               |   | AD9 | AD8 | AD7 | AD6 | AD5 | AD4 | AD3 | AD2 | AD1 | AD0 | — | — | _ | _ | — | — |

| Initial value | : | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W           | : | R   | R   | R   | R   | R   | R   | R   | R   | R   | R   | R | R | R | R | R | R |

There are four 16-bit read-only ADDR registers, ADDRA to ADDRD, used to store the results of A/D conversion.

The 10-bit data resulting from A/D conversion is transferred to the ADDR register for the selected channel and stored there. The upper 8 bits of the converted data are transferred to the upper byte (bits 15 to 8) of ADDR, and the lower 2 bits are transferred to the lower byte (bits 7 and 6) and stored. Bits 5 to 0 are always read as 0.

The correspondence between the analog input channels and ADDR registers is shown in table 16.3.

The ADDR registers can always be read by the CPU. The upper byte can be read directly, but for the lower byte, data transfer is performed via a temporary register (TEMP). For details, see section 16.3, Interface to Bus Master.

The ADDR registers are initialized to H'0000 by a reset, and in standby mode or module stop mode.

| <b>Table 16.3</b> | Analog Input Channels and Co | rresponding ADDR Registers |

|-------------------|------------------------------|----------------------------|

|-------------------|------------------------------|----------------------------|

| Ana     | log Input Channel |                   |  |

|---------|-------------------|-------------------|--|

| Group 0 | Group 1           | A/D Data Register |  |

| AN0     | AN4               | ADDRA             |  |

| AN1     | AN5               | ADDRB             |  |

| AN2     | AN6               | ADDRC             |  |

| AN3     | AN7               | ADDRD             |  |

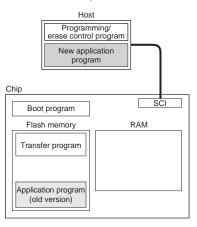

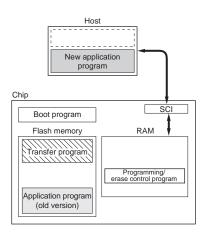

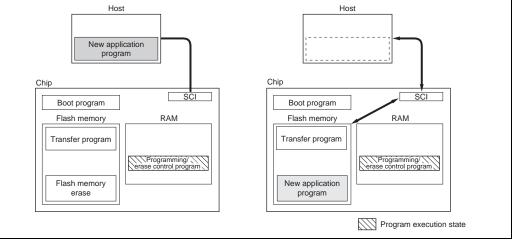

#### User program mode

1. Initial state

(1) The program that will transfer the programming/erase control program to on-chip RAM should be written into the flash memory by the user beforehand. (2) The programming/erase control program should be prepared in the host or in the flash memory.

Flash memory initialization The programming/erase program in RAM is executed, and the flash memory is initialized (to H'FF). Erasing can be performed in block units, but not in byte units.  Programming/erase control program transfer Executes the transfer program in the flash memory, and transfers the programming/erase control program to RAM.

Writing new application program Next, the new application program in the host is written into the erased flash memory blocks. Do not write to unerased blocks.

Figure 19.5 User Program Mode (Example)

**Bit 2—Program-Verify 1 (PV1):** Selects program-verify mode transition or clearing for addresses H'000000 to H'03FFFF. Do not set the SWE1, ESU1, PSU1, EV1, E1, or P1 bit at the same time.

| Bit 2<br>PV1 | Description                       |                 |

|--------------|-----------------------------------|-----------------|

| 0            | Program-verify mode cleared       | (Initial value) |

| 1            | Transition to program-verify mode |                 |

|              | [Setting condition]               |                 |

|              | When FWE = 1, SWE1 = 1            |                 |

**Bit 1—Erase 1 (E1):** Selects erase mode transition or clearing for addresses H'000000 to H'03FFFF. Do not set the SWE1, ESU1, PSU1, EV1, PV1, or P1 bit at the same time.

| Bit 1<br>E1 | Description                                  |                 |

|-------------|----------------------------------------------|-----------------|

| 0           | Erase mode cleared                           | (Initial value) |

| 1           | Transition to erase mode                     |                 |

|             | [Setting condition]                          |                 |

|             | When $FWE = 1$ , $SWE1 = 1$ , and $ESU1 = 1$ |                 |

**Bit 0—Program 1 (P1):** Selects program mode transition or clearing for addresses H'000000 to H'03FFFF. Do not set the SWE1, PSU1, ESU1, EV1, PV1, or E1 bit at the same time.

| Bit 0<br>P1 | Description                          |                 |

|-------------|--------------------------------------|-----------------|

| 0           | Program mode cleared                 | (Initial value) |

| 1           | Transition to program mode           |                 |

|             | [Setting condition]                  |                 |

|             | When FWE = 1, SWE1 = 1, and PSU1 = 1 |                 |

#### (2) Control Signal Timing

#### Table 22.6 Control Signal Timing

Condition A:  $V_{CC} = 2.7 \text{ V}$  to 3.6 V,  $AV_{CC} = 2.7 \text{ V}$  to 3.6 V,  $V_{ref} = 2.7 \text{ V}$  to  $AV_{CC}$ ,  $V_{SS} = AV_{SS} = 0 \text{ V}$ ,  $\phi = 2 \text{ MHz}$  to 20 MHz,  $T_a = -20^{\circ}\text{C}$  to 75°C (regular specifications),  $T_a = -40^{\circ}\text{C}$  to 85°C (wide-range specifications)

Condition B:  $V_{CC} = 3.0 \text{ V}$  to 3.6 V,  $AV_{CC} = 3.0 \text{ V}$  to 3.6 V,  $V_{ref} = 3.0 \text{ V}$  to  $AV_{CC}$ ,  $V_{SS} = AV_{SS} = 0 \text{ V}$ ,  $\phi = 2 \text{ MHz}$  to 25 MHz,  $T_a = -20^{\circ}\text{C}$  to 75°C (regular specifications),  $T_a = -40^{\circ}\text{C}$  to 85°C (wide-range specifications)

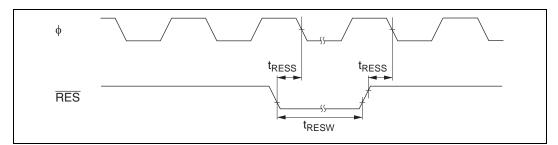

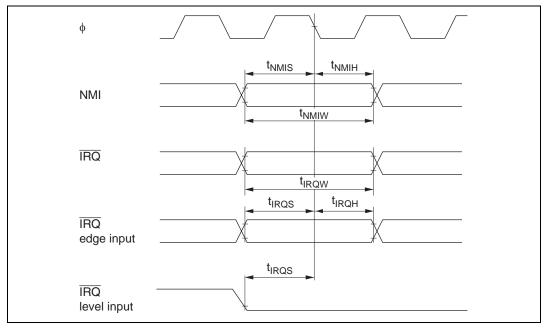

|                                                          |                   | Con | dition A | Con | dition B | 5                | Test        |

|----------------------------------------------------------|-------------------|-----|----------|-----|----------|------------------|-------------|

| Item                                                     | Symbol            | Min | Max      | Min | Max      | Unit             | Conditions  |

| RES setup time                                           | t <sub>RESS</sub> | 200 | _        | 200 | _        | ns               | Figure 22.4 |

| RES pulse width                                          | t <sub>RESW</sub> | 20  |          | 20  | —        | t <sub>cyc</sub> |             |

| NMI setup time                                           | t <sub>NMIS</sub> | 150 | _        | 150 | _        | ns               | Figure 22.5 |

| NMI hold time                                            | t <sub>NMIH</sub> | 10  | _        | 10  | _        |                  |             |

| NMI pulse width (in recovery from software standby mode) | t <sub>NMIW</sub> | 200 | —        | 200 | —        |                  |             |

| IRQ setup time                                           | t <sub>IRQS</sub> | 150 | —        | 150 | —        | ns               |             |

| IRQ hold time                                            | t <sub>IRQH</sub> | 10  | _        | 10  | _        |                  |             |

| IRQ pulse width (in recovery from software standby mode) | t <sub>IRQW</sub> | 200 |          | 200 |          |                  |             |

## Renesas

Figure 22.4 Reset Input Timing

Figure 22.5 Interrupt Input Timing

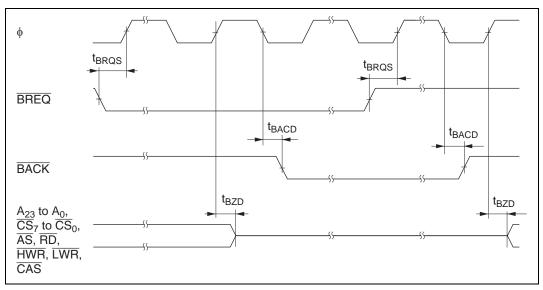

Figure 22.14 External Bus Release Timing

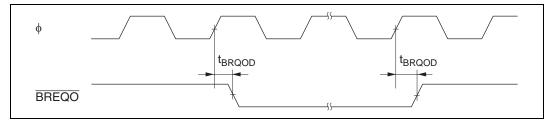

Figure 22.15 External Bus Request Output Timing

#### (2) Control Signal Timing

#### Table 22.16 Control Signal Timing

Condition B:  $V_{CC} = 3.0 \text{ V}$  to 3.6 V,  $AV_{CC} = 3.0 \text{ V}$  to 3.6 V,  $V_{ref} = 3.0 \text{ V}$  to  $AV_{CC}$ ,  $V_{SS} = AV_{SS} = 0 \text{ V}$ ,  $\phi = 2 \text{ MHz}$  to 25 MHz,  $T_a = -20^{\circ}\text{C}$  to 75°C (regular specifications),  $T_a = -40^{\circ}\text{C}$  to 85°C (wide-range specifications)

|                                                          |                   | Con | dition B |                  |                 |

|----------------------------------------------------------|-------------------|-----|----------|------------------|-----------------|

| Item                                                     | Symbol            | Min | Max      | Unit             | Test Conditions |

| RES setup time                                           | t <sub>RESS</sub> | 200 | _        | ns               | Figure 22.4     |

| RES pulse width                                          | t <sub>RESW</sub> | 20  | —        | t <sub>cyc</sub> | _               |

| NMI setup time                                           | t <sub>NMIS</sub> | 150 | _        | ns               | Figure 22.5     |

| NMI hold time                                            | t <sub>NMIH</sub> | 10  |          |                  |                 |

| NMI pulse width (in recovery from software standby mode) | t <sub>NMIW</sub> | 200 | —        |                  |                 |

| IRQ setup time                                           | t <sub>IRQS</sub> | 150 | _        | ns               | _               |

| IRQ hold time                                            | t <sub>IRQH</sub> | 10  | _        |                  |                 |

| IRQ pulse width (in recovery from software standby mode) | t <sub>IRQW</sub> | 200 | _        |                  |                 |

|      |                   |            | Inst      | Add       | Addressing Mode/<br>Instruction Length (Bytes) | Len       | gt Q      | de/             | (se |                                     |                |       |   |                             |

|------|-------------------|------------|-----------|-----------|------------------------------------------------|-----------|-----------|-----------------|-----|-------------------------------------|----------------|-------|---|-----------------------------|

|      |                   | erand Size |           | uS        | (nA3,b                                         | +uX3@/uX3 |           | ରୁଏଏ<br>ମ୍ବାଧC) |     | 0                                   | Condition Code | Cod   |   | No. of States <sup>*1</sup> |

|      | Mnemonic          |            | va<br>xx# | ⊒@<br>עצו |                                                |           | r)@<br>8@ |                 | _   | Operation                           | N<br>N<br>H    | z v   | с | Advanced                    |

| BCLR | BCLR Rn,@aa:32    | В          |           |           |                                                |           | 8         |                 |     | (Rn8 of @aa:32)←0                   |                |       |   | 9                           |

| BNOT | BNOT #xx:3,Rd     | В          | ~~~       | 2         |                                                |           |           |                 |     | (#xx:3 of Rd8)←[¬ (#xx:3 of Rd8)] — |                |       |   | -                           |

|      | BNOT #xx:3,@ERd   | В          |           | 4         |                                                |           |           |                 |     | (#xx:3 of @ERd)←                    |                |       |   | 4                           |

|      |                   |            |           |           |                                                |           |           |                 |     | [¬ (#xx:3 of @ERd)]                 |                |       |   |                             |

|      | BNOT #xx:3,@aa:8  | В          |           |           |                                                |           | 4         |                 |     | (#xx:3 of @aa:8)←                   |                |       |   | 4                           |

|      |                   |            |           |           |                                                |           |           |                 |     | [¬ (#xx:3 of @aa:8)]                |                |       |   |                             |

|      | BNOT #xx:3,@aa:16 | В          |           |           |                                                |           | 9         |                 |     | (#xx:3 of @aa:16)←                  |                |       |   | 5                           |

|      |                   |            |           |           |                                                |           |           |                 |     | [¬ (#xx:3 of @aa:16)]               |                |       |   |                             |

|      | BNOT #xx:3,@aa:32 | В          |           |           |                                                |           | 8         |                 |     | (#xx:3 of @aa:32)←                  |                |       |   | 9                           |

|      |                   |            |           |           |                                                |           |           |                 |     | [¬ (#xx:3 of @aa:32)]               |                |       |   |                             |

|      | BNOT Rn,Rd        | В          | N         | 2         |                                                |           |           |                 |     | (Rn8 of Rd8)←[¬ (Rn8 of Rd8)] —     |                |       |   | 1                           |

|      | BNOT Rn,@ERd      | В          | _         | 4         |                                                |           | _         | -               |     | (Rn8 of @ERd) ← [¬ (Rn8 of @ERd)] — | <br> <br>      |       | Ι | 4                           |

|      | BNOT Rn,@aa:8     | В          |           |           |                                                |           | 4         |                 |     | (Rn8 of @aa:8)←[¬ (Rn8 of @aa:8)] — |                |       |   | 4                           |

|      | BNOT Rn,@aa:16    | ш          |           |           |                                                |           | 9         |                 |     | (Rn8 of @aa:16)←                    |                |       |   | 5                           |

|      |                   |            |           |           |                                                |           |           |                 |     | [⊣ (Rn8 of @aa:16)]                 |                |       |   |                             |

|      | BNOT Rn,@aa:32    | Ш          |           |           |                                                |           | 00        |                 |     | (Rn8 of @aa:32)←                    |                |       |   | 9                           |

|      |                   |            | _         | _         |                                                |           | _         | -               |     | [¬ (Rn8 of @aa:32)]                 |                |       | _ |                             |

| BTST | BTST #xx:3,Rd     | ш          | 11        | 2         |                                                |           |           |                 |     | ר (#xx:3 of Rd8)→Z                  |                | <br>↔ |   | -                           |

|      | BTST #xx:3,@ERd   | ш          |           | 4         |                                                |           |           | _               |     | ר (#xx:3 of @ERd)→Z —               |                | <br>↔ |   | З                           |

|      | BTST #xx:3,@aa:8  | В          |           | _         |                                                |           | 4         | _               |     | ¬ (#xx:3 of @aa:8)→Z —              |                | <br>↔ |   | с                           |

|      | BTST #xx:3,@aa:16 | В          |           |           |                                                |           | 9         |                 |     | ר (#xx:3 of @aa:16)→Z               |                | <br>↔ |   | 4                           |

|      |                   |            |           |           |                                                |           |           |                 |     |                                     |                |       |   |                             |